Beruflich Dokumente

Kultur Dokumente

04278027

Hochgeladen von

Travis GrayOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

04278027

Hochgeladen von

Travis GrayCopyright:

Verfügbare Formate

2288

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 54, NO. 4, AUGUST 2007

Fast-Processing Modulation Strategy for the Neutral-Point-Clamped Converter With Total Elimination of Low-Frequency Voltage Oscillations in the Neutral Point

Josep Pou, Member, IEEE, Jordi Zaragoza, Pedro Rodrguez, Member, IEEE, Salvador Ceballos, Vicen M. Sala, Rolando P. Burgos, Member, IEEE, and Dushan Boroyevich, Fellow, IEEE

AbstractThis paper presents a novel modulation strategy for a neutral-point-clamped converter. This strategy overcomes one of the main problems of this converter, which is the low-frequency voltage oscillation that appears in the neutral point under some operating conditions. The proposed modulation strategy can completely remove this oscillation for all the operating points and for any kind of loads, even unbalanced and nonlinear loads. The algorithm is based on a carrier-based pulsewidth modulation. Nevertheless, it can generate the maximum output-voltage amplitudes that are attainable under linear modulation, such as space-vector modulation. Furthermore, this technique can be implemented with a very simple algorithm and, hence, can be processed very quickly. The only drawback of this strategy is that the switching frequencies of the devices are one third higher than those of standard sinusoidal pulsewidth modulation. A control loop for balancing the voltages on the dc-link capacitors is also proposed. This balancing strategy is designed, so that it does not further increase the switching frequencies of the devices when it is applied to the converter. The proposed modulation technique is veried by simulation and experiment. Index TermsModulation strategy, neutral-point-clamped (NPC) converter, pulsewidth-modulated inverters, three-level converter, voltage balance.

Fig. 1.

Three-level diode-clamped converter (or NPC converter).

I. I NTRODUCTION ULTILEVEL converters can provide more than two voltage levels at the outputs. Consequently, they can generate better output-voltage spectra than the classical twolevel converter. Another advantage of multilevel converters is that their devices only have to stand a portion of the maximum voltage that is generated at the outputs. These two features make the use of multilevel converters practical for high-power applications, in which high voltages must be handled. Moreover, the improved voltage spectra allow for the reduction of the switching frequencies of the devices. This is crucial in high-power applications not only because of the potential for reducing switching losses but also because of the intrinsic length of the ton and to switching times of these devices. The multilevel converter topology that is most extensively applied at present is the neutral-point-clamped (NPC) converter [1], which is a three-level converter (Fig. 1). For proper operation of this topology, the neutral-point (NP) voltage must be kept at one half of the dc-link voltage. If there is no external control for the voltages on the capacitors, the modulation strategy must be designed to achieve voltage balancing between the capacitors. A great deal of research has been focused on this eld [2][6]. Although the averaged NP voltage can be controlled, a low-frequency NP voltage oscillation appears under some operating conditions. This is a signicant drawback of this converter since the dc-link capacitors and the devices of the converter must be designed to stand this oscillation.

Manuscript received May 9, 2006; revised July 25, 2006. This work was supported in part by the Departament dUniversitats, Recerca i Societat de la Informaci of the Generalitat de Catalunya under Grant 2005BE00481, Grant 2004BE00105, and Grant 2004BE00060, and in part by the Ministerio de Ciencia y Tecnologia of Spain under Project ENE2004-07881-C03-02 and Project ENE2004-07881-C03-03. This work made use of the Engineering Research Center Shared Facilities, which are supported in part by the National Science Foundation under NSF Award EEC-9731677 and in part by the CPES Industry Partnership Program. Any opinions, ndings, and conclusions or recommendations expressed in this material are those of the authors and do not necessarily reect those of the National Science Foundation. This paper was presented at the 31st Annual Conference of the IEEE Industrial Electronics Society, Raleigh, NC, November 610, 2005. J. Pou, J. Zaragoza, P. Rodrguez, and V. M. Sala are with the Power Quality and Renewable Energy (QuPER) Research Group, Department of Electronic Engineering, Technical University of Catalonia (UPC), 08222 Terrassa, Spain (e-mail: pou@eel.upc.edu). S. Ceballos is with the Energy Unit, RobotikerTecnalia Research Centre, 48170 Zamudio, Spain. R. P. Burgos and D. Boroyevich are with the Center for Power Electronics Systems, Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University, Blacksburg, VA 24061 USA. Digital Object Identier 10.1109/TIE.2007.894788

0278-0046/$25.00 2007 IEEE

POU et al.: MODULATION STRATEGY FOR NPC CONVERTER WITH ELIMINATION OF VOLTAGE OSCILLATION

2289

Furthermore, if the modulation algorithm does not take into account this NP voltage oscillation, the output voltages will contain low-frequency distortion. The feedforward pulsewidth modulation (PWM) [7] can completely avoid such voltage distortion at the output; however, the low-frequency NP voltage oscillation still remains. In the case of two back-to-back-connected NPC converters, the two converters can share the task of balancing voltages on the dc-link capacitors [8], [9]. Therefore, voltage balance is usually improved compared with that of a single NPC converter. However, such improvement strongly depends on the modulation indices and power factors of the two converters at the operating point. In [10], an interesting modulation strategy that is able to cancel low-frequency voltage oscillation in the NP is proposed. The analysis is based on the use of virtual vectors in spacevector modulation (SVM). Nevertheless, the algorithm is nally implemented using a carrier-based PWM. With this approach, however, one has to deal with angles and trigonometric functions, which complicates its application. While the algorithm can achieve an averaged NP current that is equal to zero, since the voltages on the capacitors are not naturally balanced, they preserve any original imbalance from the startup of the system. Furthermore, since the voltages are not regulated, they may deviate without control. The modulation algorithm that is proposed in this paper can also enable the locally averaged NP current to be equal to zero. However, the algorithm is based on a very simple treatment of the modulation signals, which is spectacularly easy to implement, even in a low-feature microprocessor. This strategy makes use of two carrier waveforms, just as in a standard SPWM for three-level inverters. This paper also proposes an efcient voltage-balancing compensator that neither increases the switching frequencies of the devices nor distorts the output voltages. This paper ends by showing the simulation and experimental results and drawing some conclusions. II. B ASIS OF THE M ETHOD In SPWM, each phase is controlled by one modulation signal. In some approaches (e.g., [11] and [12]), a zerosequence signal is added to provide NP current control, which consequently helps achieve voltage balance. However, the low-frequency NP voltage oscillations cannot be completely removed by means of these strategies. The modulation technique that is proposed here is based on the use of two modulation signals for each phase of the converter. The process to obtain these signals is described here. First, the original modulation signals are modied to obtain SVM patterns in order to achieve the maximum range for linear operation mode as follows: v a = va v 0 v b = vb v 0 v c = vc v 0 where v0 = (max(va , vb , vc ) + min(va , vb , vc ))/2.

The two modied modulation signals for each phase will be obtained from these signals, which must accomplish va = vap + van vb = vbp + vbn vc = vcp + vcn (2)

where vip 0 and vin 0, with i = {a, b, c}. The signals with p [0, 1], subscript p will only cross the upper carrier vcarrier and the signals with subscript n will only cross the lower one n [1, 0]. In Section IV, the process that is implemented vcarrier when comparing the modulation signals with the carriers is explained. It is anticipated that the connection to the NP (0 level) is produced when

p vip > vcarrier p vip vcarrier

and and

n vin < vcarrier or n vin vcarrier .

(3)

The two inner transistors of a phase leg of the converter (Fig. 1) are in the ON state when the corresponding NP control variable si0 {0, 1}, for i = {a, b, c}, is activated. In other words, when a variable si0 takes the unity value, the subsequent output phase is connected to the NP; otherwise, it takes the value of zero. When one phase leg is clamped to the NP, its output current is injected to this point. Therefore, current i0 can be expressed as follows: i0 = sa0 ia + sb0 ib + sc0 ic . (4)

In order to preserve voltage balance, the locally averaged NP current must be zero. Therefore, it is necessary to operate with the averaged NP current instead of the instantaneous current. The averaged NP current is obtained by using the moving average operator

t

1 x(t) = Ts

x( )d

tTs

(5)

where Ts is the sampling or switching period. Applying this operator to (4), one obtains the following: i0 = da0 ia + db0 ib + dc0 ic (6)

in which di0 = si0 for i = {a, b, c}. Assuming that the frequency of the carriers is much higher than the frequency of the modulation signals, the duty cycles can be expressed as follows:

+1 vip , di0 = vin

where

+1 vin = vin + 1.

(7)

Equation (7) is obtained from (3) and using the basic trigonometry in Fig. 2. As a result,

+1 +1 +1 i0 = van vap ia + vbn vbp ib + vcn vcp ic . (8)

(1)

If van vap = vbn vbp = vcn vcp = vx or (9)

+1 +1 +1 van vap = vbn vbp = vcn vcp = 1 + vx

2290

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 54, NO. 4, AUGUST 2007

Fig. 3. Fig. 2. Two possible situations for the calculation of the duty cycle di0 : +1 +1 +1 < vip and (b) vin > vip , for vin = vin + 1. (a) vin

Scheme for the generation of vip and vin from vi (i = {a, b, c}).

the solution for vap is for 0 t 2/3, vap = (va vc )/2 = ( 3/2)mSPWM cos(t /6) for 2/3 t 4/3, vap = 0 for 4/3 t 2, vap = (va vb )/2 = ( 3/2)mSPWM cos(t + /6) (14)

then the averaged NP current would be i0 = |1 + vx |(ia + ib + ic ). (10)

Since the neutral of the load is open (Fig. 1) or is just a triangle-connected load, there is no zero sequence in the current. Subsequently, the sum of the output currents is always zero (ia + ib + ic = 0); hence, i0 becomes zero. In conclusion, the problem of maintaining the locally averaged voltages on the dc-link capacitors constant is reduced to nd a proper value for vx in (9). An innite number of solutions can be found; however, one particularly interesting solution can achieve minimum switching frequencies in the devices of the converter. This solution is found by forcing variables vip and vin to be zero for the maximum time possible since, when these signals are zero, some of the transistors do not switch (none of the modulation signals cross a carrier signal). Regarding this restriction and relationships (1), (2), and (9), the following solution is obtained: vx = max(va , vb , vc ) min(va , vb , vc ) . 2 (11)

and that for van is for 0 t /3 and 5/3 t 2, for /3 t , van = (va vb )/2 = for t 5/3, van = (va vc )/2 = van = 0

3/2 mSPWM cos(t + /6) 3/2 mSPWM cos(t /6). (15)

The new modulation signals would be vip = vin =

vi min(va ,vb ,vc ) 2 vi max(va ,vb ,vc ) 2

for i = {a, b, c}.

(12)

The algorithm can be easily implemented using the scheme that is shown in Fig. 3. Under the assumption of sinusoidal modulation signals, such that va = mSPWM cos t vb = mSPWM cos(t 2/3) vc = mSPWM cos(t + 2/3) (13)

Fig. 4 shows the waveforms for this example. The amplitude of the modulation signals mSPWM , which is also dened as the modulation index, is adopted to be mSPWM = 2/ 3 = 1.1547. The modied modulation signals for phase b have the same shape but with a 2/3 phase-shift delay, and for phase c, the modulation signals have a 2/3 phase-shift advancement. Note that the modied modulation signals are within the range of [1, 1], which means that the converter would operate under linear modulation. Therefore, this example shows that the maximum modulation index that is achievable for the linearmodulation mode (mSPWM = 1.1547) can be achieved by this method. This maximum value is also obtained by SVM or by other carrier-based PWM strategies that make use of a proper zero-sequence signal. However, the method that is proposed here has the important advantage of maintaining equal voltages on the dc-link capacitors (disregarding switching ripples).

POU et al.: MODULATION STRATEGY FOR NPC CONVERTER WITH ELIMINATION OF VOLTAGE OSCILLATION

2291

they do not preserve any interval that is clamped to zero. As a consequence, the switching frequencies of the devices increase. Furthermore, the sign of the power ux in the system needs to be known in order to provide a proper shift to the signals. The balancing strategy that is proposed in this paper avoids increasing the switching frequencies of the devices. Moreover, it does not need to detect the direction of the power ux in the system. This technique is explained here. Regarding vap and van in Fig. 4(b), none of the signals are clamped to zero throughout the intervals /3 t 2/3 and 4/3 t 5/3. Therefore, the modied modulation signals of phase a can be shifted up or down during these intervals without increasing the switching frequencies of the devices. Similarly, there are other intervals for phases b and c in which none of the associated modulation signals are clamped to zero and, therefore, can be shifted. Although this strategy preserves the switching frequency of the devices when the compensator is activated, a signicant drawback is the slow voltage-balancing dynamics of the system. This occurs because only the modied modulation signals that are associated to one phase are shifted at any time. In order to improve the balancing dynamics, the sign of the output currents should be sensed. Furthermore, (2) must be preserved in order to avoid distortion in the output voltages during the compensation. This occurs if the offset that is applied to the modied modulations signals have opposite signs. The offset that is applied to vip is vi_o = kp |vC | sign(vC ii ) sign(vip vin 1). (16)

The absolute value of the voltage imbalance is multiplied by constant kp . The term sign(vC ii ) denes a sign for the compensation. Nevertheless, the nal sign of the offset depends +1 ), in accordance with on sign(vip vin 1) or sign(vip vin the two possible cases that are shown in Fig. 2. IV. C ONTROL S IGNALS FOR THE T RANSISTORS

Fig. 4. Example for sinusoidal modulation signals: (a) original signals and (b) modied signal for phase a.

The output level that is activated at each phase of the converter is dened by a comparison of the modied modulation signals with the carriers as follows:

p , then xip = 1; If vip > vcarrier n , then xin = 1; If vin < vcarrier

III. C OMPENSATION FOR I MBALANCES Using the proposed modulation technique, the locally averaged NP current is kept to zero, and consequently, the locally averaged voltages on the dc-link capacitors are constant. However, this does not imply that these voltages are equal. In fact, in theory, if the initial voltages on the capacitors were different, this modulation strategy would tend to preserve imbalance because the locally averaged NP current is zero. In practice, the situation is even worse since dead times, different values and behaviors of the components, etc., can make the voltages drift slowly and without control. Thus, some compensation for voltage imbalances must be provided. A control method for voltage compensation can be simply shifting the modied modulation signals in accordance to the sign of the voltage error (vC = vC 1 vC 2 ). An inconvenience of this method is that when the signals are shifted,

otherwise, xip = 0 otherwise, xin = 0 (17)

xi = xip xin , i {a, b, c} .

These variables can take three values, i.e., xi {1, 0, 1}, which are the possible output levels for each phase. In order to obtain the control functions of the transistors, the following relationships are needed: si4 si3 si2 si1 = 1, = 1, = 1, = 1, if xi if xi if xi if xi =1 = 1 or xi = 0 = 0 or xi = 1 = 1.

(18)

If the preceding respective conditions are not met, then variables si1 , si2 , si3 , and si4 are correspondingly zero. These variables are associated to the ON and OFF states of the transistors

2292

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 54, NO. 4, AUGUST 2007

Fig. 6.

Dynamics of the voltage compensator operating over a linear load.

Fig. 5. Experimental results (a) for standard SPWM and (b) for the proposed modulation strategy.

(on = 1 and off = 0), where two of them are always ON for each of the valid 27 electrical states of this converter. V. E XPERIMENTAL R ESULTS The proposed modulation technique has been veried by simulation and experiment. The values of the dc-link voltage and the capacitors are Vdc = 120 V and C = 1100 F, respectively. The converter operates over an RL wye-connected load, with L = 12 mH and R = 10 . The frequency of the carriers is 5 kHz in all the results, and the modulation index is mSPWM = 0.8 for Fig. 5 and mSPWM = 0.9 for Fig. 6. Fig. 5(a) shows the results that are obtained from the application of a standard SPWM. The variables shown are a line-to-line output voltage vab , the voltages on the dc-link capacitors vC 1 and vC 2 , and the output currents ia , ib , and ic . Note that there are signicant low-frequency voltage oscillations on the dc-link capacitors. The modulation frequency has been selected to be very low in this example (f = 20 Hz) in order to emphasize this effect. Fig. 5(b) shows the same results when the proposed mod-

Fig. 7. Dynamics of the voltage compensator operating over a nonlinear load (simulation results).

ulation technique is applied. In this case, the voltages on the dc-link capacitors do not contain any low-frequency oscillation but only high-frequency ripples that are related to the switching frequency. Note, however, that the switching frequencies of the devices increase compared to the former case since there are intervals in which the line-to-line voltages commutate among three states of the converter, instead of two. This is produced when neither of the two corresponding modied modulation signals is clamped to zero. The balancing process is shown in Fig. 6, in which the initial voltages on the dc-link capacitors are unbalanced. Observe that the voltages become equal very quickly. Fig. 7 shows a simulation example in which a set of second and fourth current harmonics has been added to the load currents. These harmonics are very harmful for the standard SPWM strategy since they may introduce instability to the NP voltage, which is also a problem when operating under standard SVM techniques [13]. However, when the proposed modulation

POU et al.: MODULATION STRATEGY FOR NPC CONVERTER WITH ELIMINATION OF VOLTAGE OSCILLATION

2293

strategy is applied, the voltages on the dc-link capacitors do not show any negative effect, and the system is always stable.

VI. C ONCLUSION The modulation technique that is proposed in this paper completely removes the low-frequency voltage oscillations that appear in the NP of the three-level inverter for some operating conditions. This technique is also able to attain the maximum amplitudes that are achievable under linear modulation, and its algorithm is very simple and can therefore be quickly processed in real time. Furthermore, unbalanced and nonlinear loads no longer produce additional low-frequency voltage oscillations or instability to the NP. The only drawback of this strategy is that the switching frequencies of the devices are one third higher than those of a standard SPWM for any modulation index under linear-operation mode. The method that is proposed for voltage compensation performs very well. It is able to preserve constant switching frequencies on the devices and introduces no distortion in the output voltages. This strategy will help extend the use of the NPC converter to lower power applications. One reason for this is that the modulation algorithm can be straightforwardly implemented in a very simple microprocessor. Furthermore, since there is no longer low-frequency voltage oscillation in the NP, the values of the dc-link capacitors can be signicantly reduced. An interesting application could be the use of MOSFETs for the synthesis of the NPC converter operating at about 600 V in the dc bus. Since the NP voltage never oscillates, the devices would only have to support half of the dc-link voltage. R EFERENCES

[1] A. Nabae, I. Takahashi, and H. Akagi, A new neutral-point-clamped PWM inverter, IEEE Trans. Ind. Appl., vol. IA-17, no. 5, pp. 518523, Sep./Oct. 1981. [2] H. L. Liu, N. S. Choi, and G. H. Cho, DSP based space vector PWM for three-level inverter with DC-link voltage balancing, in Proc. IEEE IECON, Oct. 28Nov. 1, 1991, vol. 1, pp. 197203. [3] N. Celanovic and D. Boroyevich, A comprehensive study of neutral-point voltage balancing problem in three-level neutral-point-clamped voltage source PWM inverters, IEEE Trans. Power Electron., vol. 15, no. 2, pp. 242249, Mar. 2000. [4] S.-K. Lim, J.-H. Kim, and K. Nam, A DC-link voltage balancing algorithm for 3-level converter using the zero sequence current, in Proc. IEEE PESC, Jun. 27Jul. 1, 1999, vol. 2, pp. 10831088. [5] R. M. Tallam, R. Naik, and T. A. Nondahl, A carrier-based PWM scheme for neutral-point voltage balancing in three-level inverters, in Proc. IEEE APEC, Feb. 2226, 2004, vol. 3, pp. 16751681. [6] A. Bendre, G. Venkataramanan, D. Rosene, and V. Srinivasan, Modeling and design of a neutral-point voltage regulator for a three-level diodeclamped inverter using multiple-carrier modulation, IEEE Trans. Ind. Electron., vol. 53, no. 3, pp. 718726, Jun. 2006. [7] J. Pou, D. Boroyevich, and R. Pindado, New feedforward space-vector PWM method to obtain balanced AC output voltages in a three-level neutral-point-clamped converter, IEEE Trans. Ind. Electron., vol. 49, no. 5, pp. 10261034, Oct. 2002. [8] J. Pou, R. Pindado, D. Boroyevich, and P. Rodrguez, Limits of the neutral-point balance in back-to-back-connected three-level converters, IEEE Trans. Power Electron., vol. 19, no. 3, pp. 722731, May 2004. [9] R. C. Portillo, M. A. Martn Prats, J. I. Len, J. A. Snchez, J. M. Carrasco, E. Galvn, and L. Garcia Franquelo, Modeling strategy for back-to-back three-level converters applied to high-power wind turbines, IEEE Trans. Ind. Electron., vol. 53, no. 5, pp. 14831491, Oct. 2006. [10] S. Busquets-Monge, J. Bordonau, D. Boroyevich, and S. Somavilla, The nearest three virtual space vector PWMA modulation for the compre-

hensive neutral-point balancing in the three-level NPC inverter, IEEE Power Electron. Lett., vol. 2, no. 1, pp. 1115, Mar. 2004. [11] C. Newton and M. Sumner, Neutral point control for multi-level inverters: Theory, design and operational limitations, in Proc. IEEE IAS Annu. Meeting, Jul. 1997, vol. 2, pp. 13361343. [12] J. Pou, P. Rodrguez, J. Zaragoza, V. Sala, C. Jan, and D. Boroyevich, Enhancement of carrier-based modulation strategies for multilevel converters, in Proc. IEEE PESC, Recife, Brazil, Jun. 1216, 2005, pp. 25342539. [13] J. Pou, R. Pindado, D. Boroyevich, and P. Rodrguez, Effects of imbalances and nonlinear loads on the voltage balance of a neutralpoint-clamped inverter, IEEE Trans. Power Electron., vol. 20, no. 1, pp. 123131, Jan. 2005.

Josep Pou (S97M03) received the B.S., M.S., and Ph.D. degrees in electrical engineering from the Technical University of Catalonia (UPC), Terrassa, Spain, in 1989, 1996, and 2002, respectively. In 1989, he was the Technical Director of Polylux S.A. In 1990, he joined the faculty of UPC as an Assistant Professor and became an Associate Professor in 1993. From February 2001 to January 2002 and from February 2005 to January 2006, he was a Researcher in the Center for Power Electronics Systems, Virginia Polytechnic Institute and State University, Blacksburg. He is currently a member of the Power Quality and Renewable Energy (QuPER) Research Group, Department of Electronic Engineering, UPC. He has authored more than 50 published technical papers and has been involved in several industrial projects and educational programs in the elds of power electronics and systems. His research interests include modeling and control of power converters, multilevel converters, power quality, renewable energy systems, and motor drives. Dr. Pou is a member of the IEEE Power Electronics, IEEE Industry Electronics, and IEEE Industrial Applications Societies.

Jordi Zaragoza received the B.S. degree in electronic engineering and the M.S. degree in automatic and electronic industrial engineering from the Technical University of Catalonia (UPC), Terrassa, Spain, in 2001 and 2004, respectively. He is currently working toward the Ph.D. degree in the Department of Electronic Engineering, UPC. In 2003, he joined the faculty of UPC as an Assistant Professor. From June to September 2006, he was a Researcher in the Energy Unit, RobotikerTecnalia Technologic Corporation, Zamudio, Spain. He is currently a member of the Power Quality and Renewable Energy (QuPER) Research Group, Department of Electronic Engineering, UPC. He has authored more than ten published technical paper. His research interests include modeling and control of power converters, multilevel converters, wind energy, and power quality.

Pedro Rodrguez (S99M04) received the B.S. degree in electrical engineering from the University of Granada, Granada, Spain, in 1989, and the M.S. and Ph.D. degrees in electrical engineering from the Technical University of Catalonia (UPC), Terrassa, Spain, in 1994 and 2004, respectively. In 1990, he joined the faculty of UPC as an Assistant Professor and became an Associate Professor in 1993. He was a Researcher in the Center for Power Electronics Systems, Virginia Polytechnic Institute and State University, Blacksburg, in 2005 and in the Institute of Energy Technology, Aalborg University, Aalborg, Denmark, in 2006. He is currently a member of the Power Quality and Renewable Energy (QuPER) Research Group, Department of Electronic Engineering, UPC. His research interests include power conditioning, integration of distributed-energy systems, and control of power converters.

2294

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 54, NO. 4, AUGUST 2007

Salvador Ceballos was born in Santander, Spain, in 1978. He received the B.S. degree in physics from the University of Cantabria, Santander, in 2001, and the B. Eng. degree in electronic engineering from the University of the Basque Country, Bilbao, Spain, in 2002. He is currently working toward the Ph.D. degree in the Faculty of Engineering, Department of Electronics and Telecommunications, University of the Basque Country. Since 2002, he has been with the Robotiker Tecnalia Research Centre, Zamudio, Spain, where he is currently a Development Engineer in the Energy Unit. His research interests include multilevel converters and fault-tolerant power electronics topologies.

Rolando P. Burgos (S96M03) received the B.S., Electronics Engineering, M.S., and Ph.D. degrees from the University of Concepcin, Concepcin, Chile, in 1994, 1997, 1999, and 2002, respectively. In 2002, he joined the Center for Power Electronics Systems, Department of Electrical and Computer Engineering, Virginia Polytechnic Institute and State University, Blacksburg, as a Postdoctoral Fellow and became a Research Scientist in 2003 and a Research Assistant Professor in 2005. His research interests include modeling, control, and synthesis of power electronics conversion systems for more electric aircraft and marine applications.

Vicen M. Sala received the B.S. and M.S. degrees in electronic engineering from the Technical University of Catalonia (UPC), Terrassa, Spain, in 2001 and 2007, respectively. In 2000, he was the responsible for the Department of Electronic Engineering, Twistechnology SL. In 2001, he joined the faculty of UPC as an Assistant Professor. He is currently a member of the Power Quality and Renewable Energy (QuPER) Research Group, Department of Electronic Engineering, UPC. He has authored more than ten technical papers. He is the holder of one patent. His research interests include modeling and control of power converters, multilevel converters, power quality, renewable energy systems, motor drives, and class-D audio power ampliers.

Dushan Boroyevich (S81M86SM03F06) received the Dipl.Ing. degree from the University of Belgrade, Belgrade, Serbia, in 1976, the M.S. degree from the University of Novi Sad, Novi Sad, Serbia, in 1982, and the Ph.D. degree from Virginia Polytechnic Institute and State University (Virginia Tech), Blacksburg, in 1986. From 1986 to 1990, he was an Assistant Professor and the Director of the Power and Industrial Electronics Research Program, Institute for Power and Electronic Engineering, University of Novi Sad, and was later the Acting Head of the Institute. He then joined the Department of Electrical and Computer Engineering, Virginia Tech, as an Associate Professor, and is currently the American Electric Power Professor in the department and a Codirector of the Center for Power Electronics Systems. His research interests include multiphase power conversion, power electronics systems modeling and control, and multidisciplinary design optimization.

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- USA Medical ElectivesDokument40 SeitenUSA Medical ElectivesMurad Sahawneh100% (1)

- Social Psychology ReflectionDokument3 SeitenSocial Psychology Reflectionapi-325740487Noch keine Bewertungen

- 9th Form - Test Unit 7 IIDokument1 Seite9th Form - Test Unit 7 IIapi-3801443Noch keine Bewertungen

- 10thanniversary - Leafletfore MailDokument2 Seiten10thanniversary - Leafletfore MailredmondptNoch keine Bewertungen

- Master Iscrizione en 12426Dokument2 SeitenMaster Iscrizione en 12426msa65851Noch keine Bewertungen

- Parenting A Teen Girl: A Crash Course On Conflict, Communication & Connection With Your Teenage DaughterDokument11 SeitenParenting A Teen Girl: A Crash Course On Conflict, Communication & Connection With Your Teenage DaughterNew Harbinger Publications100% (6)

- Unit 1 Worksheet 1: Have You Been ?Dokument4 SeitenUnit 1 Worksheet 1: Have You Been ?Alberto SiriNoch keine Bewertungen

- Linking Extracurricular Programming To Academic Achievement: Wiio Benefits and Why?Dokument28 SeitenLinking Extracurricular Programming To Academic Achievement: Wiio Benefits and Why?Laeeq ZafarNoch keine Bewertungen

- How To Answer Bi Paper 1 and Paper 2 Wisely and Effectively by PDokument21 SeitenHow To Answer Bi Paper 1 and Paper 2 Wisely and Effectively by PNorlida Abd RahmanNoch keine Bewertungen

- TheraDokument4 SeitenTheramaircusNoch keine Bewertungen

- Gitarattan Jindal Public SchoolDokument1 SeiteGitarattan Jindal Public Schoolvishal110085Noch keine Bewertungen

- Spring Boot AnnotationsDokument12 SeitenSpring Boot AnnotationsMedNejjarNoch keine Bewertungen

- Tugas ATDokument20 SeitenTugas ATKhoirunnisa OktarianiNoch keine Bewertungen

- Personal Space Lesson PlanDokument5 SeitenPersonal Space Lesson Planapi-392223990Noch keine Bewertungen

- English 8: First Monthly ExaminationDokument2 SeitenEnglish 8: First Monthly ExaminationFloramie MorenoNoch keine Bewertungen

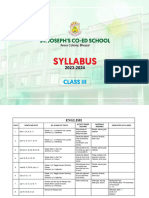

- Syllabus Class IIIDokument36 SeitenSyllabus Class IIIchandrakiranmeena14Noch keine Bewertungen

- Introduction To Deep Learning: Le Hoang Nam Namlh@hanu - Edu.vnDokument33 SeitenIntroduction To Deep Learning: Le Hoang Nam Namlh@hanu - Edu.vnKhoa Tran NgocNoch keine Bewertungen

- Building Christ-Based Relationships Disciples and Sharing The GDokument11 SeitenBuilding Christ-Based Relationships Disciples and Sharing The GEd PinedaNoch keine Bewertungen

- Alessi and Trollips Model 2011Dokument3 SeitenAlessi and Trollips Model 2011Anonymous HBT778cNoch keine Bewertungen

- FA3 - Contemporary WorldDokument15 SeitenFA3 - Contemporary WorldGill GregorioNoch keine Bewertungen

- Quality Work Refection Visual Arts Worksheet - Ofrenda Still LifeDokument3 SeitenQuality Work Refection Visual Arts Worksheet - Ofrenda Still Lifeapi-543529133Noch keine Bewertungen

- Toronto Public Library - Circulation and Collection Use (Including Fees Andfines) Policy - 2013 RecommendationsDokument10 SeitenToronto Public Library - Circulation and Collection Use (Including Fees Andfines) Policy - 2013 RecommendationsLJ's infoDOCKETNoch keine Bewertungen

- Who We Are Jan 8 2013Dokument5 SeitenWho We Are Jan 8 2013api-147600993Noch keine Bewertungen

- Person-Centered TherapyDokument3 SeitenPerson-Centered TherapyMaleesha PereraNoch keine Bewertungen

- Social Ethical ResponsibilitiesDokument16 SeitenSocial Ethical ResponsibilitiesRenz Daniel R. ElmidoNoch keine Bewertungen

- SN Key Result Area Key Task Performance Standards 1 Teaching and LearningDokument2 SeitenSN Key Result Area Key Task Performance Standards 1 Teaching and LearningrajksdNoch keine Bewertungen

- CDMTU Flyer MBA CL 2021Dokument4 SeitenCDMTU Flyer MBA CL 2021ShivendraNoch keine Bewertungen

- What I Need To Know? What I Need To Know?: Quarter 1Dokument9 SeitenWhat I Need To Know? What I Need To Know?: Quarter 1Aileen gay PayunanNoch keine Bewertungen

- Beekeeping Practices Challenge and Honey MarketingDokument24 SeitenBeekeeping Practices Challenge and Honey MarketingBrook Legese Dadhe 23926007Noch keine Bewertungen

- SASBE Call For PapersDokument1 SeiteSASBE Call For Papersanup8800% (1)