Beruflich Dokumente

Kultur Dokumente

A System Bus Power: Systematic To Algorithms

Hochgeladen von

Nandhini RamamurthyOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

A System Bus Power: Systematic To Algorithms

Hochgeladen von

Nandhini RamamurthyCopyright:

Verfügbare Formate

VLSI DESIGN 2001, Vol. 12, No. 2, pp.

101-111 Reprints available directly from the publisher Photocopying permitted by license only

(C) 2001 OPA (Overseas Publishers Association) N.V. Published by license under the Gordon and Breach Science Publishers imprint.

A Systematic Approach to Reduce the System Bus Load and Power in Multimedia Algorithms

KOEN DANCKAERTa*, CHIDAMBER KULKARNI at, FRANCKY CATTHOORa*, HUGO DE MANa and VIVEK TIWARI b

blntel Corp., 3600 Juliette Ln.,

alMEC, Kapeldreef 75, B-3001 Leuven, Belgium," Santa Clara, CA 95052, USA

(Received 20 June 2000; In final form 3 August 2000)

Multimedia algorithms deal with enormous amounts of data transfers and storage, resulting in huge bandwidth requirements at the off-chip memory and system bus level. As a result the related energy consumption becomes critical. Even for execution time the bottleneck can shift from the CPU to the external bus load. This paper demonstrates a systematic software approach to reduce this system bus load. It consists of source-tosource code transformations, that have to be applied before the conventional ILP compilation. To illustrate this we use a cavity detection algorithm for medical imaging, that is mapped on an Intel Pentium(R) II processor.

Keywords: Multimedia; Memory optimization; Low-power design; Bandwidth reduction; Bus load reduction; Medical imaging

Trademarks used: Intel and Pentium are registered trademarks of Intel Corp.

1. INTRODUCTION

Multimedia systems such as medical image processing and video compression algorithms, typically use a very large amount of data storage and transfers. This causes huge bandwidth

requirements at the off-chip memory and system bus level. The required memories and bus transfers will consume a lot of power [8, 14], which is especially a problem in embedded systems. It has been shown that a dominant part of the power in embedded multimedia systems is consumed by

*Corresponding author. Also Ph.D. student at Katholike Univ. Leuven. Tel.: +32-16281407, Fax: +32-16281515, e-mail:

Koen.Danckaert@imec.be

Also Ph.D. student at Katholike Univ. Leuven. Tel.: + 32-16281407, Fax: + 32-16281515, e-mail: Chidamber.Kulkarni@imec.be $Also prof. at Katholieke Univ. Leuven. Tel.: / 32-16281202, Fax: + 32-16281515, e-mail: Francky.Catthoor@imec.be Also prof. at Katholieke Univ. Leuven. Tel.: + 32-16281201, Fax: + 32-16281515, e-mail: Hugo.DeMan@imec.be

e-mail:

Vivek.Tiwari@intel.com

101

102

K. DANCKAERT et al.

data storage and transfers (as opposed to the computations which consume much less) [23], and even on the CPU chip itself it is a major

contribution [10, 20]. Additionally, in many cases the performance bottleneck for this kind of applications lies not in the CPU, but in the board containing the external system bus and the off-chip memories. Even when the bottleneck is still with the CPU computations for a single application, the huge bandwidth requirements will cause performance problems when this application has to share the system bus with other applications or background processes running on the same board (containing one or more processors). In this paper, we demonstrate our DTSE (Data Transfer and Storage Exploration) methodology, which is a software approach to alleviate the system bus load problem. In this approach, several source-to-source code transformations to optimize the global memory accesses of an application are applied in a systematic way. In the past we have developed such a methodology for customizable hardware systems [4], where the memory hierarchy can be designed for a specific application. In this paper we apply the relevant steps of this methodology (with adaptations) to a programmable system with a fixed memory hierarchy, to show that it reduces the system bus load on programmable systems too. Because most of the basic methodology steps are explained in [4] (for customizable systems), we will not focus in detail on the steps themselves. Instead we demonstrate the methodology by applying it on a representative application (a cavity detector for medical imaging), with a programmable processor (a 450 MHz Pentium(R) II with 512K L2-cache) as target architecture. In Section 2, we will give a short overview of our methodology. In Section 3, it is applied to the cavity detection application. Section 4 gives some other experimental results, and Section 5 discusses the current status of our work. Conclusions are drawn in Section 6.

2. OVERVIEW OF THE METHODOLOGY

In [4], we have thoroughly described our DTSE methodology for data transfer and storage exploration, for customizable systems. A number of data storage and transfer optimization steps are included in this methodology:

1. Memory oriented data-fl0w analysis and pruning of the initial system specification. 2. Global data-flow and loop transformations of the systems description for reduction of the required background memories and accesses but also to enable further optimization steps. 3. Data reuse transformations to exploit a distributed memory hierarchy more effectively in the algorithm. In this step, additional data copies are introduced in a judicious way. 4. Storage cycle budget distribution to determine the bandwidth requirements and the balancing of the available cycle budget over the different memory accesses in the algorithmic specification. 5. Memory allocation and signal to memory/port assignment, to determine the necessary number of memory units and their type (if freedom is left, e.g., in the off-chip memory organization). The goal of this step is to produce a netlist of memory units from a memory library as well as an assignment of signals to the available memory units. 6. In-place mapping. Here the aim is to increase the cache hit rate and reduce the memory size by storing signals with non-overlapping lifetimes in the same physical memory location. Conventionally memory reuse is only applied for variables with different scopes. We apply aggressive in-place transformations also when arrays have partly overlapping lifetimes. 7. Main memory data layout organization. Here we rearrange the data in memory to reduce cache conflict misses as much as possible.

Because Steps 4 and 5 are not relevant when the target architecture is a programmable processor

MULTIMEDIA ALGORITHMS

103

with a fixed memory hierarchy, they will not be applied in this paper.

3. APPLICATION TO A REPRESENTATIVE

EXAMPLE

3.1. The Initial Cavity Detection Algorithm

of the functions reads an image from off-chip memory, and writes the result back to this memory. After applying our DTSE methodology, these off-chip memories and transfers will be heavily reduced, resulting in much less off-chip data storage and transfers. Note that all these steps are performed in an application-independent systematic way.

3.2. Global Data-flow and Loop Transformations

The cavity detection algorithm extracts edges from medical images, such that they can more easily be interpreted by physicians [2]. The initial algorithm consists of a number of functions, each of which has an image frame as input and one as output (see Fig. 1). The initial code is given in Figure 2. We have made two types of measurements to compare the data transfer and storage requirements of different versions of the algorithm. First of all, to obtain precise feedback on the number of data accesses, we have developed an access counting tool (ATOMIUM), which counts all accesses for each array in an algorithm, and this in each function (or even on a finer granularity). This allows to locate the bottlenecks in terms of data storage and transfers. In Figure 6, we have summarized these results. Note that the distinction between main memory and local memory in this figure is made manually, by assigning each array to a level of the memory hierarchy. On a customizable system, this can also be done physically, but on a cache-based programmable system, these results do not directly indicate the real data transfers. To obtain these, we have used the Pentium(R) II event counters to count the number of L1 cache misses and the number of system bus memory transfers, as shown in Figure 7. For the initial algorithm, we can see in these figures that the system bus bandwidth requirements are very high. The main reason is that each

function

During this step, the code is transformed to expose maximal locality and potential data reuse. This is done by applying data-flow and loop transformations. Because loop transformations are relatively well known for increasing locality and introducing parallelism [1, 9, 12, 22], we will not go into much detail, such that we can concentrate more on the other steps of our methodology. Note however that we we apply these transformations on a more global scale than conventionally done, to optimize the global data transfers which are most crucial for the system bus load [6]. First some redundant initializations are removed by a data-flow transformation. Then another data-flow transformation is applied to remove the computation of the maximum of the whole image (in the function Reverse()). Although this computation is negligible in terms of CPU time, it is very important in terms of data transfer and storage, because the whole image has to read from memory, and stored again, before the next function (DetectRoots()) can proceed. In this case however, this maximum computation can be eliminated by a global data-flow transformation. Next, a loop folding and merging transformation is applied to the y-loops in the algorithm. As a

function

function

GaussBlur

(uchar image_in[N][M],

uchar image_out[N][M])

ComputeEdges

(uchar image_in[N][M],

uchar image_out[N][M])

DetectRoots

(uchar image_ln[N][M],

uchar image_out[N][M])

FIGURE

Initial cavity detection algorithm.

104

K. DANCKAERT et al.

void GaussBlur (uchar image_in[M] [N], uchar gauss_xy[M] [N]) // uchar stands for unsigned char uchar gauss_x[M] [N] for (y=0; y<M; ++y) for (x=0; x<N; ++x) // Apply horizontal gauss blurring gauss_x[y] [x] for (y=0; y<M; ++y) for (x=0; x<N; ++x) // Apply vertical gauss blurring gauss_xy[y] [x]

....

void ComputeEdges (uchar gauss_xy[M] [N], uchar comp_edge[M] [N]) for (y=0; y<M; ++y) for (x=0; x<N; ++x) comp_edge[y] [x] =... // Replace pix. with max. diff. with its neighbors

void Reverse (uchar comp_edge[M] [N], uchar ce_rev[M] [N]) maxval // Search for the maximum value that occurs for (y=0; y<M; ++y) for (x=0; x<N; ++x) maxval // Subtract every pixelvalue from this maximum value for (y=0; y<M; ++y) ++x) x<N; (x=0; for comp_edge[y] [x]; maxval ce_rev[y] [x]

void DetectRoots (uchar comp_edge [M] [N] uchar image_out [M] [N] uchar ce_rev [M] [N] / / Reverse image Reverse (comp_edge, ce_rev) for (y=0; y<M; ++y) for (x=0; x<N; ++x) image_out[y] [x] =... // is true if no neighbors are > than ce_rev[y] [x]

void main () uchar image_in[M] [N], gauss_xy[M] [N], comp_edge[M] [N], image_oltt[M] [N]; GaussBlur (image_in, gauss_xy) ComputeEdges (gauss_xy, comp_edge) DetectRoots (comp_edge, image_out)

FIGURE 2 Initial code of the cavity detection algorithm.

result, the functions will not work on whole image at once anymore, but on a line-per-line pipelining base. This is shown in Figure 3. Finally, a similar loop folding and merging transformation is applied to the x-loops too. The result is that the algorithm will now work on a fine-grain (pixel per pixel) pipelining base. This is shown in Figure 4. The code for the heart of the loop nest (without

pre- and post-ambles) after these transformations is given in Figure 5. Figure 6 shows that the main memory transfers have been reduced with a factor of 2 due to the data flow transformations. No further reduction in array accesses has been achieved, since the loop transformations do not change this; they only increase the locality. As a result of that however,

MULTIMEDIA ALGORITHMS

105

GaussBlur

ComputeEdges

y2

DetectRoots

y-3 y-1

y-1

FIGURE 3 Cavity detection algorithm after y-loop transformation.

Incoming pixel

GaussBlur

ComputeEdges y-2 I:::l!i!

Computation

Neighbour pixels

Can be discarded now (So upper and lower line can be stored in the same line buffer.)

FIGURE 4 Cavity detection algorithm after x-loop transformation.

void cav_detect (uchar image_in[M] [N], uchar image_out [M] [N])

for (y=0; y<M; ++y) for (x=0; x<N; ++x) gauss_x[y] [x] =... // Apply horizontal gauss-blurring gauss_xy[y-l] [x] =... // Apply vertical gauss-blurring comp_edge[y-2] [x-l] =... // Replace pix. with max. diff. with neighbors image_out[y-3] [x-2] =... // true if no neighbors are < than curr. pix.

FIGURE 5 Cavity detection code after application of data-flow and loop transformations.

the cache misses and system bus load are significantly reduced, as shown in Figure 7.

3.3. Adding Hierarchical Data Reuse Copies

While the loop transformations increase the locality of the code, we have found that in many cases this locality is not optimally exploited by the cache hierarchy. To make the data reuse more explicit, we introduce additional variables (usually small arrays) into the code in a judicious way. In these variables, copies of parts of other variables (usually large arrays) are stored. The explicit addition of these variables is necessary to enforce

the data reuse decisions on the lower level stages of compilation. It is an alternative for relying on the HW cache controller which cannot make any global trade-offs at run-time. Many alternatives for these hierarchical copies are available. We have a systematic search strategy and a model which represents all promising alternatives [24]. That allows us to identify the best solution. For the cavity detection example, two levels of data reuse can be identified from the above figures which illustrate the loop transformations: line buffers and pixel buffers.

Line Buffers For each of the functions, a buffer of three lines can be implemented, in which the line

106

K. DANCKAERT et al.

Initial

Data-flow transftrmations

Loop transformations

,Main memory transfers

(frames)

Main

Data reuse (line buffers)

iData reuse (pixei buffers)

:memory size (frames x 5)

iLocal memo.ry transfers (frames)

In-place mapping

10

2.0

30

FIGURE 6 Array accesses and sizes, for image size of 1280

1000.

Data-flow transfoations

Loop transformations

data cache misses (K)

Data reuse (line buffers)

System bus transactions (K)

Data reuse (pixet buffers)

In-place mapping

Pixel bu.ffers in registers

200

400

600

800

1000

FIGURE 7 Cache and system bus results. Note that system bus transactions correspond + to L2 cache misses and write-backs.

MULTIMEDIA ALGORITHMS

107

being processed is stored, together with the previous and the next line:

The horizontal gauss-blurring is done on an incoming pixel, and the result is stored in the buffer gauss x lines. Next, the vertical gauss-blurring is performed (on one pixel) in this buffer, and the result stored in gauss_xy_lines. Then ComputeEdges() can be executed in that buffer, the result of which is stored in comp_edge_lines. Finally, DetectRootsO is executed in comp_edge_lines, and the resulting pixel stored in the output image. The resulting code for the heart of the loop nest

is given in Figure 8. Pixel Buffers

This buffer is used in ComputeEdgesO, and the result of that step is again stored in a three by three buffer, i.e., comp_edge_pixels. Finally, DetectRootsO is performed on this buffer, and the result stored in the output

image.

The resulting code is given in Figure 9 (again without initializations and pre- and post-ambles).

Results The results are given in Figure 6 again. This shows that the line buffers have a huge impact on the main memory size and transfers, while the pixel buffers reduce mainly the local memory transfers. In Figure 7, we can see that also the cache misses and system bus load are reduced by these steps. Note that the pixel buffers can actually be stored in registers; but they have to be implemented as scalar variables instead of arrays to allow the compiler to do this. However, this is only done at the end of our DTSE script (see Section 3.6), so the influence on cache misses and bus transactions is only visible at the end of Figure 7.

In Figure 4, we can see that a

second level of data reuse can be identified, i.e., the pixels in the neighborhood of the pixel being processed:

For the horizontal gauss-blurring, a buffer of three pixels in_pixels can be implemented, storing the last used values of the incoming image. For the vertical gauss-blurring, no such buffer is possible. However, the output of this step is stored into a three by three pixels buffer: gauss_xyixels.

3.4. Aggressive In-place Mapping

The aim of this step is to reduce the memory size by storing signals with different lifetimes in the same physical memory location. Conventionally memory reuse is only applied for variables with

void cav_detect (uchar image_in[M] [N], uchar image_out[M] [N])

uchar gauss x lines[3] IN], gauss_xy_lines[3] [N], comp_edge_lines[3] [N]

for (y=0; y<=M-l+3; ++y) for (x=0; x<=N-l+2; ++x) // Apply horizontal gauss-blurring gauss x lines [y % 3] [x] // Apply vertical gauss-blurring gauss_xy_lines (y-l) % 3 [x] // Replace with max. diff. comp_edge_lines (y-2) % 3] [x-l] // true if no neighbors are < than curr. pix. image_out [y-3] [x-2]

....

....

FIGURE 8 Cavity detection code after introducing line buffers.

108

K. DANCKAERT et al.

void cav_detect (uchar image_in[M] [N], uchar image_out[M] [N])

uchar gauss_x_lines 3 [N] gauss_xy_lines 3 [N] comp_edge_lines 3 [N] comp_edge_pixels [3 [3 gauss_xy_pixels [3 [3 uchar in_pixels 3

for (y=0; y<=M-l+3; ++y) for (x=0; x<=N-l+3; ++x) image_in[y] [x] in_pixels [x % 3] // Apply horizontal gauss-blurring gauss x lines [y % 3] [x-l] gauss_xy_pixels[ (y-l) % 3] (x-l) % 3] // Apply vert. gauss-blurring gauss_xy_lines (y-l) % 3] [x-l] comp_edge_pixels[ (y-2) % 3] (x-2) % 3] // Replace with max. diff. comp_edge_lines (y-2) % 3] [x-2] // true if no neighbors are < curr. pix. image_out [y-3] [x-3]

....

....

FIGURE 9 Cavity detection code after introducing pixel buffers.

different scopes. We apply aggressive in-place transformations also when arrays have partly overlapping lifetimes [7, 19,21]. The goal is to make the data fit better in the caches, such that capacity misses can be reduced.

1. Each set of 3 line buffers (e.g., gauss x lines[3][N]) can be reduced to 2 line buffers (e.g., gauss x lines[2][N]) and a few scalars (as illustrated in Fig. 4), because the array variables in the first and the last one have largely different life-times. The extra scalars are the few pixels in the current neighborhood computations, but these are in the pixel buffers anyway. 2. The input and output image buffer can be combined. Again these buffers as such do not have non-overlapping life-times, but most of the pixels in them do. The pixels for which this is not the case, are in the line buffers anyway.

The results of this step are given in Figures 6 and 7 again.

3.5. Main Memory Data Layout Optimization

techniques from [3, 5, 11, 15, 17] can be applied, but we also go further as described in [13]. There the reduction of the conflict misses is accomplished by storing arrays in memory in an interleaved way, based on cache parameters such as line size, associativity and cache size. Arrays with potential conflict misses are assigned to memory regions that will be mapped to different lines of the cache. Note that not only the starting address or the internal layout of an array is changed: the arrays are really cut in pieces and interleaved with each other. However, this technique is especially suited for embedded systems with small caches. After the previous optimizations of the cavity detection algorithm, the number of conflict misses is already minimal on the 512K 4-way L2-cache of the Pentium(R) II. Therefore, we have not included this step in the cumulative results of Figure 7. However, when applied on the initial version, the data layout step reduces both L1 misses and system bus transactions with about 20%.

3.6. Address and Loop Flow Related Optimizations (ADOPT)

In the next step of our DTSE script, the layout of

the data in main memory has to be chosen to reduce the cache conflict misses. In this step, the

Up to now, we have not given performance results for the above versions, because some DTSE stages make the array index expressions much more

MULTIMEDIA ALGORITHMS

109

TABLE

Initial

Performance results for cavity detection algorithm

Execution time

DTSE only DTSE + ADOPT

1.38 2.64 0.58

TABLE II Results for two other applications

Application

L1 misses

QSDPCM (initial) QSDPCM (DTSE + ADOPT) Voice coder (initial) Voice coder (DTSE + ADOPT)

332 K 72 K 96 K 40 K

System bus trans. 370 K 65 K 70 K 13 K

Execution time

5.15 2.74 0.013 0.006

complex, and these have to be optimized again (e.g., by replacing modulo operations with counters). Also some conditions and more complex loop bounds were added, and these can be removed from the heart of the loop nest by a loop splitting operation. These optimizations are not really part of the DTSE methodology, but should be performed additionally to increase the performance. We have a systematic methodology for these optimizations too: ADOPT (ADdress OPTimizations) [16]. Note that, as part of these address optimizations, also the pixel buffers introduced in Section 3.3 are replaced by individual scalars (instead of arrays), such that the compiler can map them on registers.

3.6.1.

illustrate the methodology. In Table II, we give some results for two other applications: a Voice Coder, and a video compression algorithm based on motion estimation (QSDPCM) [18]. The table shows that we obtain good results for these applications too.

5. CURRENT STATUS

Performance Results

Table I gives the performance results for the Pentium(R) II target processor. The table shows that the complex addressing introduced by DTSE reduces the performance at first, but after removing this addressing overhead again, a clear performance gain w.r.t, the initial version is obtained.

It is not our goal to automate the DTSE methodology as a whole (this is not what designers want either). Rather, we want to develop a systematic methodology, with tools that automate some substeps, or help to select the best alternative. Currently we have prototype tools which apply the in-place mapping and data layout steps. For the data reuse step, we have a tool to represent all alternatives as a tree. Such a tree can be

constructed for each alternative which results from the data-flow and loop transformation step. This makes it convenient for a designer to select the best alternative. Throughout the design process, our ATOMIUM access counting tool can be used to identify the (remaining) bottlenecks.

4. OTHER EXPERIMENTAL RESULTS

6. CONCLUSION

The cavity detection is a very regular application, which lends itself very well to the DTSE optimizations. That is why we have used it in this paper to

In embedded multimedia systems, the energy consumption and performance bottlenecks are

110

K. DANCKAERT et al.

mostly in the system bus load and off-chip memory accesses (instead of the CPU) nowadays. In this paper, we have demonstrated a systematic code rewriting methodology, partly supported by tools, to optimally exploit the memory hierarchy and reduce the system bus load for these applications. The approach is valid for both programmable and custom hardware realizations. Here, we have illustrated the methodology on a cavity detection application for medical imaging, with a programmable processor (Pentium(R) II) as target architecture. The result is a large saving in the system bus load. The CPU performance improvement is also very significant, but it is smaller than the system bus load reduction.

[9] Feautrier, P. (1992). "Some efficient solutions to the affine scheduling problem", Int. J. of Parallel Programming, 21(5), 389-420. [10] Gonzales, R. and Horowitz, M., "Energy dissipation in general-purpose microprocessors", IEEE J. of Solid-state Circ., SC-31(9), 1277-1283, September, 1996. [11] Kandemir, M., Choudhary, A., Ramanujam, J., Shenoy, N. and Banerjee, P., "Enhancing spatial locality via data layout optimizations", Proc. Euro-Par Conference, Southampton, UK, Sep. 1998. "Lecture Notes in Computer Science" series, 1470, 422-434. [12] Kelly, W. and Pugh, W., "A framework for unifying

reordering transformations", Technical report CS-TR3193, Dept. of CS, Univ. of Maryland, College Park, April, 1993. Kulkarni, C., Catthoor, F. and De Man, H., "Advanced data layout organization for multi-media applications", Int. Parallel and Distr. Proc. Symp. (IPDPS), Workshop on "Parallel and Distrib. Computing in Image Proc., Video Proc., and Multimedia (PDIVM2000)", Cancun, Mexico, May, 2000. Lippens, P., van Meerbergen, J., Verhaegh, W. and van der Werf, A., "Allocation of multiport memories for hierarchical data streams", Proc. IEEE Int. Conf. Comp. Aided Design, Santa Clara CA, Nov., 1993. Manjiakian, N. and Abdelrahman, T., "Array data layout for reduction of cache conflicts", Int. Conf. on Parallel and Distributed Computing Systems, 1995. Miranda, M., Catthoor, F., Janssen, M. and De Man, H., "High-level address optimization and synthesis techniques for data-transfer intensive applications", IEEE Trans. on VLSI Systems, 6(4), 677-686, December, 1998. Rivera, G. and Tseng, C., "Data transformations for eliminating conflict misses", Proe. A CM SIGPLAN Conf. on Programming Language Design and Implementation (PLDI), pp. 38-49, Montreal, Canada, June, 1998. Strobach, P. (1988). "QSDPCM-A New Technique in Scene Adaptive Coding," Proc. 4th Eur. Signal Processing Conf., EUSIPCO-88, Grenoble, France, Elsevier Publ., Amsterdam, pp. 1141 1144. Strout, M., Carter, L., Ferrante, J. and Simon, B., "Schedule-independent storage mapping for loops", Proc. ASPLOS-VIII, pp. 24-33, San Jose CA, Oct., 1998. Tiwari, V., Malik, S. and Wolfe, A., "Power analysis of embedded software: a first step towards software power minimization", IEEE Trans. on VLSI Systems, 2(4), 437-445, December, 1994. Wilde, D. and Rajopadhye, S., "Memory reuse analysis in the polyhedral model", Proc. Euro-Par Conf., Lyon, France, Aug. 1996. Lecture Notes in Computer Science, 1123, 389-397, Springer, 1996. Wolf, M., "Improving locality and parallelism in nested loops", Ph.D. Dissertation, Aug., 1992. Wuytack, S., Catthoor, F., Nachtergaele, L. and De Man, H., "Power exploration for data dominated video applications", Proc. IEEE Intnl. Symp. on Low Power Design, Monterey CA, pp. 359-364, August, 1996. Wuytack, S., Diguet, J. P., Catthoor, F. and De Man, H., "Formalized methodology for data reuse exploration for low-power hierarchical memory mappings", IEEE Trans. on VLSI Systems, 6(4), 529-537, December, 1998.

[13]

[14]

References

[1] Amarasinghe, S., Anderson, J., Lam, M. and Tseng, C., "The SUIF compiler for scalable parallel machines", In: Proc. of the 7th SlAM Conf. on Parallel Proc. for Scientific [2]

Computing, 1995. Bister, M., Taeymans, Y. and Cornelis, J. (1989). "Automatic segmentation of cardiac MR images", Computers in Cardiology, IEEE Computer Society Press, pp. 215-218. Calder, B., Krintz, C., John, S. and Austin, T., "Cacheconscious data placement", Proc. ASPLOS- VIII, pp. 139-149, San Jose CA, Oct., 1998. Catthoor, F., Wuytack, S., De Greef, E., Franssen, F., Nachtergaele, L. and De Man, H. (1998). "System level transformations for low power data transfer and storage", In: Paper collection on "Low power CMOS design" (Eds. Chandrakasan, A. and Brodersen, R.), IEEE Press, pp. 609- 618. Chatterjee, S., Jain, V., Lebeck, A., Mundhra, S. and Thottethodi, M., "Nonlinear array layouts for hierarchical memory systems", Proc. A CM Int. Conf. on Supercomputing (ICS), Rhodes, Greece, June, 1999. Danckaert, K., Catthoor, F. and De Man, H., "System level memory optimization for hardware-software co-design", Proc. IEEE Intnl. Workshop on Hardware/ Software Co-design, pp. 55-59, Braunschweig, Germany, March, 1997. De Greef, E., Catthoor, F. and De Man, H., "Memory size reduction through storage order optimization for embedded parallel multimedia applications", special issue on "Parallel Processing and Multi-media" (Ed. Krikelis, A.), In: Parallel Computing Elsevier, 23(12), December, 1997.

tecture-driven synthesis techniques for VLSI implementation of DSP algorithms", Proc. of the IEEE, special issue on "The Future of Computer-aided Design", 78(2), 319-335, February, 1990.

[15] [16]

[17]

[3] [4]

[18]

[19]

[20]

[5]

[6]

[21]

[7]

[22]

[23]

[8] De Man, H., Catthoor, F., Goossens, G., Vanhoof, J., Van Meerbergen, J., Note, S. and Huisken, J., "Archi-

[24]

MULTIMEDIA ALGORITHMS

111

Authors Biographies

Hugo J. De Man received the electrical engineering

degree and the Ph.D. degree in Applied Sciences from the K.U. Leuven, Belgium, in 1964 and 1968, respectively. In 1974 he became a Professor at the University of Leuven. He received Best Paper Awards at the 1973 ISSCC, the 1981 ESSCIRC, and the 1989 DAC. From 1984 to 1995 he was Vice-President of the VLSI systems design group of IMEC (Leuven, Belgium), where the actual field of this research division is design methodologies for Integrated Systems for telecommunication. In 1999 he was awarded the Phil Kaufman Award by the EDA Consortium. Since 1995 he became a Senior Research Fellow of IMEC. Vivek Tiwari received a B. Tech degree in Computer Science and Engineering from the Indian Institute of Technology in 1991, and a Ph.D. in Electrical Engineering from Princeton University in 1996. He is currently managing the Low Power Design Technology group at Intel Corp. The charter of the group is to reduce power in Intels high-end microprocessors. The focus of his current research is on tools and microarchitectural techniques for power reduction. He received the IBM Fellowship in 1993, 1994 and 1995 and a Best Paper Award at ASP-DAC 95. He has served on the technical program committees of DAC, ISLPED and VLSI Design.

Koen Danckaert was born in 1972 in Ghent, Belgium. He received the engineering degree in computer science from the Katholieke Universiteit Leuven, Belgium in 1995. Since October 1995 he has been working towards a Ph.D. degree at the Inter-university Micro-Electronics Center (IMEC), Leuven, Belgium. He is supported by a fellowship of the Fund of Scientific Research-Flanders. His current research interests are global data transfer and storage exploration for (parallel) multi-media processors, mainly targeted to image and video processing applications. Francky Catthoor received the Eng. degree and a Ph.D. in El. Eng. from the K.U. Leuven, Belgium in 1982 and 1987 respectively. Since 1987, he has headed research domains in the area of architectural and synthesis methodologies, within the DESICS division at IMEC. He is assistant professor at the EE department of the K.U. Leuven. Since 1995 he is an associate editor for the IEEE Trans. on VLSI Systems and since 1996 also for the Journal of VLSI Signal Processing. His research activities mainly belong to the field of application-specific architecture design methods and system-level exploration, with emphasis on memory and global data transfers.

Control Science and Engineering

Journal of

International Journal of

Rotating Machinery

The Scientific World Journal

Hindawi Publishing Corporation http://www.hindawi.com Volume 2014

Robotics

Hindawi Publishing Corporation http://www.hindawi.com Volume 2014

Journal of

Hindawi Publishing Corporation http://www.hindawi.com

Mechanical Engineering

Volume 2014

Hindawi Publishing Corporation http://www.hindawi.com Volume 2014

Advances in

Hindawi Publishing Corporation http://www.hindawi.com

Volume 2014

Engineering

Journal of

Hindawi Publishing Corporation http://www.hindawi.com Volume 2014

Chemical Engineering

Hindawi Publishing Corporation http://www.hindawi.com Volume 2014

International Journal of

Submit your manuscripts at http://www.hindawi.com

Distributed Sensor Networks

Hindawi Publishing Corporation http://www.hindawi.com Volume 2014

International Journal of

Civil Engineering

Hindawi Publishing Corporation http://www.hindawi.com Volume 2014

Advances in

VLSI Design

Advances in OptoElectronics

Navigation and Observation

International Journal of

Advances in Acoustics & Vibration

Modelling & Simulation in Engineering

Hindawi Publishing Corporation http://www.hindawi.com

Volume 2014

Hindawi Publishing Corporation http://www.hindawi.com

Hindawi Publishing Corporation http://www.hindawi.com

Volume 2014

Volume 2014

Hindawi Publishing Corporation http://www.hindawi.com

Volume 2014

Hindawi Publishing Corporation http://www.hindawi.com

Volume 2014

Active and Passive Electronic Components

International Journal of

Antennas and Propagation

Journalof

Hindawi Publishing Corporation http://www.hindawi.com

Sensors

Volume 2014

Hindawi Publishing Corporation http://www.hindawi.com Volume 2014

Shock and Vibration

Hindawi Publishing Corporation http://www.hindawi.com Volume 2014

Electrical and Computer Engineering

Hindawi Publishing Corporation http://www.hindawi.com Volume 2014

Journal of

Hindawi Publishing Corporation http://www.hindawi.com

Volume 2014

Das könnte Ihnen auch gefallen

- Pal A Charla 1997Dokument13 SeitenPal A Charla 1997Gokul SubramaniNoch keine Bewertungen

- A 1 TOPS - W Analog Deep Machine-Learning Engine With Floating-Gate Storage in 0.13 Μm CMOSDokument12 SeitenA 1 TOPS - W Analog Deep Machine-Learning Engine With Floating-Gate Storage in 0.13 Μm CMOSKjfsa TuNoch keine Bewertungen

- Efficient Storage and Processing of High-Volume Network Monitoring DataDokument14 SeitenEfficient Storage and Processing of High-Volume Network Monitoring DataNamith DevadigaNoch keine Bewertungen

- Data Placement and Duplication For Embedded Multicore Systems With Scratch Pad MemoryDokument9 SeitenData Placement and Duplication For Embedded Multicore Systems With Scratch Pad MemoryAjay TaradeNoch keine Bewertungen

- Stack Cache Memory Improves Performance by Prefetching Stack DataDokument9 SeitenStack Cache Memory Improves Performance by Prefetching Stack DataNandan Kumar JhaNoch keine Bewertungen

- 10.Data-Driven Design of Fog Computing AidedDokument5 Seiten10.Data-Driven Design of Fog Computing AidedVenky Naidu BalineniNoch keine Bewertungen

- Report On Mpsoc'04: Students' Summary of Lectures Xi ChenDokument45 SeitenReport On Mpsoc'04: Students' Summary of Lectures Xi ChenRachana SrinivasNoch keine Bewertungen

- Implications of Cache Management in Partitioned SystemsDokument5 SeitenImplications of Cache Management in Partitioned SystemsSam RedNoch keine Bewertungen

- Ipdps2018 DTPDokument10 SeitenIpdps2018 DTPPascal UlrichNoch keine Bewertungen

- stanley assignmentDokument6 Seitenstanley assignmentTimsonNoch keine Bewertungen

- Overcoming Computational Errors in Sensing Platforms Through Embedded Machine-Learning KernelsDokument12 SeitenOvercoming Computational Errors in Sensing Platforms Through Embedded Machine-Learning KernelsctorreshhNoch keine Bewertungen

- STL For Large Data ManagementDokument51 SeitenSTL For Large Data Managementmanoj-kumar-jainNoch keine Bewertungen

- Strategy_for_power_efficient_design_of_pDokument8 SeitenStrategy_for_power_efficient_design_of_psingarayyaswamyNoch keine Bewertungen

- Chap2 SlidesDokument127 SeitenChap2 SlidesDhara RajputNoch keine Bewertungen

- Detecting Bottlenecks in Parallel DAG-based Data Flow ProgramsDokument10 SeitenDetecting Bottlenecks in Parallel DAG-based Data Flow Programsanudhull1910Noch keine Bewertungen

- M. Dasigenis, N. Kroupis, A. Argyriou, K. Tatas, D. Soudris N. ZervasDokument4 SeitenM. Dasigenis, N. Kroupis, A. Argyriou, K. Tatas, D. Soudris N. ZervasSurya VarunNoch keine Bewertungen

- Packet Classification Speed on Multi-Core PlatformsDokument8 SeitenPacket Classification Speed on Multi-Core PlatformsSudhakar SpartanNoch keine Bewertungen

- Coding and Cell-Loss Recovery in DCT-Based Packet VideoDokument11 SeitenCoding and Cell-Loss Recovery in DCT-Based Packet VideoamironlineNoch keine Bewertungen

- Dagatan Nino PRDokument12 SeitenDagatan Nino PRdagatan.ninoNoch keine Bewertungen

- Article88 Analysis Limited Migrative ModelDokument12 SeitenArticle88 Analysis Limited Migrative ModelhelinNoch keine Bewertungen

- Performance Evaluation of Overload Control in Multi-Cluster GridsDokument8 SeitenPerformance Evaluation of Overload Control in Multi-Cluster GridsMike GordonNoch keine Bewertungen

- An Embedded Merging Scheme For H.264/Avc Motion Estimation: Chztun-Yu Cho, Shiung-Yang Huung Andjiu-Shung WangDokument4 SeitenAn Embedded Merging Scheme For H.264/Avc Motion Estimation: Chztun-Yu Cho, Shiung-Yang Huung Andjiu-Shung WangDam Minh TungNoch keine Bewertungen

- Discrete Event SimulationDokument140 SeitenDiscrete Event Simulationssfofo100% (1)

- Hardware-Based Job Queue Management For Manycore Architectures and Openmp EnvironmentsDokument12 SeitenHardware-Based Job Queue Management For Manycore Architectures and Openmp EnvironmentsManali BhutiyaniNoch keine Bewertungen

- A Failure Handling Framework For Distributed Data Mining Services On The GridDokument10 SeitenA Failure Handling Framework For Distributed Data Mining Services On The GridJustin HeNoch keine Bewertungen

- Im Improving Memory Proving Space Utilization in Multi-Core Embedded Systems Using Task RecomputationDokument9 SeitenIm Improving Memory Proving Space Utilization in Multi-Core Embedded Systems Using Task RecomputationijcsnNoch keine Bewertungen

- Adriatic Paper FPL-2004Dokument5 SeitenAdriatic Paper FPL-2004prathap13Noch keine Bewertungen

- Yield-Oriented Evaluation Methodology of Network-on-Chip Routing ImplementationsDokument6 SeitenYield-Oriented Evaluation Methodology of Network-on-Chip Routing Implementationsxcmk5773369nargesNoch keine Bewertungen

- Project Report KumarDokument63 SeitenProject Report KumarKumar GolletiNoch keine Bewertungen

- Clustering Clickstream Data with a Three-Phase FrameworkDokument11 SeitenClustering Clickstream Data with a Three-Phase FrameworkPPMPhilNoch keine Bewertungen

- High-Performance Linux Cluster Monitoring Using Java: Curtis Smith and David Henry Linux Networx, IncDokument14 SeitenHigh-Performance Linux Cluster Monitoring Using Java: Curtis Smith and David Henry Linux Networx, IncFabryziani Ibrahim Asy Sya'baniNoch keine Bewertungen

- A Survey On Cache Management Mechanisms For Real-Time Embedded SystemsDokument35 SeitenA Survey On Cache Management Mechanisms For Real-Time Embedded SystemsAtulNoch keine Bewertungen

- Dynamic Data Management AmongDokument11 SeitenDynamic Data Management AmongCS & ITNoch keine Bewertungen

- 9 Challenges 2013Dokument9 Seiten9 Challenges 2013sajjad moradiNoch keine Bewertungen

- Why Systolic ArchitectureDokument10 SeitenWhy Systolic ArchitectureSarthak GoyalNoch keine Bewertungen

- Kibabii University Computer Architecture II Assignment on Programmed vs Interrupt Driven I/O, RAID, and Instruction PipeliningDokument5 SeitenKibabii University Computer Architecture II Assignment on Programmed vs Interrupt Driven I/O, RAID, and Instruction PipeliningEtabo Moses KapusNoch keine Bewertungen

- Very High-Level Synthesis of Datapath and Control Structures For Reconfigurable Logic DevicesDokument5 SeitenVery High-Level Synthesis of Datapath and Control Structures For Reconfigurable Logic Devices8148593856Noch keine Bewertungen

- Vafeiadis2012 PDFDokument8 SeitenVafeiadis2012 PDFعمار طعمةNoch keine Bewertungen

- Formal Verification of Distributed Dynamic Thermal ManagementDokument8 SeitenFormal Verification of Distributed Dynamic Thermal ManagementFaiq Khalid LodhiNoch keine Bewertungen

- Vin-Load Balancing On GridDokument19 SeitenVin-Load Balancing On GridinterestingscribdNoch keine Bewertungen

- Single Producer - Multiple Consumers Ring Buffer Data Distribution System With Memory ManagementDokument12 SeitenSingle Producer - Multiple Consumers Ring Buffer Data Distribution System With Memory ManagementCarlosHENoch keine Bewertungen

- DC AssignmentDokument3 SeitenDC AssignmentChandra SinghNoch keine Bewertungen

- Three Level Benchmarking of Singularity Containers For Scientific CalculationsDokument14 SeitenThree Level Benchmarking of Singularity Containers For Scientific CalculationsPolgár PéterNoch keine Bewertungen

- Intelligent Co-Operative PIM Architecture For Image Analysis and Pattern RecognitionDokument5 SeitenIntelligent Co-Operative PIM Architecture For Image Analysis and Pattern RecognitionAsim Rafiq JanjuaNoch keine Bewertungen

- R-Much: A Clustering Routing Algorithm Using Fuzzy Logic For WsnsDokument13 SeitenR-Much: A Clustering Routing Algorithm Using Fuzzy Logic For WsnsSami FarhatNoch keine Bewertungen

- Term Paper On Embedded SystemsDokument7 SeitenTerm Paper On Embedded Systemsaflsbbesq100% (1)

- Data Similarity-Aware Computation Infrastructure For The CloudDokument14 SeitenData Similarity-Aware Computation Infrastructure For The CloudAjay TaradeNoch keine Bewertungen

- Digital Design Using VHDL: Topic: Huffman Decoder Using VerilogDokument14 SeitenDigital Design Using VHDL: Topic: Huffman Decoder Using VerilogTùng Lâm VũNoch keine Bewertungen

- Processes: Distributed Systems Principles and ParadigmsDokument78 SeitenProcesses: Distributed Systems Principles and ParadigmsZain HamzaNoch keine Bewertungen

- Week 5 - The Impact of Multi-Core Computing On Computational OptimizationDokument11 SeitenWeek 5 - The Impact of Multi-Core Computing On Computational OptimizationGame AccountNoch keine Bewertungen

- Efficient Lossless and Lossy Image Compression via Two-Layered Wavelet AlgorithmDokument5 SeitenEfficient Lossless and Lossy Image Compression via Two-Layered Wavelet AlgorithmRajesh KulasekaranNoch keine Bewertungen

- EALARM: Enhanced Autonomic Load-Aware Resource Management For P2P Key-Value Storage in CloudDokument6 SeitenEALARM: Enhanced Autonomic Load-Aware Resource Management For P2P Key-Value Storage in CloudJames SmithNoch keine Bewertungen

- 8516cnc05 PDFDokument14 Seiten8516cnc05 PDFAIRCC - IJCNCNoch keine Bewertungen

- WSN ClusteringDokument6 SeitenWSN ClusteringSiddharth KumarNoch keine Bewertungen

- IMAGE COMPRESSION AND DECOMPRESSION SYSTEM USING RUN LENGTH ENCODING ALGORITHM (Chapter 1-3)Dokument18 SeitenIMAGE COMPRESSION AND DECOMPRESSION SYSTEM USING RUN LENGTH ENCODING ALGORITHM (Chapter 1-3)femiNoch keine Bewertungen

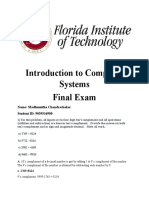

- Introduction to Computer Systems Final ExamDokument30 SeitenIntroduction to Computer Systems Final ExamMadhumitha Chandra shakerNoch keine Bewertungen

- MICROCONTROLLERS AND MICROPROCESSORS SYSTEMS DESIGN - ChapterDokument12 SeitenMICROCONTROLLERS AND MICROPROCESSORS SYSTEMS DESIGN - Chapteralice katenjeleNoch keine Bewertungen

- The Performance of Bags-of-Tasks in Large-Scale Distributed SystemsDokument12 SeitenThe Performance of Bags-of-Tasks in Large-Scale Distributed SystemsRafael BragaNoch keine Bewertungen

- Design and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesVon EverandDesign and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesNoch keine Bewertungen

- Seminar ON Intelligent RamDokument37 SeitenSeminar ON Intelligent RamSurangma ParasharNoch keine Bewertungen

- Oslib RMDokument157 SeitenOslib RMRakesh KhannaNoch keine Bewertungen

- Network Interface Data CachingDokument15 SeitenNetwork Interface Data CachingBobby LukkaNoch keine Bewertungen

- Question Bank Unit-I 2 MarksDokument6 SeitenQuestion Bank Unit-I 2 MarksSathya MuraliNoch keine Bewertungen

- 2483 Console Commands For CS GoDokument63 Seiten2483 Console Commands For CS GoJuan Carlos Álvarez AcostaNoch keine Bewertungen

- Cassandra Read-Write Path by Josh McKenzieDokument51 SeitenCassandra Read-Write Path by Josh McKenzieRajul SrivastavaNoch keine Bewertungen

- Rank TransformationDokument5 SeitenRank TransformationMallikarjun RaoNoch keine Bewertungen

- CodaDokument25 SeitenCodamourya_chandraNoch keine Bewertungen

- SS ZG516 HandoutDokument4 SeitenSS ZG516 HandoutManjunath PatelappaNoch keine Bewertungen

- M.Tech VLSI Question PaperDokument46 SeitenM.Tech VLSI Question PaperRamRatanKumarNoch keine Bewertungen

- Final ReportDokument40 SeitenFinal ReportAlanoud AlsalmanNoch keine Bewertungen

- Cache Organization (Direct Mapping)Dokument40 SeitenCache Organization (Direct Mapping)ankesh45Noch keine Bewertungen

- CPSC 457 Operating Systems Final Exam SolutionDokument11 SeitenCPSC 457 Operating Systems Final Exam SolutionmuanaserNoch keine Bewertungen

- Comp Arch Ch1 Ch2 Ch3 Ch4Dokument161 SeitenComp Arch Ch1 Ch2 Ch3 Ch4Patricia Jane PerezNoch keine Bewertungen

- Supguide PDFDokument116 SeitenSupguide PDFPedro Osorio G.Noch keine Bewertungen

- Symmetrix Foundations Student Resource GuideDokument50 SeitenSymmetrix Foundations Student Resource GuideJames PeterNoch keine Bewertungen

- Symmetrix 3000 and 5000Dokument34 SeitenSymmetrix 3000 and 5000Billc100% (1)

- ARM946E-S: Technical Reference ManualDokument218 SeitenARM946E-S: Technical Reference Manualvsc2012Noch keine Bewertungen

- Ccboot - Iscsi Boot Windows 7 Over NetworkDokument19 SeitenCcboot - Iscsi Boot Windows 7 Over NetworkEmmerNoch keine Bewertungen

- TuningDokument53 SeitenTuningbalajismithNoch keine Bewertungen

- Bcn1043 - Computer Architecture & OrganizationDokument4 SeitenBcn1043 - Computer Architecture & OrganizationYuku MashiNoch keine Bewertungen

- Intel Sandy Bridge Architecture PDFDokument54 SeitenIntel Sandy Bridge Architecture PDFUbaidullah JoyiaNoch keine Bewertungen

- ComputerScience EngineeringDokument52 SeitenComputerScience EngineeringdeepujobNoch keine Bewertungen

- Class11 CacheDokument41 SeitenClass11 Cacheef_irshadNoch keine Bewertungen

- CS 152 Computer Architecture and Engineering Lecture 7 - Memory Hierarchy-IIDokument27 SeitenCS 152 Computer Architecture and Engineering Lecture 7 - Memory Hierarchy-IIsam_almasryNoch keine Bewertungen

- HP 3PAR F-Class, T-Class, and StoreServ 10000 Storage Troubleshooting Guide PDFDokument130 SeitenHP 3PAR F-Class, T-Class, and StoreServ 10000 Storage Troubleshooting Guide PDFRobertPivacNoch keine Bewertungen

- Advanced Computer ArchitectureDokument8 SeitenAdvanced Computer Architecturett_aljobory3911Noch keine Bewertungen

- Cloud Design PatternsDokument236 SeitenCloud Design PatternsAraxhiel100% (3)

- The Architecture of Computer Hardware and Systems Software:: CPU and Memory: Design, Implementation, and EnhancementDokument42 SeitenThe Architecture of Computer Hardware and Systems Software:: CPU and Memory: Design, Implementation, and EnhancementWaqas AhmedNoch keine Bewertungen

- SPRING 2015 CDA 3101 Homework 3: Date-Assigned: Mar 27th, 2015 Due Dates: 11:55pm, April 7th, 2015Dokument5 SeitenSPRING 2015 CDA 3101 Homework 3: Date-Assigned: Mar 27th, 2015 Due Dates: 11:55pm, April 7th, 2015ayylmao kekNoch keine Bewertungen