Beruflich Dokumente

Kultur Dokumente

The Analysis and Compensation of Dead-Time Effects in PWM Inverters

Hochgeladen von

Swami KannuOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

The Analysis and Compensation of Dead-Time Effects in PWM Inverters

Hochgeladen von

Swami KannuCopyright:

Verfügbare Formate

108

IEEE TRANSACTlONS ON lNDUSTRlAL ELECTRONICS, VOL. 38, NO. 2, APRlL 1991

The Analysis and Compensation of Dead-Time Effects in PWM Inverters

Seung-Gi Jeong, Member, IEEE, and Min-Ho Park, Senior Member, IEEE

Abstract-In inverters, time delay is inserted in switching signals to prevent a short circuit in the dc link. This causes the dead-time effect, which is detrimental to the performance of inverters. This paper deals with the dead-time effect in pulse width modulated (PWM) inverters. Through the analysis and simulation, it is shown that the effect results in a decrease of the fundamental component and an increase in the low-order harmonics in the output voltage of the inverter. T o compensate the effect, two simple methods, which are adequate for sinusoidal PWM and memory-based PWM, are presented. The experimental results show the validity of the analysis and the usefulness of the compensation methods.

delay

I. INTRODUCTION

N RECENT years, the pulsewidth modulated (PWM) inverter has become one of the most popular power conversion apparatus. Considerable efforts have been devoted to improving the performance of PWM inverters in both the theoretical aspects [1]-[3] and the implementation of the control circuit [4]-[7]. As a result, versatile PWM techniques are now available and in use for various applications. It seems that most of the modulation techniques proposed so far are based on the assumption that the switching elements of the inverter operate in an ideal manner, that is, they switch on or off exactly at the instants the control signal dictates. In reality, however, any solid-state switching device has a finite switching time, and the turn-off time of the device is of particular importance in most applications [8]. In inverters, the finite turn-off time may cause a short circuit of the dc link at the instant of switchover between the two elements connected in series across the dc link. Thus, it is essential to insert a time delay in control signals in order to avoid the conduction overlap of the elements. Although the time delay guarantees safe operation, it adversely affects the performance of the inverter. The time delay results in a momentary loss of control, and the inverter output voltage waveform deviates from that for which it is originally intended. Since this is repeated over and over for every switching operation, its detrimental effect may become significant in PWM inverters that operate in high switching frequency. This is known as the dead-time effect. Recently developed fast switching devices such as MOSFET, SIT, IGBT, etc., do not necessarily improve the situation because using them generally implies quite high switching frequency, and the cumulative effect of the time delay remains essentially the same. Therefore, irrelevant to the switching device to be used, a thorough understanding of the dead-time effect is important in improving the performance of PWM inverters. The subject of this paper is first the quantitative prediction and

Manuscript received August 29, 1989; revised October 9, 1990. S. -G. Jeong is with the Department of Electrical Engineering, Kwangwmn University, Seoul, Korea. M. -H. Park is with the Department of Electrical Engineering, Seoul National University, Seoul, Korea. IEEE Log Number 9142813.

PWM

signal

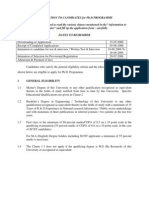

Fig. 1. Basic configuration of PWM inverter (only one phase leg is shown).

second the development of compensation methods of the deadtime effect. Simple formulae that represent the dead-time effect are derived, and two compensation methods are proposed. It is shown that the dead-time effect is strongly dependent on the load power factor and can be compensated through a slight modification of the control circuit with current feedback.

11. DEAD-TIME EFFECT IN PWM INVERTER

A. Operation with Time Delay Fig. 1 shows the leg of one phase of the PWM inverter, where power transistors are assumed to be used as switching elements. The PWM control signal drives the transistors through the time delay circuit. The base drive signals B1 and B2 for the transistors T1 and T 2 , respectively, are illustrated in Fig. 2 , where the rising edges of the drive signals are delayed by the delay time Td from the ideal signals, which are shown by broken lines. During the delay time, both transistors cease to conduct, and the output terminal A seems to be floating. However, if the output current i is continuous, as is normally the case, the current then flows throughthe freewheeling diodes 0 1 or 0 2 . Which one of the diodes will conduct depends on the direction of the current flow. When the current flows toward the load ( i > 0, according to the convention in Fig. l), the diode 0 2 conducts, and negative voltage will appear at the output terminal. In addition, for the current flowing toward the inverter, the positive voltage appears at the output through D1. As a result, neglecting the reverse storage time of the transistor, the output voltage deviates from an ideal PWM waveform by the amount of shaded areas in Fig. 2 . Obviously, during the delay time, the output voltage cannot be controlled by drive signals but is determined by the load condition, that is, the direction of the current flow. Although the load condition is subject to change, it can always be said that the

01991 IEEE

0278-0046/91/0400-0108$01.00

JEONG AND PARK: ANALYSIS AND COMPENSATION OF DEAD-TIME EFFECTS

109

increasing

VANfor i < 0

JV

Fig. 2. Delayed drive signals and corresponding output voltage

voltage deviation due to the time delay opposes the current flow in either direction. Thus, the voltage deviation makes the magnitude of the current be smaller than expected. This in turn implies one of the important effects of the time delay; the decrease in the effective output voltage of the inverter. Another important effect is concerned with the harmonics. For each pulse of the output voltage, the voltage deviation shortens or lengthens the pulse duration according to the current direction, and the output voltage cannot be the same with the original PWM control signal. As a natural consequence, there appear undesirable harmonic components in the output voltage, which cause overall distortion of the inverter output waveforms.

(b)

Fig. 3 .

Dead-time effect on fundamental output voltage.

B. Analysis

To evaluate the dead-time effect quantitatively, following assumptions are to be made: 1) The reverse storage time of the switching elements is not considered. 2) The switching frequency, compared with the fundamental output frequency, is sufficiently large. 3) The voltage deviation occurs nearly equidistantly. 4) Short pulse dropping does not occur. 5 ) Output current of the inverter is nearly sinusoidal. With these assumptions, the cumulative effect of the repetative time delays (the dead-time effect) can be evaluated by averaging voltage deviations over each positive and negative half cycle of the current. Since the deviation for each pulse A e is measured by (see Fig. 2) A e = Tdvd the average voltage deviation over a half cycle of the inverter output AV is given by

AV=

4i,

Fig. 4. Phasor representation of Fig. 3.

respect to dc link voltage is equivalent to the ratio of the total dead time to the length of one cycle. Fig. 3 describes how the average voltage deviation appears in the waveform of the inverter output voltage. In the figure, uref represents the ideal fundamental output voltage of the inverter that would result if there was no dead-time effect. If the inverter feeds an inductive load, the current waveform then lags behind urCf by an angle 4'. Since the dead time increases (decreases) the inverter output voltage for the negative (positive) half cycle of the current, the average voltage deviation over an entire cycle can be represented by Fig. 3(b) as the square wave Au, which is 180" out of phase with the current. The magnitude of the square wave is A V , which is given by (1). Let Au be the fundamental component of voltage deviation. Then, its rms magnitude AVl is given by

AVl

=

( M / 2 )A e

TI2

AV.

'R

or

AV=-V, T

MTd

where

V, magnitude of dc link voltage M number of switching per one cycle T length of one cycle.

In (l), MT, is the total sum of the time delay over the cycle. Thus, it can be said that the average voltage deviation with

The resultant effect of the dead time is the superposition of Au on the ideal voltage uref, as is represented by broken line in Fig. 3(a). Consequently, the fundamental output voltage with dead time u 1 is the sum of uref and A V , , which is plotted as a heavy solid curve. If the harmonic components of the current are neglected (assumption 5 ) , the phase displacement 4 between u 1 and i corresponds to the fundamental power factor angle of the load. It should be noted that the resultant fundamental output voltage differs from the reference wave in both the magnitude and phase. The above relationships are described in the phasor diagram shown in Fig. 4. In the phasor diagram, AVl is in opposite

110

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 38, NO. 2, APRIL 1991

phase to the current. Since the resultant voltage,v, leads the current by 4, the phase difference between AV, and VI is T - 4. Applying a trigonometrical identity to the triangle composed of the sides A VI and VI, the following quadratic equation for the unknown variable VI is obtained:

P $

= AV:

+ V:

- 2AV,V,

COS ( T

4)

(3)

where V,, , AV,, and VI are the rms values of uref, Au U , , respectively. The solution of (3) is given by VI = -AV, cos 4

,, and

(4)

Jy:,

- (AV, sin

4)2

or in a normalized form with respect to

Kef

Ob

A . 2

0.4

0.6

6

0.8

where

(a)

9 is the normalized voltage deviation and has the value 0

<9 <

1. Since AV, is constant for given M , T,, and V,, 9 is inversely proportional to Kef. This means that the relative voltage deviation effect is more significant for smaller inverter output voltage.

C. Dead-Time Eflect in Sinusoidal PWM

As an illustrative example, the dead-time effect on the subharmonk PWM inverter is described in the following. In sinusoidal subharmonic modulation [ 11, the theoretical fundamental rms output voltage of the inverter is given by

Kef = 6-

'd

0.2

(7)

30

60

90

120

d [des1

(b) Fig. 5. Variation of output voltage with respect to (a) modulation index and (b) load power factor angle.

where 6 is the modulation index, which is the magnitude ratio of the reference wave to the triangular carrier wave. By combining (l), (2), and (7) with (6), the normalized voltage deviation is expressed as

9 =

---. T

8 MT, 1

T ~

By substituting (8) into (3,the normalized fundamental output voltage under dead-time effect can be expressed as a function of the modulation index. The curves in Fig. 5(a) show the variations of the normalized output voltage for various power factor angles. As the modulation index decreases, the voltage continually decreases and reaches even to zero voltage, where the dead time effect completely cancels the fundamental output voltage. Irrespective of power factor angle, the zero-voltage point is reached at 17 = 1. From (8), the modulation index at zero voltage is given by

(9)

or

6 = -f,Td

where f , = M / T , which is the switching frequency of the inverter. Equations (9) and (10) offer an absolute lower limit of the output voltage control, which is of particular interest in

variable-voltage variable-frequency (VVVF) operation of the inverter. The effect of the power factor on the inverter performance can be examined in Fig. 4. Since the magnitude of AV, is constant for given switching frequency and time delay, the phasor VI moves along the circle shown in the figure as the load power factor angle varies. At the unity power factor, the output voltage becomes in phase with the reference voltage and reaches a minimum magnitude. Fig. 5(b) shows the effect of the power factor angle on the fundamental output voltage with respect to V,, ( = V, /2 which is the ideal output voltage at unity modulation index. As the power factor angle increases, the voltage drop becomes smaller. It is interesting that the voltage may exceed the reference voltage in regenerative operation (4 > 90"). However, generally speaking, a good power factor is bothersome on a viewpoint of voltage regulation of the inverter. To assure the validity of the analysis, detailed computer simulation has been executed. In Fig. 6, two typical simulated waveforms are shown with the harmonic spectrums of the output voltage. The effect of time delay can be observed clearly in the waveforms of the current, wherein the increasing rate is much less than the decreasing rate in both the positive and negative

a),

JEONG AND PARK: ANALYSIS AND COMPENSATION OF DEAD-TIME EFFECTS

111

!

Fig. 6. Waveforms of output voltage and current with harmonic spectrum of the output voltage for M = 40 and Td = 30 ~ s (a) : 6 = 0.5, $I = 60", (b) 6 = 0.4, $I = 30".

which is independent of output voltage and load. In Fig. 6, the envelope of the theoretical harmonics given by (1 1) is shown, which fits in well with the simulation result. It can be observed that the magnitude of the low-order harmonics remains unchanged in spite of the variation of the power factor angle and modulation index, as is expected. In the foregoing analysis, it has been assumed that the voltage deviation occurs equidistantly, but now, it should be pointed out that the assumption is not generally true because the pulsewidth is not uniform. According to the variation of pulsewidth, the distance from one voltage deviation to the next deviation smoothly varies throughout the cycle. This causes the frequency modulation effect, which appears as extended sidebands near the switching frequency. The magnitude of the sidebands is characterized by Bessel functions of the first kind [9]. Although it is interesting, this will not be discussed further because it has little significance in a practical viewpoint. The most troublesome aspect is concerned with the generation of low-order harmonics. When the output voltage is low, loworder harmonics become comparable with the fundamental component that makes the output waveform seriously distorted. The supression of low-order harmonics is very difficult. If the filter is employed, it necessarily becomes bulky and expensive. A bulky filter causes not only a large internal voltage drop but also poor dynamic response when the output voltage is controlled by a closed loop. This is of particular importance in constant-voltage constant-frequency (CVCF) power supply systems that are expected to yield the output of good quality.

111. COMPENSATION OF DEAD-TIME EFFECT

The above discussion clearly shows the detrimental effects of the time delay and the necessity of the compensation of the dead-time effect. In the following, two methods of compensation are presented. Since the dead-time effect is closely related to the load current, it would be natural to make use of the current feedback (more strictly, the feedback of current direction) for the compensation.

A . Method I-Modification of Reference Wave

directions. This is a consequence of the "reaction" of the time delay to the current flow, as is discussed in the first part of this section. For smaller modulation index and/or smaller power factor angle, the current tends to be discontinuous, as can be seen in Fig. 6(b). The harmonic spectrums show a significant decrease in the fundamental output voltage. The variations of the fundamental voltage taken from the simulation results are illustrated in Fig. 5. Close coincidence between the analytical results and the simulation results says that aforementioned assumptions are generally valid. When compared with the harmonic spectrum of an ideal waveform, the harmonic spectrum with dead time has two features: the presence of low-order harmonics and the extended sidebands near the switching frequency. The dead-time effect on the harmonic characteristics can easily be explained by referring to Fig. 3. The square wave in Fig. 3(b) is superimposed on the original PWM waveform. Thus, the inverter output voltage contains, in addition to the fundamental and switching frequency components, the characteristic harmonics of the square wave. The magnitude of the harmonics of the square wave is given by For the sinusoidal subharmonic PWM inverter, the most fundamental realization scheme is the direct comparison of a reference wave with a carrier wave. In such a system, the compensation of the dead-time effect is quite simply achieved by modifying the reference wave according to the direction of load current. The circuit in Fig. 7 shows the basic realization principle of the method. At the first stage of the circuit, a comparator detects the direction of the current. The output of the comparator has the shape of a square wave, which is then added to the reference to generate a modified reference wave. When the current flows toward the load (positive current), the reference is made more positive, and when the current flows toward the inverter (negative current), the reference is made more negative. By modifying the reference in such a manner, the average effect of the time delay shown in Fig. 3(b) is cancelled out, and the fundamental inverter output voltage follows the original reference wave. In Fig. 7, there are two variables to be adjusted-the gain and the offset of the square wave. The gain should be adjusted so that the magnitude of the square wave is the same with the average voltage deviation. Thus, for large time delay or high switching frequency, it is tuned to be large. For the system of variable switching frequency, which is often found in VVVF

I12

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 38, NO. 2, APRIL 1991

Gain adiust

Offset

adjust

-V b

U

Reference wave

W

Carrier wave

f0I

Fig. 7. Dead-time compensation circuit with modification of reference waveform. (a)

(b)

applications, it would be necessary of the gain to adapt the switching frequency. The offset adjust is included in consideration of unequal time delays of main power switches, which may result in an unbalance between the positive and negative voltage deviations. The limitation imposed on the circuit in Fig. 7 is that the circuit works on the sinusoidal PWM only, in particular, the direct comparison of the reference and carrier wave. However, the principle of the reference wave modification can be applied to any system based on the philosophy of subharmonic modulation. For example, in a microprocessor-based sinusoidal PWM [7], known as the regular PWM, the compensation can be realized through a minor modification of the software once the information on the current direction is available. In addition, it should be mentioned that the linear modulation range is somewhat sacrificed because the peak value of the reference wave is inevitably increased.

Fig. 8. Waveform synthesis for the compensation of dead-time effect: (a) Tp > 2 T d ; ( b )Tp < 2Td.

B 1

B2

B. Method 11- Compensation with Logic Circuit

Many PWM control strategies rely on the off-line precalculation of the switching patterns [2], [SI, which are usually kept in Fig. 9. Dead-time compensation circuit with logical combination. microelectronic memories. In such systems, there is no equivalency to the reference wave of subharmonic modulation, which makes it impossible to apply the modification of the reference i < 0, the inactive signal B1 rises at the rising edge of S2 and wave. Therefore, some other means of compensation is neces- falls at the falling edge of S, as is shown in Fig. 8(a), but when sary. the pulse width is shorter than twice the time delay, as in Fig. A close examination of Fig. 2 reveals the following observa- 8(b), B1 is dropped out. The current direction determines the set tions: For i > 0, the shape of the output voltage follows the base of drive signals that is to be selected. Then, the output voltage drive signal B1. On the other hand, for i < 0, the voltage is waveform will follow S1, which has the same shape as S, but shown to be a complementary shape of the signal B2. This will be delayed by Td, which does not matter practically. observation says that the output voltage is determined by only The synthesis of drive signals is achieved by logical combinaone of the two drive signals, which is called the active signal in tions of the signals S, S1, and S2 in conjunction with I , which the following, whereas the other one is said to be inactive. is the signal that represents the current direction. Let I be a Thus, in order to maintain the original pulse width of the control Boolean variable 1 when i > 0 and 0 when i < 0. A study on signal, the active drive signal should be made to be the same (or all possible cases for various pulse widths has shown that the inversely the same) as the control signal. The inactive drive relationships between the signals reduce to following simple signal needs only to be properly designed to guarantee the time formulae: delay with respect to given switching instants of the active signal. Fig. 8 shows the process of waveform synthesis. The signal S is assumed to be a portion of the original PWM wave. S 1 and Any reversal of current direction switches the drive signals s 2 are delayed signals of s, by Td and 2Td, respectively. The following waveforms show two sets of required drive signals B1 from one set to the other. However, in some intervals, the and B2 to be synthesized for positive and negative current, switchover may result in a time delay that is unsufficient to respectively. Note that the active side of the drive signals is complete the commutation. For example, consider the first intermade to be a replica (or an inverse replica) of SI. The other two val in Fig. 8(a), where (S, S1, S2) = (1,0,0). If the current signals S and S2 are used to define the transition edges of reverses direction from negative to positive during the interval, inactive side of drive signals. For example, under the condition B2 changes state from 1 to 0 instantaneously at the zero cross-

*-

JEONG AND PARK: ANALYSIS AND COMPENSATION OF DEAD-TIME EFFECTS

113

(b) Fig. 10. (a) Reference and current waveforms (horizontal 2 ms/div, vertical 2 V/div, and 5 A/div) and (b) frequency spectrum of output voltage from 0 to 5 lcHz (uncompensated).

(b)

Fig. 1 1 . (a) Reference and current waveforms (horizontal 2 ms/div, vertical 2 V/div, and 5 A/div) and (b) frequency spectrum of output voltage from 0 to 5 kHz (compensated by Method I).

ing, whereas B l remains 0. Soon after, B1 rises to 1 at the end of the interval before the sufficient time has elapsed, which may cause the short circuit of dc link. The upward and downward arrows in Fig. 8 indicate that the zero crossing of the current in such a direction should be avoided during the corresponding intervals. This can be achieved by allowing the signal Z to change state only on the intervals where ( S , S1, S 2 ) = (0,0,O) or (1, 1, 1). Fig. 9 shows a realization of (12). The D flip flop is used to latch the current direction signal during the intervals denoted by arrows. Delayed signals S1 and S 2 are generated through a shift register. However, in the memory-based PWM, where the signal S is stored in a bit of the memory, two adjacent bits, instead of the shift register, may be used to store the delayed signals. The circuit in Fig. 9 is simple and can be realized with only a few ICs. Moreover, since the circuit itself guarantees the time delay, the time delay element in Fig. 1 becomes unnecessary.

C. Experimental Results

The compensation circuits proposed are applied to a singlephase full-bridge transistor inverter that supplies an inductive load. In each leg of the inverter, two independent compensation circuits are implemented while they use a common current transformer for current feedback. The inverter operates on sinusoidal PWM, and the carrier frequency is 40 times the frequency of the reference ( M = 40). Fig. 10 (a) shows the

uncompensated reference and current waveforms. It can be observed that the current waveform is significantly distorted. The frequency spectrum of the output voltage is shown in Fig. 10 (b), which exhibits the low-order harmonics and extended sidebands near the dominant switching harmonics of the 79th and 81st order. Fig. 11 (a) shows the reference voltage and output current under the compensation of Method I . The reference has been modified according to the current direction so that the current overcome the reaction of the dead-time effect. When compared with Fig. 10 (a), the current waveform shows significant improvement in shape, as well as the increase in magnitude. These improvements are reflected in the frequency spectrum shown in Fig. 11 (b), wherein undesirable harmonics have disappeared, and the fundamental component has been increased. Method I1 compensation is realized with the circuit in Fig. 9. The PWM signal S is generated through a normal sinusoidal PWM circuit for comparison with Method I. Fig. 12 shows experimental results associated with Method 11. Although the reference wave is unchanged, the current waveform and the spectrum of the output voltage are similar to the ones in Fig. 11. However, it is observed that in Method 11, the magnitudes of the current and fundamental voltage are slightly greater than those with Method I. This is because Method I1 completely cancels the time delay, and the reverse recovery time that has been neglected so far now affects the output voltage in an opposite manner to the dead-time effect.

114

IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 38, NO. 2, APRIL 1991

compensation schemes -the modification of the reference wave and the logical combination of PWM signals. The former is adequate for subharmonic PWM and the latter for memory-based PWM. Of course, the latter method works well with any other modulation techniques including subharmonic PWM . In this regard, the method based on logical combination seems to be more general while it shows slight overcompensation. Nevertheless, both are simple and easy to implement. The only supplementary equipment they require is the current sensor, which need not be a high-performance one. There are many applications of the PWM inverter that inherently require current feedback. The compensation schemes proposed would be particularly suitable and readily applicable for such systems. Experimental results ensure the usefulness of the compensation methods. Although the pulse width modulation may be of a variety of realizations, the principle of the current feedback discussed in this paper will be useful for any type of modulation in compensating the dead-time effect or in improving the performance of the inverter.

REFERENCES

A. Schonung and H. Stemmler, Static frequency changers with subharmonic control in conjunction with reversible variable speed a.c. drives, Brown-Bovery Rev., vol. 51, pp. 555-577, Aug./Sept. 1964. H. S. Patel and R. G . Hoft, Generalized techniques of harmonic elimination and voltage control in thyristor inverters: Part I-Harmonic elimination, IEEE Trans. Industry Applications, vol. IA-9, pp. 310-317, May/June 1973. J. Hamman and F. S . Van Der Merwe, Voltage harmonics generated by voltage-fed inverters using PWM natural sampling, IEEE Trans. Power Electron. vol. PE-3, no. 3, pp. 297-302, July 1988. R. H. Green and J. T. Boys, Implementation of pulsewidth modulated inverter modulation strategies, IEEE Trans. Industry Applications, vol. IA-18, no. 2, pp. 138-145, Mar./Apr. 1983. G . S . Buja and G. B. Indri, Optimal pulsewidth modulation for feeding ac motors, IEEE Trans. Industry Applications, vol. LA-13, no. 1 , pp. 38-44, Jan./Feb. 1977. M. Varnovitsky , A microcomputer based control signal generator for a three-phase switching power inverter, IEEE Trans. Industry Applications, vol. IA-19, no. 2, pp. 228-234, Mar./Apr. 1983. S. R. Bowes and M. J. Mount, Microprocessor control of PWM inverters, Proc. Inst. Elec. Eng., vol. 128, pt. B, no. 6, pp. 293-305, NOV. 1981. R. L. Bonkowski, A technique for increasing power transistor switching frequency, IEEE Trans. Industry Applications, vol. IA-22, no. 2, pp. 240-243, Mar./Apr. 1986. G . Kennedy, Electronic Communication Systems (3rd ed.). New York: McGraw-Hill, 1984.

(b) Fig. 12. (a) Reference and current waveforms (horizontal 2 ms/div, vertical 2 V/div, and 5 A/div) and (b) frequency spectrum of output voltage from 0 to 5 kHz (compensated by Method 11).

IV. CONCLUSION

The switching time delay in a PWM inverter has a detrimental effect on inverter operation. It causes a decrease in the fundamental component and an increase in low-order harmonics. It has been shown that the effect is closely related to the phase (not the magnitude) of the output current. Analytical results show that the dead-time effect can be evaluated by averaging the voltage deviations. Simple formulae to predict the variation of fundamental voltage and the magnitude of low-order harmonics are derived and verified through simulation. In view of theoretical examinations, this paper presents two

Das könnte Ihnen auch gefallen

- A New Approach of Dead-Time Compensation For PWM Voltage InvertersDokument8 SeitenA New Approach of Dead-Time Compensation For PWM Voltage Invertersshankul.saurabhNoch keine Bewertungen

- Design Considerations For An Inverter Output Filter To Mitigate The Effects of Long Motor Leads IDokument8 SeitenDesign Considerations For An Inverter Output Filter To Mitigate The Effects of Long Motor Leads IJavier MaldonadoNoch keine Bewertungen

- A Novel Control Scheme of A ParallelDokument8 SeitenA Novel Control Scheme of A ParallelTetiHidayatiNoch keine Bewertungen

- Analysis and Design of Hysteretic Buck ConverterDokument6 SeitenAnalysis and Design of Hysteretic Buck ConverterRGinanjar Nur RahmatNoch keine Bewertungen

- D Single Phase Fully: Esign of Controlled Converter Using Cosine Wave Crossing Control With Various ProtectionsDokument6 SeitenD Single Phase Fully: Esign of Controlled Converter Using Cosine Wave Crossing Control With Various Protectionsঅর্ণব কোলেNoch keine Bewertungen

- Chopper Controlled DC Drive: INSTRUCTED BY: Dr. BuddhikaDokument8 SeitenChopper Controlled DC Drive: INSTRUCTED BY: Dr. BuddhikaNipuna Thushara WijesekaraNoch keine Bewertungen

- Electrical Drives: Lab ReportDokument17 SeitenElectrical Drives: Lab ReportJyoti KumariNoch keine Bewertungen

- An Improved Single Phase Full Bridge Inverter Using Sequential Triggering For Achieving Zero Voltage Without InductorDokument9 SeitenAn Improved Single Phase Full Bridge Inverter Using Sequential Triggering For Achieving Zero Voltage Without InductorAl MtdrsNoch keine Bewertungen

- Chopper Control DC Drive - 090075mDokument8 SeitenChopper Control DC Drive - 090075mIsuru Pasan Dasanayake100% (1)

- Effect of Dead-Time in Interleaved PWM For Two Parallel-Connected InvertersDokument8 SeitenEffect of Dead-Time in Interleaved PWM For Two Parallel-Connected Invertersnaseer m a abdul khadarNoch keine Bewertungen

- Doc-A.9-Driver Card For Single Phase Inverter Using Skhi22br PDFDokument66 SeitenDoc-A.9-Driver Card For Single Phase Inverter Using Skhi22br PDFsivananda11Noch keine Bewertungen

- LAB 13-PE-LabDokument6 SeitenLAB 13-PE-LabLovely JuttNoch keine Bewertungen

- Electrical - Ijeeer - Wavelet Modulated Z-SourceDokument10 SeitenElectrical - Ijeeer - Wavelet Modulated Z-SourceTJPRC PublicationsNoch keine Bewertungen

- 12 Moore Odavic CoxDokument15 Seiten12 Moore Odavic CoxTr NhNoch keine Bewertungen

- Active Cancellation of The Common-Mode Voltage Produced by A Voltage-Source PWM InverterDokument9 SeitenActive Cancellation of The Common-Mode Voltage Produced by A Voltage-Source PWM InverterSherif M. DabourNoch keine Bewertungen

- A New PWM DimmerDokument5 SeitenA New PWM DimmerNeeraj MuralidharanNoch keine Bewertungen

- Farhana Abdul Hamid 2020 J. Phys. Conf. Ser. 1432 012021Dokument10 SeitenFarhana Abdul Hamid 2020 J. Phys. Conf. Ser. 1432 012021Roger PerezNoch keine Bewertungen

- Digital Control of A Three Phase 4 Wire PWM Inverter For PVDokument9 SeitenDigital Control of A Three Phase 4 Wire PWM Inverter For PV7788778887Noch keine Bewertungen

- Q02201300137Dokument8 SeitenQ02201300137Vikas PatelNoch keine Bewertungen

- Analog Electronic WattmetrDokument2 SeitenAnalog Electronic WattmetrKaran AnejaNoch keine Bewertungen

- Copper Controlled DC Drive DenuDokument8 SeitenCopper Controlled DC Drive DenuDenuka PathiranaNoch keine Bewertungen

- A Review of Mitigation Methods For Overvoltage in Long-Cable-Fed PWM AC DrivesDokument7 SeitenA Review of Mitigation Methods For Overvoltage in Long-Cable-Fed PWM AC DrivesZaid RafiqueNoch keine Bewertungen

- Case Study of Sympathetic Interaction Between Transformers Caused by Inrush TransientsDokument5 SeitenCase Study of Sympathetic Interaction Between Transformers Caused by Inrush TransientsSven del PinoNoch keine Bewertungen

- Implementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationDokument6 SeitenImplementation of Single Stage Three Level Power Factor Correction AC-DC Converter With Phase Shift ModulationseventhsensegroupNoch keine Bewertungen

- A PWM Method for Reducing Switching LossesDokument7 SeitenA PWM Method for Reducing Switching Lossessiddhartha_anirban100% (1)

- A Voltage-Mode PWM Buck Regulator With End-Point PredictionDokument5 SeitenA Voltage-Mode PWM Buck Regulator With End-Point PredictionWen DwenNoch keine Bewertungen

- Elimination of Dead-Time in PWM Controlled Inverters: Lihua Chen and Fang Z. PengDokument4 SeitenElimination of Dead-Time in PWM Controlled Inverters: Lihua Chen and Fang Z. PengAlejandro Ospina0% (1)

- Resonant DC Link in PWM AC ChopperDokument5 SeitenResonant DC Link in PWM AC ChopperMukesh SharmaNoch keine Bewertungen

- A New Passive 28-Step Current Shaper For Three-Phase RectificationDokument8 SeitenA New Passive 28-Step Current Shaper For Three-Phase Rectificationkishor reddyNoch keine Bewertungen

- Single Phase Bridge VSIDokument13 SeitenSingle Phase Bridge VSIRajesh KumarNoch keine Bewertungen

- Unit - Iv Time Base GeneratorsDokument13 SeitenUnit - Iv Time Base GeneratorsAlapati RajasekharNoch keine Bewertungen

- Time Base GeneratorsDokument22 SeitenTime Base GeneratorsSanjana PulapaNoch keine Bewertungen

- DC Ripple Current Reduction On A Single-Phase PWM Voltage-Source RectifierDokument11 SeitenDC Ripple Current Reduction On A Single-Phase PWM Voltage-Source RectifierRajni YadavNoch keine Bewertungen

- SPWMDokument5 SeitenSPWMKiran Kumar NallamekalaNoch keine Bewertungen

- 60W Flyback TIDokument16 Seiten60W Flyback TIe_magazin3821Noch keine Bewertungen

- Switching Power Supply Design Review - 60 Watt Flyback Regulator by Raoji Patel and Glen FRFTZ Slup072Dokument17 SeitenSwitching Power Supply Design Review - 60 Watt Flyback Regulator by Raoji Patel and Glen FRFTZ Slup072Burlacu AndreiNoch keine Bewertungen

- Modified Space Vector Pulse Width Modulation For Modified Z-Source InverterDokument4 SeitenModified Space Vector Pulse Width Modulation For Modified Z-Source InverterAvinash GpNoch keine Bewertungen

- Modulation IndexDokument6 SeitenModulation IndexyechuriyasaswiniNoch keine Bewertungen

- MATLAB Based Analysis and Simulation of Multilevel InvertersDokument3 SeitenMATLAB Based Analysis and Simulation of Multilevel InvertersArunkumar ValusaNoch keine Bewertungen

- Artigo Cientifico Ponte de CicloconversorDokument6 SeitenArtigo Cientifico Ponte de CicloconversordelvaneijrNoch keine Bewertungen

- Selective Harmonic Elimination by Programmable Pulse Width Modulation in InvertersDokument6 SeitenSelective Harmonic Elimination by Programmable Pulse Width Modulation in InvertersseventhsensegroupNoch keine Bewertungen

- Low Power High Speed I/O Interfaces in 0.18um CmosDokument4 SeitenLow Power High Speed I/O Interfaces in 0.18um Cmosayou_smartNoch keine Bewertungen

- SV ConceptDokument9 SeitenSV Conceptnaveen_90Noch keine Bewertungen

- A Single Stage Flyback Power Supply Unit For LED Lighting ApplicationsDokument5 SeitenA Single Stage Flyback Power Supply Unit For LED Lighting ApplicationsPhạm Văn TưởngNoch keine Bewertungen

- Maswood 01035144Dokument9 SeitenMaswood 01035144rahulanlNoch keine Bewertungen

- Conv DC-DC Paper ENglishDokument5 SeitenConv DC-DC Paper ENglishpepe890305Noch keine Bewertungen

- Implementation of DSP Based Sinusoidal Pulse Width Modulation For Three Phase InverterDokument9 SeitenImplementation of DSP Based Sinusoidal Pulse Width Modulation For Three Phase InverterIJSTE100% (1)

- Family of Soft-Switching PWMDokument7 SeitenFamily of Soft-Switching PWMMohan KrishnaNoch keine Bewertungen

- H BridgeDokument16 SeitenH BridgeSkiron ThrasciusNoch keine Bewertungen

- Building Blocks of An OpampDokument11 SeitenBuilding Blocks of An OpampChathunikaNoch keine Bewertungen

- Design Guideline of AC-DC Converter Using FL6961 & FL6300A For 70W LED LightingDokument13 SeitenDesign Guideline of AC-DC Converter Using FL6961 & FL6300A For 70W LED Lightingshiva1luNoch keine Bewertungen

- Critical Bandwidth For The Load Transient Response of VRMDokument8 SeitenCritical Bandwidth For The Load Transient Response of VRMharis13harisNoch keine Bewertungen

- Elimination of Dead-Time in PWM Controlled Inverters: Lihua Chen and Fang Z. PengDokument4 SeitenElimination of Dead-Time in PWM Controlled Inverters: Lihua Chen and Fang Z. PengMarcel BlinduNoch keine Bewertungen

- Comparison of SPWM and SVPWM Scheme For Two-Level Inverter Fed Induction Motor DriveDokument6 SeitenComparison of SPWM and SVPWM Scheme For Two-Level Inverter Fed Induction Motor Drivemanish_er570Noch keine Bewertungen

- Wat MetersDokument13 SeitenWat MetersKornepati SureshNoch keine Bewertungen

- Analysis and Design of Multicell DC/DC Converters Using Vectorized ModelsVon EverandAnalysis and Design of Multicell DC/DC Converters Using Vectorized ModelsNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Bewertung: 2.5 von 5 Sternen2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Influence of System Parameters Using Fuse Protection of Regenerative DC DrivesVon EverandInfluence of System Parameters Using Fuse Protection of Regenerative DC DrivesNoch keine Bewertungen

- FPGA Based PWM Techniques For Controlling InverterDokument48 SeitenFPGA Based PWM Techniques For Controlling InverterCitharthan Magendran100% (1)

- Academic JobsDokument18 SeitenAcademic JobsNandNNoch keine Bewertungen

- Electrical Engineering PDFDokument28 SeitenElectrical Engineering PDFvineethkbNoch keine Bewertungen

- Lec01 IntroductionDokument34 SeitenLec01 IntroductionSwami KannuNoch keine Bewertungen

- Sample Teacher Resume TemplateDokument2 SeitenSample Teacher Resume TemplateSwami KannuNoch keine Bewertungen

- Instructions PHDDokument18 SeitenInstructions PHDSwami KannuNoch keine Bewertungen

- Power Electronics Project AreasDokument3 SeitenPower Electronics Project AreasSwami KannuNoch keine Bewertungen

- Embedded Project Titles Book 2012-12 - IEEE 2012 Power Electronics Project TitlesDokument13 SeitenEmbedded Project Titles Book 2012-12 - IEEE 2012 Power Electronics Project Titlesncctprojects3231Noch keine Bewertungen

- Lect 25Dokument35 SeitenLect 25Swami KannuNoch keine Bewertungen

- Multi-Level Inverter - PPTDokument16 SeitenMulti-Level Inverter - PPTSwami Kannu100% (1)

- Lect 25Dokument35 SeitenLect 25Swami KannuNoch keine Bewertungen

- Electrical Machine Design Course OverviewDokument2 SeitenElectrical Machine Design Course OverviewSwami KannuNoch keine Bewertungen

- Multilevel InverterDokument8 SeitenMultilevel InverterVamshi KrishnaNoch keine Bewertungen

- How to set up and install Tamil fonts on your computerDokument2 SeitenHow to set up and install Tamil fonts on your computerSwami KannuNoch keine Bewertungen

- Bluespec OverviewDokument2 SeitenBluespec OverviewSwami KannuNoch keine Bewertungen

- Drive Circuit Basics: Industrial Circuits Application NoteDokument7 SeitenDrive Circuit Basics: Industrial Circuits Application Notepokka20_pokkaNoch keine Bewertungen

- Hve SyllabusDokument1 SeiteHve SyllabusSwami KannuNoch keine Bewertungen

- Ss 2Dokument10 SeitenSs 2Aditya PatilNoch keine Bewertungen

- How To Make Your VBA Code BulletProofDokument13 SeitenHow To Make Your VBA Code BulletProofHemalatha S KumarNoch keine Bewertungen

- DevOps Architect with 15+ Years Experience in AWS Migrations and CI/CDDokument2 SeitenDevOps Architect with 15+ Years Experience in AWS Migrations and CI/CDMadhu DDDNoch keine Bewertungen

- Code - MSG Pervasiv PDFDokument252 SeitenCode - MSG Pervasiv PDFdarkopuNoch keine Bewertungen

- TM 87 10049 - RevA - OTS v5 00 01Dokument120 SeitenTM 87 10049 - RevA - OTS v5 00 01juan guillermo zapataNoch keine Bewertungen

- Accessing external media data bases libraryDokument7 SeitenAccessing external media data bases libraryzhyhhNoch keine Bewertungen

- Soft Light Dimmer: Application NoteDokument8 SeitenSoft Light Dimmer: Application NoteHassanein Al-hadadNoch keine Bewertungen

- Datasheet DO180-4.12Dokument4 SeitenDatasheet DO180-4.12Việt NguyễnNoch keine Bewertungen

- BITWISE OPERATOR by Sharin Aloma:-: BelowDokument9 SeitenBITWISE OPERATOR by Sharin Aloma:-: BelowShubham MeshramNoch keine Bewertungen

- AcronisCyberProtect 15Dokument582 SeitenAcronisCyberProtect 15Ivn Echegoyen RivasNoch keine Bewertungen

- CFC For M7 Continuous Function ChartDokument88 SeitenCFC For M7 Continuous Function ChartPradeep TripathiNoch keine Bewertungen

- Nexgenie Product BasketDokument16 SeitenNexgenie Product BasketSonuOm0% (1)

- Operating Systems Lecture Notes-2Dokument15 SeitenOperating Systems Lecture Notes-2Arun SasidharanNoch keine Bewertungen

- Your Ultimate Guide To Choosing The Best Drone PCBDokument9 SeitenYour Ultimate Guide To Choosing The Best Drone PCBjackNoch keine Bewertungen

- Grade 10 Baseline QuizDokument3 SeitenGrade 10 Baseline Quizishratj8736Noch keine Bewertungen

- Itdumpsfree: Get Free Valid Exam Dumps and Pass Your Exam Test With ConfidenceDokument4 SeitenItdumpsfree: Get Free Valid Exam Dumps and Pass Your Exam Test With Confidencerais lassaadNoch keine Bewertungen

- What Is Database ArchitectureDokument7 SeitenWhat Is Database ArchitecturegauravNoch keine Bewertungen

- Bachelor of Computer Applications (BCA) : Institute of Management StudiesDokument24 SeitenBachelor of Computer Applications (BCA) : Institute of Management StudiesgauravjainisNoch keine Bewertungen

- Smart Systems - Academic Year 2018-2019Dokument2 SeitenSmart Systems - Academic Year 2018-2019LêTrungĐứcNoch keine Bewertungen

- Java Multithreading ConceptsDokument17 SeitenJava Multithreading ConceptsAshok RawatNoch keine Bewertungen

- Mini-Link Outdoor MW Access From Indoor UnitsDokument11 SeitenMini-Link Outdoor MW Access From Indoor Unitszakariya nooman syedNoch keine Bewertungen

- Sepr 1 SRSDokument2 SeitenSepr 1 SRSVikrant ShimikeriNoch keine Bewertungen

- Yealink Collobration Touch Panel CTP18 DatasheetDokument3 SeitenYealink Collobration Touch Panel CTP18 Datasheetthandieu023Noch keine Bewertungen

- Buck ConvertersDokument15 SeitenBuck Convertersmuddassir07100% (2)

- Distributed Databases: Presentation-IDokument30 SeitenDistributed Databases: Presentation-Irohit_vishwakarma786Noch keine Bewertungen

- Ansible MasterDokument11 SeitenAnsible MasterJerin VargheseNoch keine Bewertungen

- Classes and Data Abstractions Lab ExplainedDokument8 SeitenClasses and Data Abstractions Lab ExplainedHamna BaigNoch keine Bewertungen

- Computer Basics ElementsDokument413 SeitenComputer Basics ElementsFaquir Sanoar SanyNoch keine Bewertungen

- Red Hat Enterprise Linux 7 Beta Logical Volume Manager Administration en USDokument149 SeitenRed Hat Enterprise Linux 7 Beta Logical Volume Manager Administration en USMohammed MarouanNoch keine Bewertungen

- DA 41 EnglishDokument2 SeitenDA 41 EnglishmouraprogNoch keine Bewertungen