Beruflich Dokumente

Kultur Dokumente

01433011DFSS

Hochgeladen von

Deepu ChinnaCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

01433011DFSS

Hochgeladen von

Deepu ChinnaCopyright:

Verfügbare Formate

848

IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 41, NO. 3, MAY/JUNE 2005

Multilevel DC-Link Inverter

Gui-Jia Su, Senior Member, IEEE

AbstractThis paper presents a new class of multilevel inverters based on a multilevel dc link (MLDCL) and a bridge inverter to reduce the number of switches, clamping diodes, or capacitors. An MLDCL can be a diode-clamped phase leg, a ying-capacitor phase leg, or cascaded half-bridge cells with each cell having its own dc source. A multilevel voltage-source inverter can be formed by connecting one of the MLDCLs with a single-phase bridge inverter. The MLDCL provides a dc voltage with the shape of a staircase approximating the rectied shape of a commanded sinusoidal wave, with or without pulsewidth modulation, to the bridge inverter, which in turn alternates the polarity to produce an ac voltage. Compared with the cascaded H-bridge, diode-clamped, and ying-capacitor multilevel inverters, the MLDCL inverters can signicantly reduce the switch count as well as the number of gate drivers as the number of voltage levels increases. For a given number of voltage levels , the required number of active switches is 2 ( 1) for the existing multilevel inverters but is + 3 for the MLDCL inverters. Simulation and experimental results are included to verify the operating principles of the MLDCL inverters. Index TermsCascaded half bridge, diode clamped, ying capacitor, multilevel dc link, multilevel inverter, reduced part count.

I. INTRODUCTION

ULTILEVEL voltage-source inverters based on the diode-clamped phase legs, ying-capacitor phase legs, or cascaded H-bridges were proposed for replacing the two-level inverters with series connection of switches or transformer-coupled multiple two-level inverters in mediumand high-voltage level applications such as motor drives and static var compensators [1][10]. Advantages of the multilevel inverters (MLIs) include: 1) the multilevel structures can ensure even voltage sharing, both statically and dynamically, among the active switches while it is difcult for a two-level inverter with a series connection of switches to do so; 2) substantial reduction in size and volume is possible due to the elimination of the bulky coupling transformers or inductors; and 3) multilevel inverters can offer better voltage waveforms with less harmonic content and, thus, can signicantly reduce the size and weight of passive lter components. The last feature was further explored in multilevel inverters using insulated gate bipolar transistors (IGBTs) for replacing gate-turn-off-thyristor

(GTO)-based two-level inverters because IGBTs can switch faster and have less demanding gate drive requirements than GTOs. On the other end of the power spectrum, because of their low cost resulting from widespread use in the automotive and power supply industries, low on-resistance, and fast switching capability, low-voltage MOSFETs are utilized in multilevel inverters to reduce the inverter cost or to provide a high bandwidth sinusoidal output voltage at high efciency that it is unable to achieve with linear ampliers [11][13]. Despite the superior voltage waveform quality provided by higher level inverters, the neutral-point-clamped inverter in [1] is perhaps the most widely used multilevel structure because of its relatively small number of switches. The high switch count and the difculty in balancing the voltage of the capacitors in the diode-clamped conguration have prevented the wide acceptance of the higher level inverters in practical applications. grows, the number of acAs the number of voltage levels for the castive switches increases according to caded H-bridge, diode-clamped, and ying-capacitor multilevel inverters. In addition, for each phase, the diode-clamped inverter clamping diodes and capacirequires at least tors for dividing the dc voltage, and the ying-capacitor inverter clamping capacitors. needs This paper presents a new class of multilevel inverters based on an MLDCL and a bridge inverter. Compared with the existing multilevel inverters, the new MLDCL inverters can signicantly reduce the switch count as well as the number of gate drivers as the number of voltage levels increases. For a given number active of voltage levels , the new inverter requires switches, roughly half the number of switches, clamping diodes, and voltage-splitting capacitors in the diode-clamped conguration, or clamping capacitors in the ying-capacitor conguration. Simulation and experimental results are included to verify the operating principle of the proposed MLDCL inverters. II. PROPOSED MLDCL INVERTER TOPOLOGIES A. Cascaded Half-Bridge-Based MLDCL Inverter Fig. 1(a) shows a schematic diagram of the proposed inverter topology, which consists of a multilevel dc source and a single-phase full-bridge (SPFB) inverter. The dc source is formed by connecting a number of half-bridge cells in series with each cell having a voltage source controlled by two and operate in a toggle switches. The two switches on and off, fashion. The cell source is bypassed with or adds to the dc-link voltage by reversing the switches. The operating principle can be explained in Fig. 1(b) by looking at the operating voltage, current, and gating signal waveforms given for the most common load, an inductive load, where is the dc-bus voltage of the SPFB inverter, the dc-bus the output ac voltage, the fundamental current,

Paper IPCSD-05-008, presented at the 2004 Industry Applications Society Annual Meeting, Seattle, WA, October 37, and approved for publication in the IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS by the Industrial Power Converter Committee of the IEEE Industry Applications Society. Manuscript submitted for review October 15, 2004 and released for publication February 25, 2005. This work was supported by the Oak Ridge National Laboratory, managed by UT-Battelle for the U.S. Department of Energy under Contract DE-AC0500OR22725. The author is with the Power Electronics and Electric Machinery Research Center, Oak Ridge National Laboratory, Oak Ridge, TN 37831-6472 USA (e-mail: sugj@ornl.gov). Digital Object Identier 10.1109/TIA.2005.847306

0093-9994/$20.00 2005 IEEE

SU: MULTILEVEL DC -LINK INVERTER

849

Fig. 2.

Comparison of required number of switches.

of a staircase that approximates the rectied waveform of the commanded sinusoidal voltage, to the SPFB inverter, which in turn alternates the voltage polarity to produce an ac voltage . While the switches in the cells can of a staircase shape perform pulsewidth modulation (PWM) if necessary or switch at twice the fundamental frequency of the output voltage, the and , and four switches in the SPFB inverter always work in pairs at the fundamental frequency of the output voltage. This topology, employing a three-phase bridge instead of an SPFB, was initially introduced in [14] to reduce current ripple for brushless dc motors with an extremely low leakage inductance. Specically, the MLDCL formed by the half-bridge cells provides a staircase-shaped dc-bus voltage of steps to the SPFB inverter, which in turn alternates the voltage polarity to of a staircase shape with produce an ac voltage levels, whose voltages are . The dc-bus voltage and current are, therefore, related to their output ac counterparts by

for for Assuming each cell adds its source voltage to the dc in each half cycle without bus over an angular period of performing PWM, the peak fundamental component of the ac output can be determined by

Fig. 1. Proposed MLDCL inverter based on cascaded half-bridge cells -level MLDCL inverter. and a single-phase full-bridge inverter. (a) n (b) Operating waveforms.

2 +1

components of , the output ac current, and , represent the corresponding switchs gating signals. The usual convention is used where 1 dictates on and 0 off. with the shape The MLDCL provides a dc-bus voltage

Fig. 2 plots a chart for comparison of the required number of switches between the proposed MLDCL inverter and the cascaded H-bridge counterpart. As the number of voltage levels grows, the number of active switches increases according for the MLDCL inverter, compared to to for the cascaded H-bridge multilevel inverters. A similar trend

850

IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 41, NO. 3, MAY/JUNE 2005

also occurs for the diode-clamped and ying-capacitor multilevel inverters, to be discussed in the following sections. Another salient feature of the new inverter is that, with an inductive in the SPFB inverter always turn off load, the switches at zero voltage and turn on at both zero voltage and current. It is noted that the proposed multilevel inverter and the cascaded H-bridge counterpart require the same number of independent voltage sources for producing the same number of levels. B. Diode-Clamped-Phase-Leg-Based MLDCL Inverter The diode-clamped phase leg can also be used to provide a multilevel dc-bus voltage with the shape of a staircase to the SPFB inverter. As an example, Fig. 3(a) is an 11-level MLDCB inverter based on the diode-clamped phase leg. The diode-clamped phase leg, consisting of ten switches , , and a voltage divider of ve eight clamping diodes capacitors , provides a dc-bus voltage of six voltage is evenly split by levels. Assuming the dc source voltage , , the capacitors, the six voltage levels of 0, , , and , can be produced by turning on simultaneously the switch combinations of , , , , , and , respectively. Again, the SPFB inverter ips the polarity of the dc-bus voltage to produce an 11-level ac voltage as shown in Fig. 3(b), , inverter output current , and where the dc bus current and the current conducting states of the switches in the SPFB are shown for an inductive load. diodes As for the Section II-A inverter, switches in the SPFB inverter always turn off at zero voltage and turn on at both zero voltage and current with an inductive load. It is also clear from Fig. 3(b) that the turn-off current approaches 0 as the power factor approaches 1. Table I gives a comparison of the number of switches, clamping diodes, and voltage-dividing capacitors required to produce an 11-level output voltage for the proposed inverter and the existing counterpart, clearly showing substantial component reduction with the proposed structure. This savings in components grows as the number of voltage levels increases, as mentioned before. C. Flying-Capacitor-Phase-Leg-Based MLDCL Inverter Fig. 4(a) shows the arrangement of a seven-level MLDCL inverter based on a capacitor-clamped phase leg and a singlephase bridge. The capacitor-clamped phase leg, consisting of six switches and two clamping capacitors and , , provides a dc-bus voltage of four voltage levels, 0, , and , by turning on the switches according to the voltage levels as listed in Table II. There are multiple choices of switch combinations to produce the two middle levels, and the capacitors will be charged or discharged as also indicated in the table. By controlling the duration of these switch combiand can be maintained at the nations, the voltage across required level of and , respectively. This is a desirable feature for preventing drift of the capacitor voltages, which happens in both the conventional and new diode-clamped congurations and leads to difculty in keeping the capacitor voltages balanced. Again, the SPFB inverter ips the polarity of

Fig. 3. Proposed MLDCL inverter based on a diode-clamped leg and a single-phase full-bridge inverter. (a) 11-level MLDCL inverter. (b) Operating waveforms. TABLE I PART COUNT COMPARISON FOR PRODUCING AN 11-LEVEL OUTPUT VOLTAGE

the dc-bus voltage to produce a seven-level ac voltage , , inverter as shown in Fig. 4(b), where the dc-bus current output current , and current conducting states of the switches and diodes in the SPFB are shown for an inductive load.

SU: MULTILEVEL DC -LINK INVERTER

851

TABLE III COMPONENT COUNT COMPARISON

TABLE IV COMPONENT TOTAL VA/V RATING COMPARISON

Fig. 4. Proposed MLDCL inverter based on a capacitor-clamped leg and a single-phase full-bridge inverter. (a) Seven-level MLDCL inverter. (b) Operating waveforms. TABLE II SWITCHING TABLE

proposed new inverters compared with their existing counterparts for a given number of output voltage levels . It can be seen that roughly half the number of the components can be eliminated as increases. Table IV gives a comparison of total VA ratings for the switches and diodes, and total voltage ratings for the capacitors in per unit, in which the voltage level-step value is used as the base voltage. Although the proposed MLDCL inverters require a higher total VA rating for the switches, the cost for the additional VA ratings could be offset by the savings from the eliminated gate drivers and from fewer assembly steps because of the substantially reduced number of components, which also leads to a smaller size and volume. In addition, a signicant reduction is gained with the proposed diode-clamped inverter in the total VA rating for the clamping diodes and the total voltage rating for the voltage-splitting capacitors, and in the total voltage rating for the clamping capacitors with the new ying-capacitor inverter, further enhancing the cost savings. III. SIMULATION AND EXPERIMENTAL RESULTS A detailed circuit simulation was conducted to verify the operating principles of the proposed MLDCL inverters. A. Half-Bridge-Based MLDCL Inverter

With the new conguration, the number of switches is reduced from 12 to ten and the number of capacitors from ve to two. Again, this savings grows with the number of levels. D. Comparison of the Proposed MLDCL Inverters and the Existing Counterparts From the previous discussions, it is demonstrated that the proposed MLDCL inverters can signicantly reduce the component count. Table III summarizes the required number of switches, their gate drivers, clamping diodes, and capacitors of the three

A three-phase 11-level half-bridge-cell-based MLDCL inverter was rst studied for powering an inductive resistor load, as shown in Fig. 5. The load resistance and inductance are 1.5 and 0.5 mH per phase, and the voltage of each dc source is set at 30 V. At an output frequency of 100 Hz, the load power factor is 0.98. , current Fig. 6 shows simulated phase- dc-bus voltage , three-phase line-to-neutral voltages , , and , and the three phase currents , , and waveforms at an output frequency of 100 Hz. These waveforms conrm the operating

852

IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 41, NO. 3, MAY/JUNE 2005

Fig. 5. 11-level half-bridge MLDCLI for three-phase conguration with an inductive resistor load.

Fig. 7. Simulated waveforms of a back-to-back connection of two 11-level diode-clamped MLDCLIs supplying an inductive resistor load. (a) Back-to-back connection of two 11-level DMLDCLIs. (b) Simulated voltage and current waveforms. Fig. 6. Simulated waveforms of the 11-level half-bridge MLDCLI for three-phase conguration with an inductive resistor load.

B. Back-to-Back Connection of Two Single-Phase Diode-Clamped MLDCL Inverters Fig. 7(a) shows a back-to-back connection of two 11-level single-phase diode-clamped MLDCL inverters, one acting as a converter connected to a voltage source of 100 Vrms at 60 Hz through an inductor of 2.9 mH and the other powering an inductive resistor load of 2 and 1.8 mH. Simulated waveforms

principle described in Section II-A. Despite the intentionally selected very low inductance, the rms value of the load current ripple is less than 2% of the fundamental current of 65.5 Arms, clearly demonstrating the superior waveform quality over the two-level PWM inverters.

SU: MULTILEVEL DC -LINK INVERTER

853

Fig. 8. Simulated waveforms of the seven-level capacitor-clamped MLDCLI for single-phase conguration with an inductive resistor load.

are given in Fig. 7(b), where and are the bus current and voltage of the inverter, and are and are the load current and voltage, bus current and voltage of the converter, and are the source are the voltages across current and voltage, and the capacitors , respectively. These waveforms clearly verify the operating principle described in Section II-B. In addition, the following observations can be stated: 1) near-sinusoidal source and load currents are produced, again demonstrating the superior waveform quality of the multilevel inverter over the two-level PWM inverters and 2) while the capacitor voltages uctuate at twice the source voltage frequency, they closely track each other due to the back-to-back connection. Because the capacitors are shared between the converter and inverter, the converter can be controlled to charge the capacitors that are discharging through the inverter, thus balancing the capacitors voltage [15]. In general, however, when a diode-clamped MLDCL inverter is directly powered by a dc source, it is difcult to balance the voltage of the capacitors. This holds for both the new and existing diode-clamped ones. C. Seven-Level Capacitor-Clamped MLDCLI Fig. 8 shows simulated dc-bus voltage and current, load voltage, and current waveforms of the seven-level capacitor-clamped MLDCLI for powering an inductive resistor load, clearly verifying the operating principle described in Section II-C. D. Testing of a 13-Level MLDCL Inverter For proof of concept, a single-phase 13-level half-bridgecell-based MLDCL inverter was assembled and tested with , mH) as an inductive resistor load ( shown in Fig. 9(a) (gate drivers are not shown for simplicity). The individual dc sources are obtained by using single-phase diode rectiers and transformers operating off the utility line. MOSFETs were used for the switches in the half-bridge cells and IGBTs in the SPFB. A Texas Instruments digital signal processor (DSP) TMS320F240 was employed to generate gate control signals for the switches. Gating signals for the MOSFETs were programmed so that each dc source contributes to

Fig. 9. Testing waveforms of a half-bridge-cell-based 13-level MLDCLI for single-phase conguration with an inductive resistor load. (a) Testing setup. (b) Testing waveforms. Time: 2 ms/div.

the dc-bus voltage for about an equal period of time per half fundamental cycle to help balance the amount of power drawn from each dc source. , output voltage Fig. 9(b) shows typical bus voltage , and load current , waveforms when the DSP was programmed for the inverter to produce a near-sinusoidal output voltage. The four IGBTs in the SPFB are switching at the fundamental frequency of 100 Hz while the other switches at 200 Hz, twice the fundamental frequency, as indicated by the gating signals, A-0 to A-7, shown in the bottom section.

854

IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 41, NO. 3, MAY/JUNE 2005

A near-sinusoidal load current with a harmonic distortion factor of less than 1% was produced. It should be noted that the gating signals are active low, i.e., a switch is turned on when its gating signal is at the low level. The MOSFETs gating signals A-0 to A-5 illustrate that the six half-bridge cells conduct for an approximately equal interval of time per half fundamental cycle and they are switched by the manner of rst-on rst-off, contrary to the typical way of rst-on last-off. IV. CONCLUSION The proposed MLDCL inverters can eliminate roughly half the number of switches, their gate drivers, clamping diodes, and capacitors compared with their existing MLI counterparts. Despite a higher total VA rating of the switches, the new MLDCL inverters could still cost less due to the savings from the eliminated gate drivers and from fewer assembly steps because of the substantially reduced number of components, which also leads to a smaller size and volume. The cost savings is further enhanced with the proposed diode-clamped and the ying-capacitor inverters because of the signicant reduction in the total VA rating of the clamping diodes and in the total voltage rating of the voltage-splitting capacitors or the clamping capacitors. One application area in the low-power range ( 100 kW) for the MLDCL inverters is in permanentmagnet (PM) motor drives employing a PM motor of very low inductance. The proposed inverters can utilize the fast-switching low-cost low-voltage MOSFETs in the half-bridge cells, the diode-clamped or capacitor-clamped phase legs, and IGBTs in the single-phase bridges to dramatically reduce current and torque ripples and to improve motor efciency by reducing the associated copper and iron losses resulting from the current ripple. These congurations may also be applied in distributed power generation involving fuel cells and photovoltaic cells [16]. For high-voltage high-power applications, high-voltage IGBTs or GTOs switching at the fundamental frequency can be used in the single-phase bridge inverters, while lower voltage but fast-switching IGBTs, which may or may not perform PWM, can be employed in the MLDCL sources. REFERENCES

[1] A. Nabae, I. Takahashi, and H. Akagi, A new neutral-point-clamped PWM inverter, IEEE Trans. Ind. Appl., vol. 17, no. 5, pp. 518523, Sep./Oct. 1981. [2] N. S. Choi, J. G. Cho, and G. H. Cho, A general circuit topology of multilevel inverter, in Conf. Rec. 1991 IEEE PESC, pp. 96103. [3] T. A. Meynard and H. Foch, Multi-level conversion: high-voltage chopper and voltage-source inverters, in Conf. Rec. 1992 IEEE PESC, pp. 397403. [4] R. W. Menzies, P. Steimer, and J. K. Steike, Five-level GTO inverters for large induction motor drives, in Conf. Rec. 1993 IEEE-IAS Annu. Meeting, pp. 595601.

[5] M. Marchesoni and M. Mazzucchelli, Multilevel converters for high power AC drives: a review, in Proc. IEEE ISIE93, Budapest, Hungary, 1993, pp. 3843. [6] C. Hochgraf, R. Lasseter, D. Divan, and T. A. Lipo, Comparison of multilevel inverters for static var compensation, in Conf. Rec. 1994 IEEE-IAS Annu. Meeting, pp. 921928. [7] J. Zhang, High performance control of a 3 level IGBT inverter fed AC drive, in Conf. Rec. 1995 IEEE-IAS Annu. Meeting, pp. 2228. [8] P. W. Hammond, A new approach to enhance power quality for medium voltage drives, in Proc. 1995 IEEE-IAS PCIC, pp. 231235. [9] J. S. Lai and F. Z. Peng, Multilevel convertersa new breed of power converters, in Conf. Rec. 1995 IEEE-IAS Annu. Meeting, pp. 23482356. [10] F. Z. Peng, J. S. Lai, J. W. McKeever, and J. VanCoevering, A multilevel voltage-source inverter with separate DC sources for static var generation, IEEE Trans. Ind. Appl., vol. 32, no. 5, pp. 11301138, Sep./Oct. 1996. [11] I. Takahashi and K. Iwaya, 100 kHz, 10 kW switching type power amplier using multilevel inverter, in Proc. 4th IEEE Int. Conf. Power Electronics and Drive Systems, vol. 1, Oct. 2225, 2001, pp. 286291. [12] , High efciency, low harmonic distortion switching type power amplier using multilevel inverter, in Proc. Power Conversion Conf., vol. 2, Osaka, Japan, 2002, pp. 25. [13] B. A. Welchko, M. B. de Rossiter Correa, and T. A. Lipo, A three-level MOSFET inverter for low-power drives, IEEE Trans. Ind. Electron., vol. 51, no. 3, pp. 669674, Jun. 2004. [14] G. J. Su and D. J. Adams, Multilevel DC link inverter for brushless permanent magnet motors with very low inductance, in Conf. Rec. 2001 IEEE-IAS Annu. Meeting, vol. 2, pp. 829834. [15] F. Z. Peng, J. S. Lai, J. W. McKeever, and J. VanCoevering, A multilevel voltage-source converter system with balanced DC voltages, in Conf. Rec. 1995 IEEE PESC, vol. 2, pp. 11441150. [16] B. Ozpineci, L. M. Tolbert, G. J. Su, Z. Du, and C. W. Miller, Optimum fuel cell utilization with multilevel converters, in Proc. 2004 IEEE APEC04, vol. 3, 2004, pp. 15721578.

Gui-Jia Su (M94SM01) received the B.S. degree in electrical power system engineering from Wuhan University of Hydraulic and Electrical Engineering (now Wuhan University), Wuhan, China, in 1985, and the M.S. and Ph.D. degrees in electrical engineering from Nagaoka University of Technology, Nagaoka, Japan, in 1989 and 1992, respectively. He was an Assistant Professor from 1992 to 1995 at Nagaoka University of Technology. From 1995 to 1998, he was with Sanken Electrical Company, Ltd., Kawagoe, Japan, where he was engaged in research and development of uninterruptible power supplies, sensorless PM motor drives, and power-factor correction for single- and three-phase rectiers. In 1998, he joined the Power Electronics and Electric Machinery Research Center (PEEMRC) at Oak Ridge National Laboratory (ORNL) as a Research Scientist with the Oak Ridge Associated Universities. He joined ORNL in 2000 as a Staff Member and is currently a Senior R&D Staff member. He holds the position of Lead Engineer of Power Electronics in the PEEMRC at the National Transportation Research Center, Knoxville, TN, a joint center of ORNL and the University of Tennessee. His current research interests include high-power dc/dc converters, inverters, motor drives, and power electronics system packaging and thermal management for electric/hybrid electric vehicle applications. He is the holder of four patents. Dr. Su is a recipient of the IEEE Industrial Electronics Society IECON01 Best Presentation Award (2001) and the IEEE Industry Applications Society Industrial Drives Committee Third Prize Paper Award (1993).

Das könnte Ihnen auch gefallen

- 46 Multileveltopology PDFDokument5 Seiten46 Multileveltopology PDFDeepu ChinnaNoch keine Bewertungen

- D EEPU05491634Dokument4 SeitenD EEPU05491634Deepu ChinnaNoch keine Bewertungen

- INV04503992Dokument6 SeitenINV04503992Deepu ChinnaNoch keine Bewertungen

- EE113 Course Notes Electronic CircuitsDokument268 SeitenEE113 Course Notes Electronic Circuitspowerdeadlifter100% (1)

- 04285962, DJSDokument9 Seiten04285962, DJSDeepu ChinnaNoch keine Bewertungen

- High Sensitive LPG Sensor With Gas Leak AlertDokument23 SeitenHigh Sensitive LPG Sensor With Gas Leak AlertDeepu Chinna100% (2)

- Single Phase Fully Controlled ConverterDokument10 SeitenSingle Phase Fully Controlled ConverterDeepu Chinna75% (4)

- Energy Audits in Thermal Power StationDokument62 SeitenEnergy Audits in Thermal Power Stationfiroj_khan995% (22)

- Ee PSDokument2 SeitenEe PSDeepu ChinnaNoch keine Bewertungen

- How and Why They Work, and What They Can Do For YouDokument21 SeitenHow and Why They Work, and What They Can Do For YouDeepu ChinnaNoch keine Bewertungen

- PWM DC Motor Control Using Timer A of The MSP430Dokument3 SeitenPWM DC Motor Control Using Timer A of The MSP430Deepu ChinnaNoch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Lab7 DSA BSEE20034Dokument7 SeitenLab7 DSA BSEE20034Muhammad Umer ShakirNoch keine Bewertungen

- EXPERIMNET 0: (Environment Configuration & Sample Program)Dokument7 SeitenEXPERIMNET 0: (Environment Configuration & Sample Program)jfkajlfjNoch keine Bewertungen

- LOGO! Analog Input PT100 ManualDokument6 SeitenLOGO! Analog Input PT100 ManualKhurram100% (3)

- NachosDokument16 SeitenNachosmkumarshahiNoch keine Bewertungen

- How To Add Fonts To Xdo FileDokument5 SeitenHow To Add Fonts To Xdo Fileseethal_2Noch keine Bewertungen

- 21 H 2 Z 32 B 4Dokument12 Seiten21 H 2 Z 32 B 4jaimedejNoch keine Bewertungen

- Deep Learning For Human Beings v2Dokument110 SeitenDeep Learning For Human Beings v2Anya NieveNoch keine Bewertungen

- Exstream05Content03Doc PDFDokument198 SeitenExstream05Content03Doc PDFAymen EL ARBINoch keine Bewertungen

- Olomo IT 13066652-0 - 74021Dokument177 SeitenOlomo IT 13066652-0 - 74021Paul WallNoch keine Bewertungen

- BST106-M10 (FB) Weighing Controller: Operation Manual V5.0Dokument61 SeitenBST106-M10 (FB) Weighing Controller: Operation Manual V5.029374925morNoch keine Bewertungen

- Design and Manufacturing of A Propeller For Axial Flow FanDokument7 SeitenDesign and Manufacturing of A Propeller For Axial Flow FancbarajNoch keine Bewertungen

- Treatment of Assets Under Construction in SAP - From Creation To Settlement - SapGurusDokument22 SeitenTreatment of Assets Under Construction in SAP - From Creation To Settlement - SapGurusAman VermaNoch keine Bewertungen

- Image Search Engine: Resource GuideDokument16 SeitenImage Search Engine: Resource Guideprakash_embsysNoch keine Bewertungen

- Oracle ASM Interview QuestionsDokument7 SeitenOracle ASM Interview QuestionsAnsuman PattnaikNoch keine Bewertungen

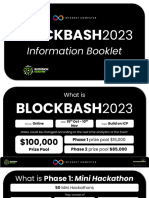

- Blockbash 2023 DocumentDokument14 SeitenBlockbash 2023 DocumentNoch keine Bewertungen

- Iot Based Waste Collection Management System For Smart Cities: An OverviewDokument4 SeitenIot Based Waste Collection Management System For Smart Cities: An OverviewApurv ChoubeyNoch keine Bewertungen

- Midshire Business Systems - Ricoh MP CW2200SP - A0 Wide Format Colour BrochureDokument8 SeitenMidshire Business Systems - Ricoh MP CW2200SP - A0 Wide Format Colour BrochureadietoppingNoch keine Bewertungen

- DTK Det DepDokument49 SeitenDTK Det DepJames SmithNoch keine Bewertungen

- Arduino Project ReportDokument16 SeitenArduino Project ReportBroAmirNoch keine Bewertungen

- SysSocketAsync V3x EDokument7 SeitenSysSocketAsync V3x Emuhamad.badar9285Noch keine Bewertungen

- Chi Square DistributionDokument4 SeitenChi Square DistributionIziNoch keine Bewertungen

- PowerFlex 4.0 Installation-SSP V2 - Downloadable ContentDokument20 SeitenPowerFlex 4.0 Installation-SSP V2 - Downloadable ContentMWANAHAWA BAKARINoch keine Bewertungen

- AB350M Pro4Dokument72 SeitenAB350M Pro4DanReteganNoch keine Bewertungen

- Sicoma Twin Shaft Mixer Brochure JECDokument8 SeitenSicoma Twin Shaft Mixer Brochure JECShabrina Meitha Nadhila RamadhanNoch keine Bewertungen

- Nguyen Pham Hai An's ResumeDokument2 SeitenNguyen Pham Hai An's ResumeSea Hai AnNoch keine Bewertungen

- Robert Salisbury Email: Office: (713) - 462-5232 Ext.102Dokument24 SeitenRobert Salisbury Email: Office: (713) - 462-5232 Ext.102KaushikNoch keine Bewertungen

- Arduino Measurement Projects For BeginnersDokument175 SeitenArduino Measurement Projects For BeginnersSimon Choquechambi Martinez100% (2)

- VerizonWireless AffDokument2 SeitenVerizonWireless Affjbjkhb hibNoch keine Bewertungen

- Chapter 2Dokument17 SeitenChapter 2priyaadharshiniNoch keine Bewertungen

- Flatness-Based ControlDokument6 SeitenFlatness-Based ControlQuyết Nguyễn CôngNoch keine Bewertungen