Beruflich Dokumente

Kultur Dokumente

Verilog Sample PPR

Hochgeladen von

jayaprasadkalluriOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Verilog Sample PPR

Hochgeladen von

jayaprasadkalluriCopyright:

Verfügbare Formate

18-360 Intro to Computer-Aided Digital Design ECE Department

Out: 1/29/04 1. Verilog Hacking

a. Here is one solution. Yours may differ Each of the three implementations are in their own module. They are instantiated in the test module, and their output is compared for each test input. If the outputs are different, the tester prints an error.

module compareTheseTwo2bitUnsignedValues_gates(A,B,AgtB,AltB,AeqB); input [1:0] A,B; output AgtB, AltB, AeqB; not not and and and xnor xnor and or nor #(4,7) #(4,7) #(4,7) #(4,7) #(4,7) #(4,7) #(4,7) #(4,7) #(4,7) #(4,7) ( ( ( ( ( ( ( ( ( ( w6, A[1]); w7, A[0]); w1, w6, B[1] ); w2, w6, w7, B[0] ); w3, w7, B[1], B[0] ); w5, A[1], B[1] ); w4, A[0], B[0] ); AeqB, w4, w5 ); AltB, w1, w2, w3 ); AgtB, AeqB, AltB );

Solutions: Homework 1

// This monitor was used to generate waveforms for the gate wires. // initial $monitor($time,, // "w1..7= %b %b %b %b %b %b %b, lt, \ // eq,gt= %b %b %b", w1, w2, w3, w4, w5, w6, w7, AltB, AgtB, AeqB ); endmodule // compareTheseTwo2bitUnsignedValues_gates module compareTheseTwo2bitUnsignedValues_always(A,B,AgtB,AltB,AeqB); input [1:0] A,B; output AgtB, AltB, AeqB; reg AgtB,AltB,AeqB; always@(A or B) begin #4; AgtB = 0; AltB = 0; AeqB = 0; if ( A==B ) AeqB = 1; else if ( A>B ) AgtB = 1; else Page 1 of 11

18-360, Spring 2004

AltB = 1; end endmodule // compareTheseTwo2bitUnsignedValues_always

module compareTheseTwo2bitUnsignedValues_assign(A,B,AgtB,AltB,AeqB); input [1:0] A,B; output AgtB, AltB, AeqB; assign #(4,7) AgtB= (A>B); assign #(4,7) AltB= (A<B); assign #(4,7) AeqB= (A==B); endmodule // compareTheseTwo2bitUnsignedValues_assign /* Compare the three input bits. Output 1 iff all input bits are the same. */ module compare_outputs( out, in ); input [2:0] in; output out; assign out = ( in === 3'b111 || in === 3'b000 );

endmodule // compare_outputs module tester; reg [1:0] A,B; wire AgtB_gate, AltB_gate, AeqB_gate; wire AgtB_assign, AltB_assign, AeqB_assign; wire AgtB_always, AltB_always, AeqB_always; wire AgtB_agree, AeqB_agree, AltB_agree; reg [3:0] test_in[15:0]; integer i; compareTheseTwo2bitUnsignedValues_gates secr (A,B,AgtB_gate, AltB_gate, AeqB_gate

);

compareTheseTwo2bitUnsignedValues_always temes (A,B,AgtB_always,AltB_always,AeqB_always); compareTheseTwo2bitUnsignedValues_assign sage (A,B,AgtB_assign,AltB_assign,AeqB_assign); compare_outputs gt( AgtB_agree, {AgtB_gate, AgtB_assign, AgtB_always} ); compare_outputs eq( AeqB_agree, {AeqB_gate, AeqB_assign, AeqB_always} ); compare_outputs lt( AltB_agree, {AltB_gate, AltB_assign, AltB_always} ); initial

Page 2 of 11

18-360, Spring 2004

begin $readmemh("tests.mem", test_in ); $monitor($time,,"Current Test: A:%b B:%b\n gate: AgtB:%b AltB:%b AeqB:%b\n assign: AgtB:%b AltB:%b AeqB:%b\n always: AgtB:%b AltB:%b AeqB:%b\n\n", A,B, AgtB_gate,AltB_gate,AeqB_gate, AgtB_assign,AltB_assign,AeqB_assign, AgtB_always,AltB_always,AeqB_always ); for(i=0; i<16; i=i+1) begin {A, B} = test_in[i]; #1000; if ( AgtB_agree !== 1 ) $display ("ERROR: The modules disagree on the gt output."); if ( AeqB_agree !== 1 ) $display ("ERROR: The modules disagree on the eq output."); if ( AltB_agree !== 1 ) $display ("ERROR: The modules disagree on the lt output."); if ( {AgtB_agree, AeqB_agree, AltB_agree} === 3'b111 ) $display ("TEST PASSED: The modules agree on all outputs."); end end endmodule // tester

Page 3 of 11

18-360, Spring 2004

A=0 and B=0 are used as one test vector. Here are the transitions for A=x, B=x to A=0,B=0. The signal names are those used in the verilog module shown above.

A[0] A[1] B[1] B[0] w1 w2 w3 w4 w5 w6 w7 A_lt_B A_gt_B A_eq_B

14 15

For the above transition, each of the 10 gates changes once, from x to its final value. So in this case, the min, max, and mean number of transitions of the gates are all 1. It is possible to have different values with a different circuit and/or a different test vector. b. If a new comparator is added, the timing of the gate events will not be affected. The timing of the gate events is a function only of the inputs to those gates. In this system, those inputs are A and B. Adding a new module that reads from A and B will not change the values of A and B. Since the inputs to the gates do not change, the physical events associated with the gates will not change.

2. Waveform City

The input signal, b, looks like this: 1 0

9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

not #2(a,b):

Page 4 of 11

18-360, Spring 2004

1 0

9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

Note that the spike did not go through the primitive gate. It was less than the propagation delay. assign #2 a = ~b 1 0

9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

always @(b) #2 a = ~b The delay of two prevents the change in b at time 10 from propagating through. Note that the delayed blocking assignment from the change at 10 waits till time 12 to read b, so the value of b at time 12 is used to compute the value of a at time 12. The change in b at time 11 does not cause the always block to be run, because the is suspended waiting for the #delay. 1 0

9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

always @(b) a = #2 ~b Here, when b changes at time 10, its value (1) is stored, causing ~b (0) to be written to a at time 12. Because the assignment is blocking, the change in b at time 11 does not activate the always block, since it is still suspended (blocked) from the change in b at time 10. 1 0

9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

always @(b) #2 a <= ~b In this case, the non-blocking assignment has no effect, because there are no other assignments in the always block. The behavior is exactly the same as the blocking assignment version.

Page 5 of 11

18-360, Spring 2004

1 0

9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

always @(b) a <= #2 ~b On a change in b, this version reads the current value of b, schedules ~b to be written to a in two time units, and goes back to wait for the next change in b in zero time. So, every change of b causes a change in a, two time units later. 1 0

9 10 11 12 13 14 15 16 17 18 19 20 21 22 23

3. Theres a price to being an author of a book

Here is a possible fix. Note that non-blocking assignment should be used in order to catch clock edges.

module ThreeInputAdder (sum, in1, in2, in3, clock); input [3:0] in1, in2, in3; input clock; output [4:0] sum; always @(posedge clock) sum <= #30 in1 + in2 + in3; endmodule

4. Waveform Needed

// non-blocking assignment initial begin a <= #0 1'bx; a <= #4 1'b0; a <= #8 1'bz; a <= #12 1'b1; a <= #16 1'b0; a <= #20 1'b1; #24 $finish(0); end // blocking assignment initial begin #0 a = 1'bx; #4 a = 1'b0; #4 a = 1'bz; #4 a = 1'b1; #4 a = 1'b0; #4 a = 1'b1; #4 $finish(0); end

Notice that since the non-blocking assignments take zero time, the simulation time is still 0 until the #24 is run. Both initial blocks call finish at time 24.

Page 6 of 11

18-360, Spring 2004

The non-blocking version enqueues all of the events that will change a, then dequeues them as the simulation progresses. The blocking version suspends the initial block each time a new value is generated. Its hard to say which will run faster. The tradeoff appears to be whether enqueueing and dequeueing events (non-blocking version) takes more or less time than enqueueing and dequeueing an initial block (blocking version). Both versions must also propagate their output.

5. Assign with a function

Three simple functions are used to do the work of the assign statements.

module compareTheseTwo2bitUnsignedValues_assign(A,B,AgtB,AltB,AeqB); input [1:0] A,B; output AgtB, AltB, AeqB; function isAgtB; input [1:0] a; input [1:0] b; begin isAgtB = (a>b); end endfunction function isAeqB; input [1:0] a; input [1:0] b; begin isAeqB = (a==b); end endfunction function isAltB; input [1:0] a; input [1:0] b; begin isAltB = (a<b); end endfunction assign #(4,7) AgtB= isAgtB( A, B ); assign #(4,7) AltB= isAltB( A, B ); assign #(4,7) AeqB= isAeqB( A, B ); endmodule // compareTheseTwo2bitUnsignedValues_assign

Page 7 of 11

18-360, Spring 2004

6. Dont be so edgy

module dff (q, d, c, r); input d, c, r; output q; reg q; always @(posedge c or negedge r) if ~r q <= 0; else q <= d; endmodule

(5%)

On the initial negative edge of r the description is indeed edge triggered. However, if r remains low for an extended period over the course of several positive edge c events, the reset does not act edge triggered. Instead the reset is level sensitive since all further activations due to posedge c will encounter the reset conditions (because of its level).

7. What are the values

(10%)

a. Fill in the table showing the values for the three registers at the given times. Legal answers are 0, 1, x, z, and indeterminate.

reg q, r, s, t; initial begin q = 1b0; t <= #1 1b0; q <= #1 1b1; s = 1b1; end always begin r = 1b1; s = 1b0; wait (t === 1b0) q = 1b0; r = 1b0; q <= #10 1b1; end

name q r

Value at the end of time 0 0, as set by the initial block 1, as set by the always block Indeterminate depends on whether the always or initial block runs first x, wont be set until time 1

Value at the end of time 1 Set to 0 by the always block Indeterminate, or oscillating, as set by the always block Set to 0 by the always block

Set to 0

b. The always will never stop after it first stops for the wait, while t is set to 0 at time 1 and does not change any more. An event (the update of q) will be in the event list for time 11.

Page 8 of 11

18-360, Spring 2004

8. Alex, Ill take #8 for 15%

a. Show the 4-value truth table for a primitive XOR XOR gate. b. and c. The update and evaluation functions are as follows.

init_XOR (gate) { // start of simulation gate.counter_one = 0; gate.counter_x = gate.num_inputs; eval_XOR (gate); }

(15%) 0 0 1 x x 1 1 0 x x x x x x x z x x x x

0 1 x z

// when any single input gate.input[id] // changes to a different value new_value, // the update_XOR function is called update_XOR (gate, id, new_value) { if (new_value == 1) gate.counter_one++; if (gate.input[id].value == 1) gate.counter_one--; if (new_value == x) gate.counter_x++; if (gate.input[id].value == x) gate.counter_x--; gate.input.value=new_value; eval_XOR (gate); } } eval_XOR (gate) { // if any input is x, the output will be x. if (gate.counter_x != 0) gate.output = x; else { // if an odd number of inputs are 1s, the output will be 1; // otherwise, the output will be 0. gate.output.value = gate.counter_one % 2; } }

Page 9 of 11

18-360, Spring 2004

9. Who needs that #delay anyway

a. Draw the waveform for a DAC write. Write 17 into DAC 4.

1 #5

(20%)

clock

rwLine addressLines dataLines 4 17

b. Draw the waveform for an ADC read. Read ADC address 4. The value written will be (17+0) >> 1 = 8. Processor waits 5 and asserts read and addressLines, then waits for last neg clock edge (far right) for value read. ADC sees read, waits 2, puts value on dataLines, then waits until far right clock edge.

#5

#2

clock rwLine addressLines dataLines

1 0 4 8

c. The solution to part c requires you to use non-blocking assignments so that everything happens concurrently on the clock edge. The following is an answer.

always begin // this models the processor which will write/read the DA/ADC. // Registers data, // addr, and readWrite are internal to the processor and are the // address to be read or written depending on readWrite. data is the // value to write or the value read back. // There are no clock edges up here in the unshown part of this always //start here rwLine <= readWrite; if (readWrite) begin // write to a DAC addressLines <= addr; dataLines <= data; end else begin // read ADC value comes back in next clock cycle addressLines <= addr; @(negedge clock); end @ (negedge clock); if (~readWrite)

Page 10 of 11

18-360, Spring 2004

data <= dataLines; // value returned by ADC end always begin //This is the DA/ADC that looks at the buslines (rwLine, addressLines, // dataLines) and either loads the DAC (on write) or drives (writes) // the dataLines with the averaged value read from the ADC // There are no clock edges up here in the unshown part of this always //start here @ (negedge clock); if (~rwLine) begin // read ADC and average with previous value tempReg = (ADC[addressLines] + previousADC[addressLines])>>1; previousADC[addressLines] = tempReg; dataLines <= tempReg; @(negedge clock); end else // write DAC DAC[addressLines] <= dataLines; end

1 clock rwLine 4 8 0

addressLines dataLines

Page 11 of 11

Das könnte Ihnen auch gefallen

- 6T40 DetayDokument52 Seiten6T40 Detaysuattosun100% (11)

- Verilog HDL Lectuer 5Dokument36 SeitenVerilog HDL Lectuer 5Nilesh GulveNoch keine Bewertungen

- Verilog Imp...Dokument105 SeitenVerilog Imp...Arun JyothiNoch keine Bewertungen

- BEST Question Bank - Digital ElectronicsDokument157 SeitenBEST Question Bank - Digital Electronicsabhinav_pundir0% (1)

- Projects With Microcontrollers And PICCVon EverandProjects With Microcontrollers And PICCBewertung: 5 von 5 Sternen5/5 (1)

- Advanced Verilog CodingDokument43 SeitenAdvanced Verilog Codingroma_haroonNoch keine Bewertungen

- Verilog CodeDokument85 SeitenVerilog Codeappuamreddy75% (8)

- Game Developer ResumeDokument1 SeiteGame Developer ResumeKevin HerndonNoch keine Bewertungen

- Verilog Interview Questions and AnswersDokument16 SeitenVerilog Interview Questions and AnswersAashish AggarwalNoch keine Bewertungen

- Hardware Modeling Using Verilog Assignment-Week 5Dokument7 SeitenHardware Modeling Using Verilog Assignment-Week 5krishna414100% (1)

- Questions&AnswersDokument8 SeitenQuestions&AnswersECEII 065Noch keine Bewertungen

- Verilog HDL: Practical - 08Dokument19 SeitenVerilog HDL: Practical - 08Ashish SharmaNoch keine Bewertungen

- Lab Sheet 3 FinalDokument9 SeitenLab Sheet 3 FinalSANJEEV MALLICKNoch keine Bewertungen

- Assignment Week4Dokument3 SeitenAssignment Week4saigdv1978100% (2)

- 24-Booth Multiplier, Behavioral Modeling-17!02!2023Dokument13 Seiten24-Booth Multiplier, Behavioral Modeling-17!02!2023Back upNoch keine Bewertungen

- Verilog Behavioral ModelingDokument44 SeitenVerilog Behavioral ModelingHarshit TyagiNoch keine Bewertungen

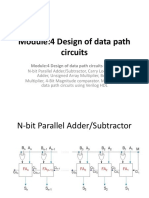

- Module:4 Design of Data Path Circuits 6 HoursDokument44 SeitenModule:4 Design of Data Path Circuits 6 HoursSahana MecheriNoch keine Bewertungen

- Hardware Logic and Flip-Flops in VerilogDokument14 SeitenHardware Logic and Flip-Flops in VerilogMohammad Seemab AslamNoch keine Bewertungen

- VLSI Lab Report 8Dokument24 SeitenVLSI Lab Report 8Umar AyubNoch keine Bewertungen

- Vlsi A & B - 2011Dokument70 SeitenVlsi A & B - 2011Amaresh RamathalNoch keine Bewertungen

- TASK 1: 8-Bit Verilog Code For Booth's MultiplierDokument2 SeitenTASK 1: 8-Bit Verilog Code For Booth's MultiplierrathiNoch keine Bewertungen

- Verilog AssignmentsDokument27 SeitenVerilog Assignmentssrikar_dattaNoch keine Bewertungen

- An Exploration of Hole Filling AlgorithmsDokument2 SeitenAn Exploration of Hole Filling AlgorithmsVeeresh SalmaniNoch keine Bewertungen

- VerilogDokument8 SeitenVerilogMuhammad MoinNoch keine Bewertungen

- DSDV Lab Manual PDFDokument15 SeitenDSDV Lab Manual PDFÅᴅᴀʀsʜ Rᴀᴍ100% (3)

- EE271 Lab1 Group06Dokument9 SeitenEE271 Lab1 Group06Lê Vương TháiNoch keine Bewertungen

- Term End Examination VLSI DesignDokument6 SeitenTerm End Examination VLSI DesignSujeet KumarNoch keine Bewertungen

- Test Benches in VerilogDokument16 SeitenTest Benches in VerilogSharan ChaitanyaNoch keine Bewertungen

- Lab 05 Handout Combinational & SequentialDokument9 SeitenLab 05 Handout Combinational & SequentialMuhammad SaudNoch keine Bewertungen

- 40-character title summarizing SystemVerilog numbers, constants, operators and modulesDokument2 Seiten40-character title summarizing SystemVerilog numbers, constants, operators and modulesRaymundo Saraiva100% (1)

- Chapter 06 Synchronous Sequential CircuitsDokument56 SeitenChapter 06 Synchronous Sequential Circuitskidgod2111Noch keine Bewertungen

- Component Test and Verification Testbench TechniquesDokument107 SeitenComponent Test and Verification Testbench TechniquesramjidrNoch keine Bewertungen

- Termend-I - Key Cat1 PPR OldDokument8 SeitenTermend-I - Key Cat1 PPR OldSANJUCTA CHOUDHURYNoch keine Bewertungen

- Testbenches - FPGA Designs With VHDL DocumentationDokument19 SeitenTestbenches - FPGA Designs With VHDL DocumentationAdriana MorenoNoch keine Bewertungen

- Solution of Quiz 5Dokument5 SeitenSolution of Quiz 5Pranavkumar PatilNoch keine Bewertungen

- Vlsi Comple Lab TaskDokument37 SeitenVlsi Comple Lab TaskTausique SheikhNoch keine Bewertungen

- 3 to 8 Decoder Verilog designDokument59 Seiten3 to 8 Decoder Verilog designvaishnaviNoch keine Bewertungen

- Week10 Sequential CircuitsDokument27 SeitenWeek10 Sequential Circuitsnavarrojules53Noch keine Bewertungen

- System Verilog For Verification: Dr.R.JayagowriDokument158 SeitenSystem Verilog For Verification: Dr.R.JayagowriAdithya ReddyNoch keine Bewertungen

- Verilog Tutorial Part 2 SummaryDokument9 SeitenVerilog Tutorial Part 2 SummaryNishana KumarNoch keine Bewertungen

- VerilogDokument17 SeitenVerilogBack UpNoch keine Bewertungen

- Birla Institute of Technology & Science, Pilani Lab Sheet - 2 Topic: Combinational Circuit ModelingDokument7 SeitenBirla Institute of Technology & Science, Pilani Lab Sheet - 2 Topic: Combinational Circuit ModelingSATYAVRAT SHARMANoch keine Bewertungen

- Vlsi - Digital - Lab ManualDokument23 SeitenVlsi - Digital - Lab ManualVamsi KrishnanNoch keine Bewertungen

- Procedural and Concurrent Blocks in Verilog 1706091941Dokument15 SeitenProcedural and Concurrent Blocks in Verilog 1706091941Purna satya srinivas VempalaNoch keine Bewertungen

- Verilog Behavioral Program For Counters: Up Counter (4 Bit)Dokument17 SeitenVerilog Behavioral Program For Counters: Up Counter (4 Bit)Sainadh YerrapragadaNoch keine Bewertungen

- EVD18I019 Assignment 2 EditedDokument22 SeitenEVD18I019 Assignment 2 EditedEVD18I019 NIMMAKAYALA SUMANTH GOURI MANJUNADHNoch keine Bewertungen

- Module 5 DSDV (Nep)Dokument11 SeitenModule 5 DSDV (Nep)AadilNoch keine Bewertungen

- Chapter 6: Synchronous Sequential Circuits OverviewDokument54 SeitenChapter 6: Synchronous Sequential Circuits OverviewThanh Diện NguyễnNoch keine Bewertungen

- 22bce20019. Lab Report-DldDokument40 Seiten22bce20019. Lab Report-Dldrockstarguy2005Noch keine Bewertungen

- 18ecl58 HDL Lab 2020Dokument16 Seiten18ecl58 HDL Lab 2020sureshfm170% (10)

- Module 5 DSDV (Bec302)Dokument11 SeitenModule 5 DSDV (Bec302)h.s.surabhi2005Noch keine Bewertungen

- Vlsi Part A ManualDokument47 SeitenVlsi Part A ManualLohit PNoch keine Bewertungen

- Lab Assignment 1:: Design IssuesDokument6 SeitenLab Assignment 1:: Design IssuesAbdul Wasay JawaidNoch keine Bewertungen

- Behavioral Modeling: Unit - IiiDokument38 SeitenBehavioral Modeling: Unit - IiiNageswara ReddyNoch keine Bewertungen

- Aim: Hardware RequiredDokument12 SeitenAim: Hardware RequiredfjhgfiuyufyjNoch keine Bewertungen

- Verilog HDL: ModuleDokument9 SeitenVerilog HDL: ModuleAvinash ReddyNoch keine Bewertungen

- Delays VerilogDokument18 SeitenDelays VerilogAkhilesh SinghNoch keine Bewertungen

- Chapter - 06 - Synchronous Sequential CircuitsDokument34 SeitenChapter - 06 - Synchronous Sequential CircuitsNgô Trọng NghĩaNoch keine Bewertungen

- Verilog Lab SolutionsDokument15 SeitenVerilog Lab Solutionsraja_ramalingam07Noch keine Bewertungen

- UNIT III (Autosaved)Dokument93 SeitenUNIT III (Autosaved)Nageswara ReddyNoch keine Bewertungen

- Goto Repetition, Boolean ( ( - N), ( - N:M) )Dokument3 SeitenGoto Repetition, Boolean ( ( - N), ( - N:M) )SupalShahNoch keine Bewertungen

- ADD hw4Dokument8 SeitenADD hw4Aarushi GuptaNoch keine Bewertungen

- VersantDokument1 SeiteVersantjayaprasadkalluriNoch keine Bewertungen

- HP Fortify Static Code Analyzer: User GuideDokument136 SeitenHP Fortify Static Code Analyzer: User GuidejayaprasadkalluriNoch keine Bewertungen

- JnTuk Od ApplicationDokument4 SeitenJnTuk Od ApplicationNekkanti Sarath ChandraNoch keine Bewertungen

- Vdocuments - MX - Versant English Test Sample Question and Answer 1 Liner Question Part CDokument4 SeitenVdocuments - MX - Versant English Test Sample Question and Answer 1 Liner Question Part CjayaprasadkalluriNoch keine Bewertungen

- (WWW - Entrance-Exam - Net) - 10 January 2011 Capgemini PaperDokument2 Seiten(WWW - Entrance-Exam - Net) - 10 January 2011 Capgemini PaperPranav KondekarNoch keine Bewertungen

- Parallel Self Timed AdderDokument5 SeitenParallel Self Timed AdderjayaprasadkalluriNoch keine Bewertungen

- QUANTITATIVE ABILITY: PIPES FILLING TANKS AND PERCENTAGE WORD PROBLEMSDokument1 SeiteQUANTITATIVE ABILITY: PIPES FILLING TANKS AND PERCENTAGE WORD PROBLEMSParnab Kumar BhattacharyaNoch keine Bewertungen

- Floating Point Multiplier Unit: (SET ID 09SETMVD0022)Dokument2 SeitenFloating Point Multiplier Unit: (SET ID 09SETMVD0022)jayaprasadkalluriNoch keine Bewertungen

- Interview QuestionsDokument4 SeitenInterview Questionssrinidhiprabhu_koteshwaraNoch keine Bewertungen

- Facenow LogicalDokument17 SeitenFacenow LogicaljayaprasadkalluriNoch keine Bewertungen

- Verilog Coding of Signed Adders & Multipliers: VLSI DSP Assignment-2Dokument41 SeitenVerilog Coding of Signed Adders & Multipliers: VLSI DSP Assignment-2jayaprasadkalluriNoch keine Bewertungen

- CMOS Process: Material Mainly Taken From UMBC, Kang and CampbellDokument38 SeitenCMOS Process: Material Mainly Taken From UMBC, Kang and CampbellSmitha KollerahithluNoch keine Bewertungen

- Cmos Fabrication: N - Well ProcessDokument42 SeitenCmos Fabrication: N - Well ProcessArun GopinathNoch keine Bewertungen

- ISPD 2010 - High Performance Clock Network Synthesis Contest and the Benchmark SuiteDokument37 SeitenISPD 2010 - High Performance Clock Network Synthesis Contest and the Benchmark SuitejayaprasadkalluriNoch keine Bewertungen

- Parallel Prefix Adders PresentationDokument35 SeitenParallel Prefix Adders Presentations akhilaNoch keine Bewertungen

- Verilog Code For Comb. CircuitsDokument33 SeitenVerilog Code For Comb. Circuitsjayaprasadkalluri100% (1)

- Datapath ElementsDokument4 SeitenDatapath ElementsjayaprasadkalluriNoch keine Bewertungen

- Low Power Ic SyllabusDokument2 SeitenLow Power Ic SyllabusjayaprasadkalluriNoch keine Bewertungen

- Kaushik Roy, Sharat Prasad-Low Power CMOS VLSI - Circuit Design-Wiley (2000)Dokument374 SeitenKaushik Roy, Sharat Prasad-Low Power CMOS VLSI - Circuit Design-Wiley (2000)jayaprasadkalluri67% (3)

- Register FileDokument6 SeitenRegister FilejayaprasadkalluriNoch keine Bewertungen

- PKI & KerberosDokument6 SeitenPKI & KerberosArun RNoch keine Bewertungen

- Engr. Marvin A. DumaguitDokument4 SeitenEngr. Marvin A. DumaguitjasperNoch keine Bewertungen

- A Note On Zagreb Indices: Bo ZhouDokument10 SeitenA Note On Zagreb Indices: Bo Zhoudragance106Noch keine Bewertungen

- Stock InfocomputerDokument12 SeitenStock InfocomputerLuis OrtegaNoch keine Bewertungen

- Cloud ComputingDokument27 SeitenCloud ComputingNehal GuptaNoch keine Bewertungen

- Regin Optigo OP5U Preprogrammed ControllerDokument6 SeitenRegin Optigo OP5U Preprogrammed Controllerckyee88Noch keine Bewertungen

- Stmicro Mcu Pfe 2012xDokument15 SeitenStmicro Mcu Pfe 2012xkbma2009Noch keine Bewertungen

- Manual For Seal Team 16 Flipper RigDokument6 SeitenManual For Seal Team 16 Flipper RigVenkatesh LakkamaneniNoch keine Bewertungen

- Audison Signal Processor Optimized Audio DSPDokument2 SeitenAudison Signal Processor Optimized Audio DSPVlad GrigoreNoch keine Bewertungen

- AND & Ampersand OR - Pipe NOT Tilde XOR CaretDokument5 SeitenAND & Ampersand OR - Pipe NOT Tilde XOR CaretMohamed RayanyNoch keine Bewertungen

- Daftar Harga Produk Fiber Optic Htu Periode Customer Mei 2023Dokument3 SeitenDaftar Harga Produk Fiber Optic Htu Periode Customer Mei 2023Bang PinNoch keine Bewertungen

- Type-61 ElastomerSeatedButterflyValves 10 28 2022Dokument10 SeitenType-61 ElastomerSeatedButterflyValves 10 28 2022viksursNoch keine Bewertungen

- Textron G1 7120 en ManualDokument24 SeitenTextron G1 7120 en Manualdesportista_luisNoch keine Bewertungen

- ZCL LACS Documentation 2018Dokument27 SeitenZCL LACS Documentation 2018Alid Franco AñonuevoNoch keine Bewertungen

- Checklist Komponen Mesin CNC LatheDokument20 SeitenChecklist Komponen Mesin CNC LatheMuis AnwarNoch keine Bewertungen

- The Home Tab in Microsoft Word PDFDokument14 SeitenThe Home Tab in Microsoft Word PDFSunil baghelNoch keine Bewertungen

- Finite Diff PDFDokument14 SeitenFinite Diff PDFElshan AliyevNoch keine Bewertungen

- HP Notebook 15-Bs105ne: Reliable Performance. Beautiful Design. Do MoreDokument2 SeitenHP Notebook 15-Bs105ne: Reliable Performance. Beautiful Design. Do MoreMohamedNoch keine Bewertungen

- Darpan Singh: Rae Bareli - 229001 (U.P)Dokument6 SeitenDarpan Singh: Rae Bareli - 229001 (U.P)boobobbyNoch keine Bewertungen

- Altec: Instruction ManualDokument33 SeitenAltec: Instruction Manualfrankie35Noch keine Bewertungen

- Thinkpad Usb-C Dock User GuideDokument42 SeitenThinkpad Usb-C Dock User GuidexialiaoliaoNoch keine Bewertungen

- Harga PC Branded PDFDokument25 SeitenHarga PC Branded PDFTopan MuhamadNoch keine Bewertungen

- EE5630 - EE5660 - Exam - Main - FinalDokument5 SeitenEE5630 - EE5660 - Exam - Main - FinalMadalin PetrachiNoch keine Bewertungen

- 17 Service Manual - Packard Bell - Easynote Tm85 Tm86 Tm89Dokument212 Seiten17 Service Manual - Packard Bell - Easynote Tm85 Tm86 Tm89Soporte Tecnico Buenos Aires100% (1)

- COOLER MASTER - Silencio S600Dokument2 SeitenCOOLER MASTER - Silencio S600casogerardoNoch keine Bewertungen

- Hardware and Software Installation: Tracer SummitDokument152 SeitenHardware and Software Installation: Tracer SummitDevices MobilesNoch keine Bewertungen

- AVP101 Manual V1.2Dokument26 SeitenAVP101 Manual V1.217527520Noch keine Bewertungen

- h15084 Dell Emc Unity Introduction To The PlatformDokument44 Seitenh15084 Dell Emc Unity Introduction To The PlatformNirmal Vallathai SreenivasanNoch keine Bewertungen