Beruflich Dokumente

Kultur Dokumente

Shift Registers

Hochgeladen von

Syed Abdullah Hasan Chishti0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

35 Ansichten8 SeitenIs about the shift registers in the Digital logic design an digital system design. In digital circuits, a shift register is a cascade of flip flops, sharing the same clock, in which the output of each flip-flop is connected to the "data" input of the next flip-flop in the chain, resulting in a circuit that shifts by one position the "bit array" stored in it, shifting in the data present at its input and shifting out the last bit in the array, at each transition of the clock input. More generally, a shift register may be multidimensional, such that its "data in" and stage outputs are themselves bit arrays: this is implemented simply by running several shift registers of the same bit-length in parallel.

Shift registers can have both parallel and serial inputs and outputs. These are often configured as serial-in, parallel-out (SIPO) or as parallel-in, serial-out (PISO). There are also types that have both serial and parallel input and types with serial and parallel output. There are also bi-directional shift registers which allow shifting in both directions: L→R or R→L. The serial input and last output of a shift register can also be connected to create a circular shift register. These are the simplest kind of shift registers. The data string is presented at 'Data In', and is shifted right one stage each time 'Data Advance' is brought high. At each advance, the bit on the far left (i.e. 'Data In') is shifted into the first flip-flop's output. The bit on the far right (i.e. 'Data Out') is shifted out and lost.

The data are stored after each flip-flop on the 'Q' output, so there are four storage 'slots' available in this arrangement, hence it is a 4-Bit Register. To give an idea of the shifting pattern, imagine that the register holds 0000 (so all storage slots are empty). As 'Data In' presents 1,0,1,1,0,0,0,0 (in that order, with a pulse at 'Data Advance' each time—this is called clocking or strobing) to the register, this is the result. The left hand column corresponds to the left-most flip-flop's output pin, and so on.

So the serial output of the entire register is 10110000. It can be seen that if data were to be continued to input, it would get exactly what was put in, but offset by four 'Data Advance' cycles. This arrangement is the hardware equivalent of a queue. Also, at any time, the whole register can be set to zero by bringing the reset (R) pins high.

This arrangement performs destructive readout - each datum is lost once it has been shifted out of the right-most bit. This configuration allows conversion from serial to parallel format. Data is input serially, as described in the SISO section above. Once the data has been inputted, it may be either read off at each output simultaneously, or it can be shifted out and replaced.

In cases where the parallel outputs should not change during the serial loading process, it is desirable to use a latched output. In a latched shift register (such as the 74595) the serial data is first loaded into an internal shift register, then upon receipt of a load signal the state of the shift register is copied into a set of output registers. In general, the practical application of the serial-in/parallel-out shift register is to convert data from serial format on a single wire to parallel format on multiple wires.

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenIs about the shift registers in the Digital logic design an digital system design. In digital circuits, a shift register is a cascade of flip flops, sharing the same clock, in which the output of each flip-flop is connected to the "data" input of the next flip-flop in the chain, resulting in a circuit that shifts by one position the "bit array" stored in it, shifting in the data present at its input and shifting out the last bit in the array, at each transition of the clock input. More generally, a shift register may be multidimensional, such that its "data in" and stage outputs are themselves bit arrays: this is implemented simply by running several shift registers of the same bit-length in parallel.

Shift registers can have both parallel and serial inputs and outputs. These are often configured as serial-in, parallel-out (SIPO) or as parallel-in, serial-out (PISO). There are also types that have both serial and parallel input and types with serial and parallel output. There are also bi-directional shift registers which allow shifting in both directions: L→R or R→L. The serial input and last output of a shift register can also be connected to create a circular shift register. These are the simplest kind of shift registers. The data string is presented at 'Data In', and is shifted right one stage each time 'Data Advance' is brought high. At each advance, the bit on the far left (i.e. 'Data In') is shifted into the first flip-flop's output. The bit on the far right (i.e. 'Data Out') is shifted out and lost.

The data are stored after each flip-flop on the 'Q' output, so there are four storage 'slots' available in this arrangement, hence it is a 4-Bit Register. To give an idea of the shifting pattern, imagine that the register holds 0000 (so all storage slots are empty). As 'Data In' presents 1,0,1,1,0,0,0,0 (in that order, with a pulse at 'Data Advance' each time—this is called clocking or strobing) to the register, this is the result. The left hand column corresponds to the left-most flip-flop's output pin, and so on.

So the serial output of the entire register is 10110000. It can be seen that if data were to be continued to input, it would get exactly what was put in, but offset by four 'Data Advance' cycles. This arrangement is the hardware equivalent of a queue. Also, at any time, the whole register can be set to zero by bringing the reset (R) pins high.

This arrangement performs destructive readout - each datum is lost once it has been shifted out of the right-most bit. This configuration allows conversion from serial to parallel format. Data is input serially, as described in the SISO section above. Once the data has been inputted, it may be either read off at each output simultaneously, or it can be shifted out and replaced.

In cases where the parallel outputs should not change during the serial loading process, it is desirable to use a latched output. In a latched shift register (such as the 74595) the serial data is first loaded into an internal shift register, then upon receipt of a load signal the state of the shift register is copied into a set of output registers. In general, the practical application of the serial-in/parallel-out shift register is to convert data from serial format on a single wire to parallel format on multiple wires.

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

35 Ansichten8 SeitenShift Registers

Hochgeladen von

Syed Abdullah Hasan ChishtiIs about the shift registers in the Digital logic design an digital system design. In digital circuits, a shift register is a cascade of flip flops, sharing the same clock, in which the output of each flip-flop is connected to the "data" input of the next flip-flop in the chain, resulting in a circuit that shifts by one position the "bit array" stored in it, shifting in the data present at its input and shifting out the last bit in the array, at each transition of the clock input. More generally, a shift register may be multidimensional, such that its "data in" and stage outputs are themselves bit arrays: this is implemented simply by running several shift registers of the same bit-length in parallel.

Shift registers can have both parallel and serial inputs and outputs. These are often configured as serial-in, parallel-out (SIPO) or as parallel-in, serial-out (PISO). There are also types that have both serial and parallel input and types with serial and parallel output. There are also bi-directional shift registers which allow shifting in both directions: L→R or R→L. The serial input and last output of a shift register can also be connected to create a circular shift register. These are the simplest kind of shift registers. The data string is presented at 'Data In', and is shifted right one stage each time 'Data Advance' is brought high. At each advance, the bit on the far left (i.e. 'Data In') is shifted into the first flip-flop's output. The bit on the far right (i.e. 'Data Out') is shifted out and lost.

The data are stored after each flip-flop on the 'Q' output, so there are four storage 'slots' available in this arrangement, hence it is a 4-Bit Register. To give an idea of the shifting pattern, imagine that the register holds 0000 (so all storage slots are empty). As 'Data In' presents 1,0,1,1,0,0,0,0 (in that order, with a pulse at 'Data Advance' each time—this is called clocking or strobing) to the register, this is the result. The left hand column corresponds to the left-most flip-flop's output pin, and so on.

So the serial output of the entire register is 10110000. It can be seen that if data were to be continued to input, it would get exactly what was put in, but offset by four 'Data Advance' cycles. This arrangement is the hardware equivalent of a queue. Also, at any time, the whole register can be set to zero by bringing the reset (R) pins high.

This arrangement performs destructive readout - each datum is lost once it has been shifted out of the right-most bit. This configuration allows conversion from serial to parallel format. Data is input serially, as described in the SISO section above. Once the data has been inputted, it may be either read off at each output simultaneously, or it can be shifted out and replaced.

In cases where the parallel outputs should not change during the serial loading process, it is desirable to use a latched output. In a latched shift register (such as the 74595) the serial data is first loaded into an internal shift register, then upon receipt of a load signal the state of the shift register is copied into a set of output registers. In general, the practical application of the serial-in/parallel-out shift register is to convert data from serial format on a single wire to parallel format on multiple wires.

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 8

110

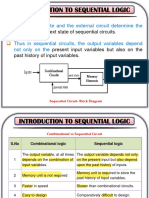

Chapter 10 Shift Registers

10.1 Introduction

A Register is a digital circuit that both stores data and moves data. The term shift

register is used to highlight that the register also moves data. Since a shift register

stores data it implemented using flip-flops. The flip-flop operation required is that of a

D-type flip flop. Remember that the truth table for a D-type flip-flop is as follows:

Inputs Outputs Description

D C

Q Q

D D D Follows D

In other words, when a clock edge is detected (in this case rising clock edge) the

output Q becomes equal to the input D. The D-type flip-flop can be implemented from

a JK flip-flop as follows:

We can say that when a clock edge is detected the D-type flip-flop stores the value of

D. For each bit that we want to store we require a flip-flop. Therefore if we require to

store 4 bits then 4 flip-flops are needed. Each flip-flop stores one bit, that is each stage

(the number of stages is often used to refer to the number of flip-flops a register

contains and hence the number of bits it can store) of the register stores one bit.

There are a variety of implementations of shift registers. Simplified diagrams are

shown below naming the various types possible (4-bit shift registers are shown).

K

J

C

Q

Q

D

C

Q

Q

D

C

Q

Q

1. Serial-in Serial-out

Data in Data out 1(a) Left to Right

Data out Data in 1(b) Right to Left

111

4. Serial-in Parallel-out

Data in

Data out

3. Parallel-in Serial-out

Data in

Data out

2. Parallel-in Parallel-out

Data in

Data out

Data in Data out 1(c) Rotate Left

Data out Data in 1(d) Rotate Right

112

Note that the variations that exist for Serial-in Serial-out shift registers also exist for

the other types of shift register. They are not shown here for simplicity.

The remaining sections of this chapter look at the implementation of each of the four

types of shift register.

10.2 Serial-In Serial-Out Shift Registers

A Serial-in Serial-out shift register can be implemented using D-type flip-flops joined

together, the output of one flip-flop used as the input to the next flip-flop. The circuit

for a 4-bit Serial-in Serial-out shift register is shown below.

The operation of the serial-in Serial-out shift register can be easily explained. Consider

the circuit shown. On each clock edge (rising in this case) we can say the following

about the outputs of each stage of the register (i.e. each D-type flip-flop in the

register):

Data out = Q

3

= D

3

= Q

2

;

Q

2

= D

2

= Q

1

;

Q

1

= D

1

= Q

0

;

Q

0

= D

0

= Data in;

Which simplifies to:

Data out = Q

2

;

Q

2

= Q

1

;

Q

1

= Q

0

;

Q

0

= Data in;

Hence we can use these equations to step through the register's operation.

Consider that all the flip-flops outputs are 0. If Data in is LOW, i.e. 0, and a rising

clock edge occurs then the equations listed can be applied to determine the new

outputs of the flip-flops, i.e.

D

0

C

Q

0

D

3

C

Q

3

D

1

C

Q

1

D

2

C

Q

2 Data in

CLK

Data out

On each rising clock edge

On each rising clock edge

113

Data out = Q

2

= 0;

Q

2

= Q

1

= 0;

Q

1

= Q

0

= 0;

Q

0

= Data in = 0;

Q

0

Q

1

Q

2

Q

3

= Data out

0 0 0 0

There is no change. If Data in is HIGH, i.e. 1, and a rising clock edge occurs then

once again the equations listed can be applied to determine the new outputs of the flip-

flops, i.e.

Data out = Q

2

= 0;

Q

2

= Q

1

= 0;

Q

1

= Q

0

= 0;

Q

0

= Data in = 1;

Q

0

Q

1

Q

2

Q

3

= Data out

1 0 0 0

A 1 is now present at the output of the first flip-flop. If Data in remains HIGH, i.e. 1,

and another rising clock edge occurs then the flip-flop outputs become:

Data out = Q

2

= 0;

Q

2

= Q

1

= 0;

Q

1

= Q

0

= 1;

Q

0

= Data in = 1;

Q

0

Q

1

Q

2

Q

3

= Data out

1 1 0 0

Data in is made LOW, i.e. 0, and another rising clock edge occurs. The flip-flop

outputs become:

Data out = Q

2

= 0;

Q

2

= Q

1

= 1;

Q

1

= Q

0

= 1;

Q

0

= Data in = 0;

Q

0

Q

1

Q

2

Q

3

= Data out

0 1 1 0

Data in is made HIGH, i.e. 1, and another rising clock edge occurs. The flip-flop

outputs become:

Data out = Q

2

= 1;

Q

2

= Q

1

= 1;

Q

1

= Q

0

= 0;

Q

0

= Data in = 1;

114

Q

0

Q

1

Q

2

Q

3

= Data out

1 0 1 1

We can see that the bit sequence 1101 has been serially shifted into the register. As

rising clock edges continue to occur the sequence will be serially shifted out of the

shift register, i.e.

Data in is made LOW, i.e. 0, and another rising clock edge occurs. The flip-flop

outputs become:

Data out = Q

2

= 1;

Q

2

= Q

1

= 0;

Q

1

= Q

0

= 1;

Q

0

= Data in = 0;

Q

0

Q

1

Q

2

Q

3

= Data out

0 1 0 1

Data in remains LOW, i.e. 0, and another rising clock edge occurs. The flip-flop

outputs become:

Data out = Q

2

= 0;

Q

2

= Q

1

= 1;

Q

1

= Q

0

= 0;

Q

0

= Data in = 0;

Q

0

Q

1

Q

2

Q

3

= Data out

0 0 1 0

Data in remains LOW, i.e. 0, and another rising clock edge occurs. The flip-flop

outputs become:

Data out = Q

2

= 1;

Q

2

= Q

1

= 0;

Q

1

= Q

0

= 0;

Q

0

= Data in = 0;

Q

0

Q

1

Q

2

Q

3

= Data out

0 0 0 1

Data in is made LOW, i.e. 0, and another rising clock edge occurs. The flip-flop

outputs become:

Data out = Q

2

= 0;

Q

2

= Q

1

= 0;

Q

1

= Q

0

= 0;

Q

0

= Data in = 0;

Q

0

Q

1

Q

2

Q

3

= Data out

0 0 0 0

115

At this point the shift register has returned to its original state of 0s at the outputs of

the flip-flops. It can be seen therefore that with the circuit given a 4-bit number can be

shifted serially into the register, where it is stored, before being shifted serially out of

the shift register.

If it is desired that the data be rotated in the shift register the circuit would need to be

modified as shown:

If ROTATE is HIGH then the effect is to pass Data in through the AND gate to the OR

gate and block the Data out from the OR gate. This is the case because we know that

(from Chapter 3) an AND gate will only give an output of 1 when both inputs are 1.

When ROTATE is LOW then the effect is to block Data in and pass Data out to the

input of the first flip-flop. Then, each time a rising clock edge is detected, the data will

be rotated through the shift register.

10.3 Parallel-In Parallel-Out Shift

Registers

A Parallel-in Parallel-out shift register can be implemented as follows.

Data in

Data out

CLK

ROTATE

D

0

C

Q

0

D

3

C

Q

3

D

1

C

Q

1

D

2

C

Q

2

CLK

Q

0

Q

1

Q

2

Q

3

D

0

C

Q

0

D

3

C

Q

3

D

1

C

Q

1

D

2

C

Q

2

D

0

D

1

D

2

D

3

Data in

Data out

116

The operation of the Parallel-in Parallel-out shift register is straightforward. When a rising

clock edge is detected the outputs become equal to the inputs, i.e.

Data out =

Q

3

= D

3

Q

2

= D

2

Q

1

= D

1

Q

0

= D

0

= Data in

10.4 Serial-In Parallel-Out Shift Registers

A Serial-in Parallel-out shift register can be implemented using a circuit similar to a

Serial-in Serial-out shift register, i.e. the D-type flip-flops are joined together and the

output of one flip-flop used as the input to the next flip-flop. The circuit is:

The operation of the Serial-in Parallel-out shift register is the same as that of the

Serial-in Serial-out register except that the Data out is n-bits for an n-bit register, in

this case n = 4. Hence the data out is Q

0

, Q

1

, Q

2

and Q

3

. In the Serial-in Serial-out

register Data out is Q

3

only.

10.5 Parallel-In Serial-Out Shift Registers

The Parallel-in Serial-out shift register is the most complex of the shift registers

because it logic to determine whether you are loading data to the register or you are

shifting data currently in the register. The circuit for a Parallel-in Serial-out register is

shown on the following page. The circuit should be interpreted as follows. Each input

to each flip-flop can either be data in or data shifted from the previous flip-flop.

Which is required depends on the state of LOAD SHIFT / . If it is HIGH, i.e. we want

the register to shift data (not read in new data) then the data in inputs are disabled

because they are ANDed with 0. The shift data (the output of the previous flip-flop) is

CLK

Q

0

Q

1

Q

2

Q

3

D

0

C

Q

0

D

3

C

Q

3

D

1

C

Q

1

D

2

C

Q

2

Data out

Data in

117

passed through to the input of the next flip-flop because it is ANDed with 1. When

LOAD SHIFT / is LOW then we want to load new data to the register. In this case the

data in is passed through to the input of each flip-flop and the shift data is blocked.

The circuit is shown below:

Notice that the behaviour of the LOAD SHIFT / circuitry is the same as that of the

ROTATE circuitry in Section 10.2.

D

0

D

1

D

2

D

3

Data in

CLK

D

3

C

Q

3

D

0

C

Q

0

D

1

C

Q

1

D

2

C

Q

2

SHIFT/LOAD

Data out

Das könnte Ihnen auch gefallen

- Shift Register PDFDokument8 SeitenShift Register PDFmahimaNoch keine Bewertungen

- Digital Design On Digital Works.Dokument25 SeitenDigital Design On Digital Works.nileshchaurasiaNoch keine Bewertungen

- 6 RegistersDokument24 Seiten6 RegistersPiyooshTripathiNoch keine Bewertungen

- CounterDokument22 SeitenCounterMahesh MahiNoch keine Bewertungen

- Shift Sins OutDokument11 SeitenShift Sins Outawa buayaNoch keine Bewertungen

- Arithmetic and Logic (Cont) : 2.3 Build Sequential Logic CircuitDokument22 SeitenArithmetic and Logic (Cont) : 2.3 Build Sequential Logic CircuitBadrul Afif ImranNoch keine Bewertungen

- Unit-1 - Digital ElectronicsDokument50 SeitenUnit-1 - Digital ElectronicsVignesh VigneshNoch keine Bewertungen

- Chapter 7 - Flip Flop and Registers2020Dokument25 SeitenChapter 7 - Flip Flop and Registers2020SYAFIQAH BATRISYIA MOHD ZAHIRNoch keine Bewertungen

- Simulation of Se Qu Ntial CK TDokument10 SeitenSimulation of Se Qu Ntial CK TSivaprakasam KarthikeyanNoch keine Bewertungen

- DTE Question Bank SolutionDokument15 SeitenDTE Question Bank SolutionkhantaukirhasanNoch keine Bewertungen

- EE331L Experiment #4: Written By: Shehab Alaa Ramadan Group: C University ID Number: 022180589Dokument19 SeitenEE331L Experiment #4: Written By: Shehab Alaa Ramadan Group: C University ID Number: 022180589Shehab RamadanNoch keine Bewertungen

- Unit 5 DLDDokument189 SeitenUnit 5 DLDGuru VelmathiNoch keine Bewertungen

- Jkflip FlopDokument27 SeitenJkflip FlopUsama NaveedNoch keine Bewertungen

- Computer Architecture 1Dokument39 SeitenComputer Architecture 1ARAFAT GaamanNoch keine Bewertungen

- Chapter 7 - Flip FlopsDokument12 SeitenChapter 7 - Flip FlopsAmeer AzharNoch keine Bewertungen

- Flip FlopsDokument29 SeitenFlip FlopsShweta RoyNoch keine Bewertungen

- De-16 (Unit 4)Dokument49 SeitenDe-16 (Unit 4)MALLIDI VIJAYA SREENoch keine Bewertungen

- Fundamentals of Digital Computers: Unit - VDokument25 SeitenFundamentals of Digital Computers: Unit - VrajagopalNoch keine Bewertungen

- Sequential Circuits: Flip FlopsDokument16 SeitenSequential Circuits: Flip FlopsSonam SoniNoch keine Bewertungen

- Registers and Counters: in This Topic We Will Be Covering - Registers - CountersDokument7 SeitenRegisters and Counters: in This Topic We Will Be Covering - Registers - CountersZoolJcNoch keine Bewertungen

- Shift Registers1Dokument8 SeitenShift Registers1Gowtham KrishnaBBENoch keine Bewertungen

- Gated SR Latch: CSE 271 - Introduction To Digital Systems Supplementary Reading Some Basic Memory ElementsDokument8 SeitenGated SR Latch: CSE 271 - Introduction To Digital Systems Supplementary Reading Some Basic Memory ElementsJohnNoch keine Bewertungen

- Linear Integrated Circuits Lab Manual For Flip Flops and Logic GatesDokument14 SeitenLinear Integrated Circuits Lab Manual For Flip Flops and Logic GatesTimoth DevNoch keine Bewertungen

- DDCO QBDokument20 SeitenDDCO QB333jayanth333Noch keine Bewertungen

- Report FlipFlopsDokument15 SeitenReport FlipFlopsPratibh SinhaNoch keine Bewertungen

- UntitledDokument8 SeitenUntitledlalita chauhanNoch keine Bewertungen

- Designing of Flip FlopsDokument8 SeitenDesigning of Flip FlopsOni OniNoch keine Bewertungen

- Flip Flop Mealy and Moore ModelDokument25 SeitenFlip Flop Mealy and Moore Modelsurajpb1989100% (1)

- WAVEFORM EXPLAINATION WholeDokument10 SeitenWAVEFORM EXPLAINATION Whole12 EC ATUL KUMAR SRIVASTAVANoch keine Bewertungen

- Module - 3 DSDVDokument40 SeitenModule - 3 DSDVHimabindu SanapaNoch keine Bewertungen

- Sequential Logic - Flip-Flops: 6.1 SR LatchDokument5 SeitenSequential Logic - Flip-Flops: 6.1 SR Latchanon020202Noch keine Bewertungen

- ENS2456 and ENS6154 Digital Electronics: Registers & CountersDokument32 SeitenENS2456 and ENS6154 Digital Electronics: Registers & CountersNubia DiazNoch keine Bewertungen

- Unit-VI Counters and Shift RegistersDokument20 SeitenUnit-VI Counters and Shift RegistersVarsha SenthilNoch keine Bewertungen

- Microprocessor-Based System Design, Ricardo Gutierrez-Osuna, Wright State UniversityDokument21 SeitenMicroprocessor-Based System Design, Ricardo Gutierrez-Osuna, Wright State UniversityAce DanielNoch keine Bewertungen

- Flip Flop Sect 2Dokument31 SeitenFlip Flop Sect 2Bink BonkNoch keine Bewertungen

- Sequential Circuits: Latches and Flip-FlopsDokument32 SeitenSequential Circuits: Latches and Flip-FlopsRohan BorgalliNoch keine Bewertungen

- DSD Module 5Dokument81 SeitenDSD Module 5Abinesh RNoch keine Bewertungen

- Test 1Dokument6 SeitenTest 1kavana a ganigaNoch keine Bewertungen

- Digital Electronics 8Dokument12 SeitenDigital Electronics 8Tapas BanerjeeNoch keine Bewertungen

- LogicDesign CHPT 10Dokument31 SeitenLogicDesign CHPT 10john juanNoch keine Bewertungen

- Physics Project FileDokument14 SeitenPhysics Project FileSrutanik BhaduriNoch keine Bewertungen

- Lec Nnaik Sequential CircuitsDokument27 SeitenLec Nnaik Sequential Circuits11kumarvishal4Noch keine Bewertungen

- Digital Circuitry: Flip-Flops Leds - Seven Segment DecoderDokument9 SeitenDigital Circuitry: Flip-Flops Leds - Seven Segment DecoderMaposse SimioneNoch keine Bewertungen

- STLD TestDokument136 SeitenSTLD TestganeshNoch keine Bewertungen

- Mini Project DigitDokument7 SeitenMini Project DigitMUHAMMAD IZZAT BIN ZULKIFLI STUDENTNoch keine Bewertungen

- Flip-Flop LabDokument7 SeitenFlip-Flop Labjose mirandaNoch keine Bewertungen

- COE211 CH5 Part1Dokument30 SeitenCOE211 CH5 Part1hm100hm100hm100Noch keine Bewertungen

- Unit 3Dokument24 SeitenUnit 3Raja BenitaNoch keine Bewertungen

- Flip FlopsDokument60 SeitenFlip FlopsA10-14Rajat KumarNoch keine Bewertungen

- Objective Questions MCQ On LatchesDokument32 SeitenObjective Questions MCQ On LatchesNaman KumarNoch keine Bewertungen

- Mini Project DigitDokument7 SeitenMini Project DigitMUHAMMAD IZZAT BIN ZULKIFLI STUDENTNoch keine Bewertungen

- TTTTT Eeee AsDokument20 SeitenTTTTT Eeee AsEric GongNoch keine Bewertungen

- Module 5 - Counter Design Problems and Flip-Flops - Oct 8thDokument65 SeitenModule 5 - Counter Design Problems and Flip-Flops - Oct 8thRavi CharanNoch keine Bewertungen

- The Clocked RS Flip-FlopDokument4 SeitenThe Clocked RS Flip-Flopabhisheksikka17Noch keine Bewertungen

- Search For DocumentsDokument9 SeitenSearch For DocumentsdineshvhavalNoch keine Bewertungen

- Digital LabDokument51 SeitenDigital LabBala SubramanianNoch keine Bewertungen

- Computer Science Notes: Digital and Analogue Circuit DesignDokument52 SeitenComputer Science Notes: Digital and Analogue Circuit DesignMuhammedNoch keine Bewertungen

- DS - Expt 10Dokument6 SeitenDS - Expt 10Aditya SalunkheNoch keine Bewertungen

- Assignment 1Dokument1 SeiteAssignment 1Syed Abdullah Hasan ChishtiNoch keine Bewertungen

- Assignment2 SolutionDokument11 SeitenAssignment2 SolutionSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Assignment 2Dokument3 SeitenAssignment 2Syed Abdullah Hasan ChishtiNoch keine Bewertungen

- Assignment1 SolutionDokument8 SeitenAssignment1 SolutionSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Laboratory Manual: Fundamentals of ProgrammingDokument84 SeitenLaboratory Manual: Fundamentals of ProgrammingSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Electricity Consumption CalculatorDokument2 SeitenElectricity Consumption CalculatorSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- LAB No. 1 Implementation of Data Types, Variables, Conditional Statements and LoopsDokument1 SeiteLAB No. 1 Implementation of Data Types, Variables, Conditional Statements and LoopsSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Robotic Indoor Path Planning Using Dijkstra's Algorithm With Multi-Layer DictionariesDokument4 SeitenRobotic Indoor Path Planning Using Dijkstra's Algorithm With Multi-Layer DictionariesSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Excel BasicsDokument17 SeitenExcel BasicsMuhammad Tayyab AhmadNoch keine Bewertungen

- Microwave Theory and TechniquesDokument46 SeitenMicrowave Theory and TechniquesSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Electrical EngineeringDokument200 SeitenElectrical EngineeringEhsan Elahi BashirNoch keine Bewertungen

- Electricity Consumption CalculatorDokument2 SeitenElectricity Consumption CalculatorSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Orcad Capture Release 15.7: Robert J. Hofinger Purdue University 1/15/08Dokument38 SeitenOrcad Capture Release 15.7: Robert J. Hofinger Purdue University 1/15/08serhatbNoch keine Bewertungen

- Assignment 6 PDFDokument1 SeiteAssignment 6 PDFSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- OFDMDokument11 SeitenOFDMSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Assignment No 1: Submitted To: Sir. Dr. Tair Zaidi.Dokument5 SeitenAssignment No 1: Submitted To: Sir. Dr. Tair Zaidi.Syed Abdullah Hasan ChishtiNoch keine Bewertungen

- DC MotorDokument8 SeitenDC MotorSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Lecture 4Dokument46 SeitenLecture 4Syed Abdullah Hasan ChishtiNoch keine Bewertungen

- AssignmentLMS RLSDokument11 SeitenAssignmentLMS RLSSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Stick Diagram & Boolean FunctionDokument17 SeitenStick Diagram & Boolean FunctionSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Lecture 5Dokument38 SeitenLecture 5Syed Abdullah Hasan ChishtiNoch keine Bewertungen

- Sensors 14 12847 v2 PDFDokument24 SeitenSensors 14 12847 v2 PDFSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Introduction To ProgrammingDokument56 SeitenIntroduction To ProgrammingSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Win DSPDokument62 SeitenWin DSPSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Communicatin System 1 Lab Manual 2011Dokument63 SeitenCommunicatin System 1 Lab Manual 2011Sreeraheem SkNoch keine Bewertungen

- Lab 02 - Getting Familier To Ladder Logic ProgrammingDokument12 SeitenLab 02 - Getting Familier To Ladder Logic ProgrammingSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- A Novel Timing Estimation Method For OFDM Systems (Journal)Dokument4 SeitenA Novel Timing Estimation Method For OFDM Systems (Journal)Syed Abdullah Hasan ChishtiNoch keine Bewertungen

- Lab 01 - Introduction To PLC Hardware and SoftwareDokument18 SeitenLab 01 - Introduction To PLC Hardware and SoftwareSyed Abdullah Hasan Chishti100% (1)

- Name: Regd. No.: Attempt All Questions. Marks Are Mentioned Against The QuestionsDokument1 SeiteName: Regd. No.: Attempt All Questions. Marks Are Mentioned Against The QuestionsSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Assignment No-3: Submitted by Abdullah HasanDokument3 SeitenAssignment No-3: Submitted by Abdullah HasanSyed Abdullah Hasan ChishtiNoch keine Bewertungen

- Learning Objectives: Lecture 3: Moving Averages and Exponential SmoothingDokument6 SeitenLearning Objectives: Lecture 3: Moving Averages and Exponential SmoothingcuriousdumboNoch keine Bewertungen

- Lottery Cheaters' Guide by Charles CooperDokument43 SeitenLottery Cheaters' Guide by Charles CooperCiprian Dobrescu100% (2)

- Statistics Fall2013 - Final Sample Test 01Dokument7 SeitenStatistics Fall2013 - Final Sample Test 01Thanh VyNoch keine Bewertungen

- Spirometric Evaluation of Pulmonary Function Tests in Bronchial Asthma PatientsDokument6 SeitenSpirometric Evaluation of Pulmonary Function Tests in Bronchial Asthma PatientsdelphineNoch keine Bewertungen

- Qbake - Production Planning Guide - Bread Line.Dokument27 SeitenQbake - Production Planning Guide - Bread Line.ahetNoch keine Bewertungen

- Job Salary PredictionDokument23 SeitenJob Salary PredictionShah Momtaj Ala Hriday 171-15-8834Noch keine Bewertungen

- Concrete Mix DesignDokument36 SeitenConcrete Mix Designamitbd80% (5)

- Rapid Prototyping PPT SeminarDokument32 SeitenRapid Prototyping PPT SeminarShantha Kumar G C0% (1)

- Grade 4 Decimals: Answer The QuestionsDokument4 SeitenGrade 4 Decimals: Answer The QuestionsEduGainNoch keine Bewertungen

- Planar Edge Terminations For High Power SiC DiodesDokument234 SeitenPlanar Edge Terminations For High Power SiC DiodesRaul PerezNoch keine Bewertungen

- Emulsions: - Part 1 Preparation Methods (Some) PropertiesDokument52 SeitenEmulsions: - Part 1 Preparation Methods (Some) PropertieschandramohanNoch keine Bewertungen

- Danfoss FC 301-302 AngDokument268 SeitenDanfoss FC 301-302 AngkudakwasheNoch keine Bewertungen

- MAT3700-MayJune ExamDokument3 SeitenMAT3700-MayJune ExamNhlanhla NdebeleNoch keine Bewertungen

- Ac Machinery FormulasDokument4 SeitenAc Machinery FormulasNhilNoch keine Bewertungen

- LI 6500WX: Making Life Easier and SaferDokument17 SeitenLI 6500WX: Making Life Easier and SaferkellyburtonNoch keine Bewertungen

- Disomat Tersus: Instruction ManualDokument268 SeitenDisomat Tersus: Instruction ManualMohamed Hamad100% (1)

- Thesis DocumentDokument21 SeitenThesis DocumentChris Lorenz83% (18)

- Production ManagementDokument14 SeitenProduction Managementavinasss1963_3707255Noch keine Bewertungen

- Object Kpis For The Digital Transformation: June 2020Dokument12 SeitenObject Kpis For The Digital Transformation: June 2020MUHAMMAD FIKRI DEVIANESNoch keine Bewertungen

- Lincoln Douglas Debate TextbookDokument115 SeitenLincoln Douglas Debate TextbookRogelio Aurelio Rojas ReyesNoch keine Bewertungen

- A Short-Form Proof of Fermat's Last TheoremDokument15 SeitenA Short-Form Proof of Fermat's Last TheoremNishkarsh SwarnkarNoch keine Bewertungen

- Slip TestDokument2 SeitenSlip TestkrctmechNoch keine Bewertungen

- Astm D698Dokument13 SeitenAstm D698Jorge CarrascoNoch keine Bewertungen

- Je Tire 006084Dokument7 SeitenJe Tire 006084AmerNoch keine Bewertungen

- Calculation of The Size of The Mooring SystemDokument7 SeitenCalculation of The Size of The Mooring SystemKyle RubricoNoch keine Bewertungen

- Spreadsheet Practice Exercises-2016FDokument40 SeitenSpreadsheet Practice Exercises-2016FDharneeshkarDandy92% (12)

- Learning Activity Sheet In: Computer Systems ServicingDokument12 SeitenLearning Activity Sheet In: Computer Systems ServicingCarvalds 0315100% (1)

- Lattice Structure Design For AmDokument9 SeitenLattice Structure Design For AmNishar Alam Khan 19MCD0042Noch keine Bewertungen

- Airfoil Fans CatalogDokument52 SeitenAirfoil Fans CatalogGChandraSekharaRaoNoch keine Bewertungen