Beruflich Dokumente

Kultur Dokumente

Proyecto 5 Completo

Hochgeladen von

Fatima Valdez PalaciosOriginalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Proyecto 5 Completo

Hochgeladen von

Fatima Valdez PalaciosCopyright:

Verfügbare Formate

UNIVERSIDAD NACIONAL AUTNOMA DE MXICO FACULTAD DE INGENIERA

DISEO DIGITAL

TAREAS DE CLASE

Prof.: Ing. MANDUJANO WILD ROBERTO

GRUPO No.

INTEGRANTES: Valdez Palacios Fatima Isabel

FECHA DE ENTREGA: lunes 21 de Abril de 2014

Objetivos: Aplicar los conocimientos vistos en clase para realizar un multiplicador x5 de un digito BCD donde se desea la implementacin mnima. Introduccin: El cdigo binario decimal o BCD (del ingls Binary Coded Decimal) es un sistema de numeracin no posicional que representa a los nmeros enteros positivos. Por ejemplo, teniendo la siguiente correspondencia entre las diez cifras decimales y sus correspondientes representaciones binarias: 0000 = 0 0001 = 1 0010 = 2 0011 = 3 0100 = 4 0101 = 5 0110 = 6 0111 = 7 1000 = 8 1001 = 9 Como se observa con BCD slo se utilizan 10 de las 16 posibles combinaciones que se pueden formar con nmeros de 4 bits, por lo que el sistema pierde capacidad de representacin y se requiere ms espacio, aunque se facilita la interpretacin humana. La codificacin de un nmero se realiza asignando a cada dgito de su representacin decimal el nibble correspondiente: 0101 0000 = 50 0101 1001 0001 0000 0111= 59107 0001 0001 0010 = 112 1001 1001 1001 = 999 0110 0101= 65 0110 0110 0110 = 666

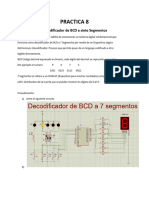

La ventaja del cdigo BCD frente a la representacin binaria clsica en los ordenadores es que no hay un lmite inicial para el tamao de un nmero. El formato binario estaba limitado por el tamao de palabra utilizado por el procesador (8, 16 o 32 bits), con lo que el mayor nmero que se puede representar ser 256, 65536 o 4294967296. Por el contrario utilizando BCD aadir un nuevo dgito slo implica aadir una nueva secuencia de 4 bits. El desarrollo del hardware ha hecho menos relevante esta cualidad. El bit mas significativo usa un decodificador 74LS48:

Para los bits menos significativos se utiliz una compuerta de

Desarrollo: Disear un multiplicador x5 de un digito en BCD con salida en un display de 7 segmentos (se desea la implementacin minina):

En las compuertas que utilizamos el bit ms significativo usa un decodificador 74LS48 y el menos significativo usa una compuerta de negacin 74LS04

El bit mas significativo usa un decodificador 74LS48:

Para los bits menos significativos se utiliz una compuerta de negacin

El bit menos significativo tiene 4 LEDs que siempre estarn prendidos puesto que los 4 LEDs que tienen en comn son el 0 y el 5

Entrada de Variables (Dgitos del 0 al 9) A 0 0 0 0 0 0 0 0 1 1 B 0 0 0 0 1 1 1 1 0 0 C 0 0 1 1 0 0 1 1 0 0 D 0 1 0 1 0 1 0 1 0 1

Salidas Decenas D2 0 0 0 0 0 0 0 0 1 1 D1 0 0 0 0 1 1 1 1 0 0 D0 0 0 1 1 0 0 1 1 0 0 U2 0 1 0 1 0 1 0 1 0 1 Unidades U1 0 0 0 0 0 0 0 0 0 0 U0 0 1 0 1 0 1 0 1 0 1

Donde: D2 = A D1 = B D0 = C Patrigrama: U2 = U0 = D U1 = 0

Elaboracin: Entrada 02 = 010 Salida 0x5=0 Entrada 10102 = 1010 Salida 10 x 5 = 50 Entrada 10012 = 910 Salida 9 x 5 = 45 Entrada 01012 = 510 Salida 5 x 5 = 25

Conclusin Se puede deducir a partir la tabla de verdad las funciones salen directas simplemente implementando con un decodificador para convertir las entradas que estn en BCD en M lneas de salida que se representaron en decimal mediante el display de 7 segmentos. Mediante el display de 7 segmentos fue ms fcil identificar la respuesta ya que para mostrar la respuesta se saba que 4 LEDs que siempre estaran prendidos porque tienen en comn el 0 y el 5.

Acomodando a las variables de este modo, el multiplicador fue econmicamente barato de hacer. Su ventaja es que se utiliz la mnima cantidad de material posible para transmitir la seal deseada de entrada. Bibliografa http://sergiorendain.blogspot.mx/2011/08/codigo-bcdcodigo-gray-alfa-numerico.html

Das könnte Ihnen auch gefallen

- Proyecto 4 Diseño Digital Control de Corriente Alterna Con Un Decodificador DigitalDokument5 SeitenProyecto 4 Diseño Digital Control de Corriente Alterna Con Un Decodificador DigitalRicardo Guzmán100% (1)

- Proyecto Final Diseño Digital UNAMDokument6 SeitenProyecto Final Diseño Digital UNAMAlex AlbíterNoch keine Bewertungen

- Práctica 3 Diseño Digital ModernoDokument17 SeitenPráctica 3 Diseño Digital ModernoJuanVazquez100% (1)

- Sumador de 4 Palabras de 2 Bits.Dokument5 SeitenSumador de 4 Palabras de 2 Bits.Miguel GuzmanNoch keine Bewertungen

- Practica #2 Laboratorio de Análisis de Circuitos Eléctricos FIDokument13 SeitenPractica #2 Laboratorio de Análisis de Circuitos Eléctricos FICarlos FraustoNoch keine Bewertungen

- Fuente de Alimentación - AyalaAlbanya - GarcíaArturo - RodríguezRogelioDokument5 SeitenFuente de Alimentación - AyalaAlbanya - GarcíaArturo - RodríguezRogelioAlbanya Yendalli Ayala TrejoNoch keine Bewertungen

- LFSC Práctica Distorsión LinealDokument10 SeitenLFSC Práctica Distorsión LinealRodrigo TorresNoch keine Bewertungen

- Previo 4Dokument4 SeitenPrevio 4Jose Luis Erazo DuranNoch keine Bewertungen

- Practica 7 LAMGDokument12 SeitenPractica 7 LAMGMelesio García Luis AntonioNoch keine Bewertungen

- Sumador de 2 Palabras de 4 Bits Con Carry Look AheadDokument7 SeitenSumador de 2 Palabras de 4 Bits Con Carry Look AheadPaul Andrés Fernández Carrillo100% (2)

- Reporte Practica 1 Circuitos ElectricosDokument6 SeitenReporte Practica 1 Circuitos ElectricosRichard Hdz0% (1)

- Práctica 5: Distorsión Lineal (Sistema de Comunicaciones FI)Dokument10 SeitenPráctica 5: Distorsión Lineal (Sistema de Comunicaciones FI)Joel GonzalezNoch keine Bewertungen

- Previo2 Sistemas de Comunicaciones Fi UnamDokument4 SeitenPrevio2 Sistemas de Comunicaciones Fi UnamLUIS BARRERANoch keine Bewertungen

- Previo 3 SCEDokument2 SeitenPrevio 3 SCEDranNoch keine Bewertungen

- LSC Práctica #06 Distorsion AlinealDokument7 SeitenLSC Práctica #06 Distorsion AlinealKevin Alvarado100% (1)

- Práctica No7Dokument9 SeitenPráctica No7sanyNoch keine Bewertungen

- Cuestionario Previo 1 Diseño Digital FI UNAMDokument8 SeitenCuestionario Previo 1 Diseño Digital FI UNAMPandaNoch keine Bewertungen

- Morris Mano EjerciciosDokument12 SeitenMorris Mano EjerciciosMaura SichaNoch keine Bewertungen

- Practica 1 Sistemas de Comunicaciones Electronicas FIDokument9 SeitenPractica 1 Sistemas de Comunicaciones Electronicas FIjose joseNoch keine Bewertungen

- Practica 6 Sistemas de Comunicaciones Electronicas Distorsion AlinealDokument7 SeitenPractica 6 Sistemas de Comunicaciones Electronicas Distorsion AlinealSteve ResidenceNoch keine Bewertungen

- Práctica 2 Diseño Digital, Introducción Al Software de Descripción de Hardware y Compuertas LógicasDokument15 SeitenPráctica 2 Diseño Digital, Introducción Al Software de Descripción de Hardware y Compuertas LógicasJorge Ojeda100% (1)

- p3 Analisis de Señales DeterministicasDokument11 Seitenp3 Analisis de Señales DeterministicasOmar CasillasNoch keine Bewertungen

- Examen Sistemas de TelecomunicacionesDokument10 SeitenExamen Sistemas de TelecomunicacionesLuisMLNoch keine Bewertungen

- G13 Teorema de ParsevalDokument4 SeitenG13 Teorema de ParsevalRoslyn Fedra Cruz CastroNoch keine Bewertungen

- Astable y MonoestableDokument24 SeitenAstable y MonoestableOmar Ruiz Rodríguez83% (6)

- Práctica 6 Circuitos ElectronicosDokument10 SeitenPráctica 6 Circuitos ElectronicosRodrigoNoch keine Bewertungen

- Practica 2 Diseño Digital FI UNAMDokument7 SeitenPractica 2 Diseño Digital FI UNAMLUIS BARRERANoch keine Bewertungen

- Práctica 5 DDM UnamDokument11 SeitenPráctica 5 DDM UnamJuanVazquezNoch keine Bewertungen

- Practica 4 DigitalDokument14 SeitenPractica 4 DigitalLuis Fernando Hernandez LopezNoch keine Bewertungen

- Practica 6 de SistemasDokument5 SeitenPractica 6 de SistemasAndres MuñozNoch keine Bewertungen

- Practica 7Dokument13 SeitenPractica 7Eduardo RojasNoch keine Bewertungen

- SD Gr8 Conchambay Alexis Practica#11 InformeDokument2 SeitenSD Gr8 Conchambay Alexis Practica#11 InformeAlexis ConchambayNoch keine Bewertungen

- Práctica 4Dokument13 SeitenPráctica 4JuanVazquezNoch keine Bewertungen

- Práctica 8 Filtros EléctricosDokument7 SeitenPráctica 8 Filtros EléctricosErick Ivan Barcenas MartinezNoch keine Bewertungen

- Practica 2 ANÁLISIS DEL ESTADO SENOIDAL PERMANENTE DE CIRCUITOS LINEALESDokument8 SeitenPractica 2 ANÁLISIS DEL ESTADO SENOIDAL PERMANENTE DE CIRCUITOS LINEALESjose joseNoch keine Bewertungen

- Cuestionario Previo 5Dokument5 SeitenCuestionario Previo 5index plus100% (1)

- Previo Practica 7 Analisis de CircuitosDokument2 SeitenPrevio Practica 7 Analisis de CircuitosOmar AC50% (2)

- Previo 1 - Laboratorio de Sistemas de Comunicaciones, Facultad de Ingeniería.Dokument2 SeitenPrevio 1 - Laboratorio de Sistemas de Comunicaciones, Facultad de Ingeniería.Daniel_Hdz_GNoch keine Bewertungen

- Práctica 5 C.E. FiDokument7 SeitenPráctica 5 C.E. FiMario_zym100% (1)

- Diseñe e Implemente Un Circuito SumadorDokument4 SeitenDiseñe e Implemente Un Circuito SumadorJuan Luis Mamani SirpaNoch keine Bewertungen

- Circuito SujetadorDokument6 SeitenCircuito SujetadorEdison ChicaizaNoch keine Bewertungen

- Reporte Practica 3 Diseño DigitalDokument6 SeitenReporte Practica 3 Diseño DigitalDaniel MorenoNoch keine Bewertungen

- Ejercicio Resuelto - MultietapasDokument6 SeitenEjercicio Resuelto - MultietapasJorge Andres Guevara Reyes100% (2)

- Practica-6 Distorsion LinealDokument10 SeitenPractica-6 Distorsion LinealJosh WayneNoch keine Bewertungen

- Cuestionario Previo Medicion e Instrumentacion Previo 2Dokument2 SeitenCuestionario Previo Medicion e Instrumentacion Previo 2Grzzly AVNoch keine Bewertungen

- Práctica 3Dokument14 SeitenPráctica 3Jarenny MartínezNoch keine Bewertungen

- Practica1 Diseño Digital ModernoDokument10 SeitenPractica1 Diseño Digital ModernoJuanVazquezNoch keine Bewertungen

- Análisis Senoidal Permanente de Circuitos Trifásicos Balanceados y DesbalanceadosDokument12 SeitenAnálisis Senoidal Permanente de Circuitos Trifásicos Balanceados y DesbalanceadosHugo98Noch keine Bewertungen

- Practica 1 Polarizacion FET 1Dokument11 SeitenPractica 1 Polarizacion FET 1Ma-Elisa EscobarNoch keine Bewertungen

- Cuestionario Previo 6 Diseño Digital FI UNAMDokument3 SeitenCuestionario Previo 6 Diseño Digital FI UNAMPandaNoch keine Bewertungen

- Cuestionario Previo A La Practica 8Dokument2 SeitenCuestionario Previo A La Practica 8Vicente RuizNoch keine Bewertungen

- Previo 7 - Sistemas de Comunicaciones Electrónicas - Alarcón Fuertes Ricardo RodrigoDokument5 SeitenPrevio 7 - Sistemas de Comunicaciones Electrónicas - Alarcón Fuertes Ricardo RodrigoRicardo FuertesNoch keine Bewertungen

- Practica No. 2 de Sistemas de Datos Muestreados 1 PDFDokument14 SeitenPractica No. 2 de Sistemas de Datos Muestreados 1 PDFPaola YllañisNoch keine Bewertungen

- Conversión de Código Gray A 7 SegmentoDokument8 SeitenConversión de Código Gray A 7 SegmentoValentina RoyeroNoch keine Bewertungen

- Electronica para Ingenieros-Opamp 14.0Dokument147 SeitenElectronica para Ingenieros-Opamp 14.0w6110Noch keine Bewertungen

- Z80division Montenegro 2085Dokument14 SeitenZ80division Montenegro 2085Mikael Montenegro100% (1)

- Practica 7: Escalamiento de Impedancia y de FrecuenciaDokument10 SeitenPractica 7: Escalamiento de Impedancia y de FrecuenciaSevy Tom Zoriuq0% (1)

- Sistema de Comunicaciones Practica2Dokument7 SeitenSistema de Comunicaciones Practica2Albanya Yendalli Ayala TrejoNoch keine Bewertungen

- PracticasDokument1 SeitePracticasGASTON SOLORZA LEYVANoch keine Bewertungen

- Código BCD (Autoguardado)Dokument15 SeitenCódigo BCD (Autoguardado)Luis RobledoNoch keine Bewertungen

- Tema 3 Bloque I BioenergeticaDokument11 SeitenTema 3 Bloque I BioenergeticaPamelitha Huayanca CarbajalNoch keine Bewertungen

- Resumen RLCDokument8 SeitenResumen RLCBRANDON JAIR BARRANCO VEGANoch keine Bewertungen

- Ficha Sobre PotenciasDokument2 SeitenFicha Sobre PotenciasDiana Elisabeth Alvarado BarrientosNoch keine Bewertungen

- Movimiento OndulatorioDokument4 SeitenMovimiento OndulatorioDANIEL ALEXANDER CASTRO BALLESTASNoch keine Bewertungen

- EPA 452 - Tecnologia de Control de Contaminacion Del AireDokument6 SeitenEPA 452 - Tecnologia de Control de Contaminacion Del AireCesar Muñoz OssesNoch keine Bewertungen

- 4# Medios FisicosDokument10 Seiten4# Medios FisicosFernando coelloNoch keine Bewertungen

- Bicarbonato de Sodio (M-I)Dokument8 SeitenBicarbonato de Sodio (M-I)José Manuel Quintero PardoNoch keine Bewertungen

- Diapositivas para Temario Inventor 2021Dokument10 SeitenDiapositivas para Temario Inventor 2021Almagesto QuenayaNoch keine Bewertungen

- Curso de Javascript PDFDokument31 SeitenCurso de Javascript PDFFrancisco JavierNoch keine Bewertungen

- INFORME #7 Proctor ModificadoDokument18 SeitenINFORME #7 Proctor ModificadoRomarioVasquezGomezNoch keine Bewertungen

- Cuadro Comparativo de Los Tipos de Soldadura.Dokument4 SeitenCuadro Comparativo de Los Tipos de Soldadura.MarcoNoch keine Bewertungen

- Ejercicio s05 - Velocidad Real de Flujo - 2021 - II - Barrios Rosas JamerDokument6 SeitenEjercicio s05 - Velocidad Real de Flujo - 2021 - II - Barrios Rosas JamerBarrios Rosas JamerNoch keine Bewertungen

- La Interpretación Geométrica de La DerivadaDokument7 SeitenLa Interpretación Geométrica de La DerivadaVicente de Paulo Pérez CastilloNoch keine Bewertungen

- Apertura de Centro de Apoyo Escolar - InformeDokument41 SeitenApertura de Centro de Apoyo Escolar - Informejeanine Alejandra Cano SilesNoch keine Bewertungen

- Mega Subasta ResueltaDokument36 SeitenMega Subasta ResueltamiguelNoch keine Bewertungen

- Cuestionario - Termo - Guía de Laboratorio 3Dokument7 SeitenCuestionario - Termo - Guía de Laboratorio 3Ramsés Pilco ZavalaNoch keine Bewertungen

- Problema Del ViajanteDokument2 SeitenProblema Del ViajanteJimy el rosqueteNoch keine Bewertungen

- Fisica 3Dokument5 SeitenFisica 3Yanza GomezNoch keine Bewertungen

- Calculo Diferencial e Integral Full TOMO1 2023 PDFDokument463 SeitenCalculo Diferencial e Integral Full TOMO1 2023 PDFKranner SamaNoch keine Bewertungen

- Trabajo Final Caf 3Dokument17 SeitenTrabajo Final Caf 3Junior Romero PerezNoch keine Bewertungen

- CALIPERDokument6 SeitenCALIPEROswaldo GallardoNoch keine Bewertungen

- PaumatcsiialgebraDokument14 SeitenPaumatcsiialgebraAbel Sarcco UstoNoch keine Bewertungen

- Antropometria Calculo DietaDokument3 SeitenAntropometria Calculo Dietamarena loorNoch keine Bewertungen

- Seminario - Grupo 5Dokument13 SeitenSeminario - Grupo 5FRANK JESUS ROJAS GUTIERREZNoch keine Bewertungen

- Puertas de BanoDokument18 SeitenPuertas de BanomarcoNoch keine Bewertungen

- Adaptación Vegetal Al Medio AmbienteDokument2 SeitenAdaptación Vegetal Al Medio Ambienteroger vargas oreNoch keine Bewertungen

- Soluciones MFIDokument6 SeitenSoluciones MFIMarianela GambelliNoch keine Bewertungen

- Semana 9 - Media, Mediana y ModaDokument8 SeitenSemana 9 - Media, Mediana y ModaLiliana AlcantaraNoch keine Bewertungen

- Modelo Matematico EmpiricoDokument10 SeitenModelo Matematico EmpiricoMixy Pereda TupalayaNoch keine Bewertungen

- Deber de ConversionesDokument4 SeitenDeber de ConversionesFranchesca RobalinoNoch keine Bewertungen