Beruflich Dokumente

Kultur Dokumente

PIC 16F877 Resumen Tecnico

Hochgeladen von

nicortele2390Originalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

PIC 16F877 Resumen Tecnico

Hochgeladen von

nicortele2390Copyright:

Verfügbare Formate

MICROCONTROLADOR PIC 16F877 CARACTERSTICAS: 1 PRINCIPALES CARACTERSTICAS Se enumeran las prestaciones y dispositivos especiales que rodean a los PIC16

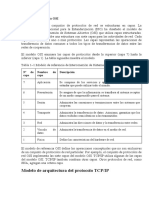

!"#$$ Procesador de arquitectura RISC avan%ada &ue'o de solo () instrucciones con 1* +its de lon'itud$ Todas ellas se e,ecutan en un ciclo de instrucci-n. menos las de salto que tardan dos$ /asta !0 pala+ras de 1* +its para la 1emoria de Pro'rama. tipo LAS/ en los modelos 16 !"6 y 16 !"" y *02 de memoria para los PIC 16 !"( y 16 !"*$ /asta (6! 2ytes de memoria de 3atos RA1$ /asta 4)6 2ytes de memoria de 3atos EEPR51$ Pines de salida compati+les para el PIC 16C"(6"*6"66""$ /asta 1* 7uentes de interrupci-n internas y e8ternas$ Pila de ! niveles$ 1odos de direccionamiento directo e indirecto$ Po9er:on Reset ;P5P<$ Tempori%ador Po9er:on ;P5P< y 5scilador Tempori%ador Start:=p ;5ST<$ Perro >uardi?n ;@3T<$ C-di'o de protecci-n pro'rama+le$ 1odo SLEEP de +a,o consumo$ Pro'ramaci-n serie en circuito con dos pines$ Solo necesita )A para pro'ramarlo en este modo$ Aolta,e de alimentaci-n comprendido entre 4 y ).) A$ 2a,o consumoB C 4 mA valor para ) A y * 1D% 4E FA para (A y (4 1D% C1 FA en stand+y i'ura 1$: Encapsulado P3IP de *E pines DISPOSITIVOS PERIFRICOS TirnerEB Tempori%ador:contador de ! +its con preescaler de ! +its TimerlB Tempori%ador:contador de 16 +its con preescaler que puede incrementarse en modo sleep de 7orma e8terna por un cristal6clocG$ Timer4B Tempori%ador:contador de ! +its con preescaler y postescaler$ 3os m-dulos de Captura. Comparaci-n. P@1 ;1odulaci-n de AncDura de Impulsos<$ Conversor A63 de 1 E +its$ Puerto Serie SHncrono 1aster ;1SSP< con SPI e I4C ;1aster6Slave<$ =SART6SCI ;=niversal SyncDeronus AsyncDronous Receiver Transmitter< con I +it$ Puerta Paralela Esclava ;PSP< solo en encapsulados con *E pines DIFERENCIAS ENTRE, LOS MODELOS DE 28 Y LOS DE 40 PATITAS El PIC 16 !"( y el !"6 tienen 4! pines. mientras que el PIC 1 6 !"* y !"" tienen *E$

Nos centraremos en el PIC 16 !"( y las di7erencias que tiene con sus Dermanos son mHnimas y se detallan a continuaci-nB 1$ Los modelos de *E pines disponen de ) Puertos de E6SB A. 2. C. 3 y E. mientras que los de 4! solo tienen ( PuertosB A. 2 y C$ 4$ Los modelos de *E pines tienen ! canales de entrada al Conversor A63. mientras que los de 4! solo tienen ) canales$ ($ S-lo poseen la Puerta Paralela Esclava los PIC 16 !"# de *E pines$ EL PIC 16F87X 2a,o el nom+re de esta su+7amilia de microcontroladores. actualmente encontramos cuatro modelosB EL PIC 16 !"(6*66 y "$ Estos microcontroladores disponen de una memoria e pro'rama LAS/ de * a ! 02ytes de 1* +its. considera+le menta superior 7rente al PIC 16 !* en el que solo disponHamos de l 0+yte de 1* +its$ 3e los microcontroladores indicados. el 16 !"( y el 16 S"6 son de 4! pines. mientras que 16 !"* y el 16 !"" tienen *E patillas. lo que les permite disponer de Dasta (( lHneas de E6S$ En su arquitectura adem?s incorporanB J Aarios Timer J =SART J 2us 14C En la Ta+la 1 se muestran las caracterHsticas comparativas m s relevantes de esta 7amilia de microcontroladores B Cara !"r#$!% a$ 16F87& 16F874 16F876 16F877 recuencia 1?8ima 3C:4E1D% 3#:4E1D% 3#:4E1D% 3#:4E1D% 1emoria de pro'rama *02 *02 !02 !02 LAS/ Pala+ra de 1* +its Posiciones RA1 de 1I4 1I4 (6! (6! datos Posiciones EEPR51 de 14! 14! 4)6 4)6 datos Ports E6S A. 2 y C A. 2. C y 3 A. 2 y C A. 2. C y 3 NK de Pines 4! *E 4! *E Interrupciones 1( 1* 1( 1* Timers ( ( ( ( 1-dulos CCP 4 4 4 4 Comunicaciones Serie 1SSP. 1SSP.=SART 1SSP.=SART 1SSP. =SART =SART Comunicaci-n Paralelo : PSP : PSP LHneas de entrada en ) ! ) ! Convertidor A63 de 1E +its &ue'o de Instrucciones () () () () instrucciones instrucciones instrucciones instrucciones Lon'itud de la 1* +its 1* +its 1* +its 1* +its instrucci-n Ta+la 1$: Comparaci-n de entre los PIC de la amilia 16 !"# 3ESCRIPCILN >L52AL 3EL 3ISP5SITIA5 Este documento contiene la in7ormaci-n especH7ica del dispositivo$ Se puede encontrar in7ormaci-n adicional del PICmicro T1 en el 1anual de Re7erencia de los PIC de la 'ama media. ;3S((E4(< que se puede o+tener en el website de Microchip$ El 1anual de re7erencia de+e ser considerado un documento complementario a estos datos. y recomenda+le leerlo para entender me,or la arquitectura del dispositivo y el 7uncionamiento de los m-dulos peri7Mricos$ La 7amilia consta de cuatro dispositivos ;PIC16 S"(. PIC16 !"*. PIC16 !"6 y

PIC 16 !""< en estas Do,as de datos$ Los PIC 1 6 !"66!"( entran en el +loque de dispositivos encapsulados en 4!:pines y los PIC 1 6 !""6!"* entran en el +loque de dispositivos encapsulados en *E pines$ Los dispositivos de 4!:pines no tienen implementado el puerto paralelo esclavo$ Las si'uientes 7i'uras corresponden a los dia'ramas de +loque de los dispositivos ordenados por el nNmero de pinesO El 4!:pines en la i'ura ( y los de *E:pines en$ la i'ura *$ En las Ta+las 4 y ( Day un listado de los mismos$

i'ura 1$: 3ia'rama de 2loques del PIC16 !"* y 16 !"" OR'ANI(ACI)N DE LA MEMORIA /ay tres +loques de memoria en cada uno de estos PlCmicro 1C=s$ La 1emoria de Pro'rama y la 1emoria de 3atos que tienen los +uses separados para poder permitir el acceso simult?neo a estos dos +loques$ El tercer +loque que la 1emoria de datos EEPR51 se descri+e en la Secci-n ( de este manual$ La in7ormaci-n adicional so+re la memoria del dispositivo puede encontrarse en el manual de re7erencia de los PICmicros de 'ama media ;3S((E4(<$ Or*a+%,a %-+ ." /a M"01r%a ." 2r1*ra0a

Los dispositivos de PIC 16 !"# tienen un contador de pro'rama de 1(:+its capa% de direccionar !08l* posiciones de memoria$ Los dispositivos de PIC16 !""6!"6 tienen !0 8 1* posiciones de memoria de pro'rama tipo LAS/ y el PIC 1 6 !"(6!"* tienen *08 1*$ Acceder a una posici-n de memoria no implementada. provoca la lectura o escritura de la posici-n de memoria envolvente$ El vector de Reset est? en la posici-n de memoria EEEED y el vector de interrupci-n est? en la posici-n de memoria EEE*D$

i'ura 4$: 1apa de 1emoria y STAC0 del PIC16 !""6!"! OR'ANI(ACI)N DE LA MEMORIA DE DATOS La memoria de los datos se divide en los mNltiples +ancos que contiene los Re'istros del Prop-sito >enerales y Los Re'istros de la unciones especiales Los +it RP1 ;STAT=S C6P y RPE ;el ESTA35 C)P seleccionan cada uno de estos +ancos. de acuerdo a la si'uiente ta+laB RP1 RP0 3a+ 1 E E 2anco E E 1 2anco 1 1 E 2anco 4 1 1 2anco ( Ta+la 4$: Selecci-n de los +ancos de memoria RA1 con RPE y RP1 En cada +anco Day " D posiciones de memoria ;14! +ytes<$ Las posiciones m?s +a,as est?n. reservadas para los Re'istros de unciones Especiales$ Por encima de los Re'istros de unciones Especiales se encuentran los Re'istros de Prop-sito >eneral. que se utili%an como posiciones de memoria RA1 est?tica$ Todos est?n estructurados en +ancos$ Al'unos Re'istros de unciones Especiales est?n re7le,ados en varios +ancos para reducir el c-di'o y tener un acceso m?s r?pido$

RE'ISTROS DE F4NCIONES ESPECIALES 5F6S6SR7 Los Re'istros de unciones Especiales ;S R< son re'istros usados por la CP= y los m-dulos peri7Mricos para controlar el 7uncionamiento deseado del dispositivo$ Estos re'istros est?n reali%ados como RA1 est?tica$ =n listado de estos re'istros es el que se muestra en la Ta+la )$ Los Re'istros de unci-n Especiales podemos clasi7icarlos en dos tipos. los correspondientes al la CP= y los que controlan los peri7Mricos$ Los re'istros que a7ectan directamente a la CP= se descri+en se'uidamente con detalle$ Aquellos re'istros relacionados con el 7uncionamiento de los peri7Mricos se descri+en en el apartado correspondiente al peri7Mrico$ RE>ISTR5 3E STAT=S ;3irecciones E(D. !(D.1E(D. 1!(D< P P P R6@:E R6@:E R6@:E R:1 R:1 R6@:8 IRP RP1 RP0 8T0 8PD ( 2it "

P R6@:8 DC

P R6@:8 C 2it E

+it "B IRPB Selecci-n de +ancos para el direccionamiento indirecto 1 Q 2ancos 4 y ( ;1 EED: 1 D< EQ 2ancos E y 1 ;EED: D< +it 6:)B RP1:RP0B Selecci-n del +anco para el direccionamiento directo 11 Q 2anco ( ;1 !ED: 1 D< 1E Q2anco 4;1EED:1" D< E1 Q2anco 1 ;!ED: D< EE Q 2anco E ;EED:" D< Cada 2anco es de 14! +ytes +it *B8TOB la' de Timer 5ut 1Q 3espuMs de conectar A33 o e,ecutar CLR@3T o SLEEP EQ Al des+ordarse el tempori%ador de @3T +it (B8PDB la' de Po9er 3o9n 1Q 3espuMs de conectar A33 o al e,ecutar la instrucci-n CLR@3T E Q Al e,ecutar la instrucci-n SLEEP +it 4B (B la' de Cero 1Q El resultado de la Nltima operaci-n aritmMtica o l-'ica es Cero EQ El resultado de la Nltima operaci-n aritmMtica o l-'ica es distinto cero +it 1B DCB la' de acarreo en el *K +it de menos peso 1 Q Acarreo en la suma E Q No acarreo en la suma En la resta es al contrario +it EB CB la' de acarreo en el octavo +it 1 Q Se Da producido un acarreo en la suma y no en la resta EQ Se Da producido un acarreo en la resta y no en la suma Este +it tam+iMn se utili%a en las instrucciones de rotaci-n RE'ISTRO OPTION 9 OPTION:RE' 5D%r" %-+ 81;,181;7 El Re'istro de OPTION:RE' es un re'istro que puede ser leHdo o escrito y que contiene varios +its de control para con7i'urar la asi'naci-n del preescaler al TMR0 o al @3T. la interrupci-n e8terna. el TMR0 y las resistencias de pull:up del PORT3$ Nota$: Asi'nar el preescaler como 1B 1 al re'istro TMR0. asi'na el preescaler al <a! ;.1*$ R6@:1 R3P4 2it " R6@:1 INTED R6@:1 T0CS R6@:1 T0SE R6@:1 PSA R6@:1 PS2 R6@:1 PS1 R6@:1 PS0 2it E

2it "B 8R3P4B Resistencia de Pull:up en. el P5RT2 1QResistencia de Pull:up desactivada EQ Resistencia de Pull:up activada +it6 1BINTED'B. lanco. de control de interrupciones 1BInterrupci-n por 7lanco ascendente en el pin R2E6INT. EBInterrupci-n por 7lancoB descendente en el pin R2E6INT +it )B T0SC$ Selecci-n del tipo de Relo, para T1R5 1 Q Los pulsos se introducen a travMs del. pin RA*6T5C01 E Q Los Pulsos de relo, internos: osc6* +it *B T0SEB Tipo de 7lanco para TMR0 1 Q Incremento de TMR0 en cada 7lanco. descendente por el pin RA*6T5C0I E Q Incremento de TMR0 en cada 7lanco ascendente Bpor el pin RA*6T5C0I +it (B PSAB. Asi'naci-n del Preescaler 1 Q El preescaler se le asi'na al <DT E Q El preescaler se le asi'na al TMR0 +it 4:EB PS2:PS0B Ran'o de actuaci-n del preescaler PS4 PS1 PSE 3ivisor de T1RE 3ivisor de @3T E E E 1B4 1B1 E E 1 1B* 1B4 E 1 E 1B! 1B* E 1 1 1B16 1B! 1 E E 1B(4 1B16 1 E 1 1B6* 1B(4 1 1 E 1B14! 1B6* 1 1 1 1B4)6 1B14!

RE'ISTRO INTCON 5D%r" %-+ 03;, 83;, /03;, 183;7 El re'istro INTC5N es un re'istro de lectura y escritura que contiene los +it de Da+ilitaci-n de interrupciones por des+ordamiento de TMR0 por cam+io de nivel en el P5RT2 e interrupciones e8ternas por la lHnea R3O=INT$ P P P R6@:E R6@:E R6@:E R6@:E R6@:E R6@:E R6@:E R6@:8 'IE PEIE T0IE INTE R3IE T0IF INTF R3IF 2it " 2it E +it "B 'IEB +it de Da+ilitaci-n 'lo+al de Interrupciones 1Q /a+ilita el permiso de interrupciones EQ InDa+ilita todas las interrupciones +it 6B PEIEB +it de Da+ilitaci-n de interrupciones de los peri7Mricos que no se controla con el re'istro INTC5N 1Q /a+ilita el permiso de interrupciones de los peri7Mricos EQ InDa+ilita las interrupciones de los peri7Mricos +it )B T0IEB +it de Da+ilitaci-n de la interrupci-n por des+ordamiento del T1RE 1Q /a+ilita la interrupci-n EQ InDa+ilita la interrupci-n +it *B INTEB +it de Da+ilitaci-n de la interrupci-n e8terna por el pin R2E6INT 1Q /a+ilita la interrupci-n EQ InDa+ilita la interrupci-n +it (B R3IEB +it de Da+ilitaci-n de interrupci-n por cam+io de nivel en el P5RT2 1Q /a+ilita la interrupci-n EQ InDa+ilita la interrupci-n +it 4B T0IFB 7la' de indicaci-n de des+ordamiento de T1RE

1Q El T1RE se Da des+ordado$ Se +orra por so7t9are EQ El T1RE no se Da des+ordado +it 1B INTFB 7la' de estado de la interrupci-n e8terna INT 1Q La interrupci-n e8terna se Da producido$ Se +orra por so7t9are EQ La interrupci-n e8terna no se Da producido +it EB R3IFB 7la' de indicaci-n de interrupci-n por cam+io de nivel en P5RT2 1Q Se Da producido un cam+io de nivel en los pines R2"BR2*$ Se +orra por so7t9are$ EQ No se Da producido un cam+io de nivel en los pines R2"BR2* RE'ISTRO PIE1 5D%r" %-+ 8C;7 Este re'istro contiene los +it individuales de Da+ilitaci-n de interrupciones de los peri7Mricos Nota$: El +it PEIE ;INTC5N C6P< de+e esta a uno para Da+ilitar las interrupciones de cualquiera de los peri7Mricos$ R6@:E R6@:E R6@:E R6@:E R6@:E R6@:E R6@:E R6@:E PSPIE517 ADIE RCIE TXIE SSPIE CCP1IE TMR2IE TMR1IE 2it " 2it E +it "B PSPIEB +it de Da+ilitaci-n de interrupci-n por lectura 6 escritura en el Puerto Paralelo Esclavo$ Para los modelos de *E pines$ 1 Q /a+ilita la interrupci-n por lectura6escritura en el PSP EQ inDa+ilita la interrupci-n por lectura6escria en el PSP +it 6B ADIFB +it de Da+ilitaci-n de interrupci-n por 7inali%aci-n de la conversi-n A63 l Q /a+ilita la interrupci-n del convertidor A63 E Q InDa+ilita la interrupci-n del convertidor A63 +it )B RCIEB +it de Da+ilitaci-n de interrupci-n en recepci-n por el =SAR. cuando se llena el +u77er. 1 Q /a+ilita interrupci-n por recepci-n en el =SAR E Q InDa+ilita interrupci-n por recepci-n en el =SAR +it *B TXIEB +it de interrupci-n al transmitir por el =SAR. cuando se vacHa el +u77er$ 1 Q /a+ilita la interrupci-n de transmisi-n por el =SAR E Q InDa+ilita la interrupci-n de transmisi-n por el =SAR +it (B SSPIEB +it de Da+ilitaci-n de interrupci-n por el Puerto Serie SHncrono ;SSP< 1Q /a+ilita la interrupci-n del SSP EQ InDa+ilita la: interrupci-n del SSP +it 4B CCP1IEB +it de Da+ilitaci-n de interrupci-n del m-dulo CCPI cuando se produce una captura o una comparaci-n$ 1Q /a+ilita la interrupci-n del CCPI EQ$ InDa+ilita la interrupci-n del CCPI +it 1B TMR2IEB +it de Da+ilitaci-n de interrupci-n por des+ordamiento de TMR2 que est? empare,ado con el re'istro PR4 ;I4D< 1Q /a+ilita la interrupci-n por des+ordamiento de TMR2 empare,ado a PR2 EQ InDa+ilita la interrupci-n de TMR2 empare,ado a PR4 +it EB TMR1IEB +it de Da+ilitaci-n de interrupci-n por des+ordamiento del T1RI 1Q /a+ilita la interrupci-n por des+ordamiento de T1R1 EQ InDa+ilita la interrupci-n por des+ordamiento de T1R1 Nota 1$: PSPIE para los dispositivos de 4! pines. siempre mantiene este +it a cero RE'ISTRO PIRI 5D%r" %-+ 0C;7 El re'istro de PIRI contiene los 7la's individuales que indican las interrupciones provocadas por los peri7Mricos$ P P P P P P P P

R6@:E PSPIF 2it "

R6@:E ADIF

R6@:E RCIF

R6@:E TXIF

R6@:E SSPIF

R6@:E R6@:E R6@:8 CCP1IF TMR21F TMR1IF 2it E

+it "B PSPIFB la' de Lectura6Escritura por el Puerto Paralelo esclavo 1Q Concedido el permiso de interrupci-n para la puerta paralela esclava al reali%ar una operaci-n de Lectrura6Escritura$ En los modelos de *E pines EQ No est? permitida la interrupci-n +it 6B ADIFB la' de 7inal de conversi-n del convertidor A63 1Q El convertidor A63 Da 7inali%ado la conversi-n EQ El convertidor A63 no Da 7inali%ado la conversi-n +it ) RCIFB la' de recepci-n por el =SAR 1Q El +u77er de datos reci+idos por el =SAR est? lleno EQ El +u77er de datos reci+idos por el =SAR no est? lleno +it *B TXIFB la' de transmisi-n el =SAR 1Q El +u77er de datos a transmitir no est? lleno EQ El +u77er de daos a transmitir est? lleno +it (B SSPIFB la' de interrupci-n del Puerto Serie SHncrono ;SSP< 1Q La condici-n del SSP Da ocurrido. de+e ponerse a cero por so7t9are antes de volver del pro'rama de atenci-n a la interrupci-n$ Las condiciones que soporta este +it son SPI /a tenido lu'ar una Transmisi-n 6 Recepci-n I2C S/a>" /a tenido lu'ar una Transmisi-n 6 Recepci-n I2C Ma$!"r /a tenido lu'ar una Transmisi-n 6 Recepci-n La condici-n de salida iniciada se complet- por el m-dulo de SSP$ La condici-n de parada inicio se complet- por el m-dulo de SSP$ La condici-n de reiniciali%aci-n se completo por el m-dulo SSP =na condici-n de la salida se Da reali%ado mientras el m-dulo de SSP esta+a en estado de espera ;sistema de 1ultimaster<$ E Q no Da ocurrido nin'una condici-n de interrupci-n del m-dulo SSP +it 4B CCP1IFB la' de interrupci-n de CCPI M1.1 Ca2!9ra 1Q 5curri- una captura de T1R1 ;de+e ponerse a cero por so7t9are< EQ No ocurri- nin'una captura de T1R1 M1.1 C102ara %-+ 1Q Se Da reali%ado una comparaci-n de T1R1 Con el re'istro empare,ado 6de+e ponerse a cero por So7t9are< EQ No se Da reali%ado comparaci-n M1.1 P<M Este modo no se utili%a +it 1B TMR2IFB la' de interrupci-n de T1R4 empare,ado con PR4 1Q TMR2 empare,ado con PR2 ocurri- ;de+e ponerse a cero por so7t9are< EQ No Da ocurrido el empare,amiento de T1R4 con PR4 +it EB TMR1IFB la' de des+ordamiento de T1RI 1 Qel re'istro se des+ordo ;de+e ponerse a cero por so7t9are< E Q el re'istreR de T1RI no se des+ordo Nota 1$: PSPIF est? reservado para los dispositivos de 4! pinesO se mantiene siempre a cero$

RE'ISTRO PIE2 5D%r" %-+ 8D;7 El re'istro de PIE4 contiene los +it individuales que Da+ilita las interrupciones del peri7Mrico CCP4.$ la interrupci-n por colisi-n del SSP y la ininterrupci-n de escritura en la EEPR51$ =:E R6@:E =:E R6@:E R6@:E =:E =:E R6@:E ??? E ??? EEIE 3CLIE ?? ?? CCP2IE 2it " 2it E +it "B N1 %02/"0"+!a.1B se lee como SET +it 6 R"$"r>a.1. 1antiene este +its a cero +it )B N1 %02/"0"+!a.1B se lee como SEU +it *B EEIEB /a+ilita la interrupci-n por escritura en la EEPR51 de datos 1Q /a+ilita la interrupci-n por escritura de la EEPR51 de datos E Q3esDa+ilita la interrupci-n por escritura en la EEPR51 de datos +it (B 3CLIEB /a+ilita la interrupci-n por colisi-n en el +us SSP cuando dos o m?s maestros tratan de trans7erir al mismo tiempo$ 1 Q /a+ilita la interrupci-n por colisi-n de +us SSP E Q 3esDa+ilita la interrupci-n por colisi-n en el +us SSP$ +it 4:1 N1 %02/"0"+!a.1$. se leen como SEU +it EB CCP2IEB /a+ilita la interrupci-n del modulo CCP4 1 Q Da+ilita la interrupci-n de CCP4 E Q inDa+ilita la interrupci-n de CCP4 RE'ISTRO PIR2 5D%r" %-+ 0D;7 El re'istro de PIR4 contiene los 7la's que indican la interrupci-n del CCP2. de la colisi-n del +us SSP y la interrupci-n de la escritura en la EEPROM P P P P P P P P =:E R6@:E =:E R6@:E R6@:E =:E =:E R6@:8 ??? 517 ??? EEIF 3CLIF ??? ??? CCP2IF 2it " 2it E +it "B +it 6B +it )B +it *B N1 %02/"0"+!a.1B se lee como SEU R"$"r>a.1B 1antiene este +it siempre a cero N1 %02/"0"+!a.1B se lee como SEU EEIFB la' que indica si se Da producido escritura en al EEPR51 1 Q Se Da completado la escritura en la EEPR51 ;Se pone a cero por so7t9are< E Q No se Da 7inali%ado la escritura o no se Da comen%ado +it (B 3CLIFB la' que indica la colisi-n en el +us 1 Q Se Da producido una colisi-n en el +us SSP. cuando se con7i'ura en el modo I4C 1aster$ E Q No se Da producido colisi-n en el +us +it 4:1BN1 %02/"0"+!a.1$B se leen como SEU +it EB CCP21FB la' de ininterrupci-n de CCP4 M1.1 Ca2!9ra 1 Q /a ocurrido una captura del re'istro T1R1 ;de+e ponerse a cero por so7t9are< EQ No se Da producido captura M1.1 C102ara %-+ 1 Q Se Da producido una comparaci-n de T1R1 con su pare,a ;de+e ponerse a cero por so7t9are<$ E Q No se Da producido comparaci-n M1.1 P<M No se utili%a

RE'ISTRO PCON 5D%r" %-+ 8E;7 El re'istro PC5N ;Power Control< Control de Alimentaci-n. contiene los flags que permiten di7erenciar entre un Power-on Reset ;P5P<. un Brown-out Reset ;25R<. un Reset por Watchdog ;@3T< y un Reset e8terno por 1CLR$ =:E =:E =:E =:E =:E =:E R6@:E R6@:E ??? E ??? ::: ??? ??? 8POR 83OR 2it " 2it E +it ":4BN1 %02/"0"+!a.1B se lee como SEU +it 1B 8PORB +it de estado Po9er:on Reset 1 Q No se Da producido un Po9er:on Reset EQ Se Da producido un Po9er:on Reset ;de+e reesta+lecerse por so7t9are< +it EB 83ORB +it de estado de 2or9n:out Reset 1 Q No se Da producido nin'Nn 2ro9n:out Reset EQ Se Da producido un 2ro9n:out Reset ;de+e reesta+lecerse por so7t9are< PCL @ PCLATA El contador del pro'rama ;PC< est? 7ormado por 1( +it que sirven para direccionar la memoria de c-di'o. estos +its se encuentran en dos re'istros especH7icos$ El +yte +a,o viene del re'istro de PCL que puede ser leHdo y escrito$ Los +its superiores ;PCC14B!P<$ Est?n alo,ados en el re'istro PC/ . so+re el que no se puede leer ni escri+ir. pero se puede acceder a Ml indirectamente a travMs del re'istro PCLAT/$ Las instrucciones de salto CALL y >5T5 s-lo proporcionan 11 +its de la direcci-n a saltar$ Esto limita el salto dentro de cada +anco de 40$ Cuando se desea salir del +anco actual Day que pro'ramar correctamente los +its PCLAT/ C*B(P que seleccionan el +anco$ Es la+or del pro'ramador modi7icar el valor de dicDos +its en las instrucciones CALL y >5T5$

i'ura ($: Estructura del Contador de Pro'rama EL STACB La 7amilia de los PIC 16 !"# dispone de una pila de ! niveles de pro7undidad para un tamaVo de PC de 1( +its$ Esta pila es transparente al pro'ramador. es decir. 7unciona autom?ticamente y no dispone de instrucciones para 'uardar o sacar de ella in7ormaci-n$ Con la Instrucci-n CALL y con las interrupciones el valor de PC se salva en el nivel superior$ Con las instrucciones RET=RN. RETL@ y RET IE el valor contenido en el valor superior de la pila se car'a en el PC$ La pila 7unciona como un +u77er circular$ Esto si'ni7ica que despuMs de que se Dan 'uardado ! valores en ella. el noveno +orra el valor que se 'uard- en primer lu'ar$ El

dMcimo +orra el que se 'uardo en se'undo lu'ar. etc$ Pa*%+a %-+ ." /a M"01r%a ." Pr1*ra0a Los dispositivos de la 7amilia PIC 16 !"# son capaces de direccionar un +loque de Dasta !0 de memoria continua$ Las instrucciones CALL y >5T5 proporcionan solo 11 +its de la direcci-n de memoria. lo que permite un salto de +i7urcaci-n dentro de una p?'ina de 40 de la memoria de pro'rama$ Al Dacer un CALL o una instrucci-n >5T5. dos 4 +it superiores de la direcci-n son proporcionados por el PCLAT/ C*B(P$ Al Dacer un CALL o un >5T5. el usuario de+e ase'urarse de que la p?'ina se Dan seleccionados con los +it correspondientes a la p?'ina que se desea llamar$ /ay que tener precauci-n en los retornos de su+rutinas y retornos de ininterrupci-n para no salirse con el valor almacenado en la PILA$ Por consi'uiente. manipulaci-n del PCLAT/ C*B(P no se requieren los +its para las instrucciones del retorno$ El e,emplo 4:1 muestras la llamada a una su+rutina en p?'ina 1 de la memoria del pro'rama$ Este e,emplo asume que el PCLAT/ se salva y se restaura por el pro'rama de atenci-n a la interrupci-n ;si se usan las interrupciones<$ EC"02/1 261 5R> E8)EE +c7 PCLAT/.* +s7 PCLAT/.( OSelecciona la pa'ina 1 ;!EED: D< call S=2 1:P 1 OLlamada a su+rutina en la P?'ina 1 ;!EED: D< 5R> S=21WPl return E8IEE Op?'ina 1 ;!EED: D<

OLlamada a su+rutina Op?'ina 1 ;!EED: D< ORetorno de su+rutina en pa'ina E ;EEED:"

D<

D%r" %1+a0%"+!1 %+.%r" !1, /1$ r"*%$!r1$ INDF @ FSR El re'istro IN3 no es un re'istro 7Hsico. que ocupa la direcci-n E en todos los +ancos. este re'istro se utili%a cuando queremos reali%ar un direccionamiento indirecto$ Cuando se Dace re7erencia al re'istro. se accede realmente a la direcci-n de un +anco de re'istro especi7icada con los " +its de menor peso del re'istro SR$ El +it de m?s peso del SR ,unto al +it IRP de re'istro de STAT=S se encar'a de seleccionar el +anco a acceder. mientras que los " +it de menos peso apuntan a la posici-n$

i'ura *$: orma de seleccionar el +anco y la direcci-n de la RA1 en los direccionamientos directo e indirecto$ LECT4RA Y ESCRIT4RA DE LAS MEMORIAS EEPROM Y FLASA En esta 7amilia de microcontroladores tanto la memoria EEPR51 de datos como la memoria de pro'rama LAS/ puede ser modi7icada sin necesidad de utili%ar un pro'ramador e8terior y a la tensi-n nominal de A33$ Es decir. un pro'rama din?micamente puede 'enerar in7ormaci-n que se puede 'ra+ar en la memoria LAS/$ Por lo tanto podemos utili%ar esta propiedad para queB La propia aplicaci-n se puede pro'ramar se'Nn las condiciones e8ternas Es posi+le ampliar el ?rea de la memoria de datos no vol?til EEPR51 con posiciones li+res de la memoria LAS/$ Se dispone de seis re'istros de S R para leer y escri+ir so+re la memoria no vol?til. estos re'istros sonB EEC5N1 . EEC5N4. EE3ATA. EE3AT/. EEA:3R y EEA3R/$ Para direccionar los 14! posiciones de memoria EEPR51 de ! +its del PIC16 !"( y 16 !"* o las 4)6 posiciones del PIC16 S"6 y 16 S"" +asta con ! +it. por ello para escri+ir o leer en la memoria EEPR51 solo Dacen 7altan el re'istro EEA3R para direccionar la posici-n y el re'istro EE3ATA para colocar el dato leHdo o escrito$ Sin em+ar'o para poder escri+ir o leer datos en la memoria LAS/ que puede tener Dasta !0 pala+ras de 1* +its Dacen 7alta dos re'istros para direccionar la posici-n de memoria. por ello se utili%a el re'istro EEA3R concatenado con el re'istro EEA3R/ que contiene la parte alta de la pala+ra de direccionamiento de memoria$ 3e 7orma similar se utili%an los re'istros EE3ATA concatenado con el re'istro EEA3R/ que contiene los 6 +it de mayor peso de las pala+ras de 1* +its$ Adem?s para controlar el proceso de lectura y escritura de la memoria EEPR51 y LAS/ se dispone de dos re'istrosB el EEC5N1 y el EEC5N4$ RE'ISTROS EECON1 5D%r" %-+ 18C;7 @ EECON2 Se'uidamente se descri+en los +it de control de re'istro EEC5N1 P R6@:8 =:E =:E =:E R6@:8 R6@:E R6S:E R6S:E EEP'D ??? ??? ??? <RERR <REN <R RD 2it " 2it E +it "B EEP'DB Pro'rama 6 +it de selecci-n de datos EEPR51 1Q Acceso a la memoria de pro'rama AS/ EQ Acceso a la memoria de datos EEPR51 ;No se puede cam+iar mientras la lectura o escritura est? en proceso< +it 6B*BN1 %02/"0"+!a.1$B Se leen como SEU +it (B <RERRB la' de error de escritura en la EEPR51 1 Q El proceso de lectura se Da producido prematuramente ;se Da producido un Reset por 1CLR o un @3T durante el proceso< E Q Se Da producido el proceso de escritura con M8ito +it 4B <RENB +it de Da+ilitaci-n de escritura 1 Q Permite iniciali%ar el ciclo de escritura E Q InDi+e la escritura +it 1B <RB +it de inicio de escritura 1 Q Cuando se le pone a 1 comien%a el ciclo de escritura de la memoria no vol?til$ ;El +it se pone de nuevo a cero por Dard9are cuando la escritura se completa<$ E Q Toma este valor cuando completa el ciclo de escritura de la memoria no vol?til$ +it EB RDB +it de inicio de lectura 1 Q Cuando se le pone a 1 se inicia un ciclo de lectura$ El +it RD se pone a cero por Dard9are$ E Q no Da comen%ado el ciclo de lectura de la memoria no vol?til$

El re'istro EEC5N4. no est? implementado 7Hsicamente y s-lo se utili%a para la operaci-n de lectura. de i'ual 7orma que se Dace con el PIC 16 !*. es decir. antes de iniciar la escritura de un dato en la memoria. se de+e escri+ir en el re'istro EEC5N4 primero el dato ))D y posteriormente el dato AAD$ Se'uidamente se muestran una serie de su+rutinas para la escritura y lectura de la memoria no vol?til$ S=2R=TINA PARA LA ESCRIT=RA 3E LA 1E15RIA EEPR51 3E 3AT5S ESCRI2EWEEPR51 +s7 STAT=S. RPl OSelecci-n del +anco 4 de memoria +c7 STAT=S. RPE movl9 3ATAWEEWA33R O3irecci-n de la EEPR51 a la que mov97 EEA3R Ose quiere acceder movl9 3ATAWEEW3ATA O3ato que se quiere escri+ir mov97 EE3ATA +s7 STAT=S. RPE OSelecci-n del +anco ( +c7 EEC5N1. EEP>3 OSelecci-n de acceso a la EEPR51 +s7 EEC5N1. @REN O/a+ilita la escritura en la EEPR51 +c7 INTC5N. >IE OSe ProDH+en las interrupciones movl9 ))D mov97 EEC5N4 OEscri+e ))D en EEC5N4 movl9 AADO mov97 EEC5N4 OEscri+e AAD en EEC5N4 +s7 EEC5N1. @R OSe da la orden de escritura +s7 INTC5N. >IE OSe Da+ilitan las interrupciones sleep OSe espera Dasta que se produ%ca la interrupci-nO O por 7in de escritura +c7 EEC5N1. @REN OProDi+ir la escritura de nuevos datos returm S=2R=TINA PARA LA LECT=RA 3E LA 1E15RIA EEPR51 3E 3AT5S LEEWEEPR51 +s7 STAT=S.RP1 +c7 STAT=S.RPE OSelecci-n del +anco 4 de memoria mov7 A33RWL.@ O3irecci-n a leer de EEPR51 mov97 EEA3R +s7 STAT=S.RPE OSelecci-n del +anco ( de memoria +c7 EEC5N1.EEP>3 OSe selecciona el acceso a EEPR51 +s7 EEC5N1.R3 OSe da la orden de e7ectuar +c7 STAT=S.RPE OSelecciona el +anco 4 de memoria mov7 EE3ATAWL OSe reco'e el dato leHdo y se de,a en 3ATAWL returm S=2R=TINA PARA LA ESCRIT=RA 3E LA 1E15RIA LAS/ 3E CL3I>5 ESCRI2EW LAS/ +s7 STAT=S.RP1 +c7 STAT=S.RPE . Selecci-n de 2anco 4 de memoria movl9 A33R/ OSe escri+e en EEA3R/ la parte alta de la mov97 EEA3R/ Odirecci-n a escri+ir movl9 A33RL OSe escri+e en EEA3R la parte +a,a

de la mov97 movl9 mov97 movl9 mov97 +s7 +s7 +s7 LAS/ +c7 movl9 el re'istro mov97 7a+ricante movl9 mov97 +s7 nop nop +s7 +c7 returm EEA3R 3ATAW/ EE3AT/ 3ATAWL EE3ATA STAT=S.RPE EEC5N1. EEP>3 EEC5N1. @REN INTC5N. >IE ))D EEC5N4 AAD EEC5N4 EEC5N1. @R INTC5N. >IE EEC5N1. @REN O direcci-n a escri+ir OSe mete en EEIB<AT/ la parte alta Odel dato a escri+ir OSe mete en EE3AL la parte +a,a Odel dato a escri+ir OSelecci-n del +anco ( de memoria OSelecci-n de acceso a la memoria LAS/ OSe Da+ilita la escritura en la memoria OSe proDH+en las interrupciones OSe escri+en los datos ))D y AAD en OEEC5N4 tal y como recomienda el

OSe da la orden de escritura OEl microcontrolador i'nora estas dos Oinstrucciones OSe Da+ilitan las interrupciones OSe proDH+e la escritura de nuevos datos

S43R4TINA PARA LA LECT4RA DE LA MEMORIA FLASA DE C)DI'O LEEW LAS/ +s7 STAT=S.RP1 +c7 STAT=S.RPE OSelecci-n del +anco 4 de memoria movl9 A33R/ OSe mete en EEA3R/ la parte alta mov97 EEA3R/ Ode la direcci-n a leer movl9 A33RL OSe mete en EEA3RL la parte +a,a mov97 EEA3R Ode la direcci-n a leer +s7 STAT=S.RPE OSelecci-n del +anco ( de memoria +s7 EEC5N1. EEP>3 OSelecciona el acceso a memoria LAS/ +s7 EEC5N1. R3 O5rden de lectura de la memoria LAS/ OTarda tres ciclos en tener el dato. por lo que nop Ocualquier instrucci-n es i'norada nop +c7 STAT=S.RP5 OSelecci-n del +anco 4 de memoria mov7 EE3ATA.@ OSe reco'e la parte +a,a del dato leHdo mov7 3AT5 L mov7 EE3AT/. @ OSe reco'e la parte alta del dato leHdo mov7 3AT5W/ returm La operaci-n de escritura de esta memoria dura apro8imadamente 4 ms$ El 7a+ricante recomienda la veri7icaci-n de los datos escritos en las memorias EEPR51 y LAS/ para compro+ar que su 'ra+aci-n se Da reali%ado correctamente$ Para evitar escrituras indesea+les en la EEPR51 motivadas por espNreos en la iniciali%aci-n del microcontrolador. se controla el +it <REN del re'istro EECON1. proDi+iendo cualquier operaci-n de escritura mientras duran los "4 ms que tempori%a el Timer Po9er:up$ En el caso de la memoria LAS/ se de+e poner a E el +it <RT de la Pala+ra de Con7i'uraci-n. que solo puede escri+irse desde un 'ra+ador e8terno$

3ependiendo del valor del +it <RT y de los +it de Protecci-n de c-di'o CP1 y CPE. de la Pala+ra de Con7i'uraci-n. se consi'uen diversas alternativas de protecci-n contra escritura de la memoria LAS/$ C5N I>=RACILN P5SICI5NES LECT=RA ESCRIT=RA LECT=RA ESCRIT=RA 3E 2ITS 3E LAS/ INTERNA NTERNA ICSP ICSP CP1 CPE @RT E E # Toda memoria Pro'rama Xreas Prote'idas Xrea Prote'ida Xreas Prote'idas Xreas Prote'idas Xreas Prote'idas Toda 1emoria Pro'rama la SI de no SI N5 N5 N5 N5 N5 SI N5 N5 N5 SI N5 N5 SI N5 SI N5 SI N5 SI N5 SI SI N5 N5 N5 N5 N5 N5 N5 N5

E E E E 1 1 1 1 1

1 1 1 1 E E E E 1

E E 1 1 E E 1 1 E

Xrea Prote'ida SI no SI

Xrea Prote'ida SI no SI

Xrea Prote'ida SI no SI SI la SI de

RE'ISTROS ASOCIADOS CON LA MEMORIA DE DATOS EEPROM=PRO'RAMA FLASA 3irecci- Nom+re 2it " 2it 6 2it ) 2it * 2it ( 2it 4 2it 1 2it E Aalor en Aalor n P5R.25 en el R resto de Reset E2D. INTCO 'IE PEIE T0IE INTE R3IE T0IF INTF R3IF EEEE EEEE !2D. N EEE8 EEEu 1E2D.1! 2D 1E3 D EEADR Redistro de direccionamiento de EEPR51 8888 uuuu 8888 uuuu 1E D EEADR :: :: :: Parte alta de la direccionamiento de 8888 uuuu A EEPR51 8888 uuuu 1E D EEADR :: :: :: Parte alta de la direccionamiento de 8888 uuuu A EEPR51 8888 uuuu 1E D EEADR :: :: :: Parte alta de la direccionamiento de 8888 uuuu A EEPR51 8888 uuuu 1E D EEADR :: :: :: Parte alta de la direccionamiento de 8888 uuuu A EEPR51 8888 uuuu 1EC D EEDAT Re'istro de dato de la EEPR51 8888 uuuu A 8888 uuuu 1EE D EEDAT :: :: 8888 uuuu

EEP> ::: ::: ::: @RER @RE @R R3 3 R N 1!3 D Re'istro4 de control EEPR51 ;re'istro 7Hsico no implementado< !3 D :: ;1< :: EEIE 2CLIE ::: ::: CCP4I :r:E EYE :r:EY E E E3 D PIR2 :: ;1< :: EEI 2CLI ::: ::: CCP41 :r:E EYE :r:E E::E LeyendaB 8 Q Indeterminado. u Q Permanece Invaria+le. r Q reservadoO : Q No implementado se lee como EO No se usan las cMlulas som+readas durante el acceso a LAS/6EEPR51$ Nota 1$: Xrea de memoria reservadaO estos +its se mantienen siempre a cero MOD4LO TIMER0 El m-dulo TitnerE es tempori%ador6contador con las si'uientes caracterHsticasB El tempori%ador6contador dispone de ! +its Puede escri+irse y leerse Preescaler pro'rama+le por So7t9are de ! +its Puede tra+a,ar con el relo, interno o con una seVal de relo, e8terna 3ispone de una interrupci-n por des+ordamiento al pasar de D a EED Selecci-n de 7lanco ascendente o descendente para el 7laco del relo, e8terno En la i'ura 1( se muestra un dia'rama de +loques del TirnerE y el preescaler que comparte con el @3T$ Puede encontrarse in7ormaci-n adicional so+re el m-dulo TimerE en el manual de re7erencia de los microcontroladores de la escala media ;3S((E4(<$

1!C D

A EECON 1 EECON 2 PIE2

8888 uuuu 8::: 8888 8::: uEEE

Notas$:B 1$ El preescaler es compartido con el @3T ;En la 7i'ura 1* se puede ver un dia'rama de +loques detallado 4$ T5CS. T5SE. PSA. PS4BPSE ;5PTI5NWRE>C)BEP< F%*9ra D6? D%a*ra0a ." E/1F9"$ ."/ T%0"r 0 El modo tempori%ador se selecciona poniendo a cero el +it T0CS ; re'istro OPTION:RE' C)P<$ En el modo tempori%ador. el m-dulo TimerE se incremento en cada cielo de instrucci-n ;sin el preescaler<$ Si el re'istro T1RE se escri+e. el incremento se inDi+e durante los si'uientes dos ciclos de instrucci-n$ EL usuario puede tra+a,ar teniendo en cuenta esto y a,ustando el valor a car'ar en el TMR0$ El modo contador se selecciona poniendo a uno el +it T0CS ;re'istro OPTION:RE' C)P<$ El modo contador. TimerE se incremento en cada 7laco de su+ida o de +a,ada de la seVal que le lle'a por RA*6T5C01$ El 7lanco de incremento se determina por el +it T0SE ;re'istro OPTION:RE' C*P<$ PoniMndose a cero T0SE se selecciona el 7lanco ascendente$ Las restricciones de la seVal de relo, e8terna se descri+en en la secci-n )$4$ El preescaler se comparte e8clusivamente entre el TimerE y el @3T$ El preescaler no es de lectura6escritura$ En la secci-n )$( se detalla el 7uncionamiento del preescaler$

F%*9ra 66? D%a*ra0a ." E/1F9"$ ."/ TMR0 I+!"rr92 %-+ ."/ T%0"r06 La interrupci-n de T1RE se produce cuando el re'istro TMR0 se des+orda al pasar de D a EED$ Este des+ordamiento pone a uno el +it T0IF ;INTCONC4P<$ La ininterrupci-n puede enmascararse poniendo a cero el +it T0IE ;INTCON C)P<$ EL +it T0IF de+e ponerse a cero por so7t9are al 7inali%ar la rutina de atenci-n a la interrupci-n del des+ordamiento de TMRO$ La ininterrupci-n de T1R5 no saca al microcontrolador del estado de SLEEP. de+ido a que el tempori%ador est? desactivado durante el modo SLEEP 4!%/%,a %-+ ."/ T%0"r0 1+ 9+ R"/1C EG!"r+1 Cuando no se utili%a el preescaler. la entrada de relo, e8terna es i'ual a la salida del preescaler$ Las sincroni%aci-n de T5C0I con los relo,es de 7ase interior se acopla. a la salida del preescaler en los ciclos Z4 y Z* de los relo,es de 7ase internos$ Por consi'uiente. es necesario que T5C0I est? a nivel alto por al menos durante 4Tosc ;y un pequeVo retardo de 4Ens< y a nivel +a,o por lo menos 4Tosc ;y un retardo RC de 4Ens<$Aer las caracterHsticas elMctricas del dispositivo deseado$ Pr""$ a/"r /ay s-lo un preescaler disponi+le que es est? compartido y puede asi'narse indistintamente al modul- de Timerl y el al @3T$ La asi'naci-n del preescaler al TimerE Dace que no Daya nin'Nn preescaler para el @3T. y viceversa$ Este preescaler no se puede leer ni escri+ir ;ver la i'ura 1*<$ El +it PSA y PS2BPS0 ;OPTION:RE' C(BEP< determinan la asi'naci-n del preescaler y el ran'o del preescaler$ Cuando se le asi'na al m-dulo del TirnerE . todas las instrucciones. que escri+en en el re'istro TMR0 ;por e,emplo CLR T1RE. 15A@ T1RE. 2S T1RE.8$$$ etc$< ponen a cero el preescaler$ Cuando se le asi'na al @3T. una instrucci-n CLR@3T limpia el preescaler ,unto con el tempori%ador del @3T$ EL preescaler no se puede leer ni escri+ir$ N1!a$: Escri+ir en T1RE. cuando el preescaler es asi'nado a TimerE. limpia la cuenta del preescaler. pero no cam+ia el contenido del preescaler$ TA2LA 3E RE>ISTR5S AS5CIA35S AL TI1ERE 3irecci-n Nom+re 2it " 2it 6 2it ) 2it * 2it ( 2it 4 2it 1 2it E Aalor en P5R.25R

E+D. !2D INTCON >IE PEIE TEIE INTE R2IE T5I 1E2D.1!2D !1D.1!1D OPTION:RE' R2P= INTE3> TECS TESE PSA PS4 !)D TRISA ::: :::

INT PS1

R2I PSE

EEEE EEE8 1111 1111

Re'istro de direccionamiento de datos del ::11 1111 P5RTA LeyendaB 8 Q desconocido. u Q inalteradoO : Q no implementado se lee como [ET$ Las celdas som+readas no son usadas por el TI1ERE EL M)D4LO DE TIMER1 El m-dulo de TI1ER1 es un tempori%ador6contador de 16 +its. 7ormado por dos re'istros de ! +its cada uno TMR1A y TMR1L. que son de lectura y escritura y que son los que 'uardan el valor de la cuenta en cada momento$ El valor de los re'istros TMR1A y TMR1L se incrementan desde EEEE/ Dasta /. en cuyo instante se vuelve a poner a EEEED y se activa el 7la' TMRIF ;PIR1CEP< La ininterrupci-n de TMR1 puede ser Da+ilitada6desDa+ilitada se'Nn este a uno6cero el +it TMR1IE ;PIE1 CEP<$ EL TI1ERl tiene los si'uientes modos de tra+a,oB 1$ Como Tempori%ador 4$ Como contador SHncrono ($ Como contador AsHncrono El modo de tra+a,o viene determinado la 7uente de los impulsos de relo,. es decir. la seVal de relo, puede ser e8terna o interna. se selecciona con el +it TMRLCS del re'istro T/CONClP. cuando este +it est? a nivel +a,o se selecciona el relo, el interno del micro:controlador ; osc6*< y cuando est? a uno se selecciona el modo contador y cuenta los impulsos que le lle'an a travMs del pin RCE6TlC0l$ Adem?s como se ver mas adelante el TI1ER1 tiene la posi+ilidad de reiniciali%arse. a partir del m-dulo CCP$

RE'ISTRO T1CON: R"*%$!r1 ." 1+!r1/ ."/ TIMER1 5.%r" %-+ 10;7 =:E =:E R6@:E R6@:E R6@:E R6@:E R6@:E R6@:E ??? ??? T1CBPS1 T1CBPS0 T1OSCEN T1SYNC TMR1CS TMR1ON 2it " 2it E +it ":6B N1 %02/"0"+!a.1$B Se lee como SEU +it ):*B T/CBPS1:T1CBPS0B +it de selecci-n del preescaler de la seVal de relo, del TI1E1 11 Q valor del preescaler 1B! 1E Q valor del preescaler 1B* E1 Q valor del preescaler 1B4 EE Q valor del preescaler 1B 1 +it ( B T1OSCENB +it de Da+ilitaci-n del oscilador del TI1ER1$ Cuando se emplea un oscilador e8terno. Day que poner este +it a 1$ El T1R1 puede tra+a,ar a una 7recuencia totalmente independiente de la del sistema$ 1 Q /a+ilita el oscilador Nota$: El oscilador y la resistencia de E Q 3esDa+ilita el oscilador desconectan para reducir el consumo +it 4B \TlS]NCB +it de control de sincroni%aci-n de la seVal de entrada$ Con T1R1CS Q 1 1Q No sincroni%a la entrada de relo, e8terna E Q Sincroni%a la entrada de relo, e8terna Con T1R1CS Q E En esta condici-n se i'nora$ El TI1ER1 utili%a el relo, interno cuando T1RICSQE +it 1 TMR1CSB +it de selecci-n de la 7uente de relo, del TI1ER1 1 Q Relo, e8terno por el pin RCE6T15S56T1C01 ;7lanco ascendente< E Q Relo, interno ; 5SC6*<

+it EB TMR1ONB TI1ER1$ activo$ /ace entrar o no en 7uncionamiento el TI1ER1$ 1 Q /a+ilita el TI1ER1 E Q 3esDa+ilita el TI1ER1 M1.1 ." H9+ %1+a0%"+!1 ."/ T%0"r1 101 T"021r%,a.1r Este modo se selecciona poniendo a cero el +it TMR1CS ;T1CON C1P$ En este modo la seVal de relo, es el relo, interno del microcontrolador 5SC6*$ En este modo de tra+a,o el +it T1SYNC ;T1CON C4P< no tiene nin'Nn e7ecto ya que el relo, interno est? siempre sincroni%ado$ M1.1 ." H9+ %1+a0%"+!1 ."/ T%0"1 101 C1+!a.1r En este modo puede tra+a,ar como contador sHncrono o asHncrono $ Cuando el TI1ER1 se est? incrementando se'Nn le lle'an los impulsos e8ternos. los incrementos ocurren en los 7lancos de su+ida$ 3espuMs de que el TI1ER1 se Da con7i'urado como contador. de+e producirse un 7lanco de +a,ada antes de empe%ar a contar$

N1!a6? La$ H/" ;a$ %+.% a+ /1$ %+ r"0"+!1$ ."/ 1+!a.1r

F%*9ra 76? D%a*ra0a ." E/1F9"$ ." TMR1 M1.1 ." H9+ %1+a0%"+!1 ."/ T%0"r1 101 C1+!a.1r S#+ r1+1 Para seleccionar este modo se pone a uno el +it TMR1CS ;T1CON C1P<$ En este modo el contador se incrementa en cada 7lanco ascendente de la seVal de relo, que se introduce por el pin RCE6T15S56TIC01 cuando el +it T1OSCEN est? a uno. y por el pin RC16Tl5SI6CCP4. cuando el +it T1OSCEN est? a cero$ Si T1SYNC se pone a cero. entonces la entrada de relo, e8terna se sincroni%a con los relo,es de 7ase interiores$ La sincroni%aci-n se Dace despuMs de la 7ase del preescaler$ En el preescaler la 7ase de la seVal de relo, es por lo tanto asHncrona$ En este modo de tra+a,o. durante el modo SLEEP el TI1ER1 no se incrementa aNn cuando la seVal de relo, e8terna estMT presente$ El preescaler sin em+ar'o continua increment?ndose$ M1.1 ." H9+ %1+a0%"+!1 ."/ TIMER1 101 C1+!a.1r A$#+ r1+1 Cuando el +it de control T1S]NC ;T1C5N C4P< se poner a uno. la seVal de relo, e8terna no se sincroni%a$ El contador si'ue reali%ando la cuenta de 7orma asHncrona respecto a la 7ase de la seVal de relo, interna$ El contador continua la cuenta incluso en el modo SLEEP y puede

'enerar una interrupci-n por des+ordamiento que despierta al procesador$ /ay que tener especial cuidado con el so7t9are al leer o escri+ir el contador ;Secci-n 6$)$1<$ Cuando se tra+a,a en el modo contador asHncrono. el TI1ER1 no puede usare como +ase de tiempos para el m-dulo CCP ;Captura y comparaci-n:P@1< L" !9ra @ "$ r%!9ra "+ "/ TIMER1 9a+.1 $" !raEaCa "+ "/ 01.1 1+!a.1r a$#+ r1+1 Se pueden leer los contadores TMR1A y TMR1L mientras la seVal e8terna del contador se est? reci+iendo ;teniendo cuidado con el Dard9are<$ Sin em+ar'o. el usuario de+e tener en cuenta que el contador es de 16 +its y se pueden tener ciertos pro+lemas al leer los dos re'istros de ocDo +its. ya que el contador puede des+ordarse entre las lecturas$ Para escri+ir en Ml. se recomienda que el usuario simplemente pare el contador y escri+a los valores deseados$ Cuando se escri+e el re'istro del contador puede Da+er con7licto mientras este se est? incrementando$ Esto puede producir un valor imprevisi+le en el contador$ Lee el re'istro de 16 +it requiere al'Nn cuidado$ Los e,emplos 14:4 y 14:( de la 7amilia de microcontroladores de la escala media. manual de re7erencias ;3S((E4(<. muestra como leer y escri+ir el TI1ER1. cuando est? corriendo en el modo asHncrono$ O$ %/a.1r ."/ TIMER1 Se puede conectar un oscilador a cristal entre los pines T15SI ;entrada< y T15S5 ;salida del ampli7icador<$ Se de+e Da+ilitar poniendo a uno el +it de control TL5SCEN ;TIC5N C(P<$ El oscilador de +a,o consumo puede tra+a,ar Dasta 4EE G/%$ En estas condiciones el oscilador si'ue 7uncionando aunque se 7uerce el modo SLEEP$ Est? pensado para tra+a,ar con un cristal de (4 G/%$ La Ta+la 6 muestra el valor de los condensadores para el TI1ER1$ El oscilador TI1ER1 es idMntico al oscilador LP$ El usuario de+e proporcionar un tiempo de retardo por so7t9are para ase'urar la salida apropiada del oscilador$ T%21 ." O$ %/a.1r LP Fr" 9"+ %a C1 C2 (4 G/% ((p ((p 1EEG/% 1) p 1) p 4EE 1) p 1) p Estos valores son para los si'uientes cristales de re7erencia (4$"6! EpsonC:EE1R41$"6!0:A 4E PP1 1EE G/% Epson C:4 1EE$EEE 0C:p1 4E PP1 4EE G/% ST3 #TL 4EE$EEE G/% 4E PP1 N1!a6? 1$ Capacidades mayores aumentan la esta+ilidad del oscilador. pero tam+iMn aumentan el start:up$ 4$ Cada cirstal6resonador tiene sus propias caracterHsticas. el usuario de+e consultar los valores apropiados de los componentes e8ternos al cristal$ TaE/a &6? S"/" %-+ ." /1$ 1+."+$a.1r"$ 2ara "/ 1$ %/a.1r ."/ TIMER1 RESTA3LECIMIENTO DEL TIMER1 4TILI(ADO LA SALIDA TRI''ER DEL CCP Si el m-dulo CCPI o CCP2 se con7i'uran en modo comparaci-n para 'enerar un Sdisparo por evento especialU ;CCP1M&BCCP1MO Q 1E11<. esta seVal reesta+lecer? el TIMIER1$ Nota$: El evento especial que activa los m-dulos CCP1 y CCP4 no activar? el 7la' TMR1IF ;PIR1CEP<$ El TI1ER1 de+e con7i'urarse como tempori%ador o contador sHncrono R"$!aE/" %0%"+!1 TIMER1 F9" 9$a 9+ .%$2ara.1r ." CCP TIMER1 de+e con7i'urarse para tempori%ador o contador sHncrono para aprovecDar esta caracterHstica$ Si el TIMER1 est? tra+a,ando en modo contador asHncrono. el reset no puede ser activado$ En el caso de escri+ir so+re el TIMER1 en el momento del disparo del evento especial de CCP1 o CCP2. se tomar? el valor anterior$ En el caso de escri+ir so+re TIMER1 si coincide con un disparo por evento especial de CCP1 o CCP2. se car'a el valor anterior$

En este modo de 7uncionamiento. el par de re'istros CCPRGABCCPRGL se reponen para volver a tener el periodo del TIMER1$ 06I R"$!aE/" %0%"+!1 ."/ 2ar ." r"*%$!r1 ."/ TIMER1 5TMR1R, TMR1L7 Los re'istros T1R1/ y T1R1L no se iniciali%an a EED despuMs de un Po9er:on Reset o por cualquier otro reset e8cepto por un disparo de evento especial en CCP1 y CCP2$ El re'istro T1CON se iniciali%a a EED despuMs de un Po9er:on Reset o 2ro9n:out Reset que de,a a 1:1 el preescaler$ En los dem?s reset. el re'istro no es alterado$ T%0"r1 Pr""$ a/"r El contador del preescaler se pone a cero al escri+ir en los re'istros TMR1A o TMR1L$ EL M)D4LO DE TIMER2 El TI1ER4 es un tempori%ador:contador ascendente de ! +its que ocupa la posici-n 11/ del +anco de re'istros especiales. con un preescaler y postscaler$ Se puede usar como +ase de tiempo para el m-dulo P<M, el m-dulo CCP ;1-dulo de Captura y Comparaci-n< y la Puerta Serie SHncrona ;SSP<$ El re'istro TMR2 se puede leer y escri+ir y se pone a cero despuMs de un Reset$

Nota 1$: Se puede seleccionar por so7t9are la salida del m-dulo T1R4 como seVal de relo, para la transmisi-n en +audios del m-dulo SSP F%*9ra 86? D%a*ra0a ." E/1F9"$ ."/ 0-.9/1 TIMER2 La seVal de relo, interna ; 5SC6*< antes de lle'ar al TMR2 pasa por un preescaler ;Predivisor< con ran'os de 1B1. 1B*. 1B16 que se selecciona a travMs de los +its T2CBPS1BT2CBPS0 ;T2CON C1BEP<$ O2"ra %1+"$ 1+ "/ TIMER2 El Titner4 tiene empare,ado el re'istro PR2 que ocupa la posici-n de I4/ del +anco de re'istros especiales. de manera que al incrementarse TMR2 y coincidir con el valor del re'istro PR2 se produce un impulso de salida por EJ. estos impulsos pueden ser divididos por un postescaler antes de activar el 7la' TMR2FI ;PIR1K1L<$ El re'istro PR2 es un re'istro de ! +its que puede ser escrito y leHdo. este re'istro toma el valor despuMs de un Reset$ El postscaler permite dividir la seVal por cualquier valor comprendido entre 1B1 Dasta 1B16. para controlar el postescaler se utili%an los +it TO4TPS&B TO4TPS0 ;T4C5N C6B(P<$ El Preescaler y el Postescaler se ponen a cero cuandoB J Se escri+e so+re el re'istro TMR2 J Se escri+e so+re el re'istro T2CON J Se produce un reset ;P5R. 1CLR resta+lecido. @3T reesta+lecido o 25R< TMR2 no se pone a cero cuando se escri+e en T2CON

RE'ISTRO T2CON: RE'ISTRO DE CONTROL DEL TIMER2 5.%r" %-+ 12;7 =: R6@:E R6@:E R6@:E R6@:E R6@:E R6@:E R6@:E E ??? TO4TPS& TO4TPS2 TO4TPS1 TO4TPS0 TMR2ON T2CBPS1 T2CBPS0 2it 2it E " +it ": N1 %02/"0"+!a.1B Se lee como E +it 6:(B TO4TPS&:TO4TPS0B +it de selecci-n del ran'o del divisor del Postescaler para el TIMER2 EEEE Q 3ivisor del postescaler 1B1 EEE1 Q 3ivisor del postescaler 1B4 EE1E Q 3ivisor del postescaler 1B( EE11 Q 3ivisor del postescaler 1B* E1EE Q 3ivisor del postescaler 1B) E1E1 Q 3ivisor del postescaler 1B6 E11E Q 3ivisor del postescaler 1B" E111 Q 3ivisor del postescaler 1B! 1EEE Q 3ivisor del postescaler 1BI 1EE1 Q 3ivisor del postescaler 1B1E 1E1E Q 3ivisor del postescaler 1B11 1E11 Q 3ivisor del postescaler 1B14 11EE Q 3ivisor del postescaler 1B1( 11E1 Q 3ivisor del postescaler 1B1* 111E Q 3ivisor del postescaler 1B1) 1111 Q 3ivisor del postescaler 1B16 +it 4B TMR2ONB +it de activaci-n del TI1ER4 1BQ Da+ilita el 7uncionamiento del TI1ER4 E Q InDi+e el 7uncionamiento del TI1ER4 +it 1:4B T2CBPS1:T2CBPS0 Selecci-n del ran'o de divisor del Preescaler del TI1ER4 EE Q 3ivisor del Preescaler 1B1 E1 Q 3ivisor del Preescaler 1B* I8 Q 3ivisor del Preescaler 1B16 Interrupciones del TI1ER4 El tempori%ador TMR2 tiene un 7la' de des+ordamiento el TMR2IF ;C1PPIR1<$ El TMR2 tiene asociado un Re'istro de Periodo PR4. que ocupa la posici-n I4D$ Cuando el valor de cuenta de TMR2 coincide con el valor car'ado en PR2 se 'enera un impulso en la salida EJ ;ver la i'ura 16 < y se pone a cero el TMR2$ Estos impulsos pueden ser divididos por el postdivisor antes de activar el 7la' T1R41 ;C1P PIR1<$ El tempori%ador puede producir una interrupci-n si se pone a 1 el +it T1R4IE ;C1P PIE1< Sa/%.a ."/ TMR2 La salida de TMR2 ;antes del postscaler< alimenta al 1-dulo de SSP que opcional mente puede usarse para 'enerar la seVal de relo, de despla%amiento$ MOD4LO CCP CAPT4RA = COMPARACI)N = P<M 5M1.9/a %-+ ." a+ ;9ra ." %029/$1$7 Los microcontroladores de la 7amilia 16 !"# disponen de dos m-dulos de Captura 6 Comparaci-n y P@1. cada modulo tiene un re'istro de 16 +its que pueden tra+a,ar comoB Re'istro de captura de 16 +it Re'istro de comparaci-n de 16 +its

1odulaci-n de ancDura de pulsos P@1 Los m-dulos CCP1 y CCP2 son idMnticos en su modo de 7uncionamiento. con la e8cepci-n del modo de disparo especial$ En las ta+las 1" y 1!se muestran los recursos e interacciones de los m-dulos$ En las secciones si'uientes se descri+e el 7uncionamiento del m-dulo CCP1$ CCP2 opera de i'ual modo salvo en lo ya dicDo$ M-.9/1 CCP1: El re'istro de Captura 6 Comparaci-n 6 P@1 ;CCPR1< de 16 +its esta 7ormado por dos re'istros de ! +itsB CCPR1L ;+yte. +a,o< que ocupa la direcci-n 1)D y el CCPR1A ;+yte alto< que ocupa la posici-n 16D$ El re'istro de control del CCP1 es el CCP1CON que ocupa la direcci-n 1"D$ El modo de disparo especial se 'enera por la i'ualdad en la comparaci-n de CCPR1 con TMR1 y reesta+lecer? el TIMER1 y el CCPR1, 7unciona como un re'istro de perHodo. capa% de provocar peri-dicamente interrupciones$ M-.9/1 CCP2: El re'istro de Captura 6 Comparaci-n 6 P@1 ;CCPR4< de 16 +its est? 7ormado por dos re'istros de ! +itsB CCPR2L ;+yte +a,o< que ocupa la direcci-n l2D y CCPR2A ;+yte alto< que ocupa la direcci-n 1CD$ El re'istro de control del CCP2 es el CCP2CON que se encuentra en la direcci-n l3D$ El modo de disparo especial se 'enera por i'ualdad en la comparaci-n con el TIMER1 lo que provoca que se reesta+le%ca el TIMER1 y comience una conversi-n A63. si el convertidor A63 est? Da+ilitado$ Con lo cual puede reali%ar la conversiones A63 de 7orma peri-dica sin en control del pro'rama de instrucciones$ M1.1 CCP R" 9r$1 ." T%0"r Captura Timer1 Comparaci-n Timer1 P@1 Timer4 M1.1 CCP M R" 9r$1 ." TIMER6 E+ /1$ 0-.9/1$ ." a2!9ra @ 102ara %-+ %+!"r>%"+"+ "/ TMR1, "+ P<M "/ TMR26 INTERACCI)N DE LOS DOS M)D4LOS CCP M1.1 CCPG M1.1 CCP@ I+!"ra %-+ Captura Captura La misma +ase de tiempos de T1R1 Captura Comparaci-n El comparador de+e con7i'urarse para el modo de disparo especial que pone a cero el T1R1 Comparaci-n Comparaci-n El Comparador;es< de+e con7i'urarse para el modo de disparo especial que pone a cero el T1R1 P@1 P@1 El P@1 tendr? la misma 7recuencia y proporci-n de actuaci-n ;interrupci-n de T1R4< P@1 Captura Nin'una P@1 Comparaci-n Nin'una i'ura I R"*%$!r1 CCP1CON 5.%r" %-+ 17;7=R"*%$!r1 CCP2CON 5.%r" %-+ 1D;7 =:E =:E R6@:E R6@:E R6@:E R6@:E R6@:E R6@:E ??? CCPGX CCPGY CCPGM& CCPGM2 CCPGM1 CCPGM0 2it " 2it E +it ":6B N1 %02/"0"+!a.1$B Se lee como ^E^ +it ):*B CCPGX: CCPGYB +it menos si'ni7icativos de P@1 1odo Captura sin usar 1odo Comparaci-n sin usar 1odo P@1B Estos dos +it son los menos si'ni7icativos del ciclo de P@1$ Los ocDo +its m?s si'ni7icativos se encuentran en CCPR#L$ +it (:EBCCPGM&?6CCPGM0O +it de selecci-n del modo de tra+a,o del m-dulo comparador

CCPX$ CCPGM&: CCPGM0 EEEE E1EE E1E1 E11E E111 1EEE 1EE1 1E1E 1E11

M)DO DE TRA3ANO DEL M)D4LO 1-dulo Caputa6Comparaci-n6P@1 desactivado ;reset del m-dulo CCP8< 1odo de captura por 7lanco descendente RCy6CCP 1odo de captura por 7lanco ascendente en RCy6CCP8 1odo de captura. cada * 7lancos ascendentes en RCy6CCP8 1-do apturador$ Cada 16 7lancos ascendentes en RCy6CCP8 1odo comparaci-n. activa la patilla. se pone a 1 RCy6CCP8 al coincidir los valores ;el +it CCP8I se pone a uno< 1odo de comparaci-n se pone a E la patilla RC6CCP8 al coincidir los valores ;el +it CCP8I se pone a uno< 1odo de comparaci-n. 'enera una interrupci-n so79are ;el +it CCP8I se pone a 1. el pin de CCP8 no es a7ectado< 1odo de comparaci-n. en el que se produce un disparo especial para cada m-dulo ;el +it CCP8I se pone a uno. el pin CCP8 no es a7ectado<O CCP1 resetea T1R1O CCP4 resetea T1R1 y comien%a una conversi-n de A63 ;si el m-dulo de A63 se Da+ilita< 1odo de P@1

1188 TaE/a 4

MOD4LO CONVERTIDOR ANAL)'ICO=DI'ITAL 5A=D7 El m-dulo de conversi-n A+a/-*% 1=D%*%!a/ dispone de cinco entradas para los dispositivos de 4! pines y ocDo para los otros dispositivos de la 7amilia$ A travMs de la entrada anal-'ica se aplica la seVal anal-'ica a un condensador de captura y retenci-n ;sample and hold< que despuMs se introduce en el convertidor$ El convertidor de apro8imaciones sucesiva da como resultado una pala+ra de 1E +its$ El convertidor A63 puede seleccionar como tensi-n de re7erencia la interna A33 y masa o +ien una e8terna que se introdu%ca entre RA(6AN(6A RE _ y RA(6AN(6ARE $ Cuando se selecciona la tensi-n de re7erencia e8terna. Day que tener en cuenta que e8isten al'unas limitacionesO el m?8imo volta,e aplicado a la patilla ARE _ ;RA(6AN(< ser? A33_E.(A y el mHnimo A33:4.)A$ En cuanto a la tensi-n ARE : ;RA46AN4< la mHnima tensi-n ser? ASS:E.(A y la m?8ima ARE _ : 4A. asH por e,emplo. si la tensi-n de alimentaci-n es de )A. la tensi-n en RA(6AN( no podr? e8ceder de )A$ Por lo que el m?8imo volta,e en ARE : ser? de (A$ Siempre se Da de cumplir que $ El convertidor A63 tiene como caracterHstica especial el ser capa% de se'uir tra+a,ando mientras el dispositivo estM en el modo SEEP$ Para ello el oscilador interno RC de+e conectarse al conversar$ El m-dulo de A63 tiene cuatro re'istros$ Estos re'istros sonB J ARDES B Parte alta del resultado de la conversi-n J ADREL B Parte +a,a del resultado de la conversi-n J ADCON0B Re'istro de Control E J ADCON1. Re'istro de Control 1 Los re'istros ADCON0 de control del 7uncionamiento del conversar se muestra se'uidamente al i'ual que el re'istro ADCON1 de con7i'uraci-n de los pines del puerto$ Los pines del P5RTA pueden con7i'urarse como entradas anal-'icas ;RA. tam+iMn puede ser entrada de tensi-n de re7erencia< o como E6S di'ital$ Puede encontrarse in7ormaci-n adicional so+re los convertidores A63 de ran'o medio de la 7amilia PICmicroTm en el manual de re7erencia ;3S((E4(<$ R"*%$!r1 ADCON0 5.%r" %-+ /F;7 R6@:E R6@:E R6@:E R6@:E R6@:E R6@:E =:E R6@:E ADCS1 ADCS0 CAS2 CAS1 CAS0 '0=8DONE ??? ADON

2it "

2it E

+it ":6B ADCS1:ADCS0B +it de selecci-n de relo, para el Convertidor A63 EE osc64 E1 osc 6! 1E osc6(4 11 RC ;Procede del oscilador RC interno< +it ):(B CA2:CA0: +it de selecci-n del canal anal-'ico EEE Q Canal E. ;RAE6ANE< EE1 Q Canal 1. ;RA16AN1< E1E Q Canal 4. ;RA46AN4< E11 Q Canal (. ;RA(6AN(< 1EE Q Canal *. ;RA*6AN*< 1E1 Q Canal ). ;RA)6AN)<O los PIC16 !"# de 4! pines no tienen este canal 11E Q Canal 6. ;RA66AN6<O los PIC16 !"# de 4! pines no tienen este canal 111 Q Canal ". ;RA"6AN"<.. los PIC 1 6 !"# de 4! pines no tienen este canal +it 4B 'O=8DONE$ +it de estado de la conversi-n A63 S% ADONO1 1Q La conversi-n A63 est? en marcDa ;mientras est? a 1 se est? reali%ando la conversi-n< E Q La conversi-n Da 7inali%ado$ ;el +it se pone a cero autom?ticamente por Dard9are cuando la conversi-n A63 7inali%a< el resultado de la conversi-n aparece en A3R3ESBA3RESL +it 1B N1 %02/"0"+!a.1B Se lee como SEU +it EB ADONB +it de puesta en marcDa 1 Q El convertidor A63 est? operativo E Q El convertidor A63 est? apa'ado y no consume corriente$

Re'istro A3C5N1 ;direcci-n I D< =:E =:E R6@:E =:E ADFM ??? ??? ??? 2it "

R6@:E PCF'&

R6@:E PCF'2

R6@:E PCF'1

R6@:E PCF'0 2it E

+it "B ADFMB Selecciona el 7ormato del resultado de la conversi-n A63 1 Q Pone en el re'istro ARDESA los seis +it de mayor peso a SEU ;alineaci-n a la derecDa<$ E Q pone los 6 +it de menor peso del re'istro ADRESL a SEU ;alineaci-n a la i%quierda<$ Por lo tanto los 16 +its que 7orman el re'istro ARDESA?ARDESL con ADFMQ1 tiene los 6 +it de mayor peso a cero y con ADFMQE los 6 +it de menor peso est?n a cero +it 6:*B No implementadosB Se leen como cero +it (:EB PCF'&:PCF'0B +its de con7i'uraci-n de los canales de entrada del convertidor A63$ Se utili%an para con7i'urar las patillas como E6S di'ital o como entrada anal-'ica de acuerdo con la si'uiente ta+laB PCF'&: AN";1< AN6517 AND517 AN4 AN& AN2 AN1 AN0 VREFP VREF? CAAN= PCF'0 RE2 RE1 RE0 RAD RA& RA2 RA1 RA0 REFS V EEEE A A A A A A A A A33 ASS !6E EEE1 A A A A ARE _ A A A RA( ASS "61 EE1E 3 3 3 A A A A A A33 ASS )6E EE11 3 3 3 A ARE _ A A A RA( ASS *61 E1EE 3 3 3 3 A 3 A A A33 ASS (6E E1E1 3 3 3 3 ARE _ 3 A A RA( ASS 461 E11# 3 3 3 3 3 3 3 3 A33 ASS E6E 1EEE A A A A ARE _ ARE : A A RA( RA4 664 1EE1 3 3 A A A A A A RA( ASS 66E 1E1E 3 3 A A ARE _ A A A RA( ASS )61 1E11 3 3 A A ARE _ ARE : A A RA( RA4 *64 11EE 3 3 3 A ARE _ ARE : A A RA( RA4 (64 11E1 3 3 3 3 ARE _ ARE : A A RA( RA4 464 111E 3 3 3 3 3 3 3 A A33 ASS 16E 1111 3 3 3 3 ARE _ ARE : 3 A RA( RA4 ` AQ Entrada Anal-'icaO 3 Q E6S 3i'italO ;1< Estos canales no est?n disponi+les para los dispositivos de 4! pines TaE/a D Los re'istros ADRESA:ADRESL contienen los 1E +its resultado de la conversi-n A63$ Cuando se completa la conversi-n A63. el resultado se 'uarda en los re'istros y se pone a cero el +it 'O=DONE y el 7la' de 7in de conversi-n ADIF ;PIR1C6P< se pone a 1$El dia'rama de +loques del m-dulo conversar A63 es el de la i'ura 4*$ 3espuMs de que el conversar A63 se Da con7i'urado como se quiere. la selecci-n del canal de+e reali%arse antes de Dacer la adquisici-n$ Los canales de entrada anal-'ica de+en tener los correspondientes +its del re'istro TRIS seleccionados como entradas$ Para determinar el tiempo de muestreo. ver la secci-n I$($ Para reali%ar una conversi-n A63 de+en se'uirse los si'uientes pasosB 1$ Con7i'urar el m-dulo conversor A63 J Con7i'urar los pines que actNan como entradas anal-'icas. las seVales que Dar?n de tensi-n de re7erencia la que tra+a,ar?n como E6S di'itales ;ADDCON1<$ J Seleccionar el canal de entrada$ A63 ;ADCON0<$ J Seleccionar la 7uente de la seVal de relo, para la conversi-n A63 ;ADON0<$

4$

($ *$ )$

6$ "$

J Activar el m-dulo de conversi-n A63 ;ADCON0< Activar si. se desea. la interrupci-n$ del m-dulo conversor A63 J Poner a cero el +it ADIF J Poner a uno el +it ADIE J Poner a uno J Poner a una los +its Da+ilitadores 'IE y PEIE Esperar el tiempo requerido para la adquisici-n Inicio de la conversi-n J Poner a 1 el +it 'O=8DONE ;ADCON0< Tiempo de espera para terminar la conversi-n A63 que puede detectarse porB J E8ploraci-n de +it 'O=8DONE . que al 7inali%ar la conversi-n toma el valor SEU J Esperar que se produ%ca una interrupci-n si se Da pro'ramado al 7inali%ar la conversi-n$ J Aunque no se autorice la interrupci-n el 7la'$ ADIF se pone a S 1 S al 7inali%ar la interrupci-n$ Leer el par de re'istros ARDESA:ADRESL donde se encuentran los 1E +its que resultan de la conversi-n y poner a cero el 7la' ADIF$ Para una nueva conversi-n volver a los pasos 1 y 4 . El tiempo de conversi-n por +it est? de7inido por TA3. se e8i'e un mHnimo de 4aTA3 para reali%ar una nueva conversi-n$

R"F9%$%!1$ 2ara /a A.F9%$% %-+ A=D Para que el convertidor A63 pueda tener la e8actitud especi7icada. de+e permitirse la car'a del condensador ;CAOLD< que mantiene la entrada a un nivel de tensi-n$ El modelo de una entrada anal-'ica se muestra en la i'ura 4)$

F%*9ra 106? E$!r9 !9ra ." 9+ 2%+ ." 9+ a+a/ A+a/-*% 1 3e la impedancia de la 7uente ;RS< se toma una muestra a travMs del interruptor ; RSS< la impedancia a7ecta directamente al tiempo de car'a del condensador CAOLD$ La impedancia recomendada para las 7uentes anal-'icas es de 1E G $ Cuando la impedancia disminuye tam+iMn disminuye el tiempo de adquisici-n$ Antes de reali%ar. la conversi-n de+e seleccionarse el canal de la entrada anal-'ica$ Para calcular el tiempo mHnimo de adquisici-n mHnimo se puede utili%ar la si'uiente ecuaci-n. que asume un error de ` LS2 para 1E4* pasos del convertidor A63$

S"/" %-+ ."/ r"/1C ."/ 1+>"r!%.1r A=D

Se de7ine por TA3 al tiempo de conversi-n por +it$ El convertidor A63 requiere un mHnimo de 14 TA3 para la conversi-n de los 1E +its. La seVal de relo, para la conversi-n A63 se selecciona por so7t9are mediante los +its ADCS1:ADCS0 J 4 T5SC J ! T5SC J (4 T5SC J 5scilador interno RC ;4:6 Fs< Para reali%ar conversiones correctas el relo, del convertidor A63 de+e seleccionarse para ase'urar un tiempo mHnimo de TA3 de 1.6 mS$ La ta+la si'uiente muestra los tiempos de T A3 dependiendo de la seVal de relo, seleccionada para la conversi-n A63 F9"+!" ."/ R"/1C A=D Fr" 9"+ %a 0QG%0a ."/ .%$21$%!%>1 O2"ra %-+ ADCS1:ADCS0 MQG EE 1$4) 1/% 5SC64 E1 ) 1/% 5SC6! 6(4 1 E 4E 1/% 5SC ;1.4.(< RC 11 Nota 1 Nota$: 1$ Si la 7uente es el oscilador RC tiene un T A3 tHpico de * Fs. pero puede variar entre 4 b6 Fs$ 4$ Cuando la 7recuencia del dispositivo es mayor de 11/%. la 7uente del oscilador RC para la conversi-n A63 se recomienda solo si se tra+a,a en el modo Sleep$ ($ Para dispositivos de tensi-n mayores ;LC<. compro+ar las caracterHsticas elMctricas TaE/a 6 C1+H%*9ra %-+ ." /1$ P%+"$ ."/ P9"r!1 A+a/-*% 1 Los re'istros ADCON1 y TRIS controlan la con7i'uraci-n de los pines del puerto del convertidor A63$ Cuando se desea con7i'urar una entrada como anal-'ica. de+e con7i'urarse como entrada los +its correspondientes del re'istro TRIS$ Si el +its del TRIS correspondiente se pone a cero ;salida<. el valor di'ital de la salida ;A5/ o A5L< se convertir?$ El 7uncionamiento del convertidor A63 es independiente de los +its CAS2:CAS0 y del valor del TRISB NotasB 1$ Al leer el re'istro del puerto. cualquier pin con7i'urado como un canal anal-'ico se lee como un cero ;nivel +a,o<$ Los pines con7i'urados como entradas di'itales convertir?n la entrada anal-'ica$ Los niveles anal-'icos de una entrada di'ital no a7ectar?n la e8actitud de la conversi-n$ 4$ Los niveles anal-'icos en cualquier pin de entrada di'ital ; AN7:AN0 < pueden causar que el +u77er de entrada consuma una corriente superior a la de las especi7icaciones del dispositivo$ C1+>"r$%1+"$ A=D Si se pone a cero el +it 'O=8DONE durante la conversi-n. se a+orta la conversi-n actual$ El par de re'istros no se modi7icar?n parcialmente con los +it que se Dayan completado Dasta el momento$ Es decir. los re'istros ADRESA:ADRESL se'uir?n conteniendo el valor de la Nltima conversi-n completa ;o el Nltimo valor que se Daya escrito en ADRESA:ADRESL< despuMs de a+ortar la conversi-n A63. es requerido el T A3 de espera para reali%ar la pr-8ima adquisici-n comience$ 3espuMs de 4 TA3 de espera. la adquisici-n en cauce se comien%a autom?ticamente$ En la i'ura 46. despuMs de poner el +it 'O a uno. la primera ve% el se'mento tiene un T C] mHnimo y un TA3 m?8imo$ N1!a: El +it 'O=8DONE no de+e ponerse a uno en la misma instrucci-n que se pone en ON el convertidor A63$

F%*9ra 116? C% /1$ TAD ."/ 1+>"r!%.1r A=D R"*%$!r1 ." r"$9/!a.1$ ." /a 1+>"r$%-+ A=D El par de re'istros ADRESA:ADRESL se car'a con el resultado de 1E +its de la conversi-n A63$ Este par de re'istros se e8tienden Dasta 16 +its$ El m-dulo A63 tiene la posi+ilidad de ,usti7icar el resultado de 1E +its dentro de los 16 +its de la pare,a de re'istros$ La selecci-n del 7ormato de ,usti7icaci-n a la i%quierda o derecDa se reali%a con el +it ADFM ;ADCON1 C"P< $ Los +its restantes ; a los 1E de la conversi-n< se llenan con ceros$ Estos dos re'istros cuando el convertidor A63 est? en 5 y no se utili%a. pueden utili%arse como dos re'istros de ! +its de prop-sito 'eneral$

i'ura 14$: &usti7icaci-n de los resultados de la conversi-n A63 F9+ %1+a0%"+!1 ."/ C1+>"r!%.1r A=D "+ "/ 01.1 S/""2 El m-dulo del convertidor A63 puede tra+a,ar durante el modo Sleep$ Para ello se de+e poner como 7uente de relo, el modo RC ;ADCS16ADCS0 Q 1l<$ Cuando la 7uente de relo, es el RC interno. el m-dulo A63 espera un ciclo de m?quina antes de empe%ar la conversi-n$ Esto permite eliminar el ruido de la conversi-n di'ital. Cuando la conversi-n 7inali%a el +it 'O=8DONE se pone a cero y el resultado se car'a en. la pare,a de re'istros ADRESA:ADRESL$ Si la interrupci-n por 7inal de conversi-n A63 est? Da+ilitada. el dispositivo se despierta$ Si la interrupci-n no est? Da+ilitada. el m-dulo A63 se apa'ar? aunque el +it ADON ;ADCON0 CEP< permane%ca a uno$ Cuando el relo, del convertidor A=D es otra 7uente distinta del RC interno. la instrucci-n sleep a+orta la conversi-n actual y el m-dulo A=D se apa'a. aunque el +it ADON permane%ca a uno$ Apa'ando el m-dulo del convertidor A=D el consumo es m?s +a,o$ EH" !1$ ."/ R"$"! Cuando se 7uer%a un Reset se reesta+lecen todos los re'istros. esto o+li'a a apa'ar el convertidor A63 y se a+orta cualquier conversi-n en curso$ El valor de los re'istros ADRESA:ADRESL no es modi7icado por un Po9er:on Reset$ R"*%$!r1$ a$1 %a.1$ a/ C1+>"r!%.1r A=D Cara !"r#$!% a$ ."/ 1+>"r!%.1r A=D

Nota 1B Cuando el m-dulo A63 est? Sapa'adoU ;5 < no consume corriente M)D4LO DE COM4NICACIONES SERIE SNCRONA: MSSP El m-dulo de comunicaciones serie sHncrona ;1SSP< es un inter7ace serie. Ntil para comunicar con otro peri7Mrico o dispositivos$ Estos peri7Mricos los dispositivos pueden ser memorias EEPR51s serie. re'istros de despla%amiento. controladores de displays. convertidores A63. convertidores 36A. etc$ El m-dulo de 1SSP pueda operar en uno de dos modosB J Serial Peripheral Interface ;SPI< J Inter-Integrated el Circuito ;I4C< Para el control de este m-dulo Day dos re'istros de con7i'uraci-n se trata del re'istro SSPCON : Re'istro de control del Puerto Serie SHncrono ;Sync Serial Port Control Register< en la direcci-n 1*D y el SSPCON2B Re'istro de Control4 del Puerto Serie SHncrono (Sync Serial Port Control Register2< En la direcci-n I1D 6 Adem?s se dispone del re'istro SSPSTAT B Re'istro de estado del puerto Serie ; Sync Serial Port Status Register < en la direcci-n I*. que se'uidamente se descri+en$ Re'istro SSPSTATB Re'istro de estado del puerto Serie ;3irecci-n I*D< R6@:E R6@:E R:E R:E R:E R:E R:E R:E S1P C0E 36\A P S R6\@ =A 2 2it " 2it E +it "B S1PB ase de datos de entrada SPI M1.1 Ma$!"r SPI 1 Q 1uestra datos de entrada al 7inal del tiempo de salida E Q 1uestra datos de entrada a la mitad del tiempo de salida M1.1 "$ /a>1 SPI S1P de+e ser +orrado cuando SPI se emplea en modo esclavo M1.1 I2C Ma$!"r 1 E$ /a>1 1Q 3esDa+ilita control de variaciones para velocidad est?ndar ;1EE 0/% y 11/%< EQ /a+ilita control ;*EE0/%< +it 6B CBEB Selecci-n del 7lanco de relo, SPI ;ver los dia'ramas de tiempos de las i'uras 1E$6. 1E$" y 1E$I< CBP O 0 1Q 3ato transmitido en 7lanco ascendente de SC0 EQ 3ato transmitido en 7lanco descendente de S30 CBP O 1 1Q 3ato transmitido en 7lanco descendente de SC0 EQ 3ato transmitido en 7lanco ascendente de SC0 M1.1 I2C Ma$!"r 1 E$ /a>1 1Q Niveles de entrada de acuerdo a S12=S EQ Niveles de entrada con7orme a I4C +it )B D=8AB 2it 3atos63irecciones ;solo en modo I4C< 1Q Indica el Nltimo +yte reci+ido o transmitido es un dato EQ Indica que el Nltimo +yte reci+ido o transmitido es una direcci-n +it *B PB 2it de Stop ;Solo en modo I 4C$ Ese +it es +orrado cuando se desDa+ilita el m-dulo SSP. o cuando el Nltimo +it Start es detectado. SSPEN es +orrado< 1Q Indica que se Da detectado un +it de Stop ;este +it es SEU en RESET< EQ 2it de Stop no detectado$ +it (B SB 2it de Start ;Solo en modo I 4C$ Este +it es +orrado cuando se desDa+ilita el m-dulo SSP. o cuando el +it Nltimo +it Start es detectado. SSPEN es +orrado< 1Q Indica que se Da detectado un +it de Start ;este +it es SEU en RESET< EQ 2it de Start no detectado 2it 4B R=8<B 2it de in7ormaci-n Lectura6escritura ;solo en modo I4C< 1Q Lectura

EQ Escritura M1.1 I2C M1.1 E$ /a>1 1Q Lectura EQ Escritura M1.1 I2C M1.1 Ma$!"r 1Q Transmisi-n en pro'reso EQ Transmisi-n no en pro'reso +it 1 4AB Activaci-n de direcci-n ;s-lo en modo I4C 1E:+its< 1Q Indica que es necesario actuali%ar la direcci-n en el re'istro SSPA33 EQ No es necesario actuali%ar la direcci-n +it E 3FB 2it estado de 2u77er lleno R" "2!1r 5M1.1 SPI " I2C7 1Q Recepci-n completa. SSP2= est? lleno EQ Recepci-n no completa. SSP2= est? vacHo Tra+$0%$1r 5M1.1 I2C7 1Q Transmisi-n en pro'reso. SSP2= est? lleno ;no incluye AC0 y +it de Stop< EQ Transmisi-n completa. SSP2= est? vacHo ;no incluye AC0 y +it de Stop< R"*%$!r1 SSPCON: R"*%$!r1 ." 1+!r1/ ."/ 29"r!1 S"r%" 5D%r" %-+ 14;7 R6@:E R6@:E R6@:E R6@:E R6@:E R6@:E R6@:E @C5L SSP5A SSPEN C0P SSP1( SSP14 SSP11 +it "

R6@:E SSP1E +it E

2it "B <COLB 2it detector de colisi-n 1Q El re'istro SSP2= se Da escrito cuando Day una transmisi-n en proceso ;Se de+e +orrar por so7t9are< EQ No Day colisi-n +it 6B SSPOVB 2it detector de des+ordamiento en recepci-n E+ 01.1 SPI 1Q Se reci+e un nuevo +yte cuando el re'istro SSP2= aNn mantiene los datos anteriores$ En caso de re+ose. los datos del re'istro SSPSR ser?n 7alsos. s-lo puede ocurrir en modo esclavo$ Se de+er? leer el SSP2= . aNn si s-lo se envHan datos. para anular el re+ose$ En modo master el +it no su+e a uno ya que en cada nueva recepci-n6transmisi-n es iniciali%ado por la escritura del re'istro SSP2=$ EQ No Day des+ordamiento E+ 01.1 I2C 1Q Se reci+e un nuevo +yte cuando el re'istro SSP2= aNn mantiene los datos anteriores$ En modo de transmisi-n no tiene importancia. en cualquier caso de+e +orrarse por so7t9are$ EQ No Day des+ordamiento +it )B SSPENB 2it de Da+ilitaci-n del m-dulo SSP ;Synchronous Serial Port< E+ 01.1 SPI 1Q /a+ilita puerto serie y con7i'ura SC0. S35 y S3I como patillas del puerto serie$ EQ 3esDa+ilita el puerto serie y con7i'ura estas patillas como puerto de Entrada6Salida$$ E+ 01.1 I2C 1Q /a+ilita el puerto serie y con7i'ura S3A y SCL como patillas del puerto serie EQ 3esDa+ilita el puerto serie y con7i'ura estas patillas como puerto de Entrada6Salida$ En am+os casos. se de+er?n con7i'urar como entradas o salidas adecuadamente$ 2it *B CBPB 2it de selecci-n de polaridad del relo, E+ 01.1 SPI 1Q Relo, en nivel alto$ Transmisi-n en 7lancos de +a,ada. en recepci-n de su+ida EQ Relo, en nivel +a,o$ Transmisi-n en 7lancos de su+ida. en recepci-n por 7lancos de +a,ada$

EEEE EEE1 EE1E EE11 E1EE

E1E1

E+ 01.1 I2C E$ /a>1 ;En este modo no se usa como master< Control de des+loqueo de SC0 1Q /a+ilita relo, EQ 1antiene relo, en estado +a,o$ 2it (:EBSSPM&:SSPM0B 2it de selecci-n del modo del SSP ;SyncrDonous Serial Port< 1odo 1aster del SPI. relo, E11E 1odo Esclavo I4C. direcci-n de " +its Q 5SC6* 1odo 1aster del SPI. relo, E111 1odo Esclavo I4C. direcci-n de 1E Q 5SC616 +its 1odo 1aster del SPI. relo, 1EEE 1odo 1aster I4C. relo, Q Q5SC6 Q 5SC6(4 ;*8;SSPA33_1<< 1odo 1aster del SPI. relo, 1E11 1odelo Esclavo I4C con soporte QT1R4 salida64 1odo 1aster del SPI. relo, 111E 1odo Esclavo I4C. direcci-n de " +its Q patilla SC0$ /a+ilita de interrupci-n Start y Stop patilla de control \SS Da+ilitados 1odo Esclavo del SPI. relo, 1111 1odo Esclavo I4C. direcci-n de 1E Q patilla SC0$ 3esDa+ilitada +its con +its de interrupci-n Start y patilla \SS. se puede Stop Da+ilitados emplear como I65

1E1E. 11EE y 11E1 Est?n reservados 1EE1. SSPCON2: R"*%$!r1 ." 1+!r1/ 2 ."/ 29"r!1 S"r%" 5.%r" %-+ I17 R6@:E R6@:E R6@:E R6@:E R6@:E R6@:E R6@:E R6@:E >CEN AS0START AC03T AC0EN RCEN PEN RSEN SEN 2it " 2it E 4 2it "B 'CENB 2it de Da+ilitaci-n 'eneral ;s-lo en modo esclavo I C< 1Q /a+ilita Interrupci-n cuando una llamada 'eneral es reci+ida en el SSPST ;EEEED< EQ 3esDa+ilita direcci-n de llamada 'eneral +it 6B ACBSTARTB 2it de estado de reconocimiento ;solo en modo master I4C< M1.1 ." Tra+$0%$%-+ 1Q Reconocimiento del esclavo no reci+ido EQ Reconocimiento del esclavo reci+ido +it )B ACBDTB 2it de reconocimiento ;solo en modo master I4C< M1.1 ." R" "2 %-+ Aalor transmitido cuando el usuario indica una secuencia de reconocimiento y 7inal de una recepci-n$ 1Q No reconocimiento EQ Reconocimiento +it *B ACBENB 2it de Da+ilitaci-n de secuencia de reconocimiento ;s-lo en modo master I4C< M1.1 ." R" "2 %-+ 1Q Indica una secuencia de reconocimiento en patillas S3A y SCL y transmite +it AC03T$ Autom?ticamente +orrado por Dard9are$ EQ Secuencia de reconocimiento en reposo +it (B RCENB 2it de Da+ilitaci-n de recepci-n ;s-lo en modo master I4C< 1Q /a+ilita recepci-n en modo I4C EQ Recepci-n en reposo +it 4B PENB 2it de Da+ilitaci-n de condici-n de Stop; s-lo en modo master I4C< C1+!r1/ SCB ."$E/1F9"a.1

1Q Indica una condici-n de Stop en S3A y SCL$ Autom?ticamente +orrado por Dard9are$ EQ Condici-n de Stop en reposo +it 1B RSENB 2it de Da+ilitaci-n repetir condici-n Start ;s-lo en modo master I4C< 1Q Indica repetici-n de condici-n de Start en S3A y SCL$ Autom?ticamente +orrado por Dard9are$ EQ Condici-n de repetici-n de Start en reposo$ +it EB SENB 2it de Da+ilitaci-n de condici-n Start ;s-lo en modo master I4C< 1Q Indica condici-n de Start en S3A y SCL$ Autom?ticamente +orrado por Dard9are EQ Condici-n de Start en reposo$ 4NIVERSAL SYNCARONO4S ASYNCARONO4S RECEIVER TRANSMITTER 54SART7 El m-dulo transmisor ;=SART< es otro de los dos puertos serie de los que dispone esta 7amilia de microcontroladores$ Los m-dulos de I65$ ;=SART tam+iMn se conocen como Serial Communications o Interface o SCI<$ El =SART puede con7i'urarse como asHncrono 7ull dNple8 que puede comunique con los dispositivos peri7Mricos como el terminales de CRT y los ordenadores personales. o puede con7i'urarse como un sistema sHncrono Dal7 duple8 que puede comunicar con otros microcontroladores. con dispositivos peri7Mricos como A63 o 36A circuitos inte'rados. EEPR51s serie etc$ El =SART puede con7i'urarse en los modos si'uientesB J AsHncrono; ull duple8 < J SHncrono: 1aster ;Dal7 duple8< J SHncrono: Slave ;Dal7 duple8< Poniendo a ^1^ +it SPEN ;RCSTA C"P<. y los +its TRISC C"B6P. se con7i'ura RC6=TX=CB y RC7 =RX=DT como =SART$ En modo sHncrono se utili%an 7ormatos est?ndarB un +it de Start y ocDo +its o nueve +its de Stop. siendo el m?s comNn el de ocDo +its de datos$ R"*%$!r1 ." E$!a.1 @ C1+!r1/ TXSTA 5Tra+$0%$1r7 R6@:E R6@:E R6@:E R6@:E =:E R6@:E R6@:E R6@:E CSRC T#I T#EN S]NC :::: 2R>/ TR1T T#I3 2it " 2it E +it "B CSRCB 2it de selecci-n de relo, 1odo AsHncrono Sin importancia 1odo SHncrono 1 Q 1odo master ;relo, 'enerado internamente para 2R> ;>enerador de 2audios<< E Q 1odo esclavo ;relo, e8terno< +it 6B TXIB /a+ilita transmisi-n de I:! +its 1 Q Transmisi-n de I +its E Q Transmisi-n de ! +its +it )B TXENB 2it de Da+ilitaci-n del transmisor 1 Q /a+ilita transmisi-n E Q 3esDa+ilita transmisi-n NotaB SREN=CREN anula TXEN en modo SYNC$ +it *B SYNCB 2it de selecci-n del modo =SART 1 Q 1odo SHncrono E Q 1odo AsHncrono +it (B S%+ %02/"0"+!arB En lectura escEc +it 4B 3R'AB 2it de selecci-n del ran'o de +audios alto 1odo AsHncrono

1 Q Alta velocidad E Q 2a,a velocidad 1odo SHncrono No se usa este modo +it 1B TRMTB 2it de estado del re'istro de despla%amiento del transmisor ;TSR< 1 Q TSR vacHo E Q TSR lleno +it EB TXIDB Noveno +it de datos de transmisi-n$ Se puede emplear como +it de paridad$ R"*%$!r1 ." "$!a.1 @ C1+!r1/ RCSTA 5R" "2!1r7 R6@:E R6@:E R6@:E R6@:E =:E R6@:E R6@:E R6@:E SPEN R#I SREN CREN :::: ERR 5ERR R#I3 2it " 2it E +it "B SPENB 2it de Da+ilitaci-n del puerto serie 1 Q /a+ilita puerto serie ;con7i'ura patillas RC7=RX=DT y RC6=TX=CB para el puerto serie< E Q 3esDa+ilita puerto serie +it 6B RXIB /a+ilita recepci-n de I:! +its 1 Q Selecciona I +its de recepci-n E Q Selecciona ! +its de recepci-n +it )B SRENB 2it de Da+ilitaci-n de recepci-n Nnica 1odo asHncrono Este modo no se usa 1odo SHncrono master 1 Q /a+ilita una recepci-n Nnica E Q 3esDa+ilita una recepci-n Nnica Este +it se +orra despuMs de completar la recepci-n 1odo SHncrono esclavo En este modo no se usa +it *B CRENB 2it de Da+ilitaci-n de recepci-n continua 1odo AsHncrono 1 Q /a+ilita recepci-n continua E Q 3esDa+ilita recepci-n continua 1odo SHncrono 1 Q /a+ilita recepci-n continua Dasta que el +it CREN sea +orrado ;CREN anula SREN< E Q 3esDa+ilita la recepci-n continua +it (B Sin implementarB En lectura es cEc +it 4B FERRB 2it de error de empaquetamiento 1 Q Error de empaquetamiento ;Puede actuali%arse al leer el re'istro RCRE' y reci+ir el si'uiente +yte< E Q No Day error +it 1B OERRB 2it de error de des+ordamiento 1 Q Error de des+ordamiento ;puede ser +orrado al +orrar CREN< E Q No Day des+ordamiento +it EB RX'DB Noveno +it de datos de recepci-n$ Se puede emplear como +it de paridad '"+"ra.1r ." 3a9.%1$ Ra!" 53R'7 Este 'enerador sirve tanto para el modo sHncrono como el asHncrono y consiste de un contador6divisor de 7recuencia de ! +its controlado por el re'istro SP3R' 5IIA<$ 3e tal manera que la 7recuencia de transmisi-n se calcula de acuerdo a la si'uiente ta+laB SYNC 3R'AO05EaCa >"/1 %.a.7 3R'AO1 5A/!a V"/1 %.a.7

E ;1odo asHncrono< 1 ;1odo SHncrono<

2aud rate Q 2aud rate Q

6;6*;#_1<< 5SC6;*;#_1<<

5SC

2aud rate Q ::

5SC

616;#_1<<

3e+ido a que el divisor es de ! +its. no se puede tener cualquier velocidad de transmisi-n deseada. ya que # se de+er? redondear al entero m?s cercano$ En las dos ta+las anteriores se muestran al'unos valores de velocidad de transmisi-n ;+aud< est?ndar. el divisor necesario ;#QSP2R>< +a,o di7erentes 7recuencias osc y el error producido en porcenta,e$ E,emploB C?lculo de la proporci-n del error de velocidad de transmisi-n para las si'uientes condicionesB 5SC Q 16 1/d Aelocidad de transmisi-n deseada Q I6EE +audios 2R>/ Q E S]NC Q E

Como puede apreciarse. el error no tiene nin'una importania para la mayorHa de las aplicaciones. no o+stante. se puede reali%ar los c?lculos empleando el Hndice ; 3R'AQ1< y sustituyendo la constante 6* por 16 ;ver la ta+la< y compro+ar si el error se reduce$ Los datos de la patilla RC7=RX=DT son muestreados en tres tiempos para detectar y determinar me,or si el nivel presente en la patilla R# est? a nivel alto o +a,o$ Si el +it 3R'A ;TXSTAC4P< est? a cero. el muestreo se reali%a en el sMptimo. octavo. y noveno 7lanco de +a,ada de 81 6 de relo,$ Si por el contrario. el +it 3R'A est? a uno. el muestreo tiene lu'ar en el tercer 7lanco de relo, precedido de la se'unda su+ida de relo, y de la primera +a,ada de 8* de relo,$ R"*%$!r1$ a$1 %a.1$ a/ '"+"ra.1r ." 3a9. Ra!" D%r" %-+ N10Er" 3%! 7 3%! 6 3%! D 3%! 4 3%! & 3%! 2 3%! 1 3%! 0 Va/1r "+ Va/1 POR,3OR "+ r"$!1 ." R"$" I!D T#STA CSRC T#I T#EN S]NC ::: 2R>/ TR1T T#I3 EEEE bE1E EEEE E1E 1!D RCSTA SPEN R#I SREN CREN A33EN ERR 5ERR R#I3 EEEE EEE# EEEE EEE# IID SP>2R> Re'istro 'enerador de 2aud Rate Leyenda$: 8 Q desconocido uQ sin cam+ios : Q Sin implementar. se lee SEU M1.1 A$#+ r1+1 4SART Como ya se Da dicDo. en este modo de comunicaciones se emplea una con7i'uraci-n est?ndar de un +it de Start. ocDo o nueve +its de datos. y un +it de Stop$ Este modo de tra+a,o es detenido durante la 7unci-n Sleep$