Beruflich Dokumente

Kultur Dokumente

Lab 1

Hochgeladen von

فیضان حنیف0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

15 Ansichten13 Seiten12026565626

Originaltitel

LAB 1

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument melden12026565626

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

15 Ansichten13 SeitenLab 1

Hochgeladen von

فیضان حنیف12026565626

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 13

1

USMAN INSTITUTE OF TECHNOLOGY

HAMDARD UNIVERSITY

DEPARTMENT OF ELECTRICAL ENGINEERING

VLSI DESIGN (EE-411)

SPRING-2014

Engr. Zohaib Jawaid

Engr. Kashif Ali Arshad

Engr. S. Aimen Naseem

Engr. Sameer Ahmad

EXPERIMENT # 01: Introduction to FPGA (Spartan 3E) and VERILOG

Name of Student: _____________________________________________________________

Roll No.: _________________________________Group:_____________________________

Date of Experiment : _____________________________________________

Report Submitted on : _____________________________________________

Marks Obtained : ______________________________________________

Remarks if any : ______________________________________________

Signature : _____________________________________________

2

INTRODUCTION TO FPGA (SPARTAN 3E)

Overview:

FPGA (SPARTAN 3E) is a complete, ready-to-use circuit development platform based on a Xilinx

Spartan 3E FPGA. Its onboard high-speed USB2 port, 16Mbytes of RAM and ROM, and several

I/O devices and ports make it an ideal platform for digital systems of all kinds, including

embedded processor systems based on Xilinxs Micro Blaze. The USB2 port provides board

power and a programming interface, so the Nexys2 board can be used with a notebook computer

to create a truly portable design station It can host countless FPGA-based digital systems, and

designs can easily grow beyond the board using any or all of the five expansion connectors. Four

12-pin Peripheral Module (Pmod) connectors can accommodate up to eight low-cost Pmods to

add features like motor control, A/D and D/A conversion, audio circuits, and a host of sensor and

actuator interfaces

Features:

500K-gate Xilinx Spartan 3E FPGA

USB2-based FPGA configuration and high-speed data transfers (using the free Adept

Suite Software)

USB-powered (batteries and/or wall-plug can also be used)

16MB of Micron PSDRAM &16MB of Intel Strata Flash ROM

Xilinx Platform Flash for nonvolatile FPGA configurations

Efficient switch-mode power supplies (good for battery powered applications)

50MHz oscillator plus socket for second oscillator

60 FPGA I/Os routed to expansion connectors (one high speed Hirose FX2 connector

and four 6-pin headers)

8 LEDs, 4-digit 7-seg display, 4 buttons, 8 slide switches

Ships in a plastic carry case with USB cable

3

User I/O

The Nexys2 board includes several input devices, output devices, and data ports, allowing many

designs to be implemented without the need for any other components.

Inputs: Slide Switches and Pushbuttons

Four pushbuttons and eight slide switches are provided for circuit inputs. Pushbutton inputs are

normally low, and they are driven high only when the pushbutton is pressed. Slide switches

generate constant high or low inputs depending on their position. Pushbutton and slide switch

inputs use a series resistor for protection against short circuits (a short circuit would occur if an

FPGA pin assigned to a pushbutton or slide switch was inadvertently defined as an output).

Pin Configuration:

4

5

INTRODUCTION TO VERILOG:

In electronics, a hardware description language or HDL is any language from a class of

computer languages for formal description of electronic circuits. The two most widely-used and

well-supported HDL varieties used in industry are:

VERILOG

VHDL

VERILOG is a HARDWARE DESCRIPTION LANGUAGE (HDL). A hardware description

language is a language used to describe a digital system: for example, a network switches, a

microprocessor or a memory or a simple flip-flop. This just means that, by using a HDL, one can

describe any (digital) hardware at any level. VERILOG is used by several companies in the

commercial chip design and manufacturing sector today. VERILOG allows a designer to develop

a complex hardware system, e.g., a VLSI chip containing millions of transistors, by defining it at

various levels of abstraction

Simulation and Synthesis

Simulation tools typically accept full set of VERILOG language constructs.

Synthesis tools typically accept only a subset of the full VERILOG language constructs.

Modules

Modules are basic building blocks of VERILOG. Description of the logic being modeled is

placed inside modules. Module definition starts with keyword module. Ends with the keyword

endmodule.

For Example Module is declared: Module dff (q,qn,d,clk)

Modules communicate with the outside world through ports. Module port is similar to pins in

hardware.

Nets

Nets represent connections between hardware elements. Just as in real circuits, nets have values

continuously driven onto them by the outputs of devices that they are connected to. net a is

connected to the output of and gate. Net a will continuously Assume the value computed at the

output of gate g], which is b anded with c. Nets are declared primarily with the keyword wire.

Nets are one-bit values by default unless they are declared explicitly as vectors. The term wire

and net are often used interchangeably. The default value of a net is z. Nets get the output value.

of their drivers. If a net has no driver, it gets the value z.

Example

Wire a; // Declare net a for the above circuit

Wire b, c; //Declare two wires b, c for the above circuit

Wire d = 'b0; // Net d is fixed to logic value 0 at declaration

6

SOFTWARE INTRODUCTION:

Steps for Configuration:

STEP 1:

To create a New Project

Select File > New Project. The New Project Wizard appears.

STEP 2:

Type tutorial or any other name in the Project Name field.

Verify that HDL is selected from the Top Level Source Type list

Enter or browse to a location for the new project. A tutorial subdirectory is created

automatically

7

STEP 3: Add New Source

STEP 4: Select VERILOG Module and Enter File Name and specify its location

8

STEP 5: Assign input and output variables

STEP 6: Summary

STEP 7: Click on Next

for n # of inputs

9

STEP 8: Summary

STEP 9: Project is now created

STEP 10: write desired program in .v file and save it

Program here

10

STEP 11:in user constraint click create area constraints to assign pin locations

11

STEP 12:

Click to synthesize- XST to check program.

click on implement design

click Generate Programming file in the .bit format

12

DIGILENT ADEPT

Digilent Adept is a powerful application which allows for configuration and data transfer with

Xilinx logic devices.

It Configure the Xilinx logic devices and Initialize a scan chain, program FPGAs, CPLDs, and

PROMs, organize and keep track of your configuration files. It also used to Transfer data and

from the onboard FPGA on your system board. It Organize and quickly connect to your

communications modules.

STEP 13:

following first figure of this step indicate when no device is connected.

Connect Device and Click Browse option of FPGA block

STEP 14: Browse Project and select .bit file then click Program.

Device connected

13

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Brochure PDFDokument15 SeitenBrochure PDFفیضان حنیفNoch keine Bewertungen

- C3600 Series: FeaturesDokument1 SeiteC3600 Series: FeaturesdadiNoch keine Bewertungen

- Total Sheet2Dokument4 SeitenTotal Sheet2فیضان حنیفNoch keine Bewertungen

- Notification: 15 December 2015Dokument1 SeiteNotification: 15 December 2015فیضان حنیفNoch keine Bewertungen

- 12-02-11technical Specification For 3.ph 4 Wire STW PDFDokument36 Seiten12-02-11technical Specification For 3.ph 4 Wire STW PDFفیضان حنیفNoch keine Bewertungen

- Matlab Prog PDFDokument1.078 SeitenMatlab Prog PDFina100% (1)

- ChokshiDokument27 SeitenChokshiAbhishek KumarNoch keine Bewertungen

- 2SC3688 SanyoSemiconDeviceDokument3 Seiten2SC3688 SanyoSemiconDeviceفیضان حنیفNoch keine Bewertungen

- Biosensors 150314095944 Conversion Gate01Dokument40 SeitenBiosensors 150314095944 Conversion Gate01فیضان حنیفNoch keine Bewertungen

- Sipart DR 22-Dr 24 Man en 2.0Dokument14 SeitenSipart DR 22-Dr 24 Man en 2.0فیضان حنیفNoch keine Bewertungen

- Opc Ua Sean LeonardDokument9 SeitenOpc Ua Sean Leonardpartho143Noch keine Bewertungen

- COGNOS Report Studio Users GuideDokument458 SeitenCOGNOS Report Studio Users GuideTrisroy MoroNoch keine Bewertungen

- FDC PC-E Manual V1.0 August-2007Dokument19 SeitenFDC PC-E Manual V1.0 August-2007فیضان حنیفNoch keine Bewertungen

- MatrikonOPC AE Historian DatasheetDokument2 SeitenMatrikonOPC AE Historian Datasheetفیضان حنیفNoch keine Bewertungen

- JobFor Worksofficer 2015Dokument2 SeitenJobFor Worksofficer 2015فیضان حنیفNoch keine Bewertungen

- How to Write a Successful Letter of Motivation for a Master's Program in GermanyDokument1 SeiteHow to Write a Successful Letter of Motivation for a Master's Program in GermanyReska Nurul FadilaNoch keine Bewertungen

- AS09 - Redundant Controllers r2Dokument4 SeitenAS09 - Redundant Controllers r2sdiamanNoch keine Bewertungen

- VR18 Manual V2.3SDokument96 SeitenVR18 Manual V2.3Sفیضان حنیفNoch keine Bewertungen

- AS09 - Redundant Controllers r2Dokument4 SeitenAS09 - Redundant Controllers r2sdiamanNoch keine Bewertungen

- Pid 1Dokument20 SeitenPid 1Nithindev GuttikondaNoch keine Bewertungen

- Faizan Hanif S/o Abdul Hanif: Professional SummaryDokument2 SeitenFaizan Hanif S/o Abdul Hanif: Professional Summaryفیضان حنیفNoch keine Bewertungen

- ModbusDokument34 SeitenModbusTecnicoItcaNoch keine Bewertungen

- 51 52 25 86 PDFDokument292 Seiten51 52 25 86 PDFفیضان حنیفNoch keine Bewertungen

- Lecture6 Classical Pid Controllers1Dokument79 SeitenLecture6 Classical Pid Controllers1فیضان حنیفNoch keine Bewertungen

- Industrial Flow MeasurementDokument244 SeitenIndustrial Flow MeasurementRoxana Gligor100% (3)

- Lab 4Dokument4 SeitenLab 4فیضان حنیفNoch keine Bewertungen

- Specifications Specifications Specifications: Analog Input Analog Input Analog InputDokument1 SeiteSpecifications Specifications Specifications: Analog Input Analog Input Analog Inputفیضان حنیفNoch keine Bewertungen

- Hart CommunicatorDokument44 SeitenHart CommunicatorkishoreprithikaNoch keine Bewertungen

- Lab 6Dokument3 SeitenLab 6فیضان حنیفNoch keine Bewertungen

- Lab 5Dokument3 SeitenLab 5فیضان حنیفNoch keine Bewertungen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Sample Cover Letter: No Work ExperienceDokument4 SeitenSample Cover Letter: No Work ExperienceMaya ElvisaNoch keine Bewertungen

- Galaxy Service ManualDokument100 SeitenGalaxy Service ManualGovind RajNoch keine Bewertungen

- TM4C129XNCZAD MicrocontrollerDokument2.191 SeitenTM4C129XNCZAD Microcontrollermamaligosu1Noch keine Bewertungen

- Cisco As5300 Voice GatewayDokument12 SeitenCisco As5300 Voice GatewayAbderrahmane AbdmezianeNoch keine Bewertungen

- Mobil Pegasus™ 1100 Series Mobil Pegasus™ 1100 Series Mobil Pegasus™ 1100 Series Mobil Pegasus™ 1100 SeriesDokument3 SeitenMobil Pegasus™ 1100 Series Mobil Pegasus™ 1100 Series Mobil Pegasus™ 1100 Series Mobil Pegasus™ 1100 SeriesMudabbir Shan AhmedNoch keine Bewertungen

- Industry 4.0 FinaleDokument25 SeitenIndustry 4.0 FinaleFrame UkirkacaNoch keine Bewertungen

- Zhao PeiDokument153 SeitenZhao PeiMuhammad Haris HamayunNoch keine Bewertungen

- Paint Color Comparison ChartDokument132 SeitenPaint Color Comparison ChartCarlos Rubiños AlonsoNoch keine Bewertungen

- Milenium BypassDokument1 SeiteMilenium BypassdinotecNoch keine Bewertungen

- Applying The Haar Wavelet Transform To Time Series InformationDokument27 SeitenApplying The Haar Wavelet Transform To Time Series InformationJohn LemonNoch keine Bewertungen

- FlowCon General InstructionDokument4 SeitenFlowCon General InstructionGabriel Arriagada UsachNoch keine Bewertungen

- 4PL Supply Chain Transformation SolutionsDokument2 Seiten4PL Supply Chain Transformation SolutionsGourav HegdeNoch keine Bewertungen

- Dry Hands MinecraftDokument1 SeiteDry Hands MinecraftBrandon RotzankNoch keine Bewertungen

- KernelDokument326 SeitenKernelSkyezine Via Kit FoxNoch keine Bewertungen

- Fundamentals 2014Dokument959 SeitenFundamentals 2014Angelo Vittorio VettorazziNoch keine Bewertungen

- Product Portfolio ManagementDokument10 SeitenProduct Portfolio ManagementSandeep Singh RajawatNoch keine Bewertungen

- Ahmad Humayun SohailDokument6 SeitenAhmad Humayun SohailHumayun SohailNoch keine Bewertungen

- AOE - FormDokument8 SeitenAOE - FormBimal GuptaNoch keine Bewertungen

- Fortumo Mobile Payments API GuideDokument8 SeitenFortumo Mobile Payments API GuideVladimir UtješinovićNoch keine Bewertungen

- Active Control of Flow Separation Over An Airfoil Using Synthetic JetsDokument9 SeitenActive Control of Flow Separation Over An Airfoil Using Synthetic JetsDrSrujana ReddyNoch keine Bewertungen

- Tyre ManufacturingDokument18 SeitenTyre ManufacturingniteshkrisNoch keine Bewertungen

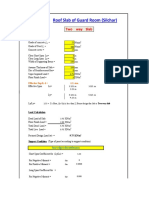

- Roof Slab of Guard RoomDokument3 SeitenRoof Slab of Guard RoomAditya KumarNoch keine Bewertungen

- Daily DAWN News Vocabulary With Urdu Meaning (05 April 2020) PDFDokument6 SeitenDaily DAWN News Vocabulary With Urdu Meaning (05 April 2020) PDFAEO Begowala100% (2)

- System Engineering Management Plan (SEMPDokument2 SeitenSystem Engineering Management Plan (SEMPKatie WestNoch keine Bewertungen

- 3095MV Calibration Procedure W QuickCal Merian 4010Dokument8 Seiten3095MV Calibration Procedure W QuickCal Merian 4010luisalbertopumaNoch keine Bewertungen

- 4c - Expanded - RevisedDokument132 Seiten4c - Expanded - RevisedMartín Serena75% (4)

- I) CentrifugesDokument46 SeitenI) Centrifugesiahim87Noch keine Bewertungen

- Strength of A440 Steel Joints Connected With A325 Bolts PublicatDokument52 SeitenStrength of A440 Steel Joints Connected With A325 Bolts Publicathal9000_mark1Noch keine Bewertungen

- Admin Interview Questions and Answers - Robert HalfDokument2 SeitenAdmin Interview Questions and Answers - Robert HalfWaqqas AhmadNoch keine Bewertungen

- Disney Channel JRDokument14 SeitenDisney Channel JRJonna Parane TrongcosoNoch keine Bewertungen