Beruflich Dokumente

Kultur Dokumente

Arquitectura Del Microprocesador

Hochgeladen von

CrashMichelCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Arquitectura Del Microprocesador

Hochgeladen von

CrashMichelCopyright:

Verfügbare Formate

INTRODUCCIN A LOS MICROPROCESADORES Y

MICROCOMPUTADORES.

1. Arquitecturas Princeton y Harvard.

2. Arquitectura de buses.

3. Juego de instrucciones.

4. Modos de direccionamiento.

5. Subrutinas: la pila o stack.

6. Interrupciones y accesos directos a memoria.

7. Dispositivos de entrada/salida o perifricos.

ARQUITECTURAS DE LOS

MICROCOMPUTADORES

Arquitectura Princeton.

La memoria de programa y la

memoria de datos se hallan

sobre un nico espacio de

memoria.

Al espacio nico de memoria se

accede mediante un nico bus

de direcciones y un nico bus

de datos/instrucciones.

Es la arquitectura tpica de los

grandes microcomputadores

(ordenadores personales).

Tambin se encuentra en

algunos microcontroladores

(por ejemplo, NEC).

Arquitectura Harvard.

La memoria de programa y la memoria de datos

constituyen dos espacios de memoria separados.

El acceso a cada espacio de memoria puede llegar a

ser mediante buses distintos, es decir, puede haber

dos buses de direcciones, un bus de datos y un bus

de instrucciones).

Lo ms habitual es que exista un nico bus de

direcciones, en cuyo caso debe existir alguna seal

de control que permita diferenciar a que espacio de

memoria se hace referencia (por ejemplo, seales

de READ, WRITE y FETCH).

Es la arquitectura propia de un buen nmero de

microcontroladores (por ejemplo, PIC).

ARQUITECTURA PRINCETON (I)

Un nico espacio de direccionamiento.

La memoria de programa, la memoria de

datos y los puertos de entrada/salida,

comparten un nico espacio de

direccionamiento.

Basta con seales de control de READ y

WRITE.

El espacio de direccionamiento se reparte

de acuerdo a las necesidades de la

aplicacin, no siendo necesario llenar todo

el espacio de direccionamiento.

Tpico de los microprocesadores de alta

gama de Motorola (68000 y posteriores).

FFFFFF

FFFE00

FFFDFF

F00000

EFFFFF

C00000

BFFFFF

800000

7FFFFF

000000

MEMORIA DE

PROGRAMA

MEMORIA DE

DATOS

PUERTOS DE

ENTRADA/SALIDA

512 registros de

entrada/salida

3 M posiciones de

memoria de datos

8 M posiciones de

memoria de

programa

24 bits de direcciones

Espacio de direccionado = 2

24

registros o posiciones (16 M)

ARQUITECTURA PRINCETON (II)

Dos espacios de direccionamiento.

Uno para la memoria de programa ms la

memoria de datos y otro para los puertos

de entrada/salida.

Si se comparte el bus de direcciones, es

necesario aadir una seal de control que

permita distinguir a que espacio se hace

referencia (por ejemplo, IO/M).

Los dos espacios de direccionamiento se

reparten de acuerdo a las necesidades de

la aplicacin, no siendo necesario

llenarlos del todo.

Tpico de los microprocesadores de alta

gama de Intel (8086 y posteriores).

FFFFFF

C00000

BFFFFF

800000

7FFFFF

000000

MEMORIA DE

PROGRAMA

MEMORIA DE

DATOS

4 M posiciones de

memoria de datos

8 M posiciones de

memoria de

programa

24 bits de direcciones para memoria

Espacio de direccionado = 2

24

posiciones (16 M)

FFF

E00

DFF

000

512 registros de

entrada/salida

12 bits de direcciones para entrada/salida

Espacio de direccionado = 2

12

registros (4 K)

PUERTOS DE

ENTRADA/SALIDA

ARQUITECTURA HARVARD

Dos o tres espacios de direccionamiento.

Pueden existir hasta tres espacios de

direccionamiento, uno para la memoria de

programa, otro para la memoria de datos y el

tercero para los puertos de entrada/salida.

Es frecuente que la memoria de datos y los

puertos de entrada/salida compartan un

mismo espacio de direccionamiento.

Si se comparte el bus de direcciones, es

necesario aadir seales de control que

permitan distinguir a que espacio se hace

referencia.

Los espacios de direccionamiento se reparten

de acuerdo a las necesidades de la aplicacin,

no siendo necesario llenarlos del todo.

Tpico de muchos microcontroladores (por

ejemplo, 8051 de Intel, derivados y PIC).

FFFF

C000

BFFF

0000

MEMORIA DE

PROGRAMA

MEMORIA DE

DATOS

48 K posiciones

de memoria de

programa

16 bits de direcciones para memoria de programa

Espacio de direccionado = 2

16

posiciones (64 K)

FFFF

FE00

FDFF

8000

7FFF

0000

PUERTOS DE

ENTRADA/SALIDA

512 registros de

entrada/salida

32 K posiciones

de memoria de

datos

16 bits de direcciones para memoria de datos

ms entrada/salida

Espacio de direccionado = 2

16

registros (64 K)

ARQUITECTURA DE BUSES (I)

La arquitectura de un microcomputador basado en un microprocesador

ms dispositivos de memoria y de entrada/salida se basa normalmente en

tres buses (conjuntos de seales):

Bus de direcciones

Comn para todos los espacios de direccionamiento.

Dimensin establecida por el espacio de direccionamiento mayor.

Generado por el microprocesador.

Bus de datos (datos/instrucciones)

Comn para todos los espacios de direccionamiento.

Dimensin establecida generalmente por la unidad de proceso.

Bidireccional.

Bus de control

Incluye las seales de control generadas por el microprocesador para acceder a los

espacios de direccionamiento (READ, WRITE, FETCH, IO/M, DMA_ACK, ...).

Puede incluir seales destinadas al microprocesador (READY, DMA_REQ, ...).

ARQUITECTURA DE BUSES (II)

BUS DE DIRECCIONES

BUS DE CONTROL

BUS DE DATOS (DATOS/INSTRUCCIONES)

SEALES DE SELECCIN

DE DISPOSITIVO

P

PUERTOS

DE

ENTRADA

PUERTOS

DE

SALIDA

MEMORIA

DE

PROGRAMA

MEMORIA

DE

DATOS

SUBSISTEMA DE

DECODIFICACIN

SELECCIN

El subsistema de decodificacin/seleccin se encarga de generar las seales de seleccin

de cada dispositivo (chip select) de acuerdo a su capacidad, ubicacin en el espacio de

direccionamiento, tipo de operaciones admitidas, tiempo de acceso, etc.

Generalmente es un circuito combinacional, pero puede ser secuencial si existen tiempos

de acceso equivalentes a varios ciclos de reloj del microprocesador.

ARQUITECTURA DE BUSES (III)

BUS DE DIRECCIONES ALTAS

BUS DE CONTROL

BUS MULTIPLEXADO DE DIRECCIONES BAJAS Y DATOS

SEALES DE SELECCIN

DE DISPOSITIVO

BUS DE DIRECCIONES (COMPLETO)

P

DISPOSITIVOS

CON BUSES

SEPARADOS

DEMULTIPLEXOR

DE DIRECCIONES

Y DATOS (LATCH)

SUBSISTEMA DE

DECODIFICACIN

SELECCIN

DISPOSITIVOS

CON BUSES

MULTIPLEXADOS

BUS DE DIRECCIONES BAJAS

Existen algunos microprocesadores que multiplexan en el tiempo direcciones bajas y

datos por un mismo bus, a fin de reducir el nmero de pins del microprocesador.

Estos sistemas presentan una seal que permite separar, en caso necesario, los buses de

datos y direcciones bajas (ALE en los microprocesadores de Intel).

Existen circuitos integrados de memoria y/o puertos de entrada/salida compatibles con el

bus multiplexado de direcciones bajas y datos.

JUEGO DE INSTRUCCIONES (I)

Es el conjunto de operaciones bsicas que un microprocesador es capaz de

realizar.

Cada operacin bsica corresponde a una instruccin y, por consiguiente, a un

cdigo binario (combinacin de 1s y 0s) almacenado en la memoria de

programa.

El juego de instrucciones es propio de cada microprocesador y depende, en

buena parte, de su arquitectura interna (operadores y registros de la unidad de

proceso), siendo un reflejo de esta.

La potencia de un microprocesador se mide, en buena parte, por su juego de

instrucciones.

La codificacin del juego de instrucciones es propia de cada microprocesador.

JUEGO DE INSTRUCCIONES (II)

Una instruccin puede ocupar una o varias posiciones de memoria.

La primera de estas posiciones de memoria contiene el campo de operacin,

cuyo contenido binario identifica la operacin a realizar y el nmero de

posiciones de memoria adicionales de la instruccin. Tambin puede contener

otros campos con informacin sobre los operandos a utilizar en la operacin.

Las restantes posiciones de memoria, caso de existir, contienen informacin

adicional sobre los operandos a utilizar en la operacin.

Se llama operando fuente al que se utiliza como dato de entrada en una

operacin.

Se llama operando destino al que se utiliza como destinatario del resultado de

una operacin.

Normalmente slo hay un operando destino.

El operando destino suele ser uno de los operandos fuente en las instrucciones en

las que interviene ms de un operando fuente.

JUEGO DE INSTRUCCIONES (III)

Instrucciones de movimiento de datos.

- Copia R1 (operando fuente) en R0 (operando destino): (R0) (R1)

- Carga el valor 0 (operando fuente) en A (operando destino): (A) 0

Instrucciones aritmticas.

- Carga la diferencia entre R1 y R0 (operandos fuente) en R1 (operando destino): (R1) (R1) (R0)

- Incrementa A (operando fuente y destino) en una unidad (operando fuente): (A) (A) + 1

Instrucciones lgicas.

- Carga la O-exclusiva de R2 y 25H (operandos fuente) en R2 (operando destino): (R2) (R2) 25H

- Complementa el bit de acarreo CY (operando fuente y destino): (CY) (CY)

Instrucciones de ruptura de secuencia.

- Salta a la posicin de memoria 27FEH: (PC) 27FEH

- Salta a la posicin de memoria ubicada 47H posiciones hacia delante: (PC) (PC) + 47H

Instrucciones mixtas.

- Decrementa A y salta a la posicin de memoria ubicada 79H posiciones hacia atrs si A pasa a ser 0

Instrucciones especiales

- Para el funcionamiento del microprocesador

MODOS DE DIRECCIONAMIENTO DE

LOS OPERANDOS (I)

Los operandos fuente y destino que intervienen en la operacin indicada por

una instruccin pueden especificarse de varias formas distintas.

Se llaman modos de direccionamiento de los operandos a las distintas formas

de interpretar la informacin contenida en la instruccin para determinar los

operandos que intervienen en ella.

Los modos de direccionamiento ofrecen:

Versatilidad en el manejo de estructuras de datos complejas.

Reducir el nmero de bits de los campos de operando.

La potencia de una mquina se mide, entre otras cosas, por la variedad de

modos de direccionamiento que admite.

MODOS DE DIRECCIONAMIENTO DE

LOS OPERANDOS (II)

Implcito: el operando se encuentra implcito en la operacin a realizar por el carcter

propio de dicha operacin o es el nico posible dada la arquitectura del microprocesador.

- La unidad en las operaciones de incrementar o decrementar: (A) (A) + 1

- El 0 en las operaciones de puesta a 0 (clear) de un registro: (R0) 0

- El registro destino de las operaciones aritmticas y lgicas si es el nico posible: (A) (A) + 15H

Inmediato: el operando es una constante que se encuentra en las posiciones de memoria que

siguen al cdigo de la instruccin (slo aplicable a operandos fuente).

- El operando fuente usado en la carga del valor 25H en R0: (R0) 25H

- El operando fuente usado en la suma del valor 18H a A: (A) (A) + 18H

DIR+1

DIR "sumar # a A"

18H

INSTRUCCIN

MEMORIA DE PROGRAMA

A

25H 3DH

UNIDAD DE PROCESO

MODOS DE DIRECCIONAMIENTO DE

LOS OPERANDOS (III)

Directo a registro: el operando se encuentra o se guarda en un registro de la unidad de

proceso. Este modo de direccionamiento se caracteriza por un acceso muy rpido a los

datos y requerir pocos bits de codificacin, lo que permite su inclusin en la primera

posicin de la instruccin, junto al campo de operacin).

- El operando destino usado en el incremento de R1: (R1) (R1) + 1

- Los operandos usados en la carga de R2 con la suma de R1 y R2 : (R2) (R2) + (R1)

DIR "sumar R1 a R2"

INSTRUCCIN

R1

R2

13H

24H 37H

UNIDAD DE PROCESO

MEMORIA DE PROGRAMA

MODOS DE DIRECCIONAMIENTO DE

LOS OPERANDOS (IV)

Directo o absoluto: el operando es, se encuentra o se guarda en una direccin de la

memoria de datos, direccin que viene indicada en las posiciones de memoria que

siguen al cdigo de la instruccin. Una de sus utilizaciones es en instrucciones de

ruptura de secuencia. Normalmente se indican todos los bits de la direccin, pero

existen modos de direccionamiento particulares en los que basta con indicar slo parte

de ellos, los menos significativos, estando los dems fijos a un valor predeterminado

(directo corto) o determinado por el contenido de un registro (pgina).

- El operando fuente usado en la carga del contenido de la posicin 25H en R1: (R1) (25H)

- El operando destino usado en la carga del valor 35H en la posicin 74H: (74H) 35H

DIR+2

DIR+1

DIR

INSTRUCCIN

MEMORIA DE DATOS

74H

35H

"mover # memoria"

74H ??? 35H

MEMORIA DE PROGRAMA

MODOS DE DIRECCIONAMIENTO DE

LOS OPERANDOS (V)

Indirecto: el operando se encuentra o se guarda en una direccin de la memoria de datos,

direccin que es el contenido de un registro especial de la unidad de proceso, denominado

registro de base. Pueden existen varios registros de base, en cuyo caso debe indicarse de

cual se trata.

- El operando destino usado en el incremento de la posicin de memoria apuntada por el registro de

base RB1: ((RB1)) ((RB1)) + 1

DIR INSTRUCCIN

"incrementar @RB1"

MEMORIA DE PROGRAMA

RB1 137H

UNIDAD DE PROCESO

MEMORIA DE DATOS

137H 19H 1AH

MODOS DE DIRECCIONAMIENTO DE

LOS OPERANDOS (VI)

Indirecto postincremental: el operando se encuentra o se guarda en una direccin de la

memoria de datos, direccin que est memorizada en un registro de base. Posteriormente

la direccin memorizada en el registro de base se incrementa en el tamao del operando.

- El operando destino usado en el decremento de la posicin de memoria previamente apuntada

por el registro de base RB1: ((RB1)) ((RB1)) 1 ; (RB1) (RB1) + 1

DIR

INSTRUCCIN

"decrementar @+RB1

MEMORIA DE PROGRAMA

RB1 205H 206H

UNIDAD DE PROCESO

MEMORIA DE DATOS

205H 80H 7FH

MODOS DE DIRECCIONAMIENTO DE

LOS OPERANDOS (VII)

Indirecto predecremental: el operando se encuentra o se guarda en una direccin de la

memoria de datos, direccin que est memorizada en un registro de base. Previamente la

direccin memorizada en el registro de base se decrementa en el tamao del operando.

- El operando destino usado en la carga del valor 3FH en la posicin de memoria finalmente

apuntada por el registro de base RB0: (RB0) (RB0) 1 ; ((RB0)) 3FH

DIR+1

DIR

INSTRUCCIN

3FH

"mover # @RB0"

MEMORIA DE PROGRAMA

RB0 305H 304H

UNIDAD DE PROCESO

MEMORIA DE DATOS

304H ??? 3FH

MODOS DE DIRECCIONAMIENTO DE

LOS OPERANDOS (VIII)

Indirecto con desplazamiento: el operando se encuentra o se guarda en una direccin de

la memoria de datos, direccin que es la suma del contenido de un registro de base y de

un desplazamiento, indicado en las posiciones de memoria que siguen al cdigo de la

instruccin y expresado en complemento a 2.

- El operando destino usado en la puesta a 0 de la posicin de memoria apuntada por el registro de

base RB0 con un desplazamiento de +27H: ((RB0) + 27H) 0

DIR+1

DIR

INSTRUCCIN

+27H

"borrar @(RB0,+)"

MEMORIA DE PROGRAMA

RB0 534H

UNIDAD DE PROCESO

534H + 27H = 55BH

MEMORIA DE DATOS

55BH

??? 0

MODOS DE DIRECCIONAMIENTO DE

LOS OPERANDOS (IX)

Indirecto indexado: el operando se encuentra o se guarda en una direccin de la memoria

de datos, direccin que es la suma del contenido de un registro de base y del contenido de

otro registro especial de la unidad de proceso, denominado registro de ndice. Pueden

existen varios registros de ndice, en cuyo caso debe indicarse de cual se trata.

- El operando destino usado en la puesta a 0 de la posicin de memoria apuntada por los registros

de base RB0 e ndice RI1: ((RB0) + (RI1)) 0

DIR INSTRUCCIN "borrar @(RB0,RI1)"

MEMORIA DE PROGRAMA

RB0

RI1

117H

237H

UNIDAD DE PROCESO

117H + 237H = 34EH

MEMORIA DE DATOS

34EH ??? 0

MODOS DE DIRECCIONAMIENTO DE

LOS OPERANDOS (X)

Indirecto indexado con desplazamiento: el operando se encuentra o se guarda en una

direccin de la memoria de datos, direccin que es la suma del contenido de un registro

de base, del contenido de un registro de ndice y de un desplazamiento, indicado en las

posiciones de memoria que siguen al cdigo de la instruccin y expresado en

complemento a 2.

- El operando destino usado en la puesta a 0 de la posicin de memoria apuntada por los registros

de base RB1 e ndice RI1 con un desplazamiento de 15H: ((RB1) + (RI1) 15H) 0

RB1

RI1

356H

7EH

UNIDAD DE PROCESO

356H + 7EH 15H = 3AFH

MEMORIA DE DATOS

3AFH ??? 0

DIR+1

DIR

INSTRUCCIN

15H

"borrar @(RB1,RI1,+)"

MEMORIA DE PROGRAMA

MODOS DE DIRECCIONAMIENTO DE

LOS OPERANDOS (XI)

Relativo al contador de programa: el operando es, se encuentra o se guarda en una

direccin de la memoria de programa, direccin que es la suma del contenido del

contador de programa y de un desplazamiento, indicado en las posiciones de memoria

que siguen al cdigo de la instruccin y expresado en complemento a 2. Una de sus

utilizaciones es en instrucciones de ruptura de secuencia.

- El operando usado en un salto relativo con un desplazamiento de +79H: (PC) (PC) + 79H

PC 7FE0H 8059H

UNIDAD DE CONTROL

DIR+1

DIR

INSTRUCCIN

+79H

"salto relativo"

MEMORIA DE PROGRAMA

SUBRUTINAS

CDIGO

IDNTICO

MEMORIA DE PROGRAMA

SUBRUTINA

RETORNO DE LA

SUBRUTINA

LLAMADA A LA

SUBRUTINA

MEMORIA DE PROGRAMA

ENTRADA DE LA

SUBRUTINA

Para saber a que direccin de la memoria de programa se ha de retornar es necesario

que esta direccin se almacene en un sitio conocido en el momento de la llamada.

LA PILA O STACK (I)

Cuando existen llamadas a subrutinas encadenadas, se han de almacenar las sucesivas

direcciones de retorno de forma que la ltima que se ha almacenado sea la primera en

recuperarse. Para almacenar las direcciones de retorno se necesita una estructura LIFO

(last-in first-out), denominada stack o pila. Existen dos posibilidades:

Una pila dedicada en la unidad de control que admite slo un nmero limitado de

llamadas encadenadas (microcontroladores poco potentes).

Una pila montada sobre la memoria de datos, de tamao y ubicacin determinados

por el usuario y gestionada con la ayuda de un registro denominado puntero de pila,

stack pointer o SP (lo ms habitual).

SUBRUTINA 1

PROGRAMA PRINCIPAL

MEMORIA DE PROGRAMA

SUBRUTINA 3 SUBRUTINA 2

LA PILA O STACK (II)

Dependiendo del microprocesador, la pila puede crecer hacia direcciones bajas de

memoria o hacia direcciones altas de memoria (direcciones bajas en el ejemplo).

Dependiendo del microprocesador, el puntero de pila puede apuntar a la ltima

posicin llena o a la primera posicin vaca (primera posicin vaca en el ejemplo).

Una llamada a subrutina (CALL) aade a la pila (escribe) el valor del contador de

programa de la siguiente instruccin. El puntero de pila se actualiza en consonancia.

Un retorno de subrutina (RET) extrae de la pila (lee) el valor que ha de poner en el

contador de programa. El puntero de pila se actualiza en consonancia.

Existen instrucciones para aadir (PUSH) y para extraer (POP) informaciones de la

pila.

SP

PUSH

CALL

DIR+n

DIR

LLENA

PILA

SP

DIR+n

DIR

LLENA

PILA

SP

DIR+n

DIR

LLENA

PILA

POP

RET

INTERRUPCIONES (I)

Se llaman aplicaciones en tiempo real a aquellas aplicaciones caracterizadas por requerir

una respuesta muy rpida del sistema que las controla ante determinados eventos externos

detectables mediante seales de entrada apropiadas (por ejemplo, presin o temperatura

que excede un lmite prefijado).

La consulta peridica a alta frecuencia de estas seales de entrada (pooling) consume

mucho tiempo de CPU, por lo que es preferible incorporar un mecanismo especial al

microprocesador para solventar este problema (interrupciones).

Una interrupcin es una indicacin de un suceso acaecido en el hardware o en el software

de un microprocesador que provoca una ruptura de la secuencia de instrucciones que ste

realiza, de forma que el microprocesador pasa a realizar una rutina especial de tratamiento

de dicha indicacin (servicio de interrupcin), tras completar la cual se retorna al punto

del programa en que se produjo la ruptura.

SERVICIO DE INTERRUPCIN

PROGRAMA

MEMORIA DE PROGRAMA

INTERRUPCIN

INTERRUPCIONES (II)

La unidad de control consulta la existencia de interrupciones tras completar la ejecucin

de cada instruccin.

Ante la existencia de una interrupcin, el microprocesador inicia una ruptura de

secuencia similar a la de una llamada a subrutina: guarda la direccin de retorno en la

pila y carga en el contador de programa una direccin que corresponde al punto de

entrada del servicio de interrupcin asociado a dicha seal.

Dependiendo del microprocesador, la direccin cargada en el contador de programa:

O es una direccin preestablecida asociada a la interrupcin y que se genera automticamente.

O es una direccin que se halla memorizada en una posicin preestablecida asociada a la

interrupcin (vector de interrupcin) y que se genera automticamente. Esta alternativa es la

ms corriente en los microprocesadores potentes.

Acabado el servicio de interrupcin, se retorna al programa interrumpido de forma

similar a como se retorna de una subrutina: se recupera la direccin de retorno de la pila.

Debe garantizarse la integridad de los datos utilizados por el programa interrumpido.

Para ello es fundamental, al comenzar un servicio de interrupcin, preservar los valores

de los registros de la unidad de proceso que van a ser utilizados en l y recuperar estos

valores al acabarlo. El lugar idneo para preservar estos valores es la pila. Algunos

microprocesadores preservan y recuperan estos valores de forma automtica.

ACCESO DIRECTO A MEMORIA

Slo algunos microprocesadores (los muy potentes) permiten accesos directos a memoria.

Los dispositivos de entrada/salida capaces de realizar accesos directos a memoria

disponen de un procesador especializado, llamado controlador de DMA, capaz de realizar

accesos a memoria de forma similar a como lo hace el microprocesador.

En los accesos directos a memoria se utilizan los buses de direcciones, datos y control del

propio microprocesador.

El controlador de DMA conoce cuantos datos debe transferir y en que posiciones de

memoria se encuentran dichos datos (o a que posiciones de memoria se deben enviar).

El mecanismo de un acceso directo a memoria es el siguiente:

El controlador de DMA solicita al microprocesador permiso para utilizar los buses.

El microprocesador consulta esta peticin en cada ciclo de mquina autorizado.

Acabado el ciclo de mquina, el microprocesador libera sus buses (alta impedancia), indicando

dicha situacin al controlador de DMA.

El controlador de DMA se apropia de los buses y realiza la transferencia de datos entre memoria

y el dispositivo de entrada/salida.

Acabada la transferencia, el controlador de DMA libera los buses (alta impedancia), indicando

dicha situacin al microprocesador.

El microprocesador retoma el control de los buses y continua ejecutando ciclos de mquina.

DISPOSITIVOS DE ENTRADA/SALIDA O

PERIFRICOS (I)

Los dispositivos de entrada/salida, dispositivos perifricos o, simplemente, perifricos, son

aquellos dispositivos que permiten la interaccin de un computador con el mundo exterior.

Los dispositivos de entrada/salida no forman parte esencial del computador, pero estn

situados cerca de l.

La conexin de un dispositivo de entrada/salida a un computador se hace a travs de un

circuito electrnico que forma parte del subsistema de entrada/salida del computador y

que se denomina interfaz.

Desde el punto de vista de la CPU, un interfaz aparece como un conjunto de registros de

entrada/salida (en algunos microprocesadores, registros de funciones especiales SFR) a los

que se accede mediante los buses de direcciones, datos y control.

Algunos interfaces pueden generar interrupciones y/o accesos directos a memoria.

P

DATOS

C

DIRECCIN

CONTROL

INTERFAZ PERIFRICO

REGISTROS

DISPOSITIVOS DE ENTRADA/SALIDA O

PERIFRICOS (II)

Perifricos tpicos de un

ordenador personal (PC):

Teclado.

Ratn.

Escner.

Terminal (pantalla).

Impresora.

Altavoces.

Disco duro (HD).

Disco flexible (FD).

Lectora/grabadora de CDs.

Lectora/grabadora de DVDs.

Perifricos de comunicaciones

(UART, USB, mdem, red, ...).

Perifricos tpicos en una

aplicacin industrial:

Interruptores y pulsadores. (*)

Finales de carrera. (*)

Sensores de magnitudes analgicas.

Temporizadores.

LEDs, bombillas y siete-segmentos. (*)

Alarmas acsticas. (*)

Motores y electrovlvulas. (*)

Visualizadores de cristal lquido (LCD).

Impresoras.

Memorias E2PROM y Compact Flash.

Perifricos de comunicaciones (UART,

I2C, CAN, Firewire, Bluetooth, ...).

(*) Va puertos paralelos de entrada/salida.

DISPOSITIVOS DE ENTRADA/SALIDA O

PERIFRICOS (III)

Los registros que tpicamente existen en un interfaz son:

Registros de salida:

Registros de datos.

Registros de control o de configuracin (permiten establecer el modo de

funcionamiento del perifrico).

Registros de entrada:

Registros de datos.

Registros de estado (permiten conocer el estado de funcionamiento del

perifrico).

Registros de salida (son realimentaciones de los registros de entrada que

facilitan la lectura de su contenido).

COMUNICACIN DE DATOS ENTRE

SISTEMAS (I)

La comunicacin de datos de n bits entre sistemas puede ser:

En paralelo, mediante n lneas, una por bit (multiplexin en el espacio).

Permite mayor throughput (datos transmitidos por unidad de tiempo).

Requiere muchas seales de entrada/salida, tanto en el emisor como en el receptor.

Es cara, especialmente para distancias largas.

En serie, mediante una lnea por la que se envan los n bits una tras otro (multiplexin en

el tiempo).

Permite menor throughput.

Requiere una nica seal de entrada/salida para los datos, tanto en el emisor como en el receptor.

Es barata, especialmente para distancias largas.

Requiere de un pacto entre emisor y receptor para establecer la velocidad de transmisin, es

decir el nmero de bits transmitidos por unidad de tiempo (baud-rate).

Requiere que emisor y receptor dispongan de una seal de reloj similar que permita establecer el

tiempo de transmisin de los bits.

COMUNICACIN DE DATOS ENTRE

SISTEMAS (II)

La comunicacin de datos en serie entre sistemas

puede ser:

Sncrona, es decir, emisor y receptor presentan la

misma seal de reloj.

La seal de reloj se genera en uno de los sistemas,

normalmente el emisor, y se transmite al otro.

La seal de reloj puede transmitirse por una lnea

dedicada o por la misma lnea que los datos,

mezclada con ellos.

Se pueden transmitir paquetes con muchos bits de

datos seguidos.

Asncrona, es decir, emisor y receptor presentan

seales de reloj distintas.

Las seales de reloj han de ser similares (diferencia

pequea) para evitar errores de transmisin.

No se pueden transmitir muchos bits seguidos, al

acumularse los errores de tiempo de un bit.

EMISOR

DATOS

RECEPTOR

RELOJ

T

E

EMISOR

DATOS

+

RELOJ RECEPTOR

EMISOR

DATOS

RECEPTOR

T

R

T

E

T

E

COMUNICACIN ASNCRONA DE DATOS

START

(1 BIT)

DATO

1

STOP

(1 o 2 BITS)

PARIDAD

(1 BIT)

(OPCIONAL)

MSB LSB

0

DATOS

(8 BITS)

Los datos se encapsulan en paquetes con 5 a 9 bits de datos (8 habitualmente).

Los bits de datos se envan de menos significativo a ms significativo.

Los paquetes presentan delimitadores (1 bit de start y 1 o 2 bits de stop).

Opcionalmente se puede enviar un bit redundante para detectar errores de transmisin: el

bit de paridad (par o impar).

El bit de start se utiliza para sincronizar los relojes y determinar el momento en que se

muestrean los bits (a mitad de sus tiempos de bit).

Se utiliza para transmitir caracteres alfanumricos (ASCII) u otros datos de hasta 9 bits.

Existe una tolerancia de 4% entre los relojes de emisor y receptor.

Das könnte Ihnen auch gefallen

- Lectura 7. Del Ciclo de Vida Del Producto Al Ciclo de Vida Del ClienteDokument6 SeitenLectura 7. Del Ciclo de Vida Del Producto Al Ciclo de Vida Del ClienteCrashMichel100% (1)

- Salas Eléctricas WEGDokument8 SeitenSalas Eléctricas WEGCrashMichelNoch keine Bewertungen

- Tarea 7. Propuesta para La Gestión Del Talento en La Nueva EraDokument2 SeitenTarea 7. Propuesta para La Gestión Del Talento en La Nueva EraCrashMichelNoch keine Bewertungen

- 10 Principios Del Pacto MundialDokument2 Seiten10 Principios Del Pacto MundialCrashMichelNoch keine Bewertungen

- Capítulo 1 Formulas y AutorellenosDokument1 SeiteCapítulo 1 Formulas y AutorellenosCrashMichelNoch keine Bewertungen

- Catalogos 2TBDokument33 SeitenCatalogos 2TBCrashMichelNoch keine Bewertungen

- Tranformadores TM2000 PDFDokument27 SeitenTranformadores TM2000 PDFCrashMichelNoch keine Bewertungen

- El Populismo Amenaza Los Derechos HumanoDokument4 SeitenEl Populismo Amenaza Los Derechos HumanoCrashMichelNoch keine Bewertungen

- Catalogo 2taDokument48 SeitenCatalogo 2taCrashMichelNoch keine Bewertungen

- Catalogo 2teDokument16 SeitenCatalogo 2teCrashMichelNoch keine Bewertungen

- ASW07Dokument2 SeitenASW07CrashMichelNoch keine Bewertungen

- ATPNRDokument2 SeitenATPNRCrashMichelNoch keine Bewertungen

- Fela02001 Catalogo de Productos Latinoamerica Industrial Variadores y Controles Nuevo PDFDokument36 SeitenFela02001 Catalogo de Productos Latinoamerica Industrial Variadores y Controles Nuevo PDFCrashMichelNoch keine Bewertungen

- Arrancadores Protecciones y Controles Industriales PDFDokument24 SeitenArrancadores Protecciones y Controles Industriales PDFCrashMichelNoch keine Bewertungen

- ASW08Dokument2 SeitenASW08CrashMichelNoch keine Bewertungen

- BCFIWDokument2 SeitenBCFIWCrashMichelNoch keine Bewertungen

- ASW06Dokument2 SeitenASW06CrashMichelNoch keine Bewertungen

- Servicio Autorizado Bosch - Skil - Dremel: Maquina: Pulidora Bosch Gws 24-230 Observaciones: SOLO TRAE LA TUERCADokument1 SeiteServicio Autorizado Bosch - Skil - Dremel: Maquina: Pulidora Bosch Gws 24-230 Observaciones: SOLO TRAE LA TUERCAmaria torresNoch keine Bewertungen

- Funcion de La HistoriaDokument4 SeitenFuncion de La HistoriagguktaeNoch keine Bewertungen

- Arbol de Causas y EfectosDokument4 SeitenArbol de Causas y EfectosKevin AcostaNoch keine Bewertungen

- Secuencia 4Dokument3 SeitenSecuencia 4Angel Infante100% (1)

- Guía de ActividadesDokument7 SeitenGuía de ActividadesJhoana PicoNoch keine Bewertungen

- UC2. Fórmulas Químicas y Su FormaciónDokument33 SeitenUC2. Fórmulas Químicas y Su Formaciónct0808847Noch keine Bewertungen

- Cuadro ComparativoDokument1 SeiteCuadro ComparativoOzkr EliazNoch keine Bewertungen

- Ejercicio de AutoevaluaciónDokument6 SeitenEjercicio de Autoevaluacióncarmen masabandaNoch keine Bewertungen

- Ejemplo de Dosificacion para Laboratorio - Sistema ConsolidDokument10 SeitenEjemplo de Dosificacion para Laboratorio - Sistema ConsolidJuan SanchezNoch keine Bewertungen

- Taller de EstudioDokument3 SeitenTaller de EstudioLizethAlejandraGomezOteroNoch keine Bewertungen

- 3 y Nos Quedamos FriosDokument9 Seiten3 y Nos Quedamos FriosAna Paula HernandezNoch keine Bewertungen

- Tablas 1Dokument78 SeitenTablas 1BrunoSouza1991Noch keine Bewertungen

- Diapositiva EvaluacionDokument229 SeitenDiapositiva EvaluacionMarlon MaridueñaNoch keine Bewertungen

- Fabricación de JabonesDokument13 SeitenFabricación de JabonesRAFAEL TORTOSANoch keine Bewertungen

- TP5 Termoquimica Pedro de ReinDokument5 SeitenTP5 Termoquimica Pedro de Reinpedro dereinNoch keine Bewertungen

- Mejora de ProcesosDokument37 SeitenMejora de ProcesosLIMANoch keine Bewertungen

- Informe Final NeyverDokument19 SeitenInforme Final NeyverNeyver Vela PortocarreroNoch keine Bewertungen

- Formulario Variante de RedDokument2 SeitenFormulario Variante de RedAlexander RivasNoch keine Bewertungen

- Curriculum VitaeDokument1 SeiteCurriculum VitaeodocapitalrrhhNoch keine Bewertungen

- Modulo 4° - 2 Bimestre PDFDokument67 SeitenModulo 4° - 2 Bimestre PDFgoyber perez cotrinaNoch keine Bewertungen

- Sesion 7 CalidadDokument35 SeitenSesion 7 CalidadPedro Cesar Silva MarquezNoch keine Bewertungen

- Cuestionario de Procesos de ManufacturaDokument13 SeitenCuestionario de Procesos de Manufacturaapolo45689% (19)

- Apunte para Examen TeoricoDokument126 SeitenApunte para Examen TeoricoTomás SuárezNoch keine Bewertungen

- Evaluacion Und 3Dokument6 SeitenEvaluacion Und 3Fredy galarza olayaNoch keine Bewertungen

- Resumen Malhotra 4Dokument9 SeitenResumen Malhotra 4PalomaNavajasNoch keine Bewertungen

- Taller de BenchmarkingDokument4 SeitenTaller de BenchmarkingMelissa Buelvas AndradeNoch keine Bewertungen

- WEG Rele Programable Clic 02 Controlador Programable TP 03 y Interfaz Hombre Maquina 50029483 Catalogo Espanol PDFDokument16 SeitenWEG Rele Programable Clic 02 Controlador Programable TP 03 y Interfaz Hombre Maquina 50029483 Catalogo Espanol PDFNicolás Alday LeivaNoch keine Bewertungen

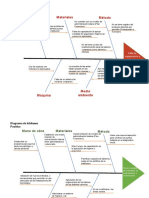

- Diagramas IsickawuaDokument2 SeitenDiagramas IsickawuaGianni VázquezNoch keine Bewertungen

- Biofiltros Basados en La Acción de HongosDokument22 SeitenBiofiltros Basados en La Acción de HongosMonserrat MoralesNoch keine Bewertungen

- Laboratorio BibliotecaDokument3 SeitenLaboratorio Bibliotecavnc hfzNoch keine Bewertungen