Beruflich Dokumente

Kultur Dokumente

005 Mips 2013

Hochgeladen von

VerónicaTaftOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

005 Mips 2013

Hochgeladen von

VerónicaTaftCopyright:

Verfügbare Formate

Captulo 4:

SEGMENTACIN EN LA EJECUCIN DE INSTRUCCIONES

Escuela Politcnica Superior de la U.A.M.

Arquitectura e Ingeniera de Computadores

ndice

SEGMENTACIN EN LA EJECUCIN DE INSTRUCCIONES

2.1.- Fundamentos de diseo de un procesador

2.1.1.- El repertorio de instrucciones

2.1.2.- Ciclo nico y multiciclo

2.1.3.- Ruta de datos y control

2.2.- La tcnica de la segmentacin

2.2.1.- Funcionamiento ideal.

2.2.2.- Conceptos asociados: latencia y rendimiento (throughput)

2.3.- Diseo de un procesador segmentado (pipeline)

2.4.- Limitaciones del cauce de instrucciones segmentado

2.4.1.- Causas que producen prdidas de rendimiento por detencin del pipeline

2.4.1.1.- Conflictos por limitaciones estructurales

2.4.1.2.- Conflictos por riesgos de control

2.4.1.3.- Conflictos por dependencia de datos

2.4.2.- Tcnicas para evitar detenciones

2.4.2.1.- Adelantamiento de datos

2.4.2.2.- Prediccin de saltos

Arquitectura e Ingeniera de Computadores

Introduccin

Para el estudio de procesadores segmentados se

parte de un sencillo procesador RISC

denominado MIPS (Microprocessor without

Interlocked Pipeline Stages)

Procesador de 32 bits (datos, memoria)

32 registros de propsito general

Memoria de datos y cdigo separadas

Arquitectura e Ingeniera de Computadores

Caractersticas de las arquitecturas RISC

Juego de instrucciones reducido.

Acceso a memoria limitado a instrucciones de

carga/almacenamiento.

Muchos registros de propsito general.

Pocos modos de direccionamiento (inmediato,

directo, indexado).

Formato de instruccin homogneo (misma

longitud y distribucin de campos).

Todas las instrucciones se ejecutan en un ciclo de

reloj.

Arquitectura e Ingeniera de Computadores

El juego de instrucciones

Los diseadores de computadoras tienen como

objetivo encontrar un juego de instrucciones tal

que

Sea sencillo construir el hardware que

materialice ese juego de instrucciones y

El compilador sea sencillo y eficiente,

Maximizando el rendimiento de la

computadora y

Minimizando su consumo de energa.

Arquitectura e Ingeniera de Computadores

Procesadores MIPS

Los procesadores MIPS tienen un juego de

instrucciones elegante desarrollado desde la

dcada de 1980.

Otro ejemplo de juego de instrucciones es el de

los procesadores ARM.

Similar a las instrucciones MIPS.

Vendi ms de 3.000 millones de chips para

aplicaciones embebidas en 2008.

Un juego de instrucciones diferente es el Intel x86.

Se vendieron 330 millones de PCs Intel en

2008.

Arquitectura e Ingeniera de Computadores

Procesadores MIPS

En 1981, un equipo liderado por John L.

Hennessy en la Univ. de Stanford comenz a

trabajar en el primer procesador MIPS.

A principios de los '90 MIPS Technologies

comenz a otorgar licencias de sus diseos a

terceros, de ah proceden ms de la mitad de

los ingresos de MIPS actualmente.

Los procesadores MIPS se utilizan por ejemplo

en dispositivos para Windows CE; routers

Cisco; y videoconsolas como la Nintendo 64 o

las Sony PlayStation, PlayStation 2, etc.

Debido a que su conjunto de instrucciones tan

claro, los cursos sobre arquitectura de

computadores en universidades a menudo se

basan en la arquitectura MIPS.

R10000 (Toshiba

TC86R10000-200,1996)

Emotion Engine (Sony, 2000)

MIPS-IV (R4000) de 128 Bits

Arquitectura e Ingeniera de Computadores

Procesador MIPS

32 registros de uso general: $0 .. $31 (excepto $0

siempre igual a 0).

2

30

palabras de memoria (32 bits c/u).

Instrucciones de 1 palabra (32 bits) de longitud.

Acceso a memoria limitado a 2 tipos de

instrucciones:

LOAD (carga una palabra de memoria en

registro)

STORE (almacena un registro en memoria)

Arquitectura e Ingeniera de Computadores

Conjunto de instrucciones MIPS (32 bits). Tres formatos de instrucciones:

op Direccin destino (Target Address)

0 26 31

6 bits 26 bits

op rs rt rd shamt funct

0 6 11 16 21 26 31

6 bits 6 bits 5 bits 5 bits 5 bits 5 bits

op rs rt inmediato

0 16 21 26 31

6 bits 16 bits 5 bits 5 bits

Tipo-R

Tipo-I

Tipo-J

El repertorio de instrucciones: caractersticas y tipos

Campos de cada instruccin:

op: Cdigo de operacin de la instruccin

rs, rt, rd: identificador de los registros fuente y destino

shamt: desplazamiento deseado

funct: seleccin de la variante de funcin asociada

inmediato: dato inmediato en 16 bits

Direccin destino

Arquitectura e Ingeniera de Computadores

El repertorio de instrucciones: Tipo-R

Ejemplos: ADD y SUB

add rd, rs, rt # rd=rs+rt

sub rd, rs, rt # rd=rs-rt

op rs rt rd shamt funct

0 6 11 16 21 26 31

6 bits 6 bits 5 bits 5 bits 5 bits 5 bits

Ejemplos: Cdigo C

f = (g + h) (i + j);

Si las variables f, g, h, i, j estn en los registros

$s0 a $s4 el compilador puede generar:

add $t0, $s1, $s2

add $t1, $s3, $s4

sub $s0, $t0, $t1

Arquitectura e Ingeniera de Computadores

Convencin para el banco de registros MIPS

Nombre Nmero Uso Se preserva en

call?

$zero 0 Constante cero -

$at 1 Reservado assembler No

$v0-$v1 2-3 Resultados de expresiones No

$a0-$a3 4-7 Argumentos No

$t0-$t7 8-15 Temporarios No

$s0-$s7 16-23 Saved Si

$t8-$t9 24-25 Temporarios No

$k0-$k1 26-27 Reservados SO No

$gp 28 Puntero global Si

$sp 29 Puntero pila Si

$fp 30 Puntero frame Si

$ra 31 Dir retorno sub-rutina Si

Arquitectura e Ingeniera de Computadores

El repertorio de instrucciones: Tipo-I

ADD inmediato

addi rt, rs, inm # rt=rs+inm

LOAD y STORE word

lw rt, rs, inm # rt=mem[rs+inm]

sw rt, rs, inm # mem[rs+inm]=rt

SALTOS

beq rs, rt, inm # si rs=rt,

# entonces PC=PC+4+inm*4

# el lenguaje ensamblador admite etiquetas y calcula inm

0

op rs rt inmediato

16 21 26 31

6 bits 16 bits 5 bits 5 bits

Arquitectura e Ingeniera de Computadores

El repertorio de instrucciones: Ejemplo

Ejemplos: Cdigo C

if (i == j) f = (g + h); else f = g h;

Si las variables f, g, h, i, j estn en los registros $s0 a $s4 el compilador puede

generar:

bne $s3, $s4, CasoElse

add $s0, $s1, $s2 # si i==j

j Exit # salto incondicional

CasoElse: sub $s0, $s1, $s2

Exit:

Arquitectura e Ingeniera de Computadores

El repertorio de instrucciones: Ejemplo

Ejemplos: Cdigo C

while (save[i] == k) i+=1;

Si las variables i y k estn en los registros $s3 y $s5 y el registro base del

arreglo save esta en $s6, el compilador puede generar:

Loop: sll $t1, $s3, 2 # sll con 2 equivale a multip x4

add $t1, $t1, $s6 # calcula dir de save[i]

lw $t0, 0($t1) # carga save[i]

bne $t0, $s5, Exit

addi $s3, $s3, 1 # i+=1

j Loop # salto incondicional

Exit:

Arquitectura e Ingeniera de Computadores

Modos de direccionamiento MIPS

El operando es una cte dentro

de la instruccin:

lui $s0, 61

El operando es un registro:

ejemplos 1, 3 y 4.

La dir del operando es la

suma de un reg y una cte en

la instrucin:

lw $t0, 8($t1)

La dir de salto es la suma del

PC mas una cte. en la instr.:

beq $s0, $s1, L1

La dir de salto es la concat.

de los 4 bits ms altos del PC

con la cte de 26 bits en la

instruccin: jal printf

Arquitectura e Ingeniera de Computadores

Instruccin add rd, rs, rt

Descripcin de la ejecucin (RTL)

IR Mem[PC] Carga de la instruccin desde memoria

R[rd] R[rs] + R[rt] Realiza la operacin (SUMAR)

PC PC + 4 Calcula la direccin de la siguiente

instruccin

op rs rt rd shamt funct

0 6 11 16 21 26 31

6 bits 6 bits 5 bits 5 bits 5 bits 5 bits

Ejemplo ejecucin RTL de una instruccin

Arquitectura e Ingeniera de Computadores

Descripcin RTL (Register Transfer Level) de las instrucciones

a. Fase inicial: carga desde Memoria (Fetch)

IR <= MEM[ PC ] ; IR = op & rs & rt & rd & shamt & funct

; IR = op & rs & rt & Imm16

; IR = op & Inm26

b. Transferencia entre Registros (ejemplos: Instrucc y transf entre registros)

ADD R[rd] <= R[rs] + R[rt]; PC <= PC + 4

ADDI R[rt] <= R[rs] + Ext_signo(Inm); PC <= PC + 4

LOAD R[rt] <= MEM[ R[rs] + Ext_signo(Inm)]; PC <= PC + 4

STORE MEM[ R[rs] + Ext_signo(Inm) ] <= R[rt]; PC <= PC + 4

BEQ if ( R[rs] == R[rt] ) then PC <= PC + 4 + (Ext_signo(Inm) & 00)

else PC <= PC + 4

Descripcin RTL del procesador MIPS

Arquitectura e Ingeniera de Computadores

1. Analizar el conjunto de instrucciones => requisitos para la ruta de datos

(datapath).

El significado de cada instruccin viene dado por su funcionamiento a

nivel de transferencia de registros (RTL).

El datapath debe incluir elementos de almacenamiento para los

registros accesibles en el modelo de programacin del procesador.

El datapath debe soportar todas las transferencias entre registros

definidas en el conjunto de instrucciones.

2. Seleccin de los componentes y de la metodologa de reloj.

3. Implementacin del datapath cumpliendo los requisitos.

4. Anlisis de cada instruccin para determinar el mecanismo de control que

efecte la transferencia entre registros.

5. Implementacin de la lgica de control.

Generalidades para el diseo de un procesador

Arquitectura e Ingeniera de Computadores

Unidades funcionales necesarias para las instrucciones

Para qu son necesarias?

Memoria de instrucciones

Memoria de

Instrucciones

Direccin

de lectura

Instruccin

Memoria de datos

MemRea d

MemWri t e

Memoria de

Datos

Direccin

Dato

Entrada

Dato Salida

Contador

de Programa

Sumador

PC

S

u

m

a

d

o

r

ALU

A LU op.

3

Cero

Resultado

ALU

Oper 1

Oper 2

Extensin de Signo

16 32

Exten.

Signo

Banco de Registros

Dato Entrada

Reg. destino

Reg. fuente 1

Registros

Reg. fuente 2

Dato Salida 1

Dato Salida 2

Nmero

De

Registro

Datos

Datos

5

5

5

x 4

Diseo del procesador: elementos bsicos

Arquitectura e Ingeniera de Computadores

La metodologa de sincronizacin indica cundo pueden leerse y escribirse las

diferentes seales.

En este procesador (MIPS) los ciclos de reloj comienzan en flanco de subida

Diseo del procesador: sincronizacin

Elemento

de memoria

Elemento

de memoria

Elemento

Combinacional

Flanco de subida

(Rising edge)

Flanco de bajada

(Falling edge)

Periodo del reloj (Clock period)

Arquitectura e Ingeniera de Computadores

Conexiones en la ruta de datos (Datapath)

Operaciones entre registros, Tipo-R (ADD, SUB, OR, AND, etc)

Conexin de los elementos:

Uso de multiplexores.

Seales de control.

Captura de la siguiente instruc.

Incremento de PC.

Instrucciones de la ALU entre

registros.

Dato Entrada

Reg. destino

Reg. fuente 1

16 32

4

A LU op.

3

RegW rit e

MemRead

MemWri t e

PCSrc

AL USrc

Mem2 Reg

Cero

Memoria de

Instrucciones

Direccin

de lectura

Instruccin

PC

Registros

Reg. fuente 2

Dato Salida 1

Dato Salida 2

M

u

x

M

u

x

Memoria de

Datos

Direccin

Dato Entrada

Dato Salida

M

u

x

Exten.

Signo

Despl.

<< 2

S

u

m

a

d

o

r

Sumador

Resultado

Resultado

ALU

Arquitectura e Ingeniera de Computadores

Dato Entrada

Reg. destino

Reg. fuente 1

Conexin de los elementos:

Uso de multiplexores.

Seales de control.

Captura de la siguiente instruc.

Incremento de PC.

Instrucciones LOAD/STORE.

16 32

4

A LU op.

3

RegW rit e

MemRead

MemWri t e

PCSrc

AL USrc

Mem2 Reg

Cero

Memoria de

Instrucciones

Direccin

de lectura

Instruccin

PC

Registros

Reg. fuente 2

Dato Salida 1

Dato Salida 2

M

u

x

M

u

x

Memoria de

Datos

Direccin

Dato Entrada

Dato Salida

M

u

x

Exten.

Signo

Despl.

<< 2

S

u

m

a

d

o

r

Sumador

Resultado

Resultado

ALU

Conexiones en la ruta de datos (Datapath)

Operaciones de carga y almacenamiento, Tipo-I (Load / Store)

Arquitectura e Ingeniera de Computadores

Exten.

Signo

Dato Entrada

Reg. destino

Reg. fuente 1

Conexiones en la ruta de datos (Datapath)

Operaciones de salto condicional (Beq)

Conexin de los elementos:

Uso de multiplexores.

Seales de control.

Captura de la siguiente

instruccin o del destino de

salto =>Incremento de PC.

Instrucciones de Salto.

16 32

4

A LU op.

3

RegW rit e

MemRead

MemWri t e

PCSrc

AL USrc

Mem2 Reg

Cero

Memoria de

Instrucciones

Direccin

de lectura

Instruccin

PC

Registros

Reg. fuente 2

Dato Salida 1

Dato Salida 2

M

u

x

M

u

x

Memoria de

Datos

Direccin

Dato Entrada

Dato Salida

M

u

x

Despl.

<< 2

S

u

m

a

d

o

r

Sumador

Resultado

Resultado

ALU

Arquitectura e Ingeniera de Computadores

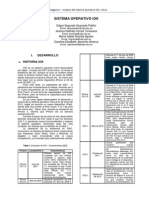

Ruta de Datos con

Control Uniciclo

Instruccin RegDest

FuenteALU

MemaReg EscrReg LeerMem EscrMen SaltoCond

ALUOp1 ALUOp0

Reg a Reg 1 0 0 1 0 0 0 1 0

LOAD

0 1 1 1 1 0 0 0 0

STORE X 1 X 0 0 1 0 0 0

BEQ

X 0 X 0 0 0 1 0 1

Control:

Bloque combinacional que

con 6 bits de la instruccin

(bits 31:26) genera las 9

seales de control

Arquitectura e Ingeniera de Computadores

Cmo agregar Jumps?

Jump usa direccionamiento pseudo-directo

El nuevo valor del PC se forma concatenando

Los 4 bits ms altos del PC

El operando de 26 bits

00

Se necesita alguna nueva seal de control?

2 address

31:26 25:0

Jump

Arquitectura e Ingeniera de Computadores

Ruta de Datos agregando Jumps

Arquitectura e Ingeniera de Computadores

Diagrama de tiempo de operacin Reg-Reg

32

Resultado

Clk

busW

32

32

busA

32

busB

Rw Ra Rb

32 Reg.

de 32-bit

ALU

ALUctr

RegWr

5 5 5

Rs Rt Rd

Clk

PC

Rs, Rt, Rd,

Op, Func

Clk-to-Q

ALUctr

Tiempo de acceso a la Memoria de Instrucciones

Old Value New Value

RegWr Old Value New Value

Retardo debido a la lgica de control

Bus A, B

Tiempo de acceso a Registros

Old

Value

New Value

busW

Retardo de ALU

Old Value New Value

Old Value New Value

New Value

Old Value

Escritura en

el registro

Arquitectura e Ingeniera de Computadores

Desventajas del diseo uniciclo (CPI=1)

Tiempo de ciclo muy largo (el peor de todos).

Casi todas las instrucciones utilizan, sin necesidad, tanto

tiempo como la instruccin ms lenta.

Se viola el principio de diseo: Hacer que el caso comn sea

rpido

PC Inst Memory mux ALU Data Mem mux

PC Reg File Inst Memory mux ALU mux

PC Inst Memory mux ALU Data Mem

PC Inst Memory cmp mux

Reg File

Reg File

Reg File

Arithmetic & Logical

Load

Store

Branch

Camino crtico

setup

setup

Arquitectura e Ingeniera de Computadores

Desventaja en la ejecucin uniciclo: ejemplo

Tiempos hipotticos para ejecutar cada instruccin

Sea un programa que utiliza 24% de cargas, 12% de almacenamientos,

44% de operaciones entre registros en la ALU, 18% de saltos

condicionales y 2 % de saltos incondicionales

Si fuese simple (NO LO ES) tener un reloj variable

Cul es tiempo medio de ciclo?

Cul sera la aceleracin respecto de una ejecucin uniciclo?

Clase de

Instruccin

Mem

instr.

Lect de

Reg

Operac.

ALU

Mem de

datos

Escrit

en Reg

Total

Formato R 2 1 2 0 1 6 ns

Load (LW) 2 1 2 2 1 8 ns

Store (SW) 2 1 2 2 7 ns

Salto (BEQ) 2 1 2 5 ns

Jump 2 2 ns

Arquitectura e Ingeniera de Computadores

Las instrucciones pueden tardar diferente nmero de ciclos.

Un datapath con ligeras modificaciones:

Dividir las instrucciones en pasos, cada paso tarda un ciclo.

Balancear la cantidad de trabajo a realizar en un paso.

En cada ciclo slo se utiliza una unidad funcional (se reduce

el nmero de U.F.)

Al final del ciclo

Almacenar los valores para su uso en posteriores pasos.

Aadir registros internos adicionales.

Ejecucin multiciclo

Arquitectura e Ingeniera de Computadores

Cambios para una aproximacin multiciclo

Arquitectura e Ingeniera de Computadores

Ejecucin en cinco pasos (5 ciclos)

1. Carga la instruccin (todas igual)

La ALU actualiza el contador de programa:

Todas: IR = Memoria[PC];

PC = PC + 4;

2. Decodificacin y lectura de operandos (todas igual)

Todava se sigue el mismo cauce para cualquier instruccin porque se estn

decodificando.

Lee registros rs y rt por si son necesarios

Calcula la direccin de salto en la ALU por si fuera necesaria (branch)

Todas: A = Reg[IR[25-21];

B = Reg[IR[20-16];

SalidaALU = PC + (extension_signo(IR[15-0]<<2);

Arquitectura e Ingeniera de Computadores

Ejecucin en cinco pasos (5 ciclos)

3. Ejecucin. Calculo de la direccin de memoria. Finalizacin del

salto.

La ALU, dependiendo del tipo de instruccin, realiza una operacin u otra.

Referencia a memoria: SalidaALU = A + extension_signo(IR[15-0]);

Operacin entre registros: SalidaALU = A op B;

Saltos: if (A==B) PC = SalidaALU;

4. Acceso a memoria o final instruccin tipo R.

Acceso a memoria en Loads y Stores.

Load: MDR = Memoria[SalidaALU];

Store: Memoria[SalidaALU] = B;

Escritura del registro destino en instrucciones entre registros.

Operacin entre registros: Reg[IR[15-11]] = SalidaALU;

(La escritura tiene lugar en el flanco al final del ciclo)

Arquitectura e Ingeniera de Computadores

5. Escritura del valor ledo de memoria en el registro destino

(Write-back).

Load: Reg[IR[20-16]]= MDR;

Ejecucin en cinco pasos (5 ciclos)

UNA INSTRUCCIN TARDA DE 3 A 5 CICLOS

Arquitectura e Ingeniera de Computadores

Control multiciclo: resumen de etapas

Nombre de la

etapa

Tipo R acceso a memoria Saltos

condicionales

Saltos

incondic(jump)

Carga Instrucciones

IR = Memoria[PC]

PC = PC + 4

Decodific de instrucc /

carga Reg

A = Reg [IR[25-21]]

B = Reg [IR[20-16]]

SalidaALU = PC + (extension-signo (IR[15-0] << 2)

Ejecucin, clculo de

direcc y fin de saltos

condicionales

SalidaAlu = A op B

SalidaALU = A +

(extension-signo (IR[15-0])

si (A = B) entonces

PC = SalidaALU

PC = PC[31-28] ||

(IR[25-0] << 2)

Acc. a MEM y Fin de

instrucc tipo R

Reg [IR[15-11]] =

SalidaALU

Load: MDR =

Memoria[SalidaALU] Store:

Memoria[SalidaALU] = B

Fin lectura MEM Load: Reg [IR[20-16]] = MDR

Arquitectura e Ingeniera de Computadores

Control Multiciclo

FSM de control

Para control multiciclo

I n s t r u c t i o n d e c o d e /

r e g i s t e r f e t c h

l e t io n

n c h

e t i o n x e c u t i o n

M e m o

a c c e s

M e m o r y

a c c e s s R - t y p e c o

W r i t e -

4

7 5 3

S t a r t

CAPTURA INSTRUCCION

ACCESO A

MEMORIA

DECODIFICA INSTRUCCIN

CAPTURA DE OPERANDOS

ESCRIBE EN REGISTRO

FIN INSTR.

JUMP

FIN INSTR. BEQ

EJECUCION

M e m o r y a d d r e s s

c o m p u t a t i o n

CALCULO

DIRECCION EFECTIVA

ACCESO A

MEMORIA

ESCRIBE EN REGISTRO

LeerMen

SelALUA = 0

IoD = 0

EscrIR

SelALUB = 01

ALUOp = 00

EscrPC

FuentePC = 00

SelALUA = 0

SelALUB = 11

ALUOp = 00

SelALUA = 1

SelALUB = 10

ALUOp = 00

SelALUA = 1

SelALUB = 00

ALUOp = 10

SelALUA = 1

SelALUB = 00

ALUOp = 01

EscrPCCond

FuentePC =01

EscrPC

FuentePC = 10

LeerMen

IoD =1

EscrMenn

IoD =1

RegDest = 1

EscrReg

MenaReg = 0

RegDest = 0

EscrReg

MenaReg = 1

(

O

p

=

)

(

O

p

=

L

W

)

2 6

9

8

1

0

Arquitectura e Ingeniera de Computadores

Segmentacin: Perspectiva General

Tcnica utilizada para optimizar el tiempo de ejecucin de procesos que se

realizan mediante la repeticin de una secuencia de pasos bsicos.

Permite la ejecucin de procesos concurrentemente.

Fundamento: Separar el proceso en etapas y ejecutar cada etapa en un

recurso independiente.

Objetivo: Mejorar la productividad, aumentando el nmero de

instrucciones ejecutadas por unidad de tiempo.

Funcionamiento: Cuando una etapa del proceso termina, el recurso

liberado puede empezar a ejecutar la misma etapa del siguiente proceso.

Se consigue la ejecucin de varios procesos en paralelo cada uno

en una etapa diferente. ILP: Instruction Level Paralelism

Las etapas son ejecutadas secuencialmente.

Arquitectura e Ingeniera de Computadores

Segmentacin: Perspectiva General (un ejemplo)

O

r

d

e

n

d

e

T

a

r

e

a

FUNCIONAMIENTO SECUENCIAL

Realizar 4 tareas

Lavado 30 MIN

Secado 40 MIN

Planchado 20 MIN

Tiempo empleado: 6 horas

Ejemplo de

Hennesy - Patterson

Arquitectura e Ingeniera de Computadores

Segmentacin: Perspectiva General (un ejemplo)

O

r

d

e

n

d

e

T

a

r

e

a

FUNCIONAMIENTO SEGMENTADO

Realizar 4 tareas

Lavado 30 MIN

Secado 40 MIN

Planchado 20 MIN

Tiempo empleado: 3,5 horas

Cada Tarea : 1,5 horas

Arquitectura e Ingeniera de Computadores

Segmentacin: Funcionamiento Ideal

T

p

T

s

T

p

T

s

SECUENCIALMENTE (1 unidad de proceso para todas las etapas)

T

p

es el tiempo de ejecucin de un proceso.

Se puede descomponer en s (s=3) etapas de duracin T

s

(T

p

=sT

s

)

T

t

= NT

p

= NsT

s

Con SEGMENTACIN (unidades independientes para cada etapa)

Si N >>s T

t

NT

s

T

t

= T

p

+ (N-1)T

s

= sT

s

+ (N-1)T

s

= (N+s-1)T

s

1 2 3 N

1

2

3

N-1

N

s=3

Ejecutar N procesos

Arquitectura e Ingeniera de Computadores

Segmentacin: Funcionamiento Ideal

Proceso segmentado vs Proceso secuencial

La segmentacin, aunque no mejora la latencia de un solo proceso,

mejora el rendimiento o productividad (throughput) de una tarea con

muchos procesos.

Varios procesos se ejecutan en paralelo.

VENTAJAS

RESTRICCIONES

La razn de segmentacin est limitada por la etapa ms lenta.

La aceleracin mxima posible = Nmero de etapas de segmentacin.

Etapas de segmentacin desequilibradas Reduccin de productividad.

Arquitectura e Ingeniera de Computadores

Segmentacin: Funcionamiento Ideal

Un procesador segmentado perfecto consigue ejecutar una

instruccin por ciclo.

La segmentacin ms evidente consta de tres etapas:

Obtener instruccin (Fetch)

Decodificar instruccin (Decode)

Ejecutar instruccin (Execute)

La frecuencia de funcionamiento es mayor si el nmero de etapas de

segmentacin se incrementa. Aunque:

La segmentacin fina es muy difcil

Cada nueva etapa aade el retardo de un registro

La independencia entre etapas es ms difcil de conseguir

Arquitectura e Ingeniera de Computadores

Segmentacin: Segmentacin de instrucciones.

EJEMPLO: Segmentacin de instrucciones con 5 etapas (MIPS)

Etapa IF Etapa ID Etapa EX Etapa MEM Etapa WB

IMem Reg ALU DMem Reg

Obtener instruccin

Acceso a la memoria

de instrucciones

Decodificar instruccin

Lectura de operandos,

carga de registros

Ejecutar instruccin

o bien

Calcular direccin

efectiva memoria.

Acceso a Memoria

o bien

Escribir en PC la

direccin de salto.

Escribir en un

registro el resultado

de la operacin.

Ejemplo para tres instrucciones tipo

Load Rx, 100(Ry)

Arquitectura e Ingeniera de Computadores

Segmentacin: Load vs Operacin entre registros

Las cuatro etapas en operaciones entre registros

Ifetch Reg/Dec Exec Mem Wr 1

er

load

Ifetch Reg/Dec Exec Mem Wr 2 load

Ifetch Reg/Dec Exec Mem Wr 3

er

load

Las cinco etapas de Load

Ciclo 1 Ciclo 2 Ciclo 3 Ciclo 4 Ciclo 5 Ciclo 6 Ciclo 7

Clock

Ifetch Reg/Dec Exec Wr R-type

Ifetch Reg/Dec Exec Wr R-type

Ifetch Reg/Dec Exec Wr R-type

Ciclo 1 Ciclo 2 Ciclo 3 Ciclo 4 Ciclo 5 Ciclo 6

Clock

Arquitectura e Ingeniera de Computadores

Existen conflictos estructurales

Hay dos instrucciones que intentan acceder a memoria al

tiempo.

Hay dos instrucciones que intentan escribir en el banco de

registros al mismo tiempo y slo existe un puerto de escritura.

Aparecen problemas

Segmentacin: Load vs Operacin entre registros

Ifetch Reg/Dec Exec Wr R-type

Ifetch Reg/Dec Exec Wr R-type

Ifetch Reg/Dec Exec Mem Wr Load

Ifetch Reg/Dec Exec Wr R-type

Ifetch Reg/Dec Exec Wr R-type

Ciclo 1 Ciclo 2 Ciclo 3 Ciclo 4 Ciclo 5 Ciclo 6 Ciclo 7

Clock

Ciclo 8

Arquitectura e Ingeniera de Computadores

Segmentacin: Consideraciones de diseo

Cada unidad funcional pueda usarse slo una vez por instruccin. Deben

aparecer dos unidades de memoria.

Cada unidad funcional se utiliza en la misma etapa para todas las

instrucciones:

Load usa el puerto de escritura en Registros durante su 5 etapa.

Las operaciones entre Registros usan el puerto de escritura en Registros

durante su 4 etapa

Ifetch Reg/Dec Exec Mem Wr Load

1 2 3 4 5

Ifetch Reg/Dec Exec Wr R-type

1 2 3 4

Soluciones posibles: paradas entre etapas, retraso de la escritura en

registro, ...

Arquitectura e Ingeniera de Computadores

Segmentacin: Consideraciones de diseo

Solucin1: Parar el cauce de instrucciones (Pipeline bubble)

Solucin 2: Retrasar la escritura en registro

Ifetch Reg/Dec Mem Wr R-type

Ifetch Reg/Dec Exec Mem Wr Load

Ifetch Reg/Dec Mem Wr R-type

Ifetch Reg/Dec Mem Wr R-type

Exec

Exec

Exec

Ifetch Reg/Dec Mem Wr R-type Exec

Clock

Ciclo 1 Ciclo 2 Ciclo 3 Ciclo 4 Ciclo 5 Ciclo 6 Ciclo 7 Ciclo 8 Ciclo 9

Ifetch Reg/Dec Exec Wr R-type

Ifetch Reg/Dec Exec

Ifetch Reg/Dec Exec Mem Wr Load

Ifetch Reg/Dec Exec Wr

R-type

Ifetch Reg/Dec Exec Wr

R-type

Pipeline

Bubble

Ifetch Reg/Dec Exec Wr

Clock

Ciclo 1 Ciclo 2 Ciclo 3 Ciclo 4 Ciclo 5 Ciclo 6 Ciclo 7 Ciclo 8 Ciclo 9

R-type

Es lo utilizado

en la prctica

Arquitectura e Ingeniera de Computadores

Resumen: Ciclo nico vs multiciclo vs segmentacin

Clk

Ciclo 1

Multiciclo

Ifetch Reg Exec Mem Wr

Ciclo 2 Ciclo 3 Ciclo 4 Ciclo 5 Ciclo 6 Ciclo 7 Ciclo 8 Ciclo 9Ciclo 10

Ifetch Reg Exec Mem

Load Store

Ifetch

R-type

Load Ifetch Reg Exec Mem Wr

Segmentacin

Ifetch Reg Exec Mem Wr

Store

Ifetch Reg Exec Mem Wr

R-type

Clk

Ciclo nico

Load

Store Sin uso

Ciclo 1

Ciclo 2

Arquitectura e Ingeniera de Computadores

Ruta de Datos de MIPS segmentado

WB

MEM

La informacin

de derecha a

izquierda va a

producir riesgos

Arquitectura e Ingeniera de Computadores

Segmentacin: Un diseo con 5 etapas

La base es el camino de datos de un ciclo.

Se aaden registros entre etapas.

Hay que analizar si todas las instrucciones funcionan.

Problema: LW R1,inm(R2)

Arquitectura e Ingeniera de Computadores

Etapa IF

Arquitectura e Ingeniera de Computadores

Etapa ID

Arquitectura e Ingeniera de Computadores

Etapa EX para Load

Arquitectura e Ingeniera de Computadores

Etapa MEM para Load

Arquitectura e Ingeniera de Computadores

Etapa WB para Load

Nmero de

registro

errado

Arquitectura e Ingeniera de Computadores

Correccin en la Ruta de Datos

La informacin del

registro de escritura

avanza con la

instruccin

Arquitectura e Ingeniera de Computadores

Segmentacin: Aadir el control

Tambin se deben

retrasar las

seales de control

para que la info de

control avance con

la instruccin

Arquitectura e Ingeniera de Computadores

Segmentacin: Aadir el control

Control

EX

M

WB

M

WB

WB

IF/ID ID/EX EX/MEM MEM/WB

Instruction

Todas las instrucciones tardan los mismos ciclos de reloj.

La secuenciacin de la instruccin est implcita en la estructura del pipeline.

No hay un control especial para la duracin de la instruccin (no hay FSM).

Toda la informacin de control se calcula durante la decodificacin, y se enva

hacia delante a travs de los registros de segmentacin.

Los valores de las lneas de control son los mismos que los calculados en el

control uniciclo.

Arquitectura e Ingeniera de Computadores

Las causas que pueden reducir el rendimiento en un procesador

segmentado de instrucciones son tres:

Riesgos estructurales:

Se intenta usar el mismo recurso de dos maneras diferentes al mismo tiempo.

El hardware impide una cierta combinacin de operaciones.

Riesgos por dependencia de datos:

Se intenta usar un dato antes de que est disponible.

El operando de una instruccin depende del resultado de otra instruccin

precedente que todava no se ha obtenido.

Riesgos de control:

Se intenta tomar una decisin antes de evaluarse la condicin.

Si se salta, las instrucciones posteriores no deben ejecutarse (o al menos,

no deben finalizar).

Segmentacin: Conflictos en funcionamiento real

Arquitectura e Ingeniera de Computadores

Cuando se detecta un riesgo, la solucin ms simple es parar la unidad de

segmentacin (stall the pipeline) hasta que desaparezca el riesgo.

Las instrucciones que preceden a la causante del riesgo pueden continuar.

La instruccin que causa el riesgo y siguientes no continan hasta que

desaparece el riesgo.

Todos estos riesgos se pueden solucionar?.....S

Cmo?...................................................Esperando

Se necesita que el control de la unidad de segmentacin (pipeline) sea

capaz de:

Detectar las causas de riesgo.

Decidir acciones que resuelvan el riesgo (por ejemplo, esperar).

Segmentacin: Conflictos en funcionamiento real

Arquitectura e Ingeniera de Computadores

Casos que se pueden presentar. Accesos simultneos a:

Memoria (si es Von Neuman, nica para datos e instrucciones).

Unidades funcionales.

Registros internos.

Tiempo (ciclos de reloj)

O

r

d

e

n

d

e

i

n

s

t

r

u

c

c

i

n

Segmentacin: Riesgos estructurales

Mem

Load

Instr 1

Instr 2

Instr 3

Instr 4

ALU

Mem Reg

Mem

Reg

ALU

Mem Reg Mem Reg

ALU

Mem Reg Mem Reg

ALU

Reg Mem Reg

ALU

Mem Reg Mem Reg

(La mitad izquierda coloreada indica escritura y la mitad derecha lectura)

Conflicto de lectura

en memoria

Arquitectura e Ingeniera de Computadores

Soluciones:

Introducir esperas.

Duplicar recursos o separar memoria de datos de la memoria de instrucciones

(Harvard en lugar de Von Neuman).

Tiempo ( ciclos de reloj)

O

r

d

e

n

d

e

i

n

s

t

r

u

c

c

i

n

Segmentacin: Riesgos estructurales

Arquitectura e Ingeniera de Computadores

Dependencias que se presentan para 2 instrucciones i y j, con i

ejecutndose antes que j.

RAW (Read After Write): la instruccin posterior j intenta leer una fuente antes

de que la instruccin anterior i la haya modificado.

WAR (Write After Read): la instruccin j intenta modificar un destino antes de

que la instruccin i lo haya ledo como fuente.

WAW (Write After Write): la instruccin j intenta modificar un destino antes de

que la instruccin i lo haya hecho (se modifica el orden normal de escritura).

Ejemplos: RAW WAR WAW

ADD r1, r2, r3 ADD r1, r2, r3 DIV r1, r2, r3

SUB r5, r1, r6 OR r3,r4, r5 AND r1,r4, r5

AND r6, r5, r1

ADD r4, r1, r3

SW r10, 100(r1)

Segmentacin: Riesgos por dependencia de datos

En micros segmentados con ejecucin

en orden slo son problema los RAW

Arquitectura e Ingeniera de Computadores

Segmentacin: Riesgos por dependencia de datos

Aparecen problemas al poder empezar la siguiente instruccin antes de

que la primera haya terminado.

Dependencias

problemticas son

aquellas que necesitan

datos que hay que

buscar hacia atrs en

el esquema de tiempos.

IM Reg

IM Reg

Ciclo1

IM

Reg

DM Reg

IM DM Reg

IM DM Reg

10 10 20

DM

Reg

Reg

Reg

Reg

DM

TIEMPO (CICLOS)

Ciclo2 Ciclo3 Ciclo4 Ciclo5 Ciclo6 Ciclo7 Ciclo8 Ciclo9

Valor de r1

PROGRAMA

add r1, r2, r3

sub r5, r1, r6

and r16, r5, r1

add r4, r1, r3

sw r10, 100(r1)

10 10 10 20 20 20 20

Ejemplo (RAW):

Arquitectura e Ingeniera de Computadores

Soluciones:

Adelantar (forward) el resultado de una etapa a las siguientes.

Definir adecuadamente la secuencia Read/Write (la instruccin add r4,r1,r3 funciona

correctamente si en la etapa WB, Write se realiza en la 1 mitad del ciclo y Read en la 2).

Segmentacin: Riesgos por dependencia de datos

IM Reg

IM Reg

IM

Reg

DM Reg

IM DM Reg

IM DM Reg

DM

Reg

Reg

Reg

Reg

DM

PROGRAMA

add r1, r2, r3

sub r5, r1, r6

and r16, r5, r1

add r4, r1, r3

sw r10, 100(r1)

Arquitectura e Ingeniera de Computadores

Necesidades hardware para adelantar resultados:

Multiplexores adicionales donde se vaya a recibir el dato (p. ej. en las entradas

de datos de la ALU).

Buses extra entre registros internos y multiplexores.

Comparadores entre los operandos de una instruccin y los operandos destino

de instrucciones previas.

Segmentacin: Riesgos por dependencia de datos

M

u

x

M

u

x

M

u

x

ALU

Data

memory

M

u

x

EX/MEM.RegisterRd

ID/EX EX/MEM MEM/WB

Arquitectura e Ingeniera de Computadores

Los riesgos pueden persistir incluso con adelantamiento de datos

Ej: tras la instruccin LOAD se pueden evitar los riesgos en AND y en OR con

adelantamiento de datos, pero no de SUB (no puede adelantar resultados a etapas que son

de tiempos anteriores)

Tiempo (ciclos de reloj)

O

r

d

e

n

d

e

i

n

s

t

r

u

c

c

i

o

n

e

s

Segmentacin: Riesgos por dependencia de datos

Arquitectura e Ingeniera de Computadores

Soluciones:

Insertar un ciclo de espera (stall) en el ciclo 3, para la instruccin SUB y siguientes

Insertar una operacin NOP detrs del LOAD (es lo ms utilizado, lo puede automatizar el

compilador sin necesidad de ms hardware)

Tiempo (ciclos de reloj)

O

r

d

e

n

d

e

i

n

s

t

r

u

c

c

i

o

n

e

s

Segmentacin: Riesgos por dependencia de datos

Arquitectura e Ingeniera de Computadores

Segmentacin: Ruta de datos con control para adelantamiento

de datos y deteccin de riesgos

Arquitectura e Ingeniera de Computadores

Segmentacin: Control para adelantamiento de datos

Unidad de adelantamiento de datos (forwarding)

Se debe detectar el riesgo y luego anticipar el valor a su destino

Se agrega un bloque combinacional para detectar el riesgo y

multiplexores para adelantar los datos oportunamente

Registers

M

u

x

M

u

x

M

u

x

ALU

Data

memory

M

u

x

Forwarding

unit

EX/MEM.RegisterRd

MEM/WB.RegisterRd

IF/IDRegisterRs

Rt

Rd

Rs

Rt

IF/IDRegisterRt

IF/IDRegisterRt

IF/IDRegisterRd

ID/EX EX/MEM MEM/WB

AnticiparA

AnticiparB

Arquitectura e Ingeniera de Computadores

Segmentacin: Control para adelantamiento de datos

Unidad de adelantamiento de datos (forwarding)

Se debe detectar el riesgo y luego anticipar el valor a la ALU

Existen 4 riesgos potenciales:

1a. EX/MEM.Registro.Rd = ID/EX.Registro.Rs

1b. EX/MEM.Registro.Rd = ID/EX.Registro.Rt

2a. MEM/WB.Registro.Rd = ID/EX.Registro.Rs

2b. MEM/WB.Registro.Rd = ID/EX.Registro.Rt

Analizar por ejemplo con:

Add r1, r2, r3

Sub r5, r1, r6

And r6, r5, r1

Add r4, r1, r3

Registers

M

u

x

M

u

x

M

u

x

ALU

Data

memory

M

u

x

Forwarding

unit

EX/MEM.RegisterRd

MEM/WB.RegisterRd

IF/IDRegisterRs

Rt

Rd

Rs

Rt

IF/IDRegisterRt

IF/IDRegisterRt

IF/IDRegisterRd

ID/EX EX/MEM MEM/WB

AnticiparA

AnticiparB

Arquitectura e Ingeniera de Computadores

Segmentacin: Control para adelantamiento de datos

Unidad de adelantamiento de datos (forwarding)

Pseudo-cdigo del funcionamiento:

(Riesgos en EX)

if (EX/MEM.EscrReg and

EX/MEM.RegistroRd 0 and

EX/MEM.Registro.Rd = ID/EX.Registro.Rs)

then AnticiparA = 10

else AnticiparA = 00

if (EX/MEM.EscrReg and

EX/MEM.RegistroRd 0 and

EX/MEM.Registro.Rd = ID/EX.Registro.Rt)

Then AnticiparB = 10

else AnticiparB = 00

M

u

x

M

u

x

M

u

x

ALU

Data

memory

M

u

x

Forwarding

unit

EX/MEM.RegisterRd

MEM/WB.RegisterRd

Rt

Rd

Rs

Rt

ID/EX EX/MEM MEM/WB

AnticiparA

AnticiparB

Arquitectura e Ingeniera de Computadores

Segmentacin: Control para adelantamiento de datos

Unidad de adelantamiento de datos (forwarding)

Pseudo-cdigo del funcionamiento:

M

u

x

M

u

x

M

u

x

ALU

Data

memory

M

u

x

Forwarding

unit

EX/MEM.RegisterRd

MEM/WB.RegisterRd

Rt

Rd

Rs

Rt

ID/EX EX/MEM MEM/WB

AnticiparA

AnticiparB

(Riesgos en MEM)

if (MEM/WB.EscrReg and

MEM/WB.RegistroRd 0 and

EX/MEM.Registro.Rd ID/EX.RegistroRs

and

MEM/WB.Registro.Rd =

ID/EX.RegistroRs)

then AnticiparA = 01

else AnticiparA = 00

if (MEM/WB.EscrReg and

MEM/WB.RegistroRd 0 and

EX/MEM.Registro.Rd ID/EX.RegistroRt

and

MEM/WB.Registro.Rd = ID/EX.Registro.Rt)

then AnticiparB = 01

else AnticiparB = 00

Arquitectura e Ingeniera de Computadores

Segmentacin: Deteccin de riesgos insalvables

Unidad de deteccin de riesgos (hazard detection unit)

Para cuando el adelantamiento no resuelve los riesgos (caso de load y

uso del registro destino en la siguiente instruccin)

Pseudo-cdigo del funcionamiento:

If (ID/EX.LeerMem and

((ID/EX.Registro.Rt = IF/ID.Registro.Rs) or

(ID/EX.Registro.Rt = IF/ID.Registro.Rt)))

then Bloquear el pipeline

Bloquear el pipeline:

PCWrite = 0

IF/IDWrite = 0

MuxNOP = 1

Todo esto no es necesario si el

compilador / ensamblador aade un

NOP despus del LOAD con riesgo

Arquitectura e Ingeniera de Computadores

Una solucin SW para el caso del lw

El compilador puede reacomodar el cdigo para evitar

stalls

Ejemplo en C: A = B + E; C = B + F;

l w $t 1, 0( $t 0)

l w $t 2, 4( $t 0)

add $t 3, $t 1, $t 2

sw $t 3, 12( $t 0)

l w $t 4, 8( $t 0)

add $t 5, $t 1, $t 4

sw $t 5, 16( $t 0)

l w $t 1, 0( $t 0)

l w $t 2, 4( $t 0)

l w $t 4, 8( $t 0)

add $t 3, $t 1, $t 2

sw $t 3, 12( $t 0)

add $t 5, $t 1, $t 4

sw $t 5, 16( $t 0)

11 ciclos 13 ciclos

stall

stall

Arquitectura e Ingeniera de Computadores

Las instrucciones de salto pueden suponer una alteracin del orden

secuencial de ejecucin.

No se sabe si el salto es efectivo hasta la etapa de ejecucin y no se

actualiza la direccin destino (caso de que sea efectivo) hasta la cuarta

etapa => Prdida de 3 ciclos

Mejora: Adelantar el clculo del destino (target) PC+Inmediato y adelantar la

resolucin de la condicin (y actualizar el PC) a la 2 etapa.

Riesgos de control (instrucciones de salto)

Etapa IF Etapa ID Etapa EX Etapa MEM Etapa WB

Obtener instruccin

Acceso a la memoria

de instrucciones

Decodificar instruccin.

Lectura de operandos,

carga de registros

Ejecutar instruccin

Calcular la direccin

efectiva salto (PC+Inm.)

Acceso a Memoria

o bien

Resolver la condicin

y escribir en PC la

direccin de salto.

Escribir en un

registro el resultado

de la operacin

Arquitectura e Ingeniera de Computadores

Ejemplo: salto efectivo

36: sub $10, $4, $8

40: beq $1, $3, 7

44: and $12, $2, $5

48: or $13, $2, $6

52: add $14, $4, $2

56: sl t $15, $6, $7

. . .

72: l w $4, 50( $7)

Cuando se decide saltar a una instruccin distinta de la siguiente, ya se estn ejecutando

otras instrucciones en el cauce segmentado => Se necesita incluir hardware para vaciar

(flushing) el pipeline

Riesgos de control (instrucciones de salto)

Arquitectura e Ingeniera de Computadores

Ejemplo: Salto Efectivo

Para descartar una instruccin cambia a 0 el campo de instruccin (opcode) del registro de

segmentacin IF/ID NOP

Arquitectura e Ingeniera de Computadores

Ejemplo: Salto Efectivo

Arquitectura e Ingeniera de Computadores

QU HACER CON LAS SIGUIENTES INSTRUCCIONES A LA DE SALTO

CONDICIONAL?

1. Esperar hasta que la direccin y condicin del salto estn definidas.

Conviene conocer la direccin de salto y la condicin tan pronto como sea posible.

2. Salto retardado, la(s) instruccin(es) posterior(es) siempre se ejecuta(n).

El compilador rellena con instrucciones vlidas los huecos de retardo.

3. Predecir si se va a saltar o no.

Se ejecuta especulativamente, en caso de error se debe vaciar el procesador.

4. Anticipar la direccin ms probable para el salto (BTB).

Se ejecuta especulativamente, se almacena en una cach la direccin del ltimo salto.

5. Ejecutar todos los caminos.

Implica la duplicacin del hardware.

6. Ejecucin con predicados.

Riesgos de Control (Instrucciones de salto)

Arquitectura e Ingeniera de Computadores

Riesgos de Control. Salto retardado

add r1, r2, r3

bnz r2, L1

nop

sub r6,r7,r6

mul r2, r3, r8

.................

L1: and r2, r3, r2

andi r5,r6,inm

La siguiente instruccin al salto siempre se termina de ejecutar, se salte o no.

El compilador utiliza tres estrategias para buscar una/varias instrucciones de relleno:

...........

bnz r2, L1

add r1, r2, r3

sub r6,r7,r6

mul r2, r3, r8

.................

L1: and r2, r3, r2

andi r5,r6,inm

add r1, r2, r3

bnz r2, L1

and r2, r3, r2

sub r6,r7,r6

mul r2, r3, r8

.................

L1: andi r5,r6,inm

............

add r1, r2, r3

bnz r2, L1

sub r6,r7,r6

.................

mul r2, r3, r8

.................

L1: and r2, r3, r2

andi r5,r6,inm

DEL BLOQUE BSICO SI SALTO PROBABLE,

DEL BLOQUE DESTINO

SI SALTO NO PROBABLE,

DEL BLOQUE SECUENCIAL

Operacin vlida si la

instruccin no afecta a la

condicin del salto. Siempre

se realiza trabajo til.

Operacin vlida siempre

siempre que r2 no se utilice

como fuente y sea modificada

como destino en el en bloque

secuencial. (CORRECTO)

Operacin vlida siempre

que r6 no se utilice como

fuente y sea modificada como

destino en el en bloque

destino. (INCORRECTO)

Arquitectura e Ingeniera de Computadores

Riesgos de Control. Predecir el salto

Prediccin esttica: siempre predice el mismo sentido del salto.

Ejecuta especulativo hasta que se resuelve la condicin (normalmente, ciclo 3-4)

En caso de error debe eliminar los resultados especulativos

Prediccin efectiva (E), el salto se realiza

Prediccin no efectiva (NE), el salto no se realiza

Prediccin NE si el salto es adelante y E si es hacia atrs

Prediccin dinmica: cambia la prediccin en funcin de la historia del salto.

Utiliza una pequea memoria asociada a cada direccin de salto (BHT, Branch

History Table)

F

PC Direccin Instruccin Salto

BHT

E

NE

A

A

F

F

PREDICCIN DE 1 BIT PREDICCIN DE 2 BITS

Ef Ed A

F

A

NEd NEf A

A

F

F

Arquitectura e Ingeniera de Computadores

Utiliza la tcnica de prediccin histrica anterior

Utiliza una tabla asociativa (tipo cach) que incorpora, para cada instruccin de

salto, la direccin de destino de la prediccin anterior.

A la tabla se la conoce como buffer de destino de saltos o BTB (Branch Target

Buffer).

Direccin

Instruccin

Direccin

Destino

Bits de

historia

Tabla de look-up

completamente asociativa

Contador de Programa

Fetch Decod.

Cargar direc. destino

Direccin

Instruccin

SEGMENTACIN DE INSTRUCCIONES

Direc. destino encontrada

Riesgos de Control. Anticipar la direccin ms probable

Arquitectura e Ingeniera de Computadores

Segmentacin: Tratamiento de excepciones y mejoras

Cmo afecta a la segmentacin el tratamiento de

excepciones (interrupciones, desbordamientos aritmticos, peticiones de

E/S, servicios del sistema operativo, uso de instrucciones no definidas, mal

funcionamiento de la circuitera, etc)?

Bsicamente detectarlo y vaciar el pipeline para dar el control a

alguna rutina de tratamiento de excepciones

Cmo mejorar an ms la segmentacin?

Super-segmentacin (implica segmentacin en operaciones aritmticas)

Superescalares (replicar rutas de datos)

Planificacin dinmica del pipeline

Das könnte Ihnen auch gefallen

- Codigo de Error Cosechadora John DeereDokument12 SeitenCodigo de Error Cosechadora John DeereSilvio Roman80% (10)

- Sistema Operativo IOSDokument6 SeitenSistema Operativo IOSCaTrAgEd50% (2)

- Tema 2 - HardwareDokument64 SeitenTema 2 - HardwarePaquito NavarroNoch keine Bewertungen

- Principio de operación de compresores y limitadoresDokument3 SeitenPrincipio de operación de compresores y limitadoresAlan Blanco100% (1)

- Parlante Video RockolaDokument52 SeitenParlante Video RockolaOswaldo100% (2)

- Manual MicroeconomiaDokument74 SeitenManual MicroeconomiaVerónicaTaftNoch keine Bewertungen

- Elastic I DadDokument20 SeitenElastic I DadMaurice CourtoisNoch keine Bewertungen

- Apunte ALUDokument46 SeitenApunte ALUVerónicaTaftNoch keine Bewertungen

- Adicionales Cap4 MIPSDokument1 SeiteAdicionales Cap4 MIPSVerónicaTaftNoch keine Bewertungen

- 009 Io 2013Dokument32 Seiten009 Io 2013VerónicaTaftNoch keine Bewertungen

- 001 Rendimiento 2014Dokument22 Seiten001 Rendimiento 2014VerónicaTaftNoch keine Bewertungen

- 006 Excepciones MIPS 2013Dokument11 Seiten006 Excepciones MIPS 2013VerónicaTaftNoch keine Bewertungen

- 001 Rendimiento 2014Dokument22 Seiten001 Rendimiento 2014VerónicaTaftNoch keine Bewertungen

- Trabajo de InstrumentacionDokument4 SeitenTrabajo de InstrumentacionRAFAGTZNoch keine Bewertungen

- Quiz EnlacesDokument2 SeitenQuiz EnlacesXochitl Escobosa RodriguezNoch keine Bewertungen

- Cuadro. Procesos de Manufactura WDokument2 SeitenCuadro. Procesos de Manufactura WaldoNoch keine Bewertungen

- Las Unidades de Medida en Informatica 1347 k7bb2hDokument2 SeitenLas Unidades de Medida en Informatica 1347 k7bb2hJhonny PerezNoch keine Bewertungen

- 80110-204 Erbe Es Apc 2 V 1 4 D010504Dokument60 Seiten80110-204 Erbe Es Apc 2 V 1 4 D010504Carlos LopezNoch keine Bewertungen

- Practica ADokument14 SeitenPractica ACarlos ZevallosNoch keine Bewertungen

- Examen Parcial Ofimatica 2017-2 Modulo 2Dokument4 SeitenExamen Parcial Ofimatica 2017-2 Modulo 2Samuel Huaman Arias100% (1)

- Algunos Aspectos Técnicos de Las Comunicaciones de Socorro en Situaciones de CatástrofeDokument66 SeitenAlgunos Aspectos Técnicos de Las Comunicaciones de Socorro en Situaciones de CatástrofemenssesNoch keine Bewertungen

- Entel - Actualizar Software - Manual IOSDokument9 SeitenEntel - Actualizar Software - Manual IOSWilliam Alex Pujay OrtizNoch keine Bewertungen

- Cuaderno Digital MetrologíaDokument15 SeitenCuaderno Digital MetrologíaLeoNoch keine Bewertungen

- GSSL-SAL-PR001. Procedimiento de Dosimetr - A de RuidoDokument10 SeitenGSSL-SAL-PR001. Procedimiento de Dosimetr - A de RuidojazminNoch keine Bewertungen

- Campo magnético 2oBach - Ejercicios resueltosDokument9 SeitenCampo magnético 2oBach - Ejercicios resueltosDebora Benitez SuarezNoch keine Bewertungen

- Que Es QoS PowerpointDokument18 SeitenQue Es QoS PowerpointKrissia ArayaNoch keine Bewertungen

- Tutorial WARP 6.3Dokument8 SeitenTutorial WARP 6.3Elmago0688Noch keine Bewertungen

- Chip SetDokument5 SeitenChip SetJuan Leonardo Medina Sanchez100% (1)

- Métodos Abreviados de Teclado Predeterminados en Premiere Pro CCDokument22 SeitenMétodos Abreviados de Teclado Predeterminados en Premiere Pro CCbasuratfe1679Noch keine Bewertungen

- Actualizacion en Operacion de Maquinaria Pesada PDFDokument88 SeitenActualizacion en Operacion de Maquinaria Pesada PDFjorgemorales416Noch keine Bewertungen

- Software Comercial 1-pDokument7 SeitenSoftware Comercial 1-pHector RuizNoch keine Bewertungen

- Lista Precio AnwoDokument115 SeitenLista Precio AnwoAnonymous L7sGDm9lL100% (1)

- Reconocimiento y Manejo Del MicroscopioDokument7 SeitenReconocimiento y Manejo Del MicroscopioNohemi Guevara ChimaNoch keine Bewertungen

- Comunicacion PLCDokument64 SeitenComunicacion PLCJulver Galindo CondoriNoch keine Bewertungen

- Cargador 1Dokument28 SeitenCargador 1Yalile MontañaNoch keine Bewertungen

- Diseño Subestación EléctricaDokument103 SeitenDiseño Subestación EléctricaMorro DelArrabal100% (1)

- Guia Tarifa Nueva ICT-2 Mayo 2013TVDokument36 SeitenGuia Tarifa Nueva ICT-2 Mayo 2013TVgmc gmcNoch keine Bewertungen