Beruflich Dokumente

Kultur Dokumente

Ejemplo Examen

Hochgeladen von

Sixto Manrique Miranda0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

86 Ansichten3 SeitenCopyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

86 Ansichten3 SeitenEjemplo Examen

Hochgeladen von

Sixto Manrique MirandaCopyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 3

Universidad Carlos III de Madrid

Examen de Electrnica Digital

Cuestin 1 (1P.)

Dados los siguientes nmeros binarios de 8 bits

a=11010101

b=01011111

efecte las operaciones que se indican y determine el valor decimal del resultado, en los

casos siguientes:

a) c=a+b, suponiendo que a, b y c son nmeros sin signo

b) c=a+b, suponiendo que a, b y c son nmeros con signo en complemento a 2

c) c=a-b, suponiendo que a, b y c son nmeros sin signo

d) c=a-b, suponiendo que a, b y c son nmeros con signo en complemento a 2

Indique en cuales de los casos anteriores existe desbordamiento y por tanto no se puede

representar el resultado c con 8 bits.

Cuestin 2 (1P.)

Determine la funcin lgica simplificada que realiza el circuito de la figura. En el

decodificador tenga en cuenta que la entrada de mayor peso es la S2 y la salida de mayor

peso es la Q7.

Cuestin 3 (1.25 P.)

Dado el circuito secuencial de la figura, complete el cronograma de la hoja adjunta

dibujando las formas de onda que se obtendran en Q0, Q1 y Q2.

Notacin:

C: Entrada de reloj, activa por flanco de subida

S: Entrada asncrona de puesta a 1

R: Entrada asncrona de puesta a 0

Universidad Carlos III de Madrid

Examen de Electrnica Digital

Cuestin 4 (1 P.)

A partir de la RAM de la figura:

Direcciones

{

Datos

}

RAM

256x4

A

0

A

7

Q

0

Q

3

CS

WE

a) Dibuje el esquema de una RAM de 256x16, indicando todas las conexiones

b) Dibuje el esquema de una RAM de 1Kx8, indicando todas las conexiones

Cuestin 5 (1P.)

En la figura se muestra una puerta lgica realizada en tecnologa NMOS. Se pide:

a) Determine la funcin lgica que realiza el circuito

b) Dibuje el esquema de transistores de un circuito CMOS que realice la misma

funcin lgica

Vcc

B

C

D

A

Z

Universidad Carlos III de Madrid

Examen de Electrnica Digital

Problema 1 (2.25 P.)

Se pretende realizar un circuito combinacional como el de la figura que consta de dos

partes. C1 es un codificador con prioridad de 5 entradas con salidas codificadas en

cdigo binario. La prioridad de las entradas viene dada por el ndice, siendo x4 la

entrada ms prioritaria y x0 la menos prioritaria. C2 es un circuito que convierte el

nmero binario obtenido y2y1y0 a cdigo Gray de 3 bits, z2z1z0. En ambos casos, el bit

ms significativo es el de mayor ndice.

Se pide

1) Realizar el circuito C1

a) slo con puertas NOR de 2 entradas

b) slo con multiplexores de 2 entradas de datos y 1 entrada de seleccin

2) Realizar el circuito C2

a) con puertas lgicas AND, OR e inversores

b) con un decodificador DM74LS138, como el de la hoja de catlogo que se

incluye, y puertas lgicas

Nota importante: se valorar el uso del menor nmero de componentes en las

soluciones

Problema 2 (2.5 P.)

Se pretende disear un circuito secuencial sncrono que tiene una entrada X y una salida

Z. La seal de entrada X est sincronizada con el reloj del circuito (CLK) y presenta

pulsos a nivel alto de duracin variable. La seal de salida Z debe activarse (Z=1)

cuando se detecte un pulso vlido en X. Un pulso se considera vlido si tiene una

duracin de 2 3 ciclos de reloj. Es decir, que si X tiene un pulso que dura 1 ciclo de

reloj o ms de 3 no se considerar vlido.

Ejemplo:

X: 010111110111000

Z: 000000000000100

Ntese que la salida Z slo se activa cuando ha terminado el pulso en X y ste ha sido

vlido.

Se pide:

a) Realice el diagrama de transicin de estados del circuito segn el modelo de Mealy

b) Implemente el circuito para una codificacin de los estados en binario natural,

utilizando biestables T y puertas lgicas

C1

x4

x3

x2

x1

x0

C2

y2

y1

y0

z2

z1

z0

Das könnte Ihnen auch gefallen

- Problemas resueltos de Hidráulica de CanalesVon EverandProblemas resueltos de Hidráulica de CanalesBewertung: 4.5 von 5 Sternen4.5/5 (7)

- Algebra BooleanaDokument9 SeitenAlgebra Booleanavargasc7Noch keine Bewertungen

- Métodos Matriciales para ingenieros con MATLABVon EverandMétodos Matriciales para ingenieros con MATLABBewertung: 5 von 5 Sternen5/5 (1)

- T2 EjerciciosDokument6 SeitenT2 EjerciciosHernan Ali LopezNoch keine Bewertungen

- Ejercicios de Integrales de Línea, Superficie y VolumenVon EverandEjercicios de Integrales de Línea, Superficie y VolumenBewertung: 4 von 5 Sternen4/5 (2)

- Ejercicios DigitalesDokument7 SeitenEjercicios DigitalesAlvaro SanchezNoch keine Bewertungen

- La ecuación general de segundo grado en dos y tres variablesVon EverandLa ecuación general de segundo grado en dos y tres variablesNoch keine Bewertungen

- Taller UAODokument3 SeitenTaller UAOJose David CastroNoch keine Bewertungen

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaVon EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaNoch keine Bewertungen

- RELACIÓN DE PROBLEMAS Bloque Temático VDokument3 SeitenRELACIÓN DE PROBLEMAS Bloque Temático Veljesurodriguez888Noch keine Bewertungen

- Prácticas de redes de datos e industrialesVon EverandPrácticas de redes de datos e industrialesBewertung: 4 von 5 Sternen4/5 (5)

- Tema3 PROBLEMASDokument7 SeitenTema3 PROBLEMASeros.llorensNoch keine Bewertungen

- Puertas LogicasDokument13 SeitenPuertas LogicasturinatecnologiaNoch keine Bewertungen

- 2bach Tema6Dokument19 Seiten2bach Tema6Samuel Guijarro Salamanca100% (1)

- PARCIAL IV Circuitos DigitalesDokument6 SeitenPARCIAL IV Circuitos DigitalesNubia DorantesNoch keine Bewertungen

- En Word REPASO EX FINALDokument3 SeitenEn Word REPASO EX FINALCriss-tian Eduardo Estupiñan VasquezNoch keine Bewertungen

- Problemas y Cuestiones - Programación y Control de Sistemas Automáticos 2002 2016 PDFDokument40 SeitenProblemas y Cuestiones - Programación y Control de Sistemas Automáticos 2002 2016 PDFpavilionhp123100% (1)

- Circuitos CombinacionalesDokument27 SeitenCircuitos CombinacionalesHenry TipanNoch keine Bewertungen

- Subsistemas CombinacionalesDokument4 SeitenSubsistemas CombinacionalesRoky RbrNoch keine Bewertungen

- Exercicis Electrònica DigitalDokument23 SeitenExercicis Electrònica Digitalretrueke1170Noch keine Bewertungen

- Ejercicios 9 0304 PDFDokument6 SeitenEjercicios 9 0304 PDFJoeliTo VeraNoch keine Bewertungen

- Problem Ass DigDokument107 SeitenProblem Ass DigYani Ivanov ManovNoch keine Bewertungen

- Unidad III. Diseño de Sistemas CombinacionalesDokument7 SeitenUnidad III. Diseño de Sistemas CombinacionalesJessica LeivaNoch keine Bewertungen

- Problemas Circuitos Combinacionales 0506Dokument6 SeitenProblemas Circuitos Combinacionales 0506Abner Isaac RomeroNoch keine Bewertungen

- FileDokument8 SeitenFileclaraNoch keine Bewertungen

- Problem As Circuit Os Secuencia Les 0405Dokument4 SeitenProblem As Circuit Os Secuencia Les 0405MaríaAmarantoNoch keine Bewertungen

- Prob Elct Digital IIDokument25 SeitenProb Elct Digital IIEsteban RiquelmeNoch keine Bewertungen

- Problemas 5Dokument5 SeitenProblemas 5EberSantaCruzBerriosNoch keine Bewertungen

- InformeDokument2 SeitenInformeRonaldo PaipaNoch keine Bewertungen

- Diseño Lógico Serie ModificadaDokument2 SeitenDiseño Lógico Serie ModificadaBlacksimb CanalNoch keine Bewertungen

- ProblemasCircuitosCombinacionales 072012Dokument5 SeitenProblemasCircuitosCombinacionales 072012Santiago GuallichicoNoch keine Bewertungen

- TallerPrimerCorte ED1 2022 1Dokument3 SeitenTallerPrimerCorte ED1 2022 1Boy NiggaNoch keine Bewertungen

- Problemas 10 11Dokument14 SeitenProblemas 10 11andrear_202Noch keine Bewertungen

- SDIG Problemas ResueltosDokument107 SeitenSDIG Problemas ResueltosAleks ValentinNoch keine Bewertungen

- Compendio de Problemas de Practica Circuitos DigitalesDokument37 SeitenCompendio de Problemas de Practica Circuitos Digitaleslennon_meoñoNoch keine Bewertungen

- Problemas Propuestos de Circuitos Electrónicos 2 PDFDokument2 SeitenProblemas Propuestos de Circuitos Electrónicos 2 PDFRodrigo Gómez ManriqueNoch keine Bewertungen

- Electronica Digital EjerciciosDokument4 SeitenElectronica Digital EjerciciosjuliNoch keine Bewertungen

- Compendio de ProblemasDokument32 SeitenCompendio de ProblemasJoséLópezPicadoNoch keine Bewertungen

- Prob 3Dokument3 SeitenProb 3hvillafuertebNoch keine Bewertungen

- Puertas LogicasDokument14 SeitenPuertas Logicasmglq100% (1)

- Cey1 2022Dokument6 SeitenCey1 2022Tomas Gonzalez AspeNoch keine Bewertungen

- PROBLEMAS DE ELECTRONICA DIGITALtodos PDFDokument26 SeitenPROBLEMAS DE ELECTRONICA DIGITALtodos PDFSaul EneNoch keine Bewertungen

- Problem As Circuit Os Comb I Nacionales 0203Dokument5 SeitenProblem As Circuit Os Comb I Nacionales 0203Alex WongNoch keine Bewertungen

- Exposicion CodificadoresDokument41 SeitenExposicion CodificadoresPio Sulca TapahuascoNoch keine Bewertungen

- Ejercicios de SEDDokument31 SeitenEjercicios de SED勵志楊Noch keine Bewertungen

- Compendio de Problemas 2019Dokument34 SeitenCompendio de Problemas 2019Celeste Quiros MarinNoch keine Bewertungen

- Problemas de Examen (2do Cuatrimestre)Dokument37 SeitenProblemas de Examen (2do Cuatrimestre)Gabriel StalinNoch keine Bewertungen

- Practica 3Dokument0 SeitenPractica 3Enrique GonzalesNoch keine Bewertungen

- Resueltos E.digitalDokument37 SeitenResueltos E.digitalxarxacalcio-1Noch keine Bewertungen

- Guia 1 Sistemas de Logica Secuencial 2020Dokument5 SeitenGuia 1 Sistemas de Logica Secuencial 2020Limon AlejandroNoch keine Bewertungen

- Fcbol 3Dokument6 SeitenFcbol 3Paola Flors'RedheadNoch keine Bewertungen

- Taller1 2 2022 CombinacionalesDokument18 SeitenTaller1 2 2022 CombinacionalesValentina RestrepoNoch keine Bewertungen

- Compendio de Problemas 2018Dokument34 SeitenCompendio de Problemas 2018Luis_k94Noch keine Bewertungen

- 2P EnI 15-16-SolucionDokument8 Seiten2P EnI 15-16-SolucionTheDoctor TheDoctorNoch keine Bewertungen

- Examen Ecaes DigitalesII 2016-1Dokument9 SeitenExamen Ecaes DigitalesII 2016-1SantiagoGrimaldos100% (1)

- CUESTIONARIO Sistemas DigitalesDokument5 SeitenCUESTIONARIO Sistemas DigitalesEdison JamiNoch keine Bewertungen

- Ej T3FtosDokument6 SeitenEj T3Ftospete sajotNoch keine Bewertungen

- Guia 1 Sistemas de Logica Secuencial 2020Dokument5 SeitenGuia 1 Sistemas de Logica Secuencial 2020Limon AlejandroNoch keine Bewertungen

- IEE Problemas Tema7 DigitalDokument4 SeitenIEE Problemas Tema7 DigitalnivekNoch keine Bewertungen

- VOLANTEDokument1 SeiteVOLANTESixto Manrique MirandaNoch keine Bewertungen

- Inicio: 16 de Octubre: Introduction To NetworksDokument5 SeitenInicio: 16 de Octubre: Introduction To NetworksSixto Manrique MirandaNoch keine Bewertungen

- PRO52E: ModeloDokument1 SeitePRO52E: ModeloSixto Manrique MirandaNoch keine Bewertungen

- DEONTOLOGÍADokument11 SeitenDEONTOLOGÍASixto Manrique MirandaNoch keine Bewertungen

- UntitledDokument11 SeitenUntitledSixto Manrique MirandaNoch keine Bewertungen

- Plan Curricular de Administración de Empresas en UNFVDokument24 SeitenPlan Curricular de Administración de Empresas en UNFVSixto Manrique MirandaNoch keine Bewertungen

- Plan Curricular Decontabilidad en UNFVDokument19 SeitenPlan Curricular Decontabilidad en UNFVSixto Manrique MirandaNoch keine Bewertungen

- Informe 3 Sistemas DigitalesDokument8 SeitenInforme 3 Sistemas DigitalesJuan Jesús Vargas SaldañaNoch keine Bewertungen

- Perdida y GananciasDokument2 SeitenPerdida y GananciasLuis Alonzo Reyes SiquerosNoch keine Bewertungen

- Actividades de Transferencia Del ConocimientoDokument3 SeitenActividades de Transferencia Del ConocimientoJhonatan Gutierrez MonsalvoNoch keine Bewertungen

- Viaje A Tulipe 2015 - Piedra Umiña PDFDokument29 SeitenViaje A Tulipe 2015 - Piedra Umiña PDFJulioCesarBarrenaDiosesNoch keine Bewertungen

- Simulacion ExamenCMRPDokument9 SeitenSimulacion ExamenCMRPjoseNoch keine Bewertungen

- Unidad 6 ElectromagnetismoDokument9 SeitenUnidad 6 ElectromagnetismojoseNoch keine Bewertungen

- Acin113 s2 SolucionarioDokument3 SeitenAcin113 s2 SolucionarioyenilobiNoch keine Bewertungen

- Historia Shampoo SabilaDokument7 SeitenHistoria Shampoo SabilaJust MusicNoch keine Bewertungen

- Personal Social 26-10-2021Dokument2 SeitenPersonal Social 26-10-2021Jhon Maicol Chavez AlayaNoch keine Bewertungen

- Clase Social y Conocimiento Escolar AnyonDokument2 SeitenClase Social y Conocimiento Escolar AnyonSandra S100% (1)

- Pensamiento LeanDokument43 SeitenPensamiento LeanVerónicaHamNoch keine Bewertungen

- Financiamiento Interno y ExternoDokument5 SeitenFinanciamiento Interno y ExternoJoseNoch keine Bewertungen

- Tarifa Detallados Pulido de Coche Madrid Motos 2017 DP Luxe DetailDokument5 SeitenTarifa Detallados Pulido de Coche Madrid Motos 2017 DP Luxe Detailhumantragedy5861Noch keine Bewertungen

- EVIDENCIA 2 Diagrama de FlujoDokument4 SeitenEVIDENCIA 2 Diagrama de FlujoKari GomezNoch keine Bewertungen

- 4to Lab de AutoDokument20 Seiten4to Lab de AutoBryan VillagomezNoch keine Bewertungen

- Estado Del ArteDokument12 SeitenEstado Del ArteAngela GarciaNoch keine Bewertungen

- Problemas de Optimizacion y Razon de CambioDokument3 SeitenProblemas de Optimizacion y Razon de CambioHelena Dulcey H.Noch keine Bewertungen

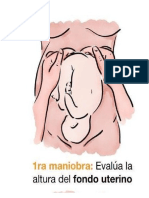

- En Que Consiste Cada Maniobra de LiopolDokument11 SeitenEn Que Consiste Cada Maniobra de LiopolAndres BuesoNoch keine Bewertungen

- Topografía I - Teoría de ProbabilidadesDokument7 SeitenTopografía I - Teoría de ProbabilidadesJunior Quispe HuarcayaNoch keine Bewertungen

- IVA Exportador 1Dokument5 SeitenIVA Exportador 1Jota CNoch keine Bewertungen

- La Calumnia de ApelesDokument2 SeitenLa Calumnia de ApelesMercedes RuizNoch keine Bewertungen

- Diagrama de Flujo - Fuente LinealesDokument6 SeitenDiagrama de Flujo - Fuente LinealesTemas del Talento en Sistemas100% (1)

- LO 5.1 Guia Trabajo Aplicativo-DAF 2023-2Dokument2 SeitenLO 5.1 Guia Trabajo Aplicativo-DAF 2023-2Ariana Andrea RIOS LIZANONoch keine Bewertungen

- Museo de Arte Contemporaneo NiteroiDokument23 SeitenMuseo de Arte Contemporaneo NiteroiRonald CauichNoch keine Bewertungen

- El Experimento FiladelfiaDokument11 SeitenEl Experimento FiladelfiaJorge Ivan Velazquez VicenteNoch keine Bewertungen

- Ciencias 8 Basico, 16 Al 20 de AgostoDokument1 SeiteCiencias 8 Basico, 16 Al 20 de AgostoSandra Morales GuerraNoch keine Bewertungen

- Trabajo Construcciones EspecialesDokument11 SeitenTrabajo Construcciones Especialestania reynilda davila vilcaNoch keine Bewertungen

- Guia de Calculo IntegralDokument77 SeitenGuia de Calculo IntegralJesse HarperNoch keine Bewertungen

- 4.control Fiscal Micro - 98836 PDFDokument45 Seiten4.control Fiscal Micro - 98836 PDFDiego CastroNoch keine Bewertungen