Beruflich Dokumente

Kultur Dokumente

Phase 1 Top: Note Guard - Guard

Hochgeladen von

2vijOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Phase 1 Top: Note Guard - Guard

Hochgeladen von

2vijCopyright:

Verfügbare Formate

PHASE 1 TOP

In phase 1,

1) We will write SystemVerilog Interfaces for input port, output port and memory port.

2) We will write Top module where testcase and DUT instances are done.

3) DUT and TestBench interfaces are connected in top module.

4) Clock is generator in top module.

NOTE: In every file you will see the syntax

`ifndef GUARD_*

`endif GUARD_*

Interfaces

In the interface.sv file, declare the 3 interfaces in the following way.

All the interfaces has clock as input.

All the signals in interface are logic type.

All the signals are synchronized to clock except reset in clocking block.

Signal directional w.r.t TestBench is specified with modport.

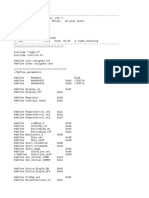

`ifndef GUARD_INTERFACE

`define GUARD_INTERFACE

//////////////////////////////////////////

// Interface declaration for the memory///

//////////////////////////////////////////

interface mem_interface(input bit clock);

logic [7:0] mem_data;

logic [1:0] mem_add;

logic mem_en;

logic mem_rd_wr;

clocking cb@(posedge clock);

default input #1 output #1;

output mem_data;

output mem_add;

output mem_en;

output mem_rd_wr;

endclocking

modport MEM(clocking cb,input clock);

endinterface

////////////////////////////////////////////

// Interface for the input side of switch.//

// Reset signal is also passed hear. //

////////////////////////////////////////////

interface input_interface(input bit clock);

logic data_status;

logic [7:0] data_in;

logic reset;

clocking cb@(posedge clock);

default input #1 output #1;

output data_status;

output data_in;

endclocking

modport IP(clocking cb,output reset,input clock);

endinterface

/////////////////////////////////////////////////

// Interface for the output side of the switch.//

// output_interface is for only one output port//

/////////////////////////////////////////////////

interface output_interface(input bit clock);

logic [7:0] data_out;

logic ready;

logic read;

clocking cb@(posedge clock);

default input #1 output #1;

input data_out;

input ready;

output read;

endclocking

modport OP(clocking cb,input clock);

endinterface

//////////////////////////////////////////////////

`endif

Testcase

Testcase is a program block which provides an entry point for the test and creates a scope that

encapsulates program-wide data. Currently this is an empty testcase which just ends the simulation

after 100 time units. Program block contains all the above declared interfaces as arguments. This

testcase has initial and final blocks.

`ifndef GUARD_TESTCASE

`define GUARD_TESTCASE

program testcase(mem_interface.MEM mem_intf,input_interface.IP input_intf,output_interface.OP out

put_intf[4]);

initial

begin

$display(" ******************* Start of testcase ****************");

#1000;

end

final

$display(" ******************** End of testcase *****************");

endprogram

`endif

Top Module

The modules that are included in the source text but are not instantiated are called top modules. This

module is the highest scope of modules. Generally this module is named as "top" and referenced as "top

module". Module name can be anything.

Do the following in the top module:

1)Generate the clock signal.

bit Clock;

initial

forever #10 Clock = ~Clock;

2)Do the instances of memory interface.

mem_interface mem_intf(Clock);

3)Do the instances of input interface.

input_interface input_intf(Clock);

4)There are 4 output ports. So do 4 instances of output_interface.

output_interface output_intf[4](Clock);

5)Do the instance of testcase and pass all the above declared interfaces.

testcase TC (mem_intf,input_intf,output_intf);

6)Do the instance of DUT.

switch DUT (.

7)Connect all the interfaces and DUT. The design which we have taken is in verilog. So Verilog DUT

instance is connected signal by signal.

switch DUT (.clk(Clock),

.reset(input_intf.reset),

.data_status(input_intf.data_status),

.data(input_intf.data_in),

.port0(output_intf[0].data_out),

.port1(output_intf[1].data_out),

.port2(output_intf[2].data_out),

.port3(output_intf[3].data_out),

.ready_0(output_intf[0].ready),

.ready_1(output_intf[1].ready),

.ready_2(output_intf[2].ready),

.ready_3(output_intf[3].ready),

.read_0(output_intf[0].read),

.read_1(output_intf[1].read),

.read_2(output_intf[2].read),

.read_3(output_intf[3].read),

.mem_en(mem_intf.mem_en),

.mem_rd_wr(mem_intf.mem_rd_wr),

.mem_add(mem_intf.mem_add),

.mem_data(mem_intf.mem_data));

Top Module Source Code:

`ifndef GUARD_TOP

`define GUARD_TOP

module top();

/////////////////////////////////////////////////////

// Clock Declaration and Generation //

/////////////////////////////////////////////////////

bit Clock;

initial

forever #10 Clock = ~Clock;

/////////////////////////////////////////////////////

// Memory interface instance //

/////////////////////////////////////////////////////

mem_interface mem_intf(Clock);

/////////////////////////////////////////////////////

// Input interface instance //

/////////////////////////////////////////////////////

input_interface input_intf(Clock);

/////////////////////////////////////////////////////

// output interface instance //

/////////////////////////////////////////////////////

output_interface output_intf[4](Clock);

/////////////////////////////////////////////////////

// Program block Testcase instance //

/////////////////////////////////////////////////////

testcase TC (mem_intf,input_intf,output_intf);

/////////////////////////////////////////////////////

// DUT instance and signal connection //

/////////////////////////////////////////////////////

switch DUT (.clk(Clock),

.reset(input_intf.reset),

.data_status(input_intf.data_status),

.data(input_intf.data_in),

.port0(output_intf[0].data_out),

.port1(output_intf[1].data_out),

.port2(output_intf[2].data_out),

.port3(output_intf[3].data_out),

.ready_0(output_intf[0].ready),

.ready_1(output_intf[1].ready),

.ready_2(output_intf[2].ready),

.ready_3(output_intf[3].ready),

.read_0(output_intf[0].read),

.read_1(output_intf[1].read),

.read_2(output_intf[2].read),

.read_3(output_intf[3].read),

.mem_en(mem_intf.mem_en),

.mem_rd_wr(mem_intf.mem_rd_wr),

.mem_add(mem_intf.mem_add),

.mem_data(mem_intf.mem_data));

endmodule

`endif

Run the simulation:

vcs -sverilog -f filelist -R -ntb_opts dtm

Log file after simulation:

******************* Start of testcase ****************

******************** End of testcase *****************

Das könnte Ihnen auch gefallen

- Testplan ApbDokument14 SeitenTestplan Apbanon_185221148100% (3)

- Foundation Course for Advanced Computer StudiesVon EverandFoundation Course for Advanced Computer StudiesNoch keine Bewertungen

- Verilog CodesDokument10 SeitenVerilog CodesKrishna RamaNoch keine Bewertungen

- UART (Verilog Code) With FSMDokument24 SeitenUART (Verilog Code) With FSMसौरभ शुक्ला0% (1)

- VLSI CMOS Interview Questions and AnswersDokument67 SeitenVLSI CMOS Interview Questions and AnswersrAM95% (85)

- Laboratory Manual For Distributed Computing PDFDokument22 SeitenLaboratory Manual For Distributed Computing PDFashokmvanjareNoch keine Bewertungen

- Moshell CommandDokument16 SeitenMoshell Commandodanbgh22160% (1)

- PHASE 1 TOP ModuleDokument48 SeitenPHASE 1 TOP ModulePriyank PatelNoch keine Bewertungen

- Keyboard - C: Programa en C USB PIC18FDokument11 SeitenKeyboard - C: Programa en C USB PIC18FLuis GonzalesNoch keine Bewertungen

- Memory Verification Using UVMDokument13 SeitenMemory Verification Using UVMAnji medidiNoch keine Bewertungen

- EE312 Experiment 07: Objective 1Dokument18 SeitenEE312 Experiment 07: Objective 1SAURABH RAJNoch keine Bewertungen

- Verilog ReferenceDokument77 SeitenVerilog ReferencePRANJAL SHRIVASTAVANoch keine Bewertungen

- 4-8 MarchDokument15 Seiten4-8 Marchadyadesai7Noch keine Bewertungen

- Developing Supercollider Unit Generators Under GNU/ Linux: Matthew John Yee-King June 4, 2007Dokument6 SeitenDeveloping Supercollider Unit Generators Under GNU/ Linux: Matthew John Yee-King June 4, 2007anil kisanNoch keine Bewertungen

- MicrocontrollerDokument20 SeitenMicrocontrollerugiyf eu6e6uNoch keine Bewertungen

- 12F683Dokument10 Seiten12F683Sanel LerićNoch keine Bewertungen

- TCP Client/Server Example in C Using SelectDokument5 SeitenTCP Client/Server Example in C Using Selectbingyang100% (1)

- National University of Science and Technology: Digital System Design (EE-421) Assignment #1Dokument23 SeitenNational University of Science and Technology: Digital System Design (EE-421) Assignment #1Tariq UmarNoch keine Bewertungen

- Cpu - Timer0 - Isr Initxintf: #Include "Dsp28X - Project.H"Dokument3 SeitenCpu - Timer0 - Isr Initxintf: #Include "Dsp28X - Project.H"RajendraNoch keine Bewertungen

- Lab0 CDokument5 SeitenLab0 CJorge Cruz Mancilla100% (1)

- EE5530 Lecture18 Complete SV TestBenchDokument45 SeitenEE5530 Lecture18 Complete SV TestBenchjithinkrishnac4474Noch keine Bewertungen

- Shortest Job First CDokument12 SeitenShortest Job First CfarhanhubbleNoch keine Bewertungen

- Whatsapp Bloker and Haking Tool KitDokument2.359 SeitenWhatsapp Bloker and Haking Tool KitAaditya KhannaNoch keine Bewertungen

- ELEC 3040/3050 Lab 4Dokument12 SeitenELEC 3040/3050 Lab 4rktiwary256034Noch keine Bewertungen

- ERC16064-1 DemoCode 4 Wire SPIDokument19 SeitenERC16064-1 DemoCode 4 Wire SPIDVTNoch keine Bewertungen

- uvm_config_dbDokument10 Seitenuvm_config_dbAFSAL ANoch keine Bewertungen

- LAB Manual: Disributed System Name:-Akshay Kumar Sem.: - 7Dokument10 SeitenLAB Manual: Disributed System Name:-Akshay Kumar Sem.: - 7loki gurjarNoch keine Bewertungen

- Verilog modules for 4-bit ALU, register, RAM and instruction decoderDokument6 SeitenVerilog modules for 4-bit ALU, register, RAM and instruction decoderRaffi SkNoch keine Bewertungen

- AT07347: Executing Code From RAM: SMART ARM-based MicrocontrollersDokument9 SeitenAT07347: Executing Code From RAM: SMART ARM-based MicrocontrollersUgur EwrNoch keine Bewertungen

- File KernelDokument189 SeitenFile KerneltegalexNoch keine Bewertungen

- Spi Protocol Verilog Code ExplanationDokument15 SeitenSpi Protocol Verilog Code Explanationgokul pNoch keine Bewertungen

- VerilogDokument22 SeitenVerilogSyurga FathonahNoch keine Bewertungen

- E:/#0-2S2017/#1-TEC - SELDI/SAP-02 - Projeto Forno MCU/SELDI - SAP-02 MCU - FW/Forno - DSET-SAP01 - 137-V1.X/forno.hDokument7 SeitenE:/#0-2S2017/#1-TEC - SELDI/SAP-02 - Projeto Forno MCU/SELDI - SAP-02 MCU - FW/Forno - DSET-SAP01 - 137-V1.X/forno.hVinícius Lopes Sampaio100% (1)

- Syn_fifo design and code for synchronous FIFODokument5 SeitenSyn_fifo design and code for synchronous FIFOVenky KoolchipNoch keine Bewertungen

- Debugging Techniques: 4/24/2012 1 Embedded System Design - IiDokument32 SeitenDebugging Techniques: 4/24/2012 1 Embedded System Design - IiCyril LeoNoch keine Bewertungen

- Errors and Exception Handling: Tim BissonDokument24 SeitenErrors and Exception Handling: Tim BissonRizwan MasoodiNoch keine Bewertungen

- Program Initial For CCS CommandDokument15 SeitenProgram Initial For CCS CommandThuhtay AgNoch keine Bewertungen

- Enc 28 J 60Dokument27 SeitenEnc 28 J 60Doanh Trần VănNoch keine Bewertungen

- ScriptDokument5 SeitenScriptSilviuDragomirNoch keine Bewertungen

- Riscv CoreDokument21 SeitenRiscv Coreapi-576930856Noch keine Bewertungen

- CodeDokument3 SeitenCodeSteve DicksonNoch keine Bewertungen

- LSU EE 3755 - Fall 2012 - Computer Organization Verilog Notes 4 - Synthesis Under ConstructionDokument20 SeitenLSU EE 3755 - Fall 2012 - Computer Organization Verilog Notes 4 - Synthesis Under ConstructionMerupu DebbaNoch keine Bewertungen

- EkrannDokument6 SeitenEkrannBubbleNoch keine Bewertungen

- UVM Testbench Architecture Example 1671715841Dokument20 SeitenUVM Testbench Architecture Example 1671715841Sumanish SharmaNoch keine Bewertungen

- Infecting Loadable Kernel Modules on Linux 2.6/3.0Dokument46 SeitenInfecting Loadable Kernel Modules on Linux 2.6/3.0Rishab ChoubeyNoch keine Bewertungen

- TCP - TX Process ModelDokument10 SeitenTCP - TX Process Model27YDCNoch keine Bewertungen

- Projet SEDokument9 SeitenProjet SEmaachoudouaa04Noch keine Bewertungen

- CCS C compiler Access to PIC internal peripherals summaryDokument14 SeitenCCS C compiler Access to PIC internal peripherals summaryEdmond LamNoch keine Bewertungen

- Data PliDokument3 SeitenData PliJesus NavasNoch keine Bewertungen

- Uvm TB Code 1672202269Dokument16 SeitenUvm TB Code 1672202269Sumanish SharmaNoch keine Bewertungen

- All VerilogLabsDokument74 SeitenAll VerilogLabssamruthNoch keine Bewertungen

- Prepostsynth FlowDokument17 SeitenPrepostsynth FlowveenaNoch keine Bewertungen

- DC1062 NotesDokument107 SeitenDC1062 Notessharedbrain1997Noch keine Bewertungen

- Oslab Inhouse ManualDokument37 SeitenOslab Inhouse ManualTanisha MaheshwariNoch keine Bewertungen

- Top Half Bottom HalfDokument13 SeitenTop Half Bottom HalfthulasiramaswamyNoch keine Bewertungen

- EE5530 Lecture16 Complete SV TestBenchDokument29 SeitenEE5530 Lecture16 Complete SV TestBenchjithinkrishnac4474Noch keine Bewertungen

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Von EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Noch keine Bewertungen

- PHASE5DRIVERDokument10 SeitenPHASE5DRIVER2vijNoch keine Bewertungen

- Phase 9 Testcase: Class Extends Constraint EndclassDokument2 SeitenPhase 9 Testcase: Class Extends Constraint Endclass2vijNoch keine Bewertungen

- Phase 8 Coverage: CoverpointDokument4 SeitenPhase 8 Coverage: Coverpoint2vijNoch keine Bewertungen

- D3400UM NT (En) 03Dokument136 SeitenD3400UM NT (En) 03mr. AdityaspontaneousNoch keine Bewertungen

- List of Vlsi Companies in BangloreDokument5 SeitenList of Vlsi Companies in Banglore2vijNoch keine Bewertungen

- Phase 3 ResetDokument4 SeitenPhase 3 Reset2vijNoch keine Bewertungen

- Phase 6 ReceiverDokument9 SeitenPhase 6 Receiver2vijNoch keine Bewertungen

- Sri YantraDokument1 SeiteSri Yantra2vijNoch keine Bewertungen

- Phase 4 PacketDokument10 SeitenPhase 4 Packet2vijNoch keine Bewertungen

- Linear TBDokument1 SeiteLinear TB2vijNoch keine Bewertungen

- Phase 1 Top: Note Guard - GuardDokument8 SeitenPhase 1 Top: Note Guard - Guard2vijNoch keine Bewertungen

- Phase 2 EnvironmentDokument7 SeitenPhase 2 Environment2vijNoch keine Bewertungen

- ConstructDokument103 SeitenConstruct2vijNoch keine Bewertungen

- Fun CoveDokument34 SeitenFun Cove2vijNoch keine Bewertungen

- Verilog SemaphoreDokument7 SeitenVerilog Semaphore2vijNoch keine Bewertungen

- Index: IntroductionsDokument24 SeitenIndex: Introductions2vijNoch keine Bewertungen

- White Gray Black BoxDokument1 SeiteWhite Gray Black Box2vijNoch keine Bewertungen

- Microsoft Word Faq in VlsDokument2 SeitenMicrosoft Word Faq in Vls2vijNoch keine Bewertungen

- Error Injuction: Value ErrorsDokument1 SeiteError Injuction: Value Errors2vijNoch keine Bewertungen

- CheckerDokument2 SeitenChecker2vijNoch keine Bewertungen

- DebuggingDokument8 SeitenDebugging2vijNoch keine Bewertungen

- Event Cycle SimulationDokument1 SeiteEvent Cycle Simulation2vijNoch keine Bewertungen

- Microsoft Word AptitudeDokument13 SeitenMicrosoft Word Aptitude2vijNoch keine Bewertungen

- About Code CoverageDokument9 SeitenAbout Code Coverage2vijNoch keine Bewertungen

- Microsoft Word PuzzelsDokument45 SeitenMicrosoft Word Puzzels2vijNoch keine Bewertungen

- Microsoft Word PuzzelsDokument45 SeitenMicrosoft Word Puzzels2vijNoch keine Bewertungen

- ECE3829 Class Examples: Binary To BCD ConverterDokument6 SeitenECE3829 Class Examples: Binary To BCD Converter2vijNoch keine Bewertungen