Beruflich Dokumente

Kultur Dokumente

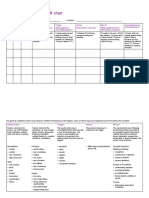

Interview Verification Questions

Hochgeladen von

jeerlamallaiahOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Interview Verification Questions

Hochgeladen von

jeerlamallaiahCopyright:

Verfügbare Formate

What is Constrained-Random Verification ?

Introduction

As ASIC and system-on-chip (SoC) designs continue to increase in size and complexity,

there is an equal or greater increase in the size of the verification effort required to achieve

functional coverage goals. This has created a trend in RTL verification techniques to employ

constrained-random verification, which shifts the emphasis from hand-authored tests to

utilization of compute resources. With the corresponding emergence of faster, more

complex bus standards to handle the massive volume of data traffic there has also been a

renewed significance for verification IP to speed the time taken to develop advanced

testbench environments that include randomization of bus traffic.

Directed-Test Methodology

Building a directed verification environment with a comprehensive set of directed tests is

extremely time-consuming and difficult. Since directed tests only cover conditions that have

been anticipated by the verification team, they do a poor job of covering corner cases. This

can lead to costly re-spins or, worse still, missed market windows.

Traditionally verification IP works in a directed-test environment by acting on specific

testbench commands such as read, write or burst to generate transactions for whichever

protocol is being tested. This directed traffic is used to verify that an interface behaves as

expected in response to valid transactions and error conditions. The drawback is that, in this

directed methodology, the task of writing the command code and checking the responses

across the full breadth of a protocol is an overwhelming task. The verification team

frequently runs out of time before a mandated tape-out date, leading to poorly tested

interfaces. However, the bigger issue is that directed tests only test for predicted behavior

and it is typically the unforeseen that trips up design teams and leads to extremely costly

bugs found in silicon.

Constrained-Random Verification Methodology

The advent of constrained-random verification gives verification engineers an effective

method to achieve coverage goals faster and also help find corner-case problems. It shifts

the emphasis from writing an enormous number of directed tests to writing a smaller set of

constrained-random scenarios that let the compute resources do the work. Coverage goals

are achieved not by the sheer weight of manual labor required to hand-write directed tests

but by the number of processors that can be utilized to run random seeds. This significantly

reduces the time required to achieve the coverage goals.

Scoreboards are used to verify that data has successfully reached its destination, while

monitors snoop the interfaces to provide coverage information. New or revised constraints

focus verification on the uncovered parts of the design under test. As verification

progresses, the simulation tool identifies the best seeds, which are then retained as

regression tests to create a set of scenarios, constraints, and seeds that provide high

coverage of the design.

Das könnte Ihnen auch gefallen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- 05.terrace PlanDokument1 Seite05.terrace PlanAnushka ThoratNoch keine Bewertungen

- Social Ethical ResponsibilitiesDokument16 SeitenSocial Ethical ResponsibilitiesRenz Daniel R. ElmidoNoch keine Bewertungen

- Solutions Manual For Power System Analysis and Design 5th Edition by Glover PDFDokument15 SeitenSolutions Manual For Power System Analysis and Design 5th Edition by Glover PDFFrederick Cas50% (2)

- Psychology Research Paper AppendixDokument6 SeitenPsychology Research Paper Appendixzrpcnkrif100% (1)

- IPCR Portfolio MOVs TrackerDokument10 SeitenIPCR Portfolio MOVs TrackerKris Tel Delapeña ParasNoch keine Bewertungen

- Verbs PrepositionsDokument4 SeitenVerbs PrepositionsKarina RossiNoch keine Bewertungen

- Behaviour Recording Star Chart 1Dokument5 SeitenBehaviour Recording Star Chart 1api-629413258Noch keine Bewertungen

- Gambaran Pengelolaan Emergency Kit (Trolley) Di Rumah Sakit Umum Daerah (RSUD) Dr. Hasri Ainun HabibieDokument10 SeitenGambaran Pengelolaan Emergency Kit (Trolley) Di Rumah Sakit Umum Daerah (RSUD) Dr. Hasri Ainun HabibieRutharyantiSihotangNoch keine Bewertungen

- Ciolli G ArberDokument41 SeitenCiolli G ArberAirB13Noch keine Bewertungen

- What Is Political EconomyDokument10 SeitenWhat Is Political EconomyayulatifahNoch keine Bewertungen

- National Emergency Medicine Board Review CourseDokument1 SeiteNational Emergency Medicine Board Review CourseJayaraj Mymbilly BalakrishnanNoch keine Bewertungen

- Writing Persuasive Texts PowerPoint Year 5 and Year 6 Microsoft PowerPoint 24562.potxDokument20 SeitenWriting Persuasive Texts PowerPoint Year 5 and Year 6 Microsoft PowerPoint 24562.potxMr. RamNoch keine Bewertungen

- Mathematics in The Modern World: CCGE - 104Dokument42 SeitenMathematics in The Modern World: CCGE - 104Mary Rose NaboaNoch keine Bewertungen

- Effects of Music Notation Software On Compositional Practices and OutcomeDokument271 SeitenEffects of Music Notation Software On Compositional Practices and OutcomeConstantin PopescuNoch keine Bewertungen

- The Importance of Teaching Communication in Dental Education. A Survey Amongst Dentists, Students and PatientsDokument6 SeitenThe Importance of Teaching Communication in Dental Education. A Survey Amongst Dentists, Students and Patientsandres castroNoch keine Bewertungen

- L&T Limited: About The CompanyDokument2 SeitenL&T Limited: About The CompanySai SanjeevareddyNoch keine Bewertungen

- Chitra NakshatraDokument12 SeitenChitra NakshatraSri KayNoch keine Bewertungen

- Pooja Raut Resume - Java DeveloperDokument3 SeitenPooja Raut Resume - Java DeveloperVaibhav PahuneNoch keine Bewertungen

- DROID: A Large-Scale In-The-Wild Robot Manipulation DatasetDokument21 SeitenDROID: A Large-Scale In-The-Wild Robot Manipulation Datasetxepit98367Noch keine Bewertungen

- SCOPUS Guide For Journal Editors ELSEVIERDokument75 SeitenSCOPUS Guide For Journal Editors ELSEVIERKhis HudhaNoch keine Bewertungen

- 2016 Tesol Convention Full Program PDFDokument268 Seiten2016 Tesol Convention Full Program PDFscribdnikolett100% (1)

- Indirect Questions Exercise 21847309256Dokument3 SeitenIndirect Questions Exercise 21847309256sirmaNoch keine Bewertungen

- Power BI Vs Tableau - Which One Is Right For YouDokument9 SeitenPower BI Vs Tableau - Which One Is Right For Youboo ajuNoch keine Bewertungen

- Demo June 5Dokument10 SeitenDemo June 5Mae Ann Carreon TrapalNoch keine Bewertungen

- Pe Assignment TopicsDokument2 SeitenPe Assignment Topicsapi-246838943Noch keine Bewertungen

- Health Committees ReportDokument6 SeitenHealth Committees ReportKailash NagarNoch keine Bewertungen

- Arrival of Guest: Script For Emcee in The Opening CeremonyDokument3 SeitenArrival of Guest: Script For Emcee in The Opening Ceremonyamelia golda100% (1)

- X & Y TheoryDokument16 SeitenX & Y Theoryanon_231950378100% (2)

- TheraDokument4 SeitenTheramaircusNoch keine Bewertungen

- Original PDF Management by Christopher P Neck PDFDokument41 SeitenOriginal PDF Management by Christopher P Neck PDFvan.weidert217100% (35)