Beruflich Dokumente

Kultur Dokumente

PCI Express

Hochgeladen von

Papillon BleuCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

PCI Express

Hochgeladen von

Papillon BleuCopyright:

Verfügbare Formate

PCI Express

1

PCI Express

Cet article ou cette section est actualiser.

Des passages de cet article sont obsoltes ou annoncent des vnements dsormais passs. Amliorez-le

[1]

ou discutez des points

vrifier.

Cet article ne cite pas suffisamment ses sources(novembre 2012).

Si vous disposez d'ouvrages ou d'articles de rfrence ou si vous connaissez des sites web de qualit traitant du thme abord ici, merci

de complter l'article en donnant les rfrences utiles sa vrifiabilit et en les liant la section Notes et rfrences (modifier l'article

[1]

).

Port PCI Express (de haut en bas : 4, 16, 1 et 16), compar au

traditionnel Port PCI 32-bit (en bas)

Le PCI Express, abrg PCI-E ou PCIe

(anciennement 3GIO, 3rd Generation Input/Output) est

un standard dvelopp par Intel et introduit en 2004. Il

spcifie un bus local srie ( bus PCI express ) et un

connecteur qui sert connecter des cartes dextension

sur la carte mre dun ordinateur. Il est destin

remplacer tous les connecteurs dextension dun PC,

dont le PCI et lAGP.

Une volution du PCI

Carte PCI express pleine hauteur

Un avantage du PCI Express est dtre driv de la norme PCI

(Peripheral Component Interconnect), ce qui permet aux constructeurs

dadapter simplement leurs cartes dextension existantes, puisque seule

la couche matrielle est modifier. Dautre part, il est suffisamment

rapide pour pouvoir remplacer non seulement le PCI classique mais

aussi lAGP, un port rapide pour cartes graphiques.

Contrairement au PCI qui est reli au southbridge de la carte mre, le

PCI Express est souvent disponible la fois au niveau du northbridge

et du southbridge, il a mme t rcemment intgr certains

microprocesseurs.

Alors que le PCI utilise un unique bus de largeur 32 bits bidirectionnel altern (half duplex) pour lensemble des

priphriques, le PCI Express utilise une interface srie (de largeur 1 bit) base de lignes bidirectionnelles. On

pourra ainsi parler dune carte mre possdant 20 lignes PCIe. Une ligne permet thoriquement des changes full

duplex 250Mo/s pour la version 1.1 du protocole. Les diffrents priphriques communiquent alors par change de

paquets et larbitrage du bus PCI est remplac par un commutateur. Le principe de fonctionnement est semblable de

la commutation de paquets selon un modle quatre couches :

couche logicielle : codage/dcodage des paquets de donnes.

PCI Express

2

couche transaction : rajout/suppression dun en-tte de dbut et dun en-tte de squencement ou de numrotation

du paquet.

couche liaison : rajout/suppression dun code de correction derreur (contrle de redondance cyclique).

couche physique : transmission du paquet (transmission srie point point).

On parle de ports PCIe 1, 2, 4, 8, 16 et 32 pour diffrencier les ports en fonction du nombre de connecteurs

de ligne dont ils disposent (respectivement 1, 2, 4, 8, 16 ou 32 lignes maximum). Un port 32 permet d'atteindre en

thorie un dbit de 8Go/s, soit 4 fois le dbit des ports AGP

[2]

.

Un port 16 par exemple peut ntre reli qu 8 lignes PCIe ; il devra tout de mme avoir un apport de puissance

lectrique ncessaire aux cartes 16. Une carte dextension 16 fonctionnera sur ce port (mais probablement avec

des performances non optimales), car le protocole PCIe prvoit la ngociation mutuelle du nombre de lignes

maximum supportes par les deux entits en relation. De mme, une carte (exemple : 1) peut tre connecte et

fonctionnera correctement sur un port plus grand (exemple : 1, 2, , 32)....

En 2007 est apparu la deuxime gnration de PCIe : gen 2.0. Cette version permet, entre autres, de passer le dbit

de 250Mo/s 500Mo/s par sens par lien (le dbit de la premire gnration gen 1.0 est doubl).

Cette mme anne a t publie, en fvrier, la norme External PCI Express 1.0 (ePCIe 1.0, Cabled PCIe 1.0)

,

, qui

permet de connecter des priphriques externes sur le bus PCIe, en utilisant une carte permettant de rediriger celui-ci

vers un connecteur externe. Le dbit de chaque ligne est limite 250Mo/s. Il existe des connecteurs et des cbles

pour les versions 1x, 4x, 8x et 16x du bus. Une volution vers des lignes 500Mo/s (comme le PCIe 2.0) est prvue

mais sans date annonce.

En 2010, PCI-SIG publie le cahier des charges du PCIe : gen 3.0. Le dbit est doubl 1000Mo/s grce une

augmentation de 60 % de la frquence qui est maintenant de 8GHz contre 5GHz pour la gen 2.0, mais aussi par un

encodage 128 bits/130 bits. Au lieu de consommer 20 % du dbit pour gen 2.0, cet encodage ne fait plus perdre que

1,6 % de la bande passante totale. Les premiers priphriques en PCIe 3.0 sont arrivs mi-2011, mais les cartes

graphiques exploitant cette interface ne sont arrives que dbut 2012.

Les bases de PCIe

Deux liens diffrentiels permettent l'change de donnes en mission (direct) et rception (revers) entre deux points

A & B.

'n' de ces liens constituent alors les chemins d'changes (lane) : PCIe 1x 2x 4x 8x.

Un signal mission ou rception est donc compos de deux fils en mode diffrentiel.

La combinaison des signaux mission et rception, soit 4 fils, constitue un chemin (lane).

Le regroupement de 'n' chemin reprsentent le lien PCIe nX.

Root composant permet l'accs au CPU, la mmoire ou tout autre priphrique.

Switch composant qui est optionnel permet le transfert PCIe entre end point sans passer par le root.

End point sont les priphriques d'changes.

Les donnes sont labores sous forme de paquets.

PCIe permet le contrle de flux, la QoS, la virtualisation de canaux, une latence prvisible...

Dbit et bande passante :

Une paire diffrentielle permet un dbit de 2,5 Gbit/s

PCIe 1x aura donc un dbit utile de (2,5 * 1000 * 2 * 8/10)/8 = 500Mo/s

Le facteur 2 vient du mode full duplex mission + rception.

Le facteur 8/10 est introduit par l'encodage 8B10B utilis.

PCIe suit le modle OSI :

La couche PHYsique permet le passage des paquets en un flux srie. (PCS/PMA layer)

PCI Express

3

La couche Data link permet la gestion de l'intgrit du lien (LCRC) et le contrle de flux.

La couche Transaction permet les accs plus haut niveau : mmoire, I/O...

Un calcul de CRC est effectue au niveau data link, il permet de vrifier l'intgrit des changes ce niveau.

Un deuxime calcul est ralis au niveau transactionnel, c'est un calcul de CRC de bout en bout (ECRC).

Si ECRC est faux, il est possible de demander de renvoyer nouveau le paquet.

Ceci est gr au niveau data link par un paquet DLLP (data link layer paquet) spcifique.

Les paquets de type DLLP sont transparents l'utilisateur qui ne voit que les paquets TLP en gnral.

DLLP sont donc des paquets de management (completion, configuration).

Software layer *data*

+-------------------+

| Transaction layer | **Header,*data*,ecrc**

+-------------------+

| Data Link Layer |

| | ***Sequence,**Header,*data*,ecrc**,lcrc***

+-------------------+

| PHYsical LAyer |

| | Start,***Sequence,**Header,*data*,ecrc**,lcrc***,End

+-------------------+

L'en tte du packet PCIe est de 3 4 mots de 32 bits.

La zone de charge utile, data, est de 0 1024 mots de 32 bits.

Un mot de 32 bits est appel Double Word (DW) sachant qu'un word est un double octet et qu'un octet est compos

de 8 bits.

Le niveau physique est compos des lments suivant :

circuit de rcupration d'horloge (cot rception), (PMA)

SERDES, (PMA)

embrouilleur, (PMA)

encodage 8B/10B. (PCS)

Le niveau data link dispose d'un "Replay Buffer" cot mission permettant de renvoyer le paquet lorsque le rcepteur

dtecte des erreurs.

Diffrents types de transactions existent :

lecture ou d'criture du plan mmoire,

configuration en phase d'initialisation,

messages permettant l'change d'vnements entre priphriques,

achvement (completion) de la transaction.

Deux types de transactions sont possibles : post ou non poste.

La transaction de type poste envoie un paquet et n'attend rien en retour : c'est comme une lettre la poste.

La transaction de type non poste qui attend un paquet d'achvement en retour : c'est comme une lettre en

recommande.

Une criture mmoire sera de type post alors qu'une lecture mmoire sera de type non post.

Si l'usage fait de PCIe est simple, l'utilisateur peut se brancher au niveau transactionnel.

Il faudra alors grer les paquets TLP (transaction layer paquet) en mission rception.

Pour des usages plus pousss, des IP existent (cas d'un design FPGA).

Cette sur couche grera par exemple des accs mmoire direct DMA en mode "scatter gather" ventuellement.

PCI Express

4

PCI Express 2

Article dtaill : PCI Express 2.

PCI Express 3

Cette section est vide, insuffisamment dtaille ou incomplte. Votre aide

[1]

est la bienvenue !

Notes et rfrences

[1] http:/ / fr. wikipedia. org/ w/ index. php?title=PCI_Express& action=edit

[2] commentcamarche.net (http:/ / www. commentcamarche. net/ contents/ pc/ pci-express. php3)

Portail de linformatique

Sources et contributeurs de larticle

5

Sources et contributeurs de larticle

PCI Express Source: http://fr.wikipedia.org/w/index.php?oldid=103838992 Contributeurs: A3 nm, ABACA, AFAccord, Archeos, Arm@nd, Arnaud.Serander, ArsniureDeGallium, Axou,

Belgavox, Binabik155, Bub's, Cgsyannick, Dadu, Ecclecticus, Eutvakerre, Freewol, Ggal, Isaac Sanolnacov, JackPotte, Jona, Julien06200, Kelson, Kyro, LYV, Madlozoz, MetalGearLiquid,

Mikay, NaSH, Nataraja, Nono64, Noritaka666, Oz, Pautard, Phe, Rohanec, Salam32, Sangen48, Sebleouf, Sherbrooke, Simorou, Speculos, Tafreser, Thesupermat, W'rkncacnter, Ygonaar,

Yves-Laurent, Zetud, 45 modifications anonymes

Source des images, licences et contributeurs

Fichier:Out of date clock icon.svg Source: http://fr.wikipedia.org/w/index.php?title=Fichier:Out_of_date_clock_icon.svg Licence: GNU Lesser General Public License Contributeurs:

Composition by Tkgd2007. I used and modified images from the alternative sources listed below.

Fichier:Question book-4.svg Source: http://fr.wikipedia.org/w/index.php?title=Fichier:Question_book-4.svg Licence: GNU Free Documentation License Contributeurs: Tkgd2007

Image:PCIExpress.jpg Source: http://fr.wikipedia.org/w/index.php?title=Fichier:PCIExpress.jpg Licence: GNU Free Documentation License Contributeurs: FxJ, GMLSX, GreyCat, Jokes

Free4Me, Jona, Mentifisto, Paxan, Trelio, Wouterhagens, 16 modifications anonymes

Fichier:PCIe card full height.jpg Source: http://fr.wikipedia.org/w/index.php?title=Fichier:PCIe_card_full_height.jpg Licence: Creative Commons Attribution-Sharealike 3.0 Contributeurs:

User:Bubba73

Fichier:Crystal mycomputer.png Source: http://fr.wikipedia.org/w/index.php?title=Fichier:Crystal_mycomputer.png Licence: inconnu Contributeurs: Dake, Rocket000

Licence

Creative Commons Attribution-Share Alike 3.0

//creativecommons.org/licenses/by-sa/3.0/

Das könnte Ihnen auch gefallen

- Expose Ipv6Dokument73 SeitenExpose Ipv6Doudou Gaye83% (6)

- Annales Maths Cm2Dokument58 SeitenAnnales Maths Cm2KOUAO Guy Roger100% (1)

- Facture Proforma Gilles-RichardDokument1 SeiteFacture Proforma Gilles-RichardPapillon BleuNoch keine Bewertungen

- Configuration CiscoDokument16 SeitenConfiguration CiscoConso KbdNoch keine Bewertungen

- Support Cours BusDokument6 SeitenSupport Cours BusmedNoch keine Bewertungen

- Chapitre 0 Protocole-Ipv6Dokument9 SeitenChapitre 0 Protocole-Ipv6Alain priceNoch keine Bewertungen

- Chap 2 Composants de L'ordinateurDokument61 SeitenChap 2 Composants de L'ordinateursr6662146Noch keine Bewertungen

- Chap 3 - Couche RéseauDokument166 SeitenChap 3 - Couche RéseauFerdaous HdioudNoch keine Bewertungen

- Chap5 BusDokument6 SeitenChap5 Bushoummani ismailNoch keine Bewertungen

- TD2 DatagrammeIPv6Dokument3 SeitenTD2 DatagrammeIPv6Ahmed MaalejNoch keine Bewertungen

- Protocoles RéseauDokument44 SeitenProtocoles RéseauDavid EwanNoch keine Bewertungen

- Chapitre IiDokument8 SeitenChapitre IiMOMONoch keine Bewertungen

- Chat GPTDokument11 SeitenChat GPTFabrice AMOULENoch keine Bewertungen

- Chapitre N27Dokument11 SeitenChapitre N27Bet EdeNoch keine Bewertungen

- Stage EteDokument33 SeitenStage EteAtef Belhaj AlayaNoch keine Bewertungen

- 007.PDF Texte PDFDokument5 Seiten007.PDF Texte PDFMerit KhaledNoch keine Bewertungen

- Chapitre 6Dokument23 SeitenChapitre 6Chiraz Ben BoubakerNoch keine Bewertungen

- TD 1: Modèles en Couches (OSI Et TCP/IP) : Exercice 1Dokument4 SeitenTD 1: Modèles en Couches (OSI Et TCP/IP) : Exercice 1Okay_404Noch keine Bewertungen

- Chapitre 5 Couche RéseauDokument20 SeitenChapitre 5 Couche RéseauGhada Ben MabroukNoch keine Bewertungen

- Les Bus: Bus Et Transports en CommunDokument11 SeitenLes Bus: Bus Et Transports en Communtendresseirung919Noch keine Bewertungen

- Lolut Utbm Ipv6 PRINTDokument18 SeitenLolut Utbm Ipv6 PRINTbeguenineNoch keine Bewertungen

- Cours BusDokument121 SeitenCours BusMoh HbNoch keine Bewertungen

- 14-Concepts de RoutageDokument59 Seiten14-Concepts de RoutageAmine XGhost MidoNoch keine Bewertungen

- Routage RipDokument8 SeitenRoutage RipFouad ElhajjiNoch keine Bewertungen

- Ipv6 Et 6lowpanDokument15 SeitenIpv6 Et 6lowpanNaziha AbNoch keine Bewertungen

- IPv 6Dokument79 SeitenIPv 6Rainx Rain0% (1)

- PPP MultilinkDokument9 SeitenPPP MultilinkGossan AnicetNoch keine Bewertungen

- CHAPITRE 6 Protocole IPDokument101 SeitenCHAPITRE 6 Protocole IPJason ludovic Nguema ondoNoch keine Bewertungen

- Exposer Sur Le Bus D'instrumentation Et Le Bus de DonnéeDokument17 SeitenExposer Sur Le Bus D'instrumentation Et Le Bus de DonnéeBelhamidi Mohammed HoussameNoch keine Bewertungen

- PortDokument25 SeitenPortGanesh PaulNoch keine Bewertungen

- Chapitre2 - Pile de Protocoles TCP IP Et Adressage IP - MBDDokument29 SeitenChapitre2 - Pile de Protocoles TCP IP Et Adressage IP - MBDSarah IBNoch keine Bewertungen

- TP 13 Ipv6Dokument16 SeitenTP 13 Ipv6julesNoch keine Bewertungen

- IPv6 13 14Dokument52 SeitenIPv6 13 14amirdgNoch keine Bewertungen

- CHAPITRE 1 Protocole IPDokument76 SeitenCHAPITRE 1 Protocole IPJason ludovic Nguema ondoNoch keine Bewertungen

- Chapitre 1 EtudiantDokument4 SeitenChapitre 1 EtudiantChristianNoch keine Bewertungen

- Synthèse Des ExposésDokument44 SeitenSynthèse Des ExposésMEDFEJJI100% (1)

- Préparation Exam Final CCNA 4 - 2020Dokument8 SeitenPréparation Exam Final CCNA 4 - 2020best leagueNoch keine Bewertungen

- 0287 Cours Adressage Ipv4Dokument6 Seiten0287 Cours Adressage Ipv4Rodrigue ChuingouaNoch keine Bewertungen

- Travail Pratique Protocoles Réseaux LOUGA 1Dokument16 SeitenTravail Pratique Protocoles Réseaux LOUGA 1KasudiNoch keine Bewertungen

- Travail Pratique Protocoles Réseaux13 LOUGADokument16 SeitenTravail Pratique Protocoles Réseaux13 LOUGAKasudiNoch keine Bewertungen

- Cours - Protocole IPv6Dokument41 SeitenCours - Protocole IPv6papematarsarrNoch keine Bewertungen

- 8 Encapsulation PDFDokument12 Seiten8 Encapsulation PDFIMENNoch keine Bewertungen

- Chapter 5Dokument33 SeitenChapter 5Hamma DaouthiNoch keine Bewertungen

- Ospf RoutageDokument29 SeitenOspf RoutageChawki TrabelsiNoch keine Bewertungen

- Texas Instruments A Introduit Le DSP TMS32010 de Première Génération en 1982Dokument26 SeitenTexas Instruments A Introduit Le DSP TMS32010 de Première Génération en 1982hafsaNoch keine Bewertungen

- Audio IpDokument33 SeitenAudio IpChaabane FaouziNoch keine Bewertungen

- Exercice Modèle OSI/TCPIPDokument6 SeitenExercice Modèle OSI/TCPIPWafo KamgueNoch keine Bewertungen

- ICND1 0x0a IPv6 SynthétiqueDokument100 SeitenICND1 0x0a IPv6 SynthétiqueFrançois-Emmanuel GoffinetNoch keine Bewertungen

- 4649 Mpls Faq 4649Dokument7 Seiten4649 Mpls Faq 4649ndeyematy.611Noch keine Bewertungen

- Interview Questions Booklet Design V4Dokument31 SeitenInterview Questions Booklet Design V4Høussàéîn Bèn MéssâõûdNoch keine Bewertungen

- TP-4 Couche Réseau - Routage Et NAT Objectifs Pédagogiques: Manuels/doc - Packettracer PDFDokument10 SeitenTP-4 Couche Réseau - Routage Et NAT Objectifs Pédagogiques: Manuels/doc - Packettracer PDFpierreNoch keine Bewertungen

- Point-to-Point Tunneling ProtocolDokument3 SeitenPoint-to-Point Tunneling ProtocolMALEKPARISNoch keine Bewertungen

- Communication Avec MatlabDokument9 SeitenCommunication Avec Matlabben boubakerNoch keine Bewertungen

- Inf1160 ProtocolesreseauxDokument28 SeitenInf1160 ProtocolesreseauxIssam ChawkiNoch keine Bewertungen

- Canal de CommunicationDokument19 SeitenCanal de CommunicationBonjourNoch keine Bewertungen

- Initiation Aux Microcontrôleurs dsPIC30FDokument10 SeitenInitiation Aux Microcontrôleurs dsPIC30Fanon_72023590100% (1)

- Chapitre 2 - Connexions Point À PointDokument42 SeitenChapitre 2 - Connexions Point À PointAbdenour MohammediNoch keine Bewertungen

- Chap 1. Généralités Sur Le RoutageDokument5 SeitenChap 1. Généralités Sur Le RoutageArnaud Diffo Tchinda50% (2)

- tp1 LP CorDokument6 Seitentp1 LP Corchkairi87Noch keine Bewertungen

- Architecture L2TPDokument18 SeitenArchitecture L2TProme1506871999Noch keine Bewertungen

- Introduction À L'implantation Des Réseaux InterconnectésDokument6 SeitenIntroduction À L'implantation Des Réseaux InterconnectésjeffNoch keine Bewertungen

- Python pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasVon EverandPython pour Débutants : Guide Complet pour Apprendre la Programmation Pas à PasNoch keine Bewertungen

- Extrait CM2 Maths Avec Devoirs PDFDokument18 SeitenExtrait CM2 Maths Avec Devoirs PDFDame DiopNoch keine Bewertungen

- Invitation EIED BanguiDokument1 SeiteInvitation EIED BanguiPapillon BleuNoch keine Bewertungen

- G14. Les Propositions Indépendantes Coordonnées Ou JuxtaposéesDokument6 SeitenG14. Les Propositions Indépendantes Coordonnées Ou JuxtaposéesPapillon BleuNoch keine Bewertungen

- PDFDokument153 SeitenPDFDame DiopNoch keine Bewertungen

- 513 WorkbenchDokument36 Seiten513 WorkbenchPapillon BleuNoch keine Bewertungen

- Les Droits Et Taxes de Douanes en CEMACDokument3 SeitenLes Droits Et Taxes de Douanes en CEMACPapillon Bleu100% (1)

- Mail Confirmation 200ko Pret RoyDokument1 SeiteMail Confirmation 200ko Pret RoyPapillon BleuNoch keine Bewertungen

- P2 11 SihDokument28 SeitenP2 11 SihPapillon BleuNoch keine Bewertungen

- Cas Corrig - 01 - Pratique de La DouaneDokument3 SeitenCas Corrig - 01 - Pratique de La DouanePapillon BleuNoch keine Bewertungen

- Commande CamerounDokument1 SeiteCommande CamerounPapillon BleuNoch keine Bewertungen

- Gérez Vos Réservations - BookingDokument2 SeitenGérez Vos Réservations - BookingPapillon BleuNoch keine Bewertungen

- Proforma Billet Rapat Famille NGAMA PIAULT DoualaDokument2 SeitenProforma Billet Rapat Famille NGAMA PIAULT DoualaPapillon BleuNoch keine Bewertungen

- Demande RapatriementDokument1 SeiteDemande RapatriementPapillon BleuNoch keine Bewertungen

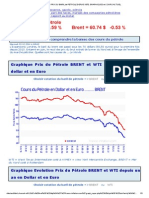

- Evolution Prix Du Baril de Petrole Depuis 1970, Graphiques Et Cours ActuelDokument3 SeitenEvolution Prix Du Baril de Petrole Depuis 1970, Graphiques Et Cours ActuelPapillon BleuNoch keine Bewertungen

- Gérez Vos Réservations - BookingDokument2 SeitenGérez Vos Réservations - BookingPapillon BleuNoch keine Bewertungen

- Manicore - Comment A Évolué Le Prix Du Pétrole Depuis 1860Dokument6 SeitenManicore - Comment A Évolué Le Prix Du Pétrole Depuis 1860Papillon BleuNoch keine Bewertungen

- Pubs PDF ATR10 ATR10Dokument44 SeitenPubs PDF ATR10 ATR10Papillon BleuNoch keine Bewertungen

- Jocely YambogazaDokument1 SeiteJocely YambogazaPapillon BleuNoch keine Bewertungen

- Jocely YambogazaDokument1 SeiteJocely YambogazaPapillon BleuNoch keine Bewertungen

- Gérez Vos Réservations - BookingDokument2 SeitenGérez Vos Réservations - BookingPapillon BleuNoch keine Bewertungen

- Code Du Lit ConjugalDokument1 SeiteCode Du Lit ConjugalPapillon Bleu100% (2)

- Lms Shipping Cameroun - ICiDokument1 SeiteLms Shipping Cameroun - ICiPapillon BleuNoch keine Bewertungen

- RequisitionDokument1 SeiteRequisitionPapillon BleuNoch keine Bewertungen

- Proforma Klass ComputersDokument1 SeiteProforma Klass ComputersPapillon BleuNoch keine Bewertungen

- Economie Et Organisation Des EntreprisesDokument48 SeitenEconomie Et Organisation Des EntreprisesModou Diop100% (1)

- Lettre CV Juriste Droit Social Debutant 0Dokument2 SeitenLettre CV Juriste Droit Social Debutant 0Papillon BleuNoch keine Bewertungen

- Devis Alim HP - Bsic-BanguiDokument1 SeiteDevis Alim HP - Bsic-BanguiPapillon BleuNoch keine Bewertungen

- CEMAC - Tarif Des DouanesDokument9 SeitenCEMAC - Tarif Des Douanesth3f5Noch keine Bewertungen

- MAH4444Dokument139 SeitenMAH4444بلقاسم جلاليNoch keine Bewertungen

- Cours de Fiscalitã© Internationale 2022 2023 PDFDokument164 SeitenCours de Fiscalitã© Internationale 2022 2023 PDFSirine JabesNoch keine Bewertungen

- Le Contrat de Transport International 2022Dokument10 SeitenLe Contrat de Transport International 2022Amina ChiahiNoch keine Bewertungen

- Formation Methode HaccpDokument111 SeitenFormation Methode HaccpTIEBE SERGESNoch keine Bewertungen

- TEST Connaissance PLSQLDokument3 SeitenTEST Connaissance PLSQLFORMATION ORADISTNoch keine Bewertungen

- 2020 Sustainable Agriculture Standard - Farm Requirements - Rainforest Alliance FRDokument91 Seiten2020 Sustainable Agriculture Standard - Farm Requirements - Rainforest Alliance FRkouame gerard kouameNoch keine Bewertungen

- Unitrac 92-102 FRDokument256 SeitenUnitrac 92-102 FRjean talus100% (1)

- VOTRE ORDINATEUR 03 1984-01-02 (Acme)Dokument92 SeitenVOTRE ORDINATEUR 03 1984-01-02 (Acme)Taranis35Noch keine Bewertungen

- MS311 MS391Dokument94 SeitenMS311 MS391Bruno DenolleNoch keine Bewertungen

- Document 575912Dokument142 SeitenDocument 575912Abass DialloNoch keine Bewertungen

- Organigramme Universite Bordeaux MontaigneDokument12 SeitenOrganigramme Universite Bordeaux MontaigneingridguerreroocampoNoch keine Bewertungen

- Cat Moteurs BeDokument196 SeitenCat Moteurs Benabil loutfi100% (1)

- Myfrenchbank Christophe CarreDokument1 SeiteMyfrenchbank Christophe CarreyomanhcNoch keine Bewertungen

- La Phrase - La Forme Affirmative Et La Forme Négative - MaxicoursDokument4 SeitenLa Phrase - La Forme Affirmative Et La Forme Négative - MaxicoursTOUTA TOTONoch keine Bewertungen

- Plaquette Ouvrages Ralentissement Crues VilaineDokument6 SeitenPlaquette Ouvrages Ralentissement Crues Vilainemetalika_1981Noch keine Bewertungen

- Examen Ro 21Dokument1 SeiteExamen Ro 21صنع في المنزل Made at homeNoch keine Bewertungen

- Druanti The Arch-Revenant: Liste de CadeauxDokument1 SeiteDruanti The Arch-Revenant: Liste de CadeauxAntoine ForitesNoch keine Bewertungen

- Chapitre 7 Les Couts LogistiquesDokument2 SeitenChapitre 7 Les Couts LogistiquesMohamedNoch keine Bewertungen

- Guide EasyctnDokument13 SeitenGuide EasyctnKossi Norbert LawadanNoch keine Bewertungen

- 70 Idées de Business en 2020Dokument5 Seiten70 Idées de Business en 2020rojo razanadrakotoNoch keine Bewertungen

- Modele Acte D'engagementDokument2 SeitenModele Acte D'engagementzak.sb22Noch keine Bewertungen

- Le Chauffage Par InductionDokument4 SeitenLe Chauffage Par InductionboboNoch keine Bewertungen

- Note de Calcul NabDokument5 SeitenNote de Calcul NabLyes AlgerianoNoch keine Bewertungen

- Ci Etec NigerDokument44 SeitenCi Etec NigerSayabou MahamadouNoch keine Bewertungen

- Rapport 1Dokument13 SeitenRapport 1Safwen BoufaidNoch keine Bewertungen

- Entre TienDokument16 SeitenEntre TienKawtarSoloNoch keine Bewertungen

- Support de Cours TSQL 2000Dokument20 SeitenSupport de Cours TSQL 2000Joom LANoch keine Bewertungen

- Parlons RH Barometre de L Experience Collaobrateur Edition 2021Dokument22 SeitenParlons RH Barometre de L Experience Collaobrateur Edition 2021fatima elyaakoubiNoch keine Bewertungen

- Cours Droit GOZZIDokument32 SeitenCours Droit GOZZINicoleta BusuiocNoch keine Bewertungen

- Cps MarchéDokument22 SeitenCps Marchéyoussef benaniNoch keine Bewertungen