Beruflich Dokumente

Kultur Dokumente

RP6 Data Sheet - 74HC/HCT03 Quad 2-Input NAND Gate

Hochgeladen von

Nader_Al_Qahf0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

41 Ansichten8 Seiten74HC/HCT03

Quad 2-input NAND gate

For a complete data sheet, please also download:

• The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications • The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

• The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

-FEATURES

-GENERAL DESCRIPTION

-ORDERING INFORMATION

-PIN DESCRIPTION

Originaltitel

RP6 Data sheet - 74HC/HCT03 Quad 2-input NAND gate

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument melden74HC/HCT03

Quad 2-input NAND gate

For a complete data sheet, please also download:

• The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications • The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

• The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

-FEATURES

-GENERAL DESCRIPTION

-ORDERING INFORMATION

-PIN DESCRIPTION

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

41 Ansichten8 SeitenRP6 Data Sheet - 74HC/HCT03 Quad 2-Input NAND Gate

Hochgeladen von

Nader_Al_Qahf74HC/HCT03

Quad 2-input NAND gate

For a complete data sheet, please also download:

• The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications • The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

• The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

-FEATURES

-GENERAL DESCRIPTION

-ORDERING INFORMATION

-PIN DESCRIPTION

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 8

Product specication

File under Integrated Circuits, IC06

December 1990

INTEGRATED CIRCUITS

74HC/HCT03

Quad 2-input NAND gate

For a complete data sheet, please also download:

The IC06 74HC/HCT/HCU/HCMOS Logic Family Specifications

The IC06 74HC/HCT/HCU/HCMOS Logic Package Information

The IC06 74HC/HCT/HCU/HCMOS Logic Package Outlines

December 1990 2

Philips Semiconductors Product specication

Quad 2-input NAND gate 74HC/HCT03

FEATURES

Level shift capability

Output capability: standard (open drain)

I

CC

category: SSI

GENERAL DESCRIPTION

The 74HC/HCT03 are high-speed Si-gate CMOS devices

and are pin compatible with low power Schottky TTL

(LSTTL). They are specified in compliance with JEDEC

standard no. 7A.

The 74HC/HCT03 provide the 2-input NAND function.

The 74HC/HCT03 have open-drain N-transistor outputs,

which are not clamped by a diode connected to V

CC

. In

the OFF-state, i.e. when one input is LOW, the output

may be pulled to any voltage between GND and V

Omax

.

This allows the device to be used as a LOW-to-HIGH or

HIGH-to-LOW level shifter. For digital operation and

OR-tied output applications, these devices must have a

pull-up resistor to establish a logic HIGH level.

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25 C; t

r

= t

f

= 6 ns

Notes

1. C

PD

is used to determine the dynamic power dissipation (P

D

in W):

P

D

= C

PD

V

CC

2

f

i

+ (C

L

V

CC

2

f

o

) + (V

O

2

/R

L

) duty factor LOW, where:

f

i

= input frequency in MHz

f

o

= output frequency in MHz

V

O

= output voltage in V

C

L

= output load capacitance in pF

V

CC

= supply voltage in V

R

L

= pull-up resistor in M

(C

L

V

CC

2

f

o

) = sum of outputs

(V

O

2

/R

L

) = sum of outputs

2. For HC the condition is V

I

= GND to V

CC

For HCT the condition is V

I

= GND to V

CC

1.5 V

3. The given value of C

PD

is obtained with:

C

L

= 0 pF and R

L

=

ORDERING INFORMATION

See 74HC/HCT/HCU/HCMOS Logic Package Information.

SYMBOL PARAMETER CONDITIONS

TYPICAL

UNIT

HC HCT

t

PZL

/ t

PLZ

propagation delay C

L

= 15 pF; R

L

= 1 k; V

CC

= 5 V 8 10 ns

C

I

input capacitance 3.5 3.5 pF

C

PD

power dissipation capacitance per gate notes 1, 2 and 3 4.0 4.0 pF

December 1990 3

Philips Semiconductors Product specication

Quad 2-input NAND gate 74HC/HCT03

PIN DESCRIPTION

PIN NO. SYMBOL NAME AND FUNCTION

1, 4, 9, 12 1A to 4A data inputs

2, 5, 10, 13 1B to 4B data inputs

3, 6, 8, 11 1Y to 4Y data outputs

7 GND ground (0 V)

14 V

CC

positive supply voltage

Fig.1 Pin configuration. Fig.2 Logic symbol. Fig.3 IEC logic symbol.

Fig.4 Functional diagram. Fig.5 Logic diagram (one gate).

FUNCTION TABLE

Note

1. H = HIGH voltage level

L = LOW voltage level

Z = high impedance OFF-state

INPUTS OUTPUT

nA nB nY

L

L

H

H

L

H

L

H

Z

Z

Z

L

December 1990 4

Philips Semiconductors Product specication

Quad 2-input NAND gate 74HC/HCT03

RATINGS

Limiting values in accordance with the Absolute Maximum System (IEC 134)

Voltages are referenced to GND (ground = 0 V)

SYMBOL PARAMETER MIN. MAX. UNIT CONDITIONS

V

CC

DC supply voltage 0.5 +7 V

V

O

DC output voltage 0.5 +7 V

I

IK

DC input diode current 20 mA for V

I

< 0.5 V or V

I

> V

CC

+ 0.5 V

I

OK

DC output diode current 20 mA for V

O

< 0.5 V

I

O

DC output sink current 25 mA for 0.5 V < V

O

I

CC

;

I

GND

DC VCC or GND current 50 mA

T

stg

storage temperature range 65 +150 C

P

tot

power dissipation per package for temperature range; 40 to +125 C

74HC/HCT

plastic DIL 750 mW above +70 C: derate linearly with 12 mW/K

plastic mini-pack (SO) 500 mW above +70 C: derate linearly with 8 mW/K

December 1990 5

Philips Semiconductors Product specication

Quad 2-input NAND gate 74HC/HCT03

DC CHARACTERISTICS FOR 74HC

For the DC characteristics see 74HC/HCT/HCU/HCMOS Logic Family Specifications, except that the V

OH

values are

not valid for open drain. They are replaced by I

OZ

as given below.

Output capability: standard (open drain), excepting V

OH

I

CC

category: SSI

Voltages are referenced to GND (ground = 0 V)

Note

1. The maximum operating output voltage (V

O(max)

) is 6.0 V.

AC CHARACTERISTICS FOR 74HC

GND = 0 V; t

r

= t

f

= 6 ns; C

L

= 50 pF

SYMBOL PARAMETER

T

amb

(C) TEST CONDITIONS

74HC

UNIT V

CC

(V)

V

I

OTHER

+25 40 to +85 40 to +125

min. typ. max. min. max. min. max.

I

OZ

HIGH level output

leakage current 0.5 5.0 10.0 A

2.0

to

6.0

V

IL

V

O

= V

O(max)

(1)

or GND

SYMBOL PARAMETER

T

amb

(C) TEST CONDITIONS

74HC

UNIT

V

CC

(V)

WAVEFORMS

+25 40 to +85 40 to +125

min. typ. max. min. max. min. max.

t

PZL

/

t

PLZ

propagation delay

nA, nB to nY

28

10

8

95

19

16

120

24

20

145

29

25

ns

2.0

4.5

6.0

Fig.6

t

THL

output transition time 19

7

6

75

15

13

95

19

16

110

22

19

ns 2.0

4.5

6.0

Fig.6

December 1990 6

Philips Semiconductors Product specication

Quad 2-input NAND gate 74HC/HCT03

DC CHARACTERISTICS FOR 74HCT

For the DC characteristics see 74HC/HCT/HCU/HCMOS Logic Family Specifications, except that the V

OH

values are

not valid for open drain. They are replaced by I

OZ

as given below.

Output capability: standard (open drain), excepting V

OH

I

CC

category: SSI

Voltages are referenced to GND (ground = 0 V)

Note

1. The maximum operating output voltage (V

O(max)

) is 6.0 V.

Note to HCT types

The value of additional quiescent supply current (I

CC

) for a unit load of 1 is given in the family specifications.

To determine I

CC

per input, multiply this value by the unit load coefficient shown in the table below.

AC CHARACTERISTICS FOR 74HCT

GND = 0 V; t

r

= t

f

= 6 ns; C

L

= 50 pF

SYMBOL PARAMETER

T

amb

(C)

UNIT

TEST CONDITIONS

74HCT

V

CC

(V)

V

I

OTHER +25 40 to +85 40 to +125

min. typ. max. min. max. min. max.

I

OZ

HIGH level output

leakage current

0.5 5.0 10.0 A

4.5

to

5.5

V

IL

V

O

= V

O(max)

(1)

or GND

INPUT UNIT LOAD COEFFICIENT

nA, nB 1.0

SYMBOL PARAMETER

T

amb

(C) TEST CONDITIONS

74HCT

UNIT

V

CC

(V)

WAVEFORMS

+25 40 to +85 40 to +125

min. typ. max. min. max. min. max.

t

PZL

/ t

PLZ

propagation delay

nA, nB, to nY

12 24 30 36 ns 4.5 Fig.6

t

THL

output transition time 7 15 19 22 ns 4.5 Fig.6

December 1990 7

Philips Semiconductors Product specication

Quad 2-input NAND gate 74HC/HCT03

AC WAVEFORMS

Fig.6 Waveforms showing the input (nA, nB) to output (nY) propagation delays and the output transition times.

HC: V

M

= 50%; V

I

= GND to V

CC

HCT: V

M

= 1.3 V; V

I

= GND to 3 V.

TEST CIRCUIT AND WAVEFORMS

Fig.7 Test circuit (open drain) Fig.8 Input pulse definitions.

Denitions for Figs. 7, 8:

C

L

= load capacitance including jig and probe

capacitance

(see AC CHARACTERISTICS for values).

R

T

= termination resistance should be equal to the

output impedance Z

O

of the pulse generator.

t

r

= t

f

= 6 ns; when measuring f

max

, there is no

constraint on t

r

, t

f

with 50% duty factor.

FAMILY AMPLITUDE V

M

t

r

; t

f

f

max

;

PULSE

WIDTH

OTHER

74HC V

CC

50% < 2 ns 6 ns

74HCT 3.0 V 1.3 V < 2 ns 6 ns

December 1990 8

Philips Semiconductors Product specication

Quad 2-input NAND gate 74HC/HCT03

APPLICATION INFORMATION

Notes to Figs 9 and 10

If V

P

V

CC

(R) > 0.5 V a positive current will flow into the receiver (as described in the USER GUIDE; input/output

protection), this will not affect the receiver provided the current does not exceed 20 mA. At V

CC

< 4.5 V, R

ON (max)

is not

guaranteed; R

ON(max)

can be estimated using Figs 33 and 34 in the USER GUIDE.

Note to Application information

All values given are typical unless otherwise specified.

PACKAGE OUTLINES

See 74HC/HCT/HCU/HCMOS Logic Package Outlines.

Fig.9 Pull-up configuration.

(b) (a)

(1) R

ON(max)

= 0.26 V / 4 mA = 65 (at 25 C)

Fig.10 Minimum resistive load as a function of the pull-up voltage.

(1) V

CC

(R) = 2.0 V; V

IL

= 0.5 V.

(2) V

CC

(R) = 5.0 V; V

IL

= 0.8 V.

(3) V

CC

(R) = 4.5 V; V

IL

= 1.35 V.

(4) V

CC

(R) = 6.0 V; V

IL

= 1.8 V.

Das könnte Ihnen auch gefallen

- DElta HMI PDFDokument4 SeitenDElta HMI PDFNader_Al_QahfNoch keine Bewertungen

- Induction HeatingDokument5 SeitenInduction HeatingPavan KumarNoch keine Bewertungen

- PLC Application Exercises and Solutions for Industrial Automation TrainingDokument93 SeitenPLC Application Exercises and Solutions for Industrial Automation TrainingMuhammadSyafiuddin100% (1)

- Delta Ia-Plc DVP TP C en 20170321Dokument48 SeitenDelta Ia-Plc DVP TP C en 20170321vacsaaNoch keine Bewertungen

- PID Controller of Speed and Torque of ServoMotor Using MATLABDokument4 SeitenPID Controller of Speed and Torque of ServoMotor Using MATLABNader_Al_QahfNoch keine Bewertungen

- PDF Ebooks - Org 03011738Gk4X6Dokument18 SeitenPDF Ebooks - Org 03011738Gk4X6Nader_Al_QahfNoch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- 7W AM TransmitterDokument4 Seiten7W AM TransmitterCamanhoNoch keine Bewertungen

- Chapter 10 Digital Integrated CircuitsDokument57 SeitenChapter 10 Digital Integrated CircuitsMubeen NaeemNoch keine Bewertungen

- EET 3350 Digital Systems Design Textbook: John Wakerly: CountersDokument64 SeitenEET 3350 Digital Systems Design Textbook: John Wakerly: Countersfrg2410Noch keine Bewertungen

- Expt 8 EDC-2Dokument8 SeitenExpt 8 EDC-2samarthNoch keine Bewertungen

- Lab 7Dokument3 SeitenLab 7Walid Mohammed Suliman100% (1)

- Lab 9: O A: Perational MplifiersDokument6 SeitenLab 9: O A: Perational MplifiersAhmed ChNoch keine Bewertungen

- Electronic Instrumentation and Measurements, 3/e David A. BellDokument31 SeitenElectronic Instrumentation and Measurements, 3/e David A. Bellsabak gardiaNoch keine Bewertungen

- Module 1-1 (RC Coupling)Dokument9 SeitenModule 1-1 (RC Coupling)Jenz Ryan GacutanNoch keine Bewertungen

- CountersDokument19 SeitenCounterslakraniNoch keine Bewertungen

- Rca Cmos DatabookDokument798 SeitenRca Cmos DatabookC S Kumar100% (1)

- Sti260N6F6 Stp260N6F6: N-Channel 60 V, 0.0024 Ω, 120 A Stripfet™ Vi Deepgate™ Power Mosfet In To-220 And I²Pak PackagesDokument14 SeitenSti260N6F6 Stp260N6F6: N-Channel 60 V, 0.0024 Ω, 120 A Stripfet™ Vi Deepgate™ Power Mosfet In To-220 And I²Pak PackagesRyn YahuFNoch keine Bewertungen

- Battery SimulationDokument27 SeitenBattery SimulationBarastean GabrielNoch keine Bewertungen

- Phase Locked Loop PLL Fundamentals PDFDokument6 SeitenPhase Locked Loop PLL Fundamentals PDFRadhakrishna PangaNoch keine Bewertungen

- Equalizer PDFDokument6 SeitenEqualizer PDFLUIS EDUARDO OROZCO QUINTERONoch keine Bewertungen

- Driver IC IntroduceDokument48 SeitenDriver IC IntroducespotNoch keine Bewertungen

- Item # BLHD100K, Brushless DC DriverDokument2 SeitenItem # BLHD100K, Brushless DC DriverPhong NguyễnNoch keine Bewertungen

- Current Mode Bandgap ReferenceDokument22 SeitenCurrent Mode Bandgap ReferenceSovan GhoshNoch keine Bewertungen

- Vijay Maurya ADE TutorialDokument4 SeitenVijay Maurya ADE TutorialKshitij JaiswalNoch keine Bewertungen

- Linear Wave ShapingDokument29 SeitenLinear Wave Shapingapnrao100% (6)

- VJEC Logic Design Lab Experiments GuideDokument6 SeitenVJEC Logic Design Lab Experiments Guideresham k vNoch keine Bewertungen

- Fpga & It's ArchitectureDokument39 SeitenFpga & It's Architectureeeshgarg100% (6)

- Ica Question BankDokument4 SeitenIca Question BankSateesh KunaNoch keine Bewertungen

- DemodulatorsDokument2 SeitenDemodulatorskhalidNoch keine Bewertungen

- Skee 2263 Final Exam 1718-2 SDokument17 SeitenSkee 2263 Final Exam 1718-2 SNG JIAN RONG A20EE0177Noch keine Bewertungen

- BJT AC Analysis Part 1 PDFDokument9 SeitenBJT AC Analysis Part 1 PDFnupur kesarwaniNoch keine Bewertungen

- Unit VDokument33 SeitenUnit VDINESH KUMAR DRAVIDAMANINoch keine Bewertungen

- IRF MOSFET Power TransistorsDokument1 SeiteIRF MOSFET Power TransistorsDAVE.A.H. SIGINoch keine Bewertungen

- Basic VLSI Design by PucknellDokument2 SeitenBasic VLSI Design by Pucknelldfgdf6% (18)

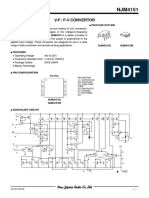

- V-F / F-V Convertor: General Description Package OutlineDokument14 SeitenV-F / F-V Convertor: General Description Package OutlineIlyes KHOUILDINoch keine Bewertungen

- 105 111年北科電子解答Dokument15 Seiten105 111年北科電子解答game davidNoch keine Bewertungen