Beruflich Dokumente

Kultur Dokumente

Ohci 11

Hochgeladen von

Abbas Raza Zaidi0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

31 Ansichten210 Seitenohci

Originaltitel

ohci_11

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenohci

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

31 Ansichten210 SeitenOhci 11

Hochgeladen von

Abbas Raza Zaidiohci

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 210

1394

Open Host Controller Interface

Specification

Release 1.1

January 6, 2000

Copyright 1996-2000 by the Promoters of the 1394 Open HCI.

Page ii Copyright 1996-2000 All rights reserved.

1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

Copyright 1996-2000 All rights reserved. Page iii

PREFACE 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

PREFACE

Notice

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY

WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR

PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR

SAMPLE. Apple Computer, Inc., Compaq Computer Corporation, Intel Corporation, Microsoft Corporation,

National Semiconductor Corporation, Sun Microsystems, Inc., and Texas Instruments, Inc. disclaim all liability,

including liability for infringement of any proprietary rights, relating to use of information in this specification. No

license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein. Except

that a license is hereby granted to copy and reproduce this specification for internal use only. *Third-party brands

and names are the property of their respective owners.

Copyright 1996-2000 All Rights Reserved. Apple Computer, Inc., Compaq Computer Corporation, Intel

Corporation, Microsoft Corporation, National Semiconductor Corporation, Sun Microsystems, Inc., and Texas

Instruments, Inc.

Intellectual Property

Implementation of this Specification is governed by the terms of the 1394 Open Host Controller Interface Patent

License Agreement.

This specification may contain and sometimes even require the use of intellectual property owned by others.

Rights to such intellectual property are not conveyed except as provided by the 1394 Open HCI Promoters agree-

ment and the 1394 Open HCI Adopters agreement.

Information

An on-line copy, updates, and notices regarding this specification will be maintained on the following web sites:

http://developer.intel.com/technology/1394/specs.htm

http://www.microsoft.com/hwdev/1394/#Specs

Questions, comments, and issues concerning this document should be directed to the 1394 Open HCI reflector:

1394ohci-l@austin.ibm.com

Page iv Copyright 1996-2000 All rights reserved.

PREFACE 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

Promoters

The Promoters of record on January 6, 2000, the date of publication of the 1394 Open Host Controller Interface Specifi-

cation, Release 1.1, are:

Apple Computer, Inc.

Compaq Computer Corporation

Intel Corporation

Microsoft Corporation

National Semiconductor Corporation

Sun Microsystems, Inc.

Texas Instruments, Inc.

Contributors

The Open HCI 1.0 specification was developed using Apple Computers Pele design as a starting point. The Pele

contributors were Jim Baldwin, Kevin Christiansen, Nikhil Jayaram, Michael Johas Teener and Rahoul Puri. The original

Editor of the 1394 Open HCI specification up through Draft 0.7, was Michael Johas Teener.

This specification is a derivative of the 1394 Open Host Controller Interface specification Release 1.00. The 1394 Open

HCI Release 1.00 key contributors were Eric W. Anderson, Richard Baker, Joe Bennett, Mike Eneboe, John Fuller, Jerry

Hauck, Diana Klashman (Editor), Robert Macomber, Rahoul Puri, Michael Johas Teener, Peter Teng, Scott Smyers, Erik

Staats, Lee Wilson, (Chair), and David Wooten.

The following is a list of key contributors to the 1394 Open Host Controller Interface Release 1.1 specification.

Lee Wilson, Chair

Steve Bard, Co-Vice-Chair

John Fuller, Co-Vice-Chair

Neil Morrow, Editor

Eric W. Anderson

Richard Baker

David Hunter

Diana Klashman

Robert Macomber

Mike Musciano

Peter Teng

David Wooten

Copyright 1996-2000 All rights reserved. Page v

Table of Contents 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

Table of Contents

PREFACE ............................................................................................................................................................................ iii

Notice .............................................................................................................................................................................. iii

Intellectual Property ........................................................................................................................................................ iii

Information ..................................................................................................................................................................... iii

Promoters ................................................................................................................................................................. iv

Contributors .................................................................................................................................................................... iv

Table of Contents ................................................................................................................................................................. v

List of Figures ................................................................................................................................................................... xiii

List of Tables .....................................................................................................................................................................xvii

1. Introduction ....................................................................................................................................................................... 1

1.1 Related documents................................................................................................................................................ 1

1.2 Overview .............................................................................................................................................................. 1

1.2.1 Asynchronous functions.............................................................................................................................1

1.2.2 Isochronous functions ................................................................................................................................1

1.2.3 Miscellaneous functions.............................................................................................................................2

1.3 Hardware description............................................................................................................................................ 3

1.3.1 Host bus interface....................................................................................................................................... 3

1.3.2 DMA.......................................................................................................................................................... 4

1.3.2.1 Asynchronous transmit DMA.......................................................................................................... 4

1.3.2.2 Asynchronous receive DMA ........................................................................................................... 5

1.3.2.3 Isochronous transmit DMA............................................................................................................. 5

1.3.2.4 Isochronous receive DMA............................................................................................................... 5

1.3.2.5 Self-ID receive DMA ...................................................................................................................... 5

1.3.3 Global unique ID (GUID) interface ........................................................................................................... 5

1.3.4 FIFOs ......................................................................................................................................................... 6

1.3.4.1 Asynchronous transmit FIFOs......................................................................................................... 6

1.3.4.2 Isochronous transmit FIFO.............................................................................................................. 6

1.3.4.3 Receive FIFOs ................................................................................................................................. 6

1.3.5 Link............................................................................................................................................................ 6

1.4 Software interface overview ................................................................................................................................. 8

1.4.1 Registers .................................................................................................................................................... 8

1.4.2 DMA operation .......................................................................................................................................... 8

1.4.3 Interrupts.................................................................................................................................................... 8

1.5 1394 Open HCI Node Offset (Address) Map........................................................................................................ 9

1.6 System Requirements ......................................................................................................................................... 10

1.7 Alignment ........................................................................................................................................................... 10

1.7.1 Data alignment ......................................................................................................................................... 10

1.7.2 Memory structure and buffer alignment ................................................................................................... 10

2. Conventions - Notation and Terms ................................................................................................................................... 11

2.1 Notation .............................................................................................................................................................. 11

2.1.1 Conformance glossary.............................................................................................................................. 11

2.1.2 Numeric Notation..................................................................................................................................... 11

2.1.3 Bit Notation.............................................................................................................................................. 11

2.1.4 Register Notation ..................................................................................................................................... 11

Page vi Copyright 1996-2000 All rights reserved.

Table of Contents 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

2.1.4.1 Read/Write registers ...................................................................................................................... 12

2.1.4.2 Set and Clear registers................................................................................................................... 12

2.1.4.3 Register Reset Values .................................................................................................................... 13

2.1.4.4 Reserved fields .............................................................................................................................. 13

2.1.4.5 Reserved registers ......................................................................................................................... 13

2.1.4.6 Register field notation ................................................................................................................... 13

2.2 Terms .................................................................................................................................................................. 14

3. Common DMA Controller Features ................................................................................................................................. 17

3.1 Context Registers................................................................................................................................................ 17

3.1.1 ContextControl register ............................................................................................................................ 17

3.1.1.1 ContextControl.run........................................................................................................................ 20

3.1.1.2 ContextControl.wake..................................................................................................................... 20

3.1.1.3 ContextControl.active.................................................................................................................... 21

3.1.1.4 ContextControl.dead...................................................................................................................... 21

3.1.2 CommandPtr register ............................................................................................................................... 22

3.1.2.1 Bad Z Value................................................................................................................................... 23

3.2 List Management ................................................................................................................................................ 23

3.2.1 Software Behavior.................................................................................................................................... 23

3.2.1.1 Context Initialization..................................................................................................................... 23

3.2.1.2 Appending to Running List ........................................................................................................... 23

3.2.1.3 Stopping a Context ........................................................................................................................ 23

3.2.2 Hardware Behavior .................................................................................................................................. 23

3.3 Asynchronous Receive........................................................................................................................................ 25

3.3.1 FIFO Implementation (informative)......................................................................................................... 25

3.3.1.1 Unrecoverable Error (informative) ................................................................................................ 26

3.3.2 Ack Codes for Write Requests ................................................................................................................. 26

3.3.3 Posted Writes ........................................................................................................................................... 27

3.3.4 Retries ...................................................................................................................................................... 28

3.4 DMA Summary .................................................................................................................................................. 28

4. Register addressing .......................................................................................................................................................... 29

4.1 DMA Context Number Assignments .................................................................................................................. 30

4.2 Register Map ...................................................................................................................................................... 30

5. 1394 Open HCI Registers ................................................................................................................................................ 35

5.1 Register Conventions .......................................................................................................................................... 35

5.2 Version Register.................................................................................................................................................. 35

5.3 GUID ROM register (optional) ........................................................................................................................... 36

5.4 ATRetries Register.............................................................................................................................................. 36

5.5 Autonomous CSR Resources .............................................................................................................................. 38

5.5.1 Bus Management CSR Registers ............................................................................................................. 38

5.5.2 Config ROM header ................................................................................................................................. 39

5.5.3 Bus identification register ........................................................................................................................ 40

5.5.4 Bus options register.................................................................................................................................. 40

5.5.5 Global Unique ID..................................................................................................................................... 42

5.5.6 Configuration ROM mapping register ...................................................................................................... 42

5.6 Vendor ID register .............................................................................................................................................. 44

5.7 HCControl registers (set and clear)..................................................................................................................... 45

5.7.1 noByteSwapData...................................................................................................................................... 47

5.7.2 programPhyEnable and aPhyEnhanceEnable........................................................................................... 48

Copyright 1996-2000 All rights reserved. Page vii

Table of Contents 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

5.7.3 LPS and linkEnable.................................................................................................................................. 49

5.8 Bus Management CSR Initialization Registers ................................................................................................... 50

5.9 FairnessControl register (optional) ..................................................................................................................... 51

5.10 LinkControl registers (set and clear)................................................................................................................. 51

5.11 Node identification and status register .............................................................................................................. 53

5.12 PHY control register ......................................................................................................................................... 54

5.13 Isochronous Cycle Timer Register .................................................................................................................... 55

5.14 Asynchronous Request Filters .......................................................................................................................... 55

5.14.1 AsynchronousRequestFilter Registers (set and clear) ............................................................................ 55

5.14.2 PhysicalRequestFilter Registers (set and clear)...................................................................................... 57

5.15 Physical Upper Bound register (optional) ......................................................................................................... 58

6. Interrupts .......................................................................................................................................................................... 61

6.1 IntEvent (set and clear) ....................................................................................................................................... 61

6.1.1 busReset ................................................................................................................................................... 64

6.2 IntMask (set and clear) ....................................................................................................................................... 64

6.3 IsochTx interrupt.registers .................................................................................................................................. 65

6.3.1 isoXmitIntEvent (set and clear)................................................................................................................ 66

6.3.2 isoXmitIntMask (set and clear) ................................................................................................................ 67

6.4 IsochRx interrupt registers.................................................................................................................................. 67

6.4.1 isoRecvIntEvent (set and clear)................................................................................................................ 67

6.4.2 isoRecvIntMask (set and clear) ................................................................................................................ 68

7. Asynchronous Transmit DMA ......................................................................................................................................... 69

7.1 AT DMA Context Programs ............................................................................................................................... 69

7.1.1 OUTPUT_MORE descriptor.................................................................................................................... 70

7.1.2 OUTPUT_MORE_Immediate descriptor ................................................................................................. 71

7.1.3 OUTPUT_LAST descriptor ..................................................................................................................... 72

7.1.4 OUTPUT_LAST_Immediate descriptor .................................................................................................. 74

7.1.5 AT DMA descriptor usage........................................................................................................................ 76

7.1.5.1 Command.Z................................................................................................................................... 76

7.1.5.2 Command.xferStatus ..................................................................................................................... 76

7.1.5.3 Command.timeStamp .................................................................................................................... 76

7.1.5.3.1 timeStamp value for Requests............................................................................................. 77

7.1.5.3.2 timeStamp value for Ping Requests .................................................................................... 77

7.1.5.3.3 timeStamp value for Responses .......................................................................................... 77

7.2 AT DMA context registers .................................................................................................................................. 80

7.2.1 CommandPtr ............................................................................................................................................ 80

7.2.2 ContextControl register (set and clear)..................................................................................................... 80

7.2.2.1 Writing status back to context command descriptors .................................................................... 81

7.2.3 Bus Reset ................................................................................................................................................. 81

7.2.3.1 Host Controller Behavior for AT ................................................................................................... 81

7.2.3.2 Software Guidelines ...................................................................................................................... 81

7.3 ack_data_error .................................................................................................................................................... 82

7.4 AT Retries ........................................................................................................................................................... 82

7.5 Fairness............................................................................................................................................................... 82

7.6 AT Interrupts....................................................................................................................................................... 83

7.7 AT Pipelining...................................................................................................................................................... 83

7.8 AT Data Formats................................................................................................................................................. 84

7.8.1 Asynchronous Transmit Requests ............................................................................................................ 84

7.8.1.1 No-data transmit ............................................................................................................................ 84

7.8.1.2 Quadlet transmit ............................................................................................................................ 85

Page viii Copyright 1996-2000 All rights reserved.

Table of Contents 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

7.8.1.3 Block transmit ............................................................................................................................... 87

7.8.1.4 PHY packet transmit ..................................................................................................................... 89

7.8.2 Asynchronous Transmit Responses.......................................................................................................... 89

7.8.2.1 No-data transmit ............................................................................................................................ 89

7.8.2.2 Quadlet transmit ............................................................................................................................ 90

7.8.2.3 Block transmit ............................................................................................................................... 91

7.8.3 Asynchronous Transmit Streams.............................................................................................................. 93

8. Asynchronous Receive DMA........................................................................................................................................... 95

8.1 AR DMA Context Programs............................................................................................................................... 95

8.1.1 INPUT_MORE descriptor........................................................................................................................ 95

8.1.2 AR DMA descriptor usage....................................................................................................................... 96

8.2 bufferFill mode ................................................................................................................................................... 97

8.3 Asynchronous Receive Context Registers........................................................................................................... 97

8.3.1 AR DMA CommandPtr register ............................................................................................................... 97

8.3.2 AR ContextControl register (set and clear) .............................................................................................. 98

8.4 AR DMA Controller ........................................................................................................................................... 98

8.4.1 Asynchronous Filter Registers ................................................................................................................. 98

8.4.2 AR DMA Controller processing .............................................................................................................. 99

8.4.2.1 AR DMA Packet Trailer .............................................................................................................. 100

8.4.2.2 Error Handling ............................................................................................................................ 100

8.4.2.3 Bus Reset Packet ......................................................................................................................... 101

8.5 PHY Packets ..................................................................................................................................................... 102

8.6 Asynchronous Receive Interrupts ..................................................................................................................... 102

8.7 Asynchronous Receive Data Formats ............................................................................................................... 103

8.7.1 Asynchronous Receive Requests............................................................................................................ 104

8.7.1.1 No-data receive............................................................................................................................ 104

8.7.1.2 Quadlet Receive .......................................................................................................................... 104

8.7.1.3 Block receive............................................................................................................................... 106

8.7.1.4 PHY packet receive ..................................................................................................................... 107

8.7.2 Asynchronous Receive Responses ......................................................................................................... 108

8.7.2.1 No-data receive............................................................................................................................ 108

8.7.2.2 Quadlet Receive .......................................................................................................................... 108

8.7.2.3 Block receive............................................................................................................................... 109

9. Isochronous Transmit DMA........................................................................................................................................... 111

9.1 IT DMA Context Programs .............................................................................................................................. 111

9.1.1 IT DMA command descriptor overview................................................................................................. 111

9.1.2 OUTPUT_MORE descriptor.................................................................................................................. 112

9.1.3 OUTPUT_MORE-Immediate descriptor................................................................................................ 113

9.1.4 OUTPUT_LAST descriptor ................................................................................................................... 114

9.1.5 OUTPUT_LAST-Immediate descriptor ................................................................................................. 115

9.1.6 STORE_VALUE descriptor ................................................................................................................... 116

9.1.7 IT DMA descriptor usage....................................................................................................................... 117

9.2 IT Context Registers ......................................................................................................................................... 118

9.2.1 CommandPtr .......................................................................................................................................... 118

9.2.2 IT ContextControl Register .................................................................................................................... 119

9.3 Isochronous transmit DMA controller .............................................................................................................. 120

9.3.1 IT DMA Processing ............................................................................................................................... 121

9.3.2 Prefetching IT Packets ........................................................................................................................... 122

9.3.3 Isochronous Transmit Cycle Loss .......................................................................................................... 122

9.3.4 Skip Processing Overflow...................................................................................................................... 123

Copyright 1996-2000 All rights reserved. Page ix

Table of Contents 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

9.3.5 FIFO Underrun....................................................................................................................................... 124

9.3.6 Determining the number of implemented IT DMA contexts.................................................................. 125

9.4 Appending to an IT DMA Context Program..................................................................................................... 125

9.5 IT Interrupts...................................................................................................................................................... 125

9.5.1 cycleInconsistent Interrupt ..................................................................................................................... 125

9.5.2 busReset Interrupt .................................................................................................................................. 125

9.5.3 UnrecoverableError Interrupt ................................................................................................................. 126

9.6 IT Data Format ................................................................................................................................................. 126

10. Isochronous Receive DMA .......................................................................................................................................... 129

10.1 IR DMA Context Programs ............................................................................................................................ 129

10.1.1 Buffer-Fill and Packet-per-Buffer Descriptors ..................................................................................... 129

10.1.2 Dual-Buffer Descriptor ........................................................................................................................ 130

10.1.3 Descriptor Z Values.............................................................................................................................. 132

10.2 Receive Modes................................................................................................................................................ 133

10.2.1 Buffer Fill Mode .................................................................................................................................. 133

10.2.2 Packet-per-Buffer Mode....................................................................................................................... 134

10.2.2.1 Command.xferStatus and Command.resCount updates ............................................................. 135

10.2.3 Dual-Buffer Mode................................................................................................................................ 135

10.3 IR Context Registers ....................................................................................................................................... 137

10.3.1 CommandPtr ........................................................................................................................................ 137

10.3.2 IR ContextControl register (set and clear)............................................................................................ 137

10.3.3 Isochronous receive contextMatch register .......................................................................................... 140

10.4 Isochronous receive DMA controller .............................................................................................................. 141

10.4.1 Isochronous receive multi-channel support .......................................................................................... 141

10.4.1.1 IRMultiChanMask registers (set and clear) ............................................................................... 141

10.4.2 Isochronous receive single-channel support ......................................................................................... 142

10.4.3 Duplicate channels ............................................................................................................................... 142

10.4.4 Determining the number of implemented IR DMA contexts................................................................ 143

10.5 IR Interrupts.................................................................................................................................................... 143

10.5.1 cycleInconsistent Interrupt ................................................................................................................... 143

10.5.2 busReset Interrupt ................................................................................................................................ 143

10.6 IR Data Formats.............................................................................................................................................. 143

10.6.1 bufferFill mode formats ....................................................................................................................... 144

10.6.1.1 IR with header/trailer................................................................................................................. 144

10.6.1.2 IR without header/trailer ........................................................................................................... 145

10.6.2 Packet-per-buffer mode and dual-buffer mode formats ........................................................................ 145

10.6.2.1 IR with header/trailer................................................................................................................. 145

10.6.2.2 IR without header/trailer ........................................................................................................... 146

11. Self ID Receive ............................................................................................................................................................ 147

11.1 Self ID Buffer Pointer Register....................................................................................................................... 147

11.2 Self ID Count Register.................................................................................................................................... 147

11.3 Self-ID receive................................................................................................................................................ 148

11.4 Enabling the SelfID DMA.............................................................................................................................. 149

11.5 Interrupt Considerations for SelfID DMA...................................................................................................... 149

11.6 SelfIDs Received Outside of Bus Initialization............................................................................................... 149

12. Physical Requests......................................................................................................................................................... 151

12.1 Filtering Physical Requests............................................................................................................................. 152

12.2 Posted Writes.................................................................................................................................................. 152

Page x Copyright 1996-2000 All rights reserved.

Table of Contents 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

12.3 Physical Responses......................................................................................................................................... 152

12.4 Physical Response Retries .............................................................................................................................. 152

12.5 Interrupt Considerations for Physical Requests .............................................................................................. 152

12.6 Bus Reset ........................................................................................................................................................ 152

13. Host Bus Errors ............................................................................................................................................................ 153

13.1 Causes of Host Bus Errors .............................................................................................................................. 153

13.2 Host Controller Actions When Host Bus Error Occurs................................................................................... 153

13.2.1 Descriptor Read Error .......................................................................................................................... 153

13.2.2 xferStatus Write Error .......................................................................................................................... 153

13.2.3 Transmit Data Read Error .................................................................................................................... 154

13.2.4 Isochronous Transmit Data Write Error ............................................................................................... 154

13.2.5 Asynchronous Receive DMA Data Write Error ................................................................................... 154

13.2.6 Isochronous Receive Data Write Error................................................................................................. 154

13.2.7 Physical Read Error ............................................................................................................................. 155

13.2.8 Physical Posted Write Error ................................................................................................................. 155

13.2.8.1 PostedWriteAddress Register (optional) ................................................................................... 156

13.2.8.2 Queue Rules .............................................................................................................................. 157

Annex A. PCI Interface (optional) ..................................................................................................................................... 159

A.1 PCI Configuration Space ................................................................................................................................. 159

A.2 Busmastering Requirements ............................................................................................................................ 159

A.3 PCI Configuration Space for 1394 Open HCI With PCI Interface ................................................................... 159

A.3.1 COMMAND Register ........................................................................................................................... 160

A.3.2 STATUS Register .................................................................................................................................. 161

A.3.3 CLASS_CODE Register ....................................................................................................................... 161

A.3.4 Revision_ID Register ............................................................................................................................ 161

A.3.5 Base_Adr_0 Register ............................................................................................................................ 161

A.3.6 CAP_PTR Register ............................................................................................................................... 162

A.3.7 PCI_HCI_Control Register ................................................................................................................... 163

A.3.8 PCI Power Management Register Interface........................................................................................... 163

A.3.8.1 Capability ID Register ................................................................................................................ 163

A.3.8.2 Next Item Pointer Register (Nxt_Ptr) ......................................................................................... 163

A.3.8.3 Power Management Capabilities Register (PMC) ...................................................................... 164

A.3.8.4 Power Management Control/Status (PMCSR)............................................................................ 165

A.3.8.5 PMCSR_BSE ............................................................................................................................. 165

A.3.8.6 PM_DATA.................................................................................................................................. 165

A.4 PCI Power Management Behavior ................................................................................................................... 166

A.4.1 Power State Transitions......................................................................................................................... 166

A.4.2 Power State Definitions......................................................................................................................... 167

A.4.3 PCI PME# Signal .................................................................................................................................. 168

A.5 PCI Expansion ROM for 1394 Open HCI........................................................................................................ 169

A.6 PCI Bus Errors................................................................................................................................................. 169

Annex B. Summary of Register Reset Values (Informative) .............................................................................................. 171

Annex C. Summary of Bus Reset Behavior (Informative) ................................................................................................. 177

C.1 Overview.......................................................................................................................................................... 177

C.2 Asynchronous Transmit: Request & Response ................................................................................................ 177

C.3 Asynchronous Receive: Request & Response .................................................................................................. 177

C.4 Isochronous Transmit ....................................................................................................................................... 177

Copyright 1996-2000 All rights reserved. Page xi

Table of Contents 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

C.5 Isochronous Receive ........................................................................................................................................ 177

C.6 Self ID Receive ................................................................................................................................................ 178

C.7 Physical Requests/Responses ........................................................................................................................... 178

C.7.1 Physical Response ................................................................................................................................. 178

C.7.2 Physical Requests .................................................................................................................................. 178

C.8 Control Registers ............................................................................................................................................. 178

Annex D. IT DMA Supplement (Informative) .................................................................................................................. 179

D.1 IT DMA Behavior............................................................................................................................................ 179

D.2 IT DMA Flowchart Summary ......................................................................................................................... 179

D.3 DMA-side IT DMA flowchart ........................................................................................................................ 179

D.3.1 DMA-side top half ............................................................................................................................... 181

D.3.2 DMA-side bottom half .......................................................................................................................... 181

D.4 Link-side IT DMA flowchart ........................................................................................................................... 182

D.4.1 Link-side top half .................................................................................................................................. 182

D.4.2 Link-side bottom half ............................................................................................................................ 184

Annex E. Sample IT DMA Controller Implementation (Informative)................................................................................ 185

Annex F. Extended Config ROM Entries ........................................................................................................................... 191

F.1 Mini-ROM Data Format.................................................................................................................................... 191

Page xii Copyright 1996-2000 All rights reserved.

Table of Contents 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

Copyright 1996-2000 All rights reserved. Page xiii

List of Figures 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

List of Figures

Figure 1-1 1394 Open HCI conceptual block diagram ..................................................................................................... 3

Figure 1-2 Node Offset Map ............................................................................................................................................ 9

Figure 3-1 ContextControl (set and clear) register format .............................................................................................. 17

Figure 3-2 CommandPtr register format ......................................................................................................................... 22

Figure 3-3 Flow Chart for Processing a DMA Context .................................................................................................. 24

Figure 5-1 Version register ............................................................................................................................................. 35

Figure 5-2 GUID ROM register ...................................................................................................................................... 36

Figure 5-3 ATRetries register ......................................................................................................................................... 37

Figure 5-4 CSR data register .......................................................................................................................................... 38

Figure 5-5 CSR compare register ................................................................................................................................... 39

Figure 5-6 CSR control register ..................................................................................................................................... 39

Figure 5-7 Config ROM header register ......................................................................................................................... 40

Figure 5-8 Bus ID register .............................................................................................................................................. 40

Figure 5-9 Bus options register ...................................................................................................................................... 41

Figure 5-10 GlobalUniqueIDHi register ......................................................................................................................... 42

Figure 5-11 GlobalUniqueIDLo register ........................................................................................................................ 42

Figure 5-12 Configuration ROM mapping register ......................................................................................................... 44

Figure 5-13 VendorID register ........................................................................................................................................ 44

Figure 5-14 HCControl register ...................................................................................................................................... 45

Figure 5-15 Initial Bandwidth Available register ............................................................................................................ 50

Figure 5-16 Initial Channels Available Hi register ......................................................................................................... 50

Figure 5-17 Initial Channels Available Lo register ......................................................................................................... 50

Figure 5-18 FairnessControl register .............................................................................................................................. 51

Figure 5-19 LinkControl register .................................................................................................................................... 51

Figure 5-20 Node ID register ......................................................................................................................................... 53

Figure 5-21 PHY control register ................................................................................................................................... 54

Figure 5-22 Isochronous cycle timer register ................................................................................................................. 55

Figure 5-23 AsynchronousRequestFilterHi (set and clear) register ................................................................................ 56

Figure 5-24 AsynchronousRequestFilterLo (set and clear) register ............................................................................... 56

Figure 5-25 PhysicalRequestFilterHi (set and clear) register ......................................................................................... 57

Figure 5-26 PhysicalRequestFilterLo (set and clear) register ......................................................................................... 57

Figure 5-27 48-bit Physical Upper Bound ...................................................................................................................... 58

Figure 5-28 Physical Upper Bound register .................................................................................................................... 58

Figure 6-1 IntEvent register ............................................................................................................................................ 62

Figure 6-2 IntMask register ............................................................................................................................................ 65

Figure 6-3 isoXmitIntEvent (set and clear) register ........................................................................................................ 66

Figure 6-4 isoXmitIntMask (set and clear) register ........................................................................................................ 67

Figure 6-5 isoRecvIntEvent (set and clear) register ........................................................................................................ 68

Figure 6-6 isoRecvIntMask (set and clear) register ........................................................................................................ 68

Figure 7-1 OUTPUT_MORE descriptor format ............................................................................................................. 70

Figure 7-2 OUTPUT_MORE-Immediate descriptor format ........................................................................................... 71

Figure 7-3 OUTPUT_LAST descriptor format .............................................................................................................. 72

Figure 7-4 OUTPUT_LAST-Immediate descriptor format ............................................................................................. 74

Figure 7-5 timeStamp format ......................................................................................................................................... 76

Figure 7-6 CommandPtr register format ......................................................................................................................... 80

Figure 7-7 ContextControl (set and clear) register format .............................................................................................. 80

Figure 7-8 Completion Status and Retry Behavior ......................................................................................................... 82

Figure 7-9 Quadlet read request transmit format ............................................................................................................ 84

Figure 7-10 Quadlet write request transmit format ......................................................................................................... 85

Figure 7-11 Block read request transmit format ............................................................................................................. 86

Figure 7-12 Write request transmit format ..................................................................................................................... 87

Figure 7-13 Lock request transmit format ...................................................................................................................... 88

Page xiv Copyright 1996-2000 All rights reserved.

List of Figures 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

Figure 7-14 PHY packet transmit format ....................................................................................................................... 89

Figure 7-15 Write response transmit format ................................................................................................................... 89

Figure 7-16 Quadlet read response transmit format ....................................................................................................... 90

Figure 7-17 Block read response transmit format .......................................................................................................... 91

Figure 7-18 Lock response transmit format .................................................................................................................... 92

Figure 7-19 Asynchronous stream packet format .......................................................................................................... 93

Figure 8-1 INPUT_MORE descriptor format ................................................................................................................. 95

Figure 8-2 bufferFill receive mode ................................................................................................................................. 97

Figure 8-3 CommandPtr register format ......................................................................................................................... 97

Figure 8-4 AR ContextControl (set and clear) register format ....................................................................................... 98

Figure 8-5 AR DMA packet trailer format ................................................................................................................... 100

Figure 8-6 AR Request Context Bus Reset packet format ............................................................................................ 101

Figure 8-7 Quadlet read request receive format ........................................................................................................... 104

Figure 8-8 Quadlet write request receive format .......................................................................................................... 104

Figure 8-9 Block read request receive format ............................................................................................................... 105

Figure 8-10 Block write request receive format ........................................................................................................... 106

Figure 8-11 Lock request receive format ...................................................................................................................... 107

Figure 8-12 PHY packet receive format ....................................................................................................................... 107

Figure 8-13 Write response receive format .................................................................................................................. 108

Figure 8-14 Quadlet read response receive format ....................................................................................................... 108

Figure 8-15 Block read response receive format .......................................................................................................... 109

Figure 8-16 Lock response receive format ................................................................................................................... 110

Figure 9-1 OUTPUT_MORE command descriptor format .......................................................................................... 112

Figure 9-2 OUTPUT_MORE-Immediate descriptor format ......................................................................................... 113

Figure 9-3 OUTPUT_LAST command descriptor format ............................................................................................ 114

Figure 9-4 OUTPUT_LAST-Immediate command descriptor format .......................................................................... 115

Figure 9-5 STORE_VALUE descriptor ........................................................................................................................ 116

Figure 9-6 CommandPtr register format ....................................................................................................................... 118

Figure 9-7 IT DMA ContextControl (set and clear) register format ............................................................................. 119

Figure 9-8 IT DMA summary ...................................................................................................................................... 121

Figure 9-9 Isochronous transmit cycle loss example .................................................................................................... 124

Figure 9-10 Isochronous transmit format .................................................................................................................... 126

Figure 10-1 INPUT_MORE/INPUT_LAST descriptor format .................................................................................... 129

Figure 10-2 DUALBUFFER descriptor format ............................................................................................................ 131

Figure 10-3 IR Buffer Fill Mode .................................................................................................................................. 133

Figure 10-4 packet-per-buffer receive mode ................................................................................................................. 134

Figure 10-5 IR Dual-Buffer Mode ................................................................................................................................ 136

Figure 10-6 CommandPtr register format ..................................................................................................................... 137

Figure 10-7 IR DMA ContextControl (set and clear) register format ........................................................................... 138

Figure 10-8 IR DMA ContextMatch register format .................................................................................................... 140

Figure 10-9 IRMultiChanMaskHi (set and clear) register ............................................................................................ 141

Figure 10-10 IRMultiChanMaskLo (set and clear) register .......................................................................................... 142

Figure 10-11 Receive isochronous format in bufferFill mode with header/trailer ........................................................ 144

Figure 10-12 Receive isochronous format in bufferFill mode without header/trailer ................................................... 145

Figure 10-13 Receive isochronous format in packet-per-buffer or dual-buffer mode with header/trailer ..................... 145

Figure 10-14 Receive isochronous format in packet-per-buffer and dual-buffer mode without header/trailer .............. 146

Figure 11-1 Self ID Buffer Pointer register .................................................................................................................. 147

Figure 11-2 Self ID Count register ............................................................................................................................... 147

Figure 11-3 Self-ID receive format .............................................................................................................................. 148

Figure 13-1 PostedWriteAddressHi register ................................................................................................................. 156

Figure 13-2 PostedWriteAddressLo register ................................................................................................................ 156

Figure 13-3 Posted Write Error Queue ......................................................................................................................... 157

Figure A-1 PCI Configuration Space ........................................................................................................................... 159

Figure A-2 Pointers to OHCI Resources in PCI Configuration Space .......................................................................... 160

Copyright 1996-2000 All rights reserved. Page xv

List of Figures 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

Figure A-3 PCI Function Power Management State Diagram ...................................................................................... 166

Figure D-1 IT DMA DMA-Side Flowchart .................................................................................................................. 180

Figure D-2 IT DMA Link-Side Flowchart ................................................................................................................... 183

Figure E-1 DMA Cycle Matching Continuum ............................................................................................................. 185

Figure E-2 IT DMA Controller counters and cycle matching logic .............................................................................. 186

Figure E-3 IT DMA Flowchart ..................................................................................................................................... 187

Figure E-4 Process IT Contexts Flowchart ................................................................................................................... 188

Figure E-5 Skip IT Contexts Flowchart ........................................................................................................................ 189

Figure F-1 GUID ROM data map ................................................................................................................................. 191

Figure F-2 Mini-ROM format ...................................................................................................................................... 191

Page xvi Copyright 1996-2000 All rights reserved.

List of Figures 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

Copyright 1996-2000 All rights reserved. Page xvii

List of Tables 1394 Open Host Controller Interface Specification / Release 1.1 Printed 1/10/00

List of Tables

Table 1-1 DMA controller types and contexts .................................................................................................................. 4

Table 1-2 Link generated acknowledges ........................................................................................................................... 7

Table 2-1 read/write register field access tags ................................................................................................................ 12

Table 2-2 Set and Clear register field access tags ........................................................................................................... 12

Table 2-3 Register field reset values ............................................................................................................................... 13

Table 3-1 ContextControl (set and clear) register description ........................................................................................ 17

Table 3-2 Packet event codes .......................................................................................................................................... 18

Table 3-3 CommandPtr register description ................................................................................................................... 22

Table 3-4 CommandPtr read values ................................................................................................................................ 22

Table 3-5 DMA Summary .............................................................................................................................................. 28

Table 4-1 1394 Open HCI register space map ................................................................................................................ 30

Table 4-2 Asynchronous DMA Context number assignments ........................................................................................ 30

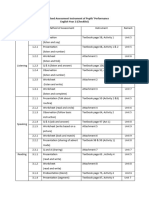

Table 4-3 Register addresses (Sheet 1 of 4) .................................................................................................................... 30

Table 5-1 Version register fields ..................................................................................................................................... 35

Table 5-2 GUID ROM register fields .............................................................................................................................. 36

Table 5-3 ATRetries register fields ................................................................................................................................ 37

Table 5-4 Serial Bus Registers ........................................................................................................................................ 38

Table 5-5 CSR registers fields ...................................................................................................................................... 39

Table 5-6 Config ROM header register fields ................................................................................................................. 40

Table 5-7 Bus ID register fields ...................................................................................................................................... 40

Table 5-8 Bus options register fields .............................................................................................................................. 41

Table 5-9 GlobalUniqueID register fields ....................................................................................................................... 42

Table 5-10 Configuration ROM mapping register fields ................................................................................................ 44