Beruflich Dokumente

Kultur Dokumente

92

Hochgeladen von

maheshsamanapallyCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

92

Hochgeladen von

maheshsamanapallyCopyright:

Verfügbare Formate

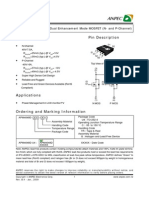

Impact of Well Edge Proximity Effect on Timing

Toshiki Kanamoto

, Yasuhiro Ogasahara

, Keiko Natsume

, Kenji Yamaguchi

,

Hiroyuki Amishiro

, Tetsuya Watanabe

and Masanori Hashimoto

Renesas Technology Corp.

4-1, Mizuhara, Itami-shi, Hyogo, Japan

E-mail: kanamoto.toshiki@renesas.com

Osaka University

1-5, Yamadaoka, Suita-shi, Osaka, Japan

AbstractThis paper studies impact of the well edge proximity

effect on digital circuit delay, based on model parameters ex-

tracted from test structures in an industrial 65nm wafer process.

The experimental results show that up to 10% of delay

increase arises by the well edge proximity effect in the 65nm

technology, and it depends on interconnect length. Furthermore,

due to asymmetric increase in pMOS and nMOS threshold

voltages, delay may decrease in spite of the threshold voltage

increase. From these results, we conclude that considering WPE

is indispensable to cell characterization in the 65nm technology.

I. INTRODUCTION

At front-end stages of CMOS wafer process, P and N types

of ions are implanted to form wells. During the implantations,

lateral scattering of the ions nearby edges of the photo-resist

causes well doping concentration, as shown in Fig. 1 [1][2][3].

The well doping concentration mainly drifts the threshold

voltage of MOS transistors. We call it well edge proximity

effect (WPE). As advanced deep well implants with high-

energy implanters are introduced to suppress parasitic bipolar

gain for latch-up protection, WPE becomes severer. In circuit

design, WPE can be suppressed by making a large separation

between gate poly and enclosing well edge.

On the other hand, as shown in Fig. 2, common cell based

designs intrinsically involve WPE, whereas analog circuit

design can make use of the large separation. The gure depicts

a part of standard cells placement. Since wells are continuous

along the cell rows and then dummy cells are placed at the

both ends of the cell rows for lithographical reasons, horizontal

proximity between gate and well edges can be negligible.

As for the vertical direction, the inner and the outer spacing

shown in the gure are uniquely determined for cell by cell.

Therefore, we should take care of WPE only for the vertical

direction in the digital cell based design.

During circuit design, a lot of effort is put into timing

convergence[4]. From a standpoint of circuit design, delay

variation due to WPE is a matter of utmost concern. We

evaluate the impact of WPE on circuit timing as a case study

in an industrial 65nm technology, and demonstrate the delay

increase quantitatively. We also point out that WPE decreases

cell delay in some conditions of input waveform and output

load.

Resist

Well

Well

STI STI

Gate

S D

Well implant

Substrate

Substrate

Fig. 1. Schematic representation of the well edge proximity effect.

II. WELL EDGE PROXIMITY EFFECT MODELING

Threshold voltage V

th

for MOSFETs with sufciently long

and wide channels are expressed by the following equation

[5].

V

th

= V FB +

s

+

s

V

bs

= V TH0 +(

s

V

bs

s

), (1)

where V FB is the at band voltage,

s

is the surface

potential, V TH0 is the threshold voltage of the device at zero

substrate bias, and is the body bias coefcient which is pro-

portional to square root of the substrate doping concentration.

BSIM4.5 species the factor of increase in the substrate doping

concentration due to WPE in terms of instance parameters

SCA, SCB, SCC and model parameters K

V TH0WE

, WEB,

WEC[5][6][7]. Amount of the V

th

shift is expressed by

dV

th

= K

V TH0WE

(SCA+WEB SCB+WEC SCC).

(2)

Here, the instance parameters SCA, SCB, SCC correspond

to proles of the extra doped well ions due to WPE, and then

they are determined by layout patterns of the MOS transistors.

We derive the model parameters K

V TH0WE

, WEB, WEC

1-4244-1124-6/07/$25.00 2007 IEEE. 115

Power

Ground

(Power)

(Ground)

Vertical inner

spacing

Vertical outer spacing

Vertical outer spacing

Gate

P+ diffusion

N+ diffusion

N well

P well

Cell row

Horizontal spacing

Horizontal spacing

Fig. 2. Well edge proximity of the standard cell region.

Fig. 3. dV

th

estimation using BSIM4.5 parameters.

by tting them to the measured dV

th

for a set of layout patterns

of test element groups. Figure 3 shows effectiveness of the

dV

th

tting. X-axis is the measured Vth shift and Y-axis is

the Vth shift in BSIM4.5 model with the derived parameters.

We can see WPE modeling is well performed.

Fig. 4. Delay increment due to WPE (FO1 small inverters chain).

III. IMPACT OF WELL EDGE PROXIMITY EFFECT ON

TIMING

We derive the model parameters explained in the previous

section for a 65nm SoC process. As shown in [3], the threshold

voltage shifts of p type MOS transistors are larger than

n type MOS transistors due to difference in the substrate

doping concentration. Actually, the maximum difference in the

threshold voltage shift reaches three times. Using the model

parameters and the instance parameters extracted from layout

patterns of standard cells for the SoC process, we achieve the

following experiments.

A. Wire length and fan-out dependency of the delay increase

First, we evaluate delay of two kinds of inverter chains by

circuit simulation. The examined inverter cell is applied to

within 100m range of wire interconnections. One inverter

chain includes the inverters with single fan-out (FO1), where

each inverter drives single inverter with the same size. The

other inverter has the inverters with 20 fan-out (FO20), where

each inverter drives 20 same size inverters. Wires connecting

the inverters, which are assumed to be in a semi-global layer

[8], vary from 1m to 100m.

Figure 4 shows the simulated cell delay[9] of the FO1

inverter chain, where relationship between gate and well edges

is as shown in Fig. 2. In the gure, rise and fall denote

rising and falling transitions of output signal of the inverter.

As seen in the gure, the delay increase due to WPE is up to

10% for this inverter chain, where the rising delay increase is

larger than the falling delay increase. It is because the rate of

the threshold voltage shift in pMOS is twice as large as the

rate in nMOS. We also see in the gure that rate of the delay

increase is reduced as the inverter drives longer wires. Buffers

inserted in a short distance are sensitive to WPE.

Figure 5 shows the simulated cell delay of the FO20 inverter

chain. This situation makes the input transient time of the

inverter cell longer compared to the FO1 case. Wire length

dependency is much smaller than the FO1 case since the output

load capacitance of the inverter is almost determined by the

FO20 of the gate capacitance.

116

Fig. 5. Delay increment due to WPE (FO20 small inverters chain).

B. Conditions of decreasing buffer delay

Next, we examine inverter chains with 24 times larger

inverters than the previous ones. MOS transistors in each

inverter cell form multiple ngers due to the limitation of cell

height. The p type MOS nger has the same size as the p

type MOS transistor in the previous inverter. On the other

hand, the n type MOS nger is twice wider than the previous

one. In general, wider MOS transistors are less affected by

WPE[6]. However, the large standard cell inverter gets the

same amount of WPE as the previous small inverter due to

the nger division. We examine the impact of WPE along

cell delay tables[9] in order to understand the impact of WPE

systematically. The cell delay tables show that falling delay

can decrease due to WPE when the input transient time is

large and the output load (fan-out) is small (Fig. 7), unlike

rising delay (Fig. 6). The reason is thought to be that decrease

in leakage current of pMOS exceeds the decrease in pull-down

current of nMOS. Figures 8 and 9 show current decreases due

to WPE. Figure 8 shows that the leakage current of pMOS is

highly suppressed by WPE, compared with current reduction

of nMOS in Fig. 9.

Then, we examine whether the case of decreasing the delay

appears in the inverter chain. Since the delay decrease can

occur when the fan-out is small, we simulate the FO1 chain.

Figure 10 shows the results. In the wire length range up

to 800m, the falling delay decrease appears. As the wire

becomes long, the wire capacitance increases the output load,

and then the falling delay decrease becomes small. As the

result, there are cases that delay decreases in spite of the

threshold voltage increase.

Fig. 6. Load capacitance and transient time dependency of delay increment

due to WPE (Large inverter, rising delay).

Fig. 7. Load capacitance and transient time dependency of delay increment

due to WPE (Large inverter, falling delay).

IV. CONCLUSION

This paper has investigated the impact of WPE on circuit

delay, applying the WPE model and extraction methodology

to circuits supposing buffer insertion cases in a cell based

design. The experimental results show that up to 10% of

delay increments are caused by WPE in a 65nm SoC process.

Further, the asymmetric increase in the threshold voltages

between p and n type MOS devices causes the situation

of decreasing delay because the decrease in leakage current

of pMOS overwhelms the decrease in pull-down current of

nMOS. From these results, we conclude that WPE in the 65nm

technology should be taken into consideration. Especially,

since the case of decreasing delay can happen, WPE should

be cared for the hold time check in the timing verication, as

well as the setup time checking. In general, since the delay

change due to WPE varies instance by instance, it should be

treated as one of the systematic variability factors[10]. As for

the digital cell based design, considering WPE is indispensable

to cell characterization in the 65nm technology.

117

Fig. 8. Current decrease due to WPE (pMOS).

Fig. 9. Current decrease due to WPE (nMOS).

Fig. 10. Delay increment due to WPE (FO1 large inverters chain).

REFERENCES

[1] T.B.Hook, J.Brown, P.Cottrell, E.Adler, D.Hoyniak, J.Johnson, R.Mann,

Lateral ion implant straggle and mask proximity effect, IEEE Transac-

tions on Electron Devices, vol.50, Issue 9, pp.19461951, Sept. 2003.

[2] I.Polishchuk, N.Mathur, C.Sandstrom, P.Manos, O.Pohland, CMOS Vt-

control improvement through implant lateral scatter elimination, Pro-

ceedings of the IEEE International Symposium on Semiconductor Man-

ufacturing 2005, pp. 193 196, Sept. 2005.

[3] Yi-Ming Sheu, Ke-Wei Su, Sheng-Jier Yang, Hsien-Te Chen, Chih-Chiang

Wang, Ming-Jer Chen, S.Liu, Modeling well edge proximity effect on

highly-scaled MOSFETs, Proceedings of the IEEE Custom Integrated

Circuits Conference 2005, pp. 831 - 834, Sept. 2005.

[4] Yiqian Zhang, Qiang Zhou, Xianlong Hong,Yici Cai, Path-based timing

optimization by buffer insertion with accurate delay model, Proceedings

of 5th International Conference on ASIC, vol.1, pp. 89-92, Oct. 2003.

[5] BSIM4.5.0 Complete Manual, University of California, Berkeley, July

2005.

[6] Guidelines for Extracting Well Proximity Effect Instance Parameters,

Compact Modeling Council, http://www.eigroup.org/CMC/proximity

[7] J.Watts, K.Su, M.Basel, Netlisting and Modeling Well-Proximity Ef-

fects, IEEE Transactions on Electron Devices, vol.53, Issue 9, pp.2179

2186, Sept. 2006.

[8] The International Technology Roadmap for Semiconductors, 2005 Edi-

tion.

[9] Library Compiler Version 2000.05 User Guide, Synopsys inc.

[10] H. Onodera, Variability: Modeling and Its Impact on Design, IEICE

Transactions on Electronics, Vol. E89-C, No. 3, pp. 342-348, March 2006.

118

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Physical Design Interview QuestionsDokument37 SeitenPhysical Design Interview Questionsmaheshsamanapally100% (1)

- Tala Patra 32Dokument17 SeitenTala Patra 32maheshsamanapally67% (3)

- Voltage References and Biasing: KT/Q, For Example) - Similarly, Any Current We Produce Must Depend On Parameters ThatDokument15 SeitenVoltage References and Biasing: KT/Q, For Example) - Similarly, Any Current We Produce Must Depend On Parameters ThatmaheshsamanapallyNoch keine Bewertungen

- Lab Overview: ECE 410 Brief Report TemplateDokument1 SeiteLab Overview: ECE 410 Brief Report TemplatemaheshsamanapallyNoch keine Bewertungen

- Analog Layout Generation For Performance and ManufacturabilityDokument1 SeiteAnalog Layout Generation For Performance and ManufacturabilitymaheshsamanapallyNoch keine Bewertungen

- Reconfigurable Computing - Clocks: John MorrisDokument15 SeitenReconfigurable Computing - Clocks: John MorrismaheshsamanapallyNoch keine Bewertungen

- Missing Analog Tools - A Proposal: Steve Grout CAD ConsultantDokument20 SeitenMissing Analog Tools - A Proposal: Steve Grout CAD ConsultantmaheshsamanapallyNoch keine Bewertungen

- Bias Circuits For RF DevicesDokument20 SeitenBias Circuits For RF Devicesmaheshsamanapally100% (1)

- Pura Than A Punya Grand A NidhiDokument201 SeitenPura Than A Punya Grand A NidhimaheshsamanapallyNoch keine Bewertungen

- Spoken English 2Dokument247 SeitenSpoken English 2maheshsamanapally100% (1)

- Gopuramu PDFDokument246 SeitenGopuramu PDFSunil KumarNoch keine Bewertungen

- Bandgap-Brokaw FundamentalsDokument60 SeitenBandgap-Brokaw FundamentalsEduardo AvilezNoch keine Bewertungen

- Design Abstraction and Validation VLSI MEDC 104Dokument90 SeitenDesign Abstraction and Validation VLSI MEDC 104maheshsamanapally0% (1)

- LayoutDokument40 SeitenLayoutSrinivas DevalankaNoch keine Bewertungen

- BSNL Certified GSM Mobile RF Engineer - Course ScheduleDokument1 SeiteBSNL Certified GSM Mobile RF Engineer - Course SchedulemaheshsamanapallyNoch keine Bewertungen

- lnk302 - 304 306 179954 PDFDokument19 Seitenlnk302 - 304 306 179954 PDFBimMarius0% (1)

- Rt9008ge Apl5611aci-Trg Apl5611 9008ge 9008 La04 La12 La13 La14 La15 La16 La17 La0 La1Dokument9 SeitenRt9008ge Apl5611aci-Trg Apl5611 9008ge 9008 La04 La12 La13 La14 La15 La16 La17 La0 La1laptophaianhNoch keine Bewertungen

- Unit 3: MOS Electrostatics: The Mobile Charge vs. Gate VoltageDokument22 SeitenUnit 3: MOS Electrostatics: The Mobile Charge vs. Gate VoltagealNoch keine Bewertungen

- Eee 335 L2Dokument30 SeitenEee 335 L2Cheung KinTungNoch keine Bewertungen

- Transistor 99029Dokument7 SeitenTransistor 99029PauloPecegueiro100% (3)

- CPF Language ReferenceDokument262 SeitenCPF Language ReferencerzunigaNoch keine Bewertungen

- LR 3410Dokument11 SeitenLR 3410karimNoch keine Bewertungen

- Dec50143 PW1Dokument11 SeitenDec50143 PW1imanbatrisyia288Noch keine Bewertungen

- M.tech Thesis VarunDokument78 SeitenM.tech Thesis VarunAppala Naidu GottapuNoch keine Bewertungen

- AP 40T03GP - Advandced Power Electronic CorpDokument4 SeitenAP 40T03GP - Advandced Power Electronic CorpStevenNoch keine Bewertungen

- Ec1 QF1Dokument3 SeitenEc1 QF1stella maryNoch keine Bewertungen

- LM 5116 WGDokument34 SeitenLM 5116 WGalan segundo garcia chotaNoch keine Bewertungen

- Cell Phone Detector Project ReportDokument34 SeitenCell Phone Detector Project ReportParamjit Singh75% (8)

- Course Information SheetDokument3 SeitenCourse Information SheetKameshSontiNoch keine Bewertungen

- Stp60nf03l - N-Channel 30v - 0.008 Ohm - 60a To-220 Stripfet Power Mosfet - StmicroelectronicsDokument6 SeitenStp60nf03l - N-Channel 30v - 0.008 Ohm - 60a To-220 Stripfet Power Mosfet - StmicroelectronicsJulio César Rosas GonzálezNoch keine Bewertungen

- Mosfet B100NFDokument15 SeitenMosfet B100NFAfortunaoNoch keine Bewertungen

- HEP-1 Laboratory Manual: Coreel TechnologiesDokument17 SeitenHEP-1 Laboratory Manual: Coreel TechnologiesGaurav PatelNoch keine Bewertungen

- STR-A6151 STR-A6159: Universal-Input/13 or 16 W Flyback Switching RegulatorsDokument7 SeitenSTR-A6151 STR-A6159: Universal-Input/13 or 16 W Flyback Switching RegulatorsVidal VelasquezNoch keine Bewertungen

- Avago Application Note 1335 - Main Applications and Selection of Gate Driver Optocouplers PDFDokument8 SeitenAvago Application Note 1335 - Main Applications and Selection of Gate Driver Optocouplers PDFFabiano TonnNoch keine Bewertungen

- Tutorial-1 Low Noise Amplifier (LNA) Design: Complied by Rashad M. RamzanDokument18 SeitenTutorial-1 Low Noise Amplifier (LNA) Design: Complied by Rashad M. RamzanSrinath SrinivasanNoch keine Bewertungen

- Datasheet SFP50N06 PDFDokument7 SeitenDatasheet SFP50N06 PDFAdeniltonNoch keine Bewertungen

- Apm 4048 DDokument13 SeitenApm 4048 DJuan CoronelNoch keine Bewertungen

- Optocoupler Design GuideDokument69 SeitenOptocoupler Design Guidescribd_20_emmanuelfaure100% (1)

- FA531X Series: FA5310BP (S), FA5314P (S), FA5316P (S) FA5311BP (S), FA5315P (S), FA5317P (S)Dokument17 SeitenFA531X Series: FA5310BP (S), FA5314P (S), FA5316P (S) FA5311BP (S), FA5315P (S), FA5317P (S)Denis PrivatNoch keine Bewertungen

- Electrical SymbolsDokument6 SeitenElectrical SymbolsAnant Catalyst ShuklaNoch keine Bewertungen

- Far Driver Tuning Guide 2.31Dokument5 SeitenFar Driver Tuning Guide 2.31cohardwayNoch keine Bewertungen

- FSCQ1565RP: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterDokument24 SeitenFSCQ1565RP: Green Mode Fairchild Power Switch (FPS) For Quasi-Resonant Switching ConverterManuelAlejandroVicuñaRojasNoch keine Bewertungen

- Irfi 3205 Power MosfetDokument9 SeitenIrfi 3205 Power MosfetAndy WilsonNoch keine Bewertungen

- BR4953DDokument7 SeitenBR4953DIvanNoch keine Bewertungen

- MOSFET Power LossesDokument7 SeitenMOSFET Power LossespauloferettiNoch keine Bewertungen