Beruflich Dokumente

Kultur Dokumente

75-H-Priyanka Joshi-Analysis of Low Poser Area Efficient

Hochgeladen von

Ramakrishna Sagar0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

32 Ansichten6 Seitenthis is gud

Originaltitel

75-H-priyanka Joshi-Analysis of Low Poser Area Efficient (1)

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenthis is gud

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

32 Ansichten6 Seiten75-H-Priyanka Joshi-Analysis of Low Poser Area Efficient

Hochgeladen von

Ramakrishna Sagarthis is gud

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 6

ISSN (Print) : 2319-5940

ISSN (Online) : 2278-1021

International J ournal of Advanced Research in Computer and Communication Engineering

Vol. 2, Issue 9, September 2013

Copyright to IJARCCE www.ijarcce.com 3705

Analysis of Low Power, Area- Efficient and High

Speed Fast Adder

Pallavi Saxena

1

, Urvashi Purohit

2

, Priyanka Joshi

3

PG Scholar, Department of ECE, Mody Institute of Technology and Science, Lakshmangarh, India

1

PG Scholar, Department of ECE, Mody Institute of Technology and Science, Lakshmangarh, India

2

Assistant Professor, Department of ECE, Mody Institute of Technology and Science, Lakshmangarh, India

3

Abstract: In electronics, adder is a digital circuit that performs addition of numbers. To perform fast arithmetic operations,

carry select adder (CSLA) is one of the fastest adders used in many data- processing processors. The structure of CSLA is

such that there is further scope of reducing the area, delay and power consumption. Simple and efficient gate level

modification is used in order to reduce the area, delay and power of CSLA. Based on the modifications, 8-bit, 16-bit, 32-bit

and 64-bit architectures of CSLA are designed and compared. In this paper, conventional CSLA is compared with Modified

Carry select adder (MCSLA), Regular Square Root CSLA (SQRT CSLA), Modified SQRT CSLA and Proposed SQRT

CSLA in terms of area, delay and power consumption. The result analysis shows that the proposed structure is better than

the conventional CSLA.

Keywords: Adder, Carry select Adder (CSLA), Modified CSLA (MCSLA), Square Root CSLA (SQRT CSLA), Data

rocessing processors.

I. INTRODUCTION

In many computers and other kind of processors, adders

are not only used in the arithmetic logic unit, but also in

other parts of the processor, where they are used to calculate

addresses, table indices and similar applications. Some other

applications of adders are in Multiply Accumulate (MAC)

structures. Adders are also used in multipliers, in high speed

integrated circuits and in digital signal processing to execute

various algorithms like FFT, IIR and FIR. Now a days,

design of low power, area efficient high speed data path

logic systems are the most substantial areas in the research

of VLSI design.

On the basis of requirements such as area, delay and

power consumption some of the complex adders are Ripple

Carry Adder, Carry look-Ahead Adder and Carry Select

Adder. Ripple Carry Adder (RCA) shows the compact

design but their computation time is longer. Time critical

applications make use of Carry Look-Ahead Adder (CLA) to

derive fast results but it leads to increase in area. But the

carry select adder provides a compromise between the small

areas but longer delay of RCA and large area with small

delay of Carry Look Ahead adder.[1]

This paper presents a comparative analysis of various

adders and proposed design of SQRT CSLA by sharing

Common Boolean Logic and modified CSLA using Binary

to Excess-1 Converter (BEC). Both these adders show less

area, delay and power than other adders.

This paper is organized as follows: In section II literature

survey is shown, section III deals with modified CSLA,

section IV explains Regular SQRT CSLA and Modified

SQRT CSLA and section V explains about Proposed SQRT

CSLA using common Boolean logic. Results are analysed in

section VI and section VII concludes. Section VIII tells

about future scope.

II. LITERATURE SURVEY

Ripple Carry Adder consists of cascaded N single bit full

adders. Output carry of previous adder becomes the input

carry of next full adder. Therefore, the carry of this adder

traverses longest path called worst case delay path through N

stages. Fig. 1 shows the block diagram of ripple carry adder.

Now as the value of N increases, delay of adder will also

increase in a linear way. Therefore, RCA has the lowest

speed amongst all the adders because of large propagation

delay but it occupies the least area. Now CSLA provides a

way to get around this linear dependency is to anticipate all

possible values of input carry i.e. 0 and 1 and evaluate the

result in advance. Once the original value of carry is known,

result can be selected using the multiplexer stage. Therefore

the conventional CSLA makes use of Dual RCAs to

generate the partial sum and carry by considering input carry

C

in

=0 and C

in

=1, then the final sum and carry are selected by

multiplexers. Fig. 2 shows the 16-bit Conventional CSLA.

ISSN (Print) : 2319-5940

ISSN (Online) : 2278-1021

International J ournal of Advanced Research in Computer and Communication Engineering

Vol. 2, Issue 9, September 2013

Copyright to IJARCCE www.ijarcce.com 3706

The conventional CSLA is area consuming due to the use of

dual RCAs.

Fig. 1 4-bit Ripple Carry Adder

The basic idea of this work is to use Binary to Excess- 1

converter (BEC) instead of RCA with C

in

=1 in conventional

CSLA in order to reduce the area and power. [2][3] BEC

uses less number of logic gates than N-bit full adder

structure. To replace N-bit RCA, an N+1 bit BEC is

required. Therefore, Modified CSLA has low power and less

area than conventional CSLA. SQRT CSLA has been chosen

for comparison with modified design using BEC as it has

more balanced delay, less area and low power [4]. Regular

SQRT CSLA also uses dual RCAs. In order to reduce the

delay, area and power, the design is modified by using BEC

instead of RCA with C

in

=1. Therefore, the modified SQRT

CSLA occupies less area, delay and low power. Further also,

the parameters like delay, area and power can be reduced.

Fig. 2 16-bit conventional carry select adder

By sharing Common Boolean Logic (CBL), a circuit of

SQRT CSLA is proposed. This proposed design is better

than all the other adders in respect of area, delay and power

consumption.

III. MODIFIED CSLA

The main idea of this work is to use BEC instead of RCA

with carry C

in

=1 in order to reduce the area and power of

conventional CSLA. BEC [3] is a circuit used to add 1 to the

input numbers. Circuit of BEC is shown in Fig. 3. And truth

table is shown in Table I. Goal of addition is achieved using

BEC together with the multiplexer as shown in Fig. 4.One of

the input of 8:4 MUX gets as its inputs(B3,B2,B1 and B0)

and another input of MUX is BEC output. Boolean

expressions of 4-bit BEC are listed below (Note: symbols

~NOT, &AND and ^XOR)

X0= ~B0

X1= B0^B1

X2= B2^(B0&B1)

X3= B3^(B0&B1&B2)

Fig. 3 4-bit Binary to Excess-1 Converter

TABLE I

TRUTH TABLE OF 4-BIT BINARY TO EXCESS-1 CONVERTER

Binary Logic

B

0

B

1

B

2

B

3

Excess-1 Logic

X

0

X

1

X

2

X

3

0000 0001

0001 0010

0010 0011

0011 0100

0100 0101

0101 0110

0110 0111

0111 1000

1000 1001

1001 1010

1010 1011

1011 1100

1100 1101

1101 1110

1110 1111

1111 0000

ISSN (Print) : 2319-5940

ISSN (Online) : 2278-1021

International J ournal of Advanced Research in Computer and Communication Engineering

Vol. 2, Issue 9, September 2013

Copyright to IJARCCE www.ijarcce.com 3707

The main idea of this work is to use BEC instead of RCA

with C

in

=1 in order to get the reduced area and power

consumption of the conventional CSLA. To replace the N-

bit RCA, N+1 bit BEC is required.

Fig.4 4-bit Binary to Excess-1 logic with 8:4 multiplexer

Thus, modified CSLA is designed such that it occupies

less area and has low power than conventional CSLA. Block

diagram of Modified CSLA is shown in Fig. 5.

Fig. 5 Block diagram of 16-bit modified carry select adder

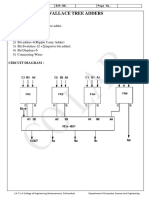

IV. REGULAR SQRT CSLA AND MODIFIED SQRT CSLA

The structure of 16-bit regular SQRT CSLA is shown in Fig.

6. It has five groups of different size RCA. Each group

contains dual RCA and MUX. Conventional CSLA has one

main disadvantage of high area usage. This advantage can be

overcome in Regular SQRT CSLA. So SQRT CSLA is

improved version of Conventional CSLA. Time delay of

conventional CSLA can be decreased by having one more

input into each set of adders than in previous set. This is

known as SQRT CSLA. In SQRT CSLA, group3 has two

sets of 3-bit RCA. Selection input of 8:4 MUX is c3.If c3=0,

then MUX selects first RCA output(C

in

=0) otherwise second

RCA output(C

in

=1) is selected.

Fig.6 Regular 16-bit SQRT CSLA

Modified SQRT CSLA is similar to that of regular

SQRT CSLA, the only difference is we replace RCA with

C

in

=1 with BEC. This replaced BEC performs the same

operation as that of the replaced RCA with C

in

=1. Fig. 7

shows the block diagram of modified SQRT CSLA. This

structure consumes less area, delay and power than regular

SQRT CSLA because of less number of transistors are used.

Modified SQRT CSLA is similar to that of regular SQRT CSLA, the only difference is we replace RCA with C

in

=1 with BEC. This replaced BEC performs the same operation as that of the replaced RCA with C

in

=1. Fig. 7 shows the block diagram of modified SQRT CSLA. This structure consumes

Fig. 7 Modified 16-bit SQRT CSLA

V. PROPOSED SQRT CSLA USING COMMON BOOLEAN

LOGIC

To remove the duplicate adder cells in the conventional

CSLA, an area efficient SQRT CSLA is proposed by sharing

Common Boolean Logic (CBL) term. While analysing the

truth table of single bit full adder, results show that the

output of summation signal as carry-in signal is logic 0 is

ISSN (Print) : 2319-5940

ISSN (Online) : 2278-1021

International J ournal of Advanced Research in Computer and Communication Engineering

Vol. 2, Issue 9, September 2013

Copyright to IJARCCE www.ijarcce.com 3708

inverse signal of itself as carry-in signal is logic 1. It is

illustrated by red circles in Table II. To share the Common

Boolean Logic term, we only need to implement a XOR gate

and one INV gate to generate the summation pair. And to

generate the carry pair, we need to implement one OR gate

and one AND gate. In this way, the summation and carry

circuits can be kept parallel.

TABLE III

TRUTH TABLE OF SINGLE BIT FULL ADDER, WHERE THE UPPER HALF PART

IS THE CASE OF CIN=0 AND THE LOWER HALF PART IS THE CASE OF

CIN=1

This method replaces the Binary to Excess-1 converter

add one circuit by common Boolean logic. As compared

with modified SQRT CSLA, the proposed structure is little

bit faster. Internal structure of proposed CSLA is shown in

Fig. 8.

Fig. 8 Internal structure of the proposed area-efficient carry select adder is

constructed by sharing the common Boolean logic term

In the proposed SQRT CSLA, the transistor count is

trade-off with the speed in order to achieve lower power

delay product. Thus the proposed SQRT CSLA using CBL

is better than all the other designed adders. Fig. 9 shows the

block diagram of Proposed SQRT CSLA.

Fig. 9 16-Bit Proposed SQRT CSLA using Common Boolean Logic

VI. RESULTS

This work has been developed using Xilinx tool. Table III

shows the comparison between the various adders like

conventional CSLA, Modified CSLA, regular SQRT CSLA,

modified SQRT CSLA and proposed SQRT CSLA for 8-bit,

16-bit, 32-bit and 64-bit. The parameters on which they are

compared are area, delay and power. Fig. 10 depicts that the

proposed SQRT CSLA has less number of gates and hence

less area. Fig. 11 shows the adder circuit for delay

comparison. The results compared in Fig. 12 shows that the

power consumption of proposed SQRT CSLA is reduced. It

is clear that power, area and delay of proposed SQRT CSLA

for 8-bit, 16-bit, 32-bit and 64-bit is reduced as compared to

other adders.

TABLE IIIII

COMPARISON OF ADDERS FOR AREA, DELAY, POWER AND POWER DELAY

PRODUCT

Wor

d

Size

Adder Area

(No. of

gate

count)

Delay

(ns)

Power

(mW)

Power

Delay

Product

(pWs)

8-bit

Conventional

(Dual RCA)

200 14.46 94.48 1366.36

Modified

(with BEC)

167 16.63 86.92 1445.47

Regular

SQRT (Dual

RCA)

144 11.92 193 2300.56

Modified

SQRT(with

132 13.69 180 2464.2

ISSN (Print) : 2319-5940

ISSN (Online) : 2278-1021

International J ournal of Advanced Research in Computer and Communication Engineering

Vol. 2, Issue 9, September 2013

Copyright to IJARCCE www.ijarcce.com 3709

BEC)

Proposed

SQRT(with

CBL)

111 11.15 119 1326.85

16-

bit

Conventional

(Dual RCA)

480 19.81 94.63 1874.90

Modified

(with BEC)

381 21.59 81.38 1757.48

Regular

SQRT (Dual

RCA)

348 16.15 315 5087.25

Modified

SQRT(with

BEC)

291 18.77 268 5030.36

Proposed

SQRT(with

CBL)

276 15.48 177 2739.96

32-

bit

Conventional

(Dual RCA)

1040 30.51 95.01 2899.42

Modified

(with BEC)

809 32.65 79.81 2605.79

Regular

SQRT (Dual

RCA)

698 28.97 553 16020.4

1

Modified

SQRT(with

BEC)

762 34.44 448 15429.1

2

Proposed

SQRT(with

CBL)

552 26.23 321 8419.23

64-

bit

Conventional

(Dual RCA)

2160 51.92 95.49 4958.22

2

Modified

(with BEC)

1665 54.01 79.25 4280.29

2

Regular

SQRT (Dual

RCA)

1592 52.82 860 45425.2

Modified

SQRT(with

BEC)

1498 64.61 745 48134.4

5

Proposed

SQRT(with

CBL)

1104 47.74 555 26495.7

Fig. 10 Comparison of adders for area (no. of gate count)

Fig. 11 Comparison of adders for delay

Fig. 12 Comparison of adders for power

ISSN (Print) : 2319-5940

ISSN (Online) : 2278-1021

International J ournal of Advanced Research in Computer and Communication Engineering

Vol. 2, Issue 9, September 2013

Copyright to IJARCCE www.ijarcce.com 3710

VII. CONCLUSION

Power, delay and area are the constituent factors in VLSI

design that limits the performance of any circuit. This work

presents a simple approach to reduce the area, delay and

power of CSLA architecture. The conventional carry select

adder has the disadvantage of more power consumption and

occupying more chip area. The proposed SQRT CSLA using

common Boolean logic has low power, less delay and

reduced area than all the other adder structures. It is also

little bit faster than all the other adders. In this way, the

transistor count of proposed SQRT CSLA is reduced having

less area and low power which makes it simple and efficient

for VLSI hardware implementations.

VIII. FUTURE SCOPE

This work has been designed for 8-bit, 16-bit, 32-bit and 64-

bit word size and results are evaluated for parameters like

area, delay and power. This work can be further extended for

higher number of bits. New architectures can be designed in

order to reduce the power, area and delay of the circuits.

Steps may be taken to optimize the other parameters like

frequency, number of gate clocks, length etc.

REFERENCES

[1] Kuldeep Rawat, Tarek Darwish and Magdy Bayoumi, A low power

and reduced area Carry Select Adder, 45th Midwest Symposium on

Circuits and Systems, vol.1, pp. 467-470, March 2002.

[2] Y. Kim and L.-S. Kim, "64-bit carry-select adder with reduced area, "

Electron. Lett. vol. 37, no. 10, pp. 614- 615, May 2001.

[3] J. M. Rabaey, Digtal Integrated Circuits-A Design Perspective.Upper

Saddle River, NJ: Prentice-Hall,2001.

[4] Cadence, "Encounter user guide, " Version 6.2.4, March 2008.

[5] R. Priya and J. Senthil Kumar, Enhanced area efficient architecture for

128 bit Modified CSLA, International Conference on Circuits, Power and

Computing Technologies,2013.

[6] Shivani Parmar and Kirat pal Singh,Design of high speed hybrid carry

select adder,IEEE ,2012.

[7] I-Chyn Wey, Cheng-Chen Ho, Yi-Sheng Lin, and Chien-Chang Peng,

An Area-Efficient Carry Select Adder Design by Sharing the Common

Boolean Logic Term, Proceedings of the International MultiConference of

Engineers and Computer Scientist 2012 Vol II,IMCES 2012,Hong-

Kong,March 14-16 2012.

[8] B. Ramkumar and Harish M Kittur, Low-Power and Area-Efficient

Carry Select Adder, IEEE Transactions on Very Large Scale Integration

(VLSI) Systems, VOL. 20, NO. 2, February 2012.

[8] Ms. S.Manjui, Mr. V. Sornagopae, An Efficient SQRT Architecture of

Carry Select Adder Design by Common Boolean Logic,IEEE, 2013.

[9] Youngjoon Kim and Lee-Sup Kim, 64-bit carry-select adder with

reduced area, Electronics Letters, vol.37, issue 10, pp.614-615, May 2001.

[10] Yajuan He, Chip-Hong Chang and Jiangmin Gu, An area efficient 64-

bit square root Carry-Select Adder for low power applications, IEEE

International Symposium on Circuits and Systems,vol.4, pp.4082-4085,

May 2005.

[11] Youngjoon Kim and Lee-Sup Kim, A low power carry select adder

with reduced area, IEEE International Symposium on Circuits and

Systems, vol.4, pp.218-221, May 2001.

[12] Hiroyuki Morinaka, Hiroshi Makino, Yasunobu Nakase, Hiroaki

Suzuki and Koichiro Mashiko, A 64bit Carry Look-ahead CMOS Adder

using Modified Carry Select,Proceeding of IEEE on Custom Integrated

Circuits Conference, pp.585-588, May 1995.

[13] June Wang, Zhongde Wang, G.A. Jullien and W.C. Miller, Areatime

analysis of Carry Lookahead Adders using enhanced multiple output

domino logic, IEEE International Symposium on Circuits and systems,

vol.4, pp.59-62, June 1994.

[14] Akhilesh Tyagi, A reduced-area scheme for Carry-Select Adders,

IEEE transaction on Computers, vol. 42, pp.1163-1170, October 1993.

[15] David Jeff Jackson and Sidney Joel Hannah, Modelling and

Comparison of Adder Designs with Verilog HDL, 25th

Southeastern Symposium on System Theory, pp.406-410, March 1993.

[16] Akhilesh Tyagi, A Reduced Area Scheme for Carry-Select Adders,

IEEE International Conference on Computer design, pp.255-258, Sept

1990.

[17] O. J. Bedrij, Carry-Select Adder, IRE transactions on Electronics

Computers, vol.EC-11, pp. 340-346, June1962.

[18] Neil H.E.Weste and K.Eshraghian, Principle Of CMOS VLSI designs:

a system perspective, (Addison-Wesley, 1998), 2nd edn, 1998.

[19] Richard P. Brent and H. T. Kung, A Regular Layout for Parallel

Adders, IEEE transactions on Computers, vol.c-31, pp.260-264, March

1982.

[20] David Jeff Jackson and Sidney Joel Hannah, Modelling and

Comparison of Adder Designs with Verilog HDL, 25th Southeastern

Symposium on System Theory, pp.406-410, March 1993.

BIOGRAPHY

Pallavi Saxena received her B.

Tech. degree in Electronics And

Instrumentation from Hindustan

College of Science And

Technology, Mathura, Uttar

Pradesh, India affiliated to Gautam

Buddha technical University,

Lucknow, Uttar Pradesh, India in

2012.At present, she is pursuing M. Tech. in VLSI Design.

Her areas of interest are Low Power VLSI Design and

Digital Electronics.

Urvashi Purohit received her B.

Tech. Degree in Electronics And

communication from Sobhasaria

Engineering College, Sikar ,

Rajasthan, India affiliated to Rajasthan

Technical University, Kota, Rajastha,

India in 2012. At present, she is

pursuing M. Tech. in VLSI Design.

Her areas of interest are Digital

communication and Digital Electronics.

Priyanka Joshi is currently working

as Faculty in ECE Department at

Mody Institute of Technology and

Science, Lakshmangarh.

Das könnte Ihnen auch gefallen

- Identifying The Water Level in The Overhead TankDokument9 SeitenIdentifying The Water Level in The Overhead TankRamakrishna SagarNoch keine Bewertungen

- 3.1 Conceptualization of Smart Urban Transportation SystemsDokument10 Seiten3.1 Conceptualization of Smart Urban Transportation SystemsRamakrishna SagarNoch keine Bewertungen

- Coursera VYVHHPE4UJSY PDFDokument1 SeiteCoursera VYVHHPE4UJSY PDFRamakrishna SagarNoch keine Bewertungen

- Session 1: Conceptualization of Smart Urban Energy SystemsDokument12 SeitenSession 1: Conceptualization of Smart Urban Energy SystemsRamakrishna SagarNoch keine Bewertungen

- IdeatationDokument1 SeiteIdeatationRamakrishna SagarNoch keine Bewertungen

- Module 1 Lecture 1 - Productive vs. Unproductive Work PDFDokument12 SeitenModule 1 Lecture 1 - Productive vs. Unproductive Work PDFRamakrishna SagarNoch keine Bewertungen

- Cities As Complex Socio-Technical SystemsDokument7 SeitenCities As Complex Socio-Technical SystemsRamakrishna SagarNoch keine Bewertungen

- Strategic Reserve Time TemplatesDokument2 SeitenStrategic Reserve Time TemplatespcmtpcmtNoch keine Bewertungen

- Piezoelectrictransducer 141128011014 Conversion Gate01 PDFDokument60 SeitenPiezoelectrictransducer 141128011014 Conversion Gate01 PDFRamakrishna SagarNoch keine Bewertungen

- Advanced Inspection by Acoustic Emission (AE) On-Line or Off-LineDokument23 SeitenAdvanced Inspection by Acoustic Emission (AE) On-Line or Off-LineRamakrishna SagarNoch keine Bewertungen

- Useofsensorsinstructuralengineeringbypirpashaujede 130320223207 Phpapp01Dokument24 SeitenUseofsensorsinstructuralengineeringbypirpashaujede 130320223207 Phpapp01Ramakrishna SagarNoch keine Bewertungen

- Presented By-Pardeep Dahiya 13001504023 M.Tech. MechanicalDokument20 SeitenPresented By-Pardeep Dahiya 13001504023 M.Tech. MechanicalRamakrishna SagarNoch keine Bewertungen

- Environmental EnggDokument72 SeitenEnvironmental EnggRamakrishna SagarNoch keine Bewertungen

- Service ConditionsDokument19 SeitenService ConditionsRamakrishna SagarNoch keine Bewertungen

- R09-Theory and Analysis of PlatesDokument1 SeiteR09-Theory and Analysis of PlatesRamakrishna SagarNoch keine Bewertungen

- Lecture1 PDFDokument8 SeitenLecture1 PDFRamakrishna SagarNoch keine Bewertungen

- AtmsDokument2 SeitenAtmsRamakrishna SagarNoch keine Bewertungen

- Irc 70-1977Dokument18 SeitenIrc 70-1977pradeepgollapudiNoch keine Bewertungen

- Load Test On Scharge MotorDokument4 SeitenLoad Test On Scharge MotorRamakrishna SagarNoch keine Bewertungen

- General NotesDokument1 SeiteGeneral NotesRamakrishna SagarNoch keine Bewertungen

- Structural EnggDokument24 SeitenStructural EnggKrishna Prakash NanduriNoch keine Bewertungen

- 3112 Vlsics 13Dokument16 Seiten3112 Vlsics 13Ramakrishna SagarNoch keine Bewertungen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Comparator Design Using Full Adder: July 2014Dokument5 SeitenComparator Design Using Full Adder: July 2014John Mark Manalo RosalesNoch keine Bewertungen

- Sap 1 2Dokument21 SeitenSap 1 2Brandon Maciel50% (2)

- Questions From 10 Question Papers: Module 1: Number Systems and CodesDokument4 SeitenQuestions From 10 Question Papers: Module 1: Number Systems and Codesvidhya seemanNoch keine Bewertungen

- 4bit Array MultiplierDokument4 Seiten4bit Array MultiplierRahul TiwariNoch keine Bewertungen

- DcsDokument50 SeitenDcskartikNoch keine Bewertungen

- Laboratory Activity 3 VHDL Modeling of Arithmetic Circuits: Digital Systems Design LaboratoryDokument21 SeitenLaboratory Activity 3 VHDL Modeling of Arithmetic Circuits: Digital Systems Design LaboratoryFrancis CadienteNoch keine Bewertungen

- Implementation and Testing of Adders Using BistDokument52 SeitenImplementation and Testing of Adders Using BistDeepthi Veeramachaneni50% (2)

- Unit 4 Combinational CircuitDokument22 SeitenUnit 4 Combinational CircuitAnurag GoelNoch keine Bewertungen

- VLSI 7th Sem Lab Manual PDFDokument66 SeitenVLSI 7th Sem Lab Manual PDFFootlooseNoch keine Bewertungen

- Computer Architecture and OrganizationDokument26 SeitenComputer Architecture and OrganizationSrishti JainNoch keine Bewertungen

- VASANTHDokument61 SeitenVASANTHVasanth PerniNoch keine Bewertungen

- ElectronicMechanic (NSQF) 2ndSEMtpDokument179 SeitenElectronicMechanic (NSQF) 2ndSEMtpMd SalmanNoch keine Bewertungen

- Exp 3Dokument3 SeitenExp 3Cherry Charan TejNoch keine Bewertungen

- Design and Implementation of High Frequency 16-Bit Full Adder On FPGA FamiliesDokument7 SeitenDesign and Implementation of High Frequency 16-Bit Full Adder On FPGA Familiesnikhilreddy522002Noch keine Bewertungen

- Chapter 4: Basics of Digital Electronics: Logic GatesDokument19 SeitenChapter 4: Basics of Digital Electronics: Logic GatesSyed ShaNoch keine Bewertungen

- Combinational Logic: CS270 Max Luttrell, Fall 2016Dokument67 SeitenCombinational Logic: CS270 Max Luttrell, Fall 2016kNoch keine Bewertungen

- Analysis of 8 X 8 BitDokument4 SeitenAnalysis of 8 X 8 BitDwarakaManeekantaAddagiriNoch keine Bewertungen

- CALab - Jalish BuktawarDokument19 SeitenCALab - Jalish BuktawarSouvik PalNoch keine Bewertungen

- EasaDokument33 SeitenEasaAlaa MortadaNoch keine Bewertungen

- Register Transfer and MicrooperationsDokument18 SeitenRegister Transfer and MicrooperationsShivam RaiNoch keine Bewertungen

- 21ELN24 - Question Bank For ExamDokument4 Seiten21ELN24 - Question Bank For ExamEmail ServiceNoch keine Bewertungen

- Ghazipur Class 12 Summer Vacation HomeworkDokument5 SeitenGhazipur Class 12 Summer Vacation HomeworkTitan'S HereNoch keine Bewertungen

- Second-Order IIR Digital Filter Macro (IIR) : Serial Data Input Serial Data Output Y YDokument3 SeitenSecond-Order IIR Digital Filter Macro (IIR) : Serial Data Input Serial Data Output Y YMarrowsNoch keine Bewertungen

- Verilog Code On 8 X 8 Wallace Tree MultiplierDokument5 SeitenVerilog Code On 8 X 8 Wallace Tree MultiplierNick để họcNoch keine Bewertungen

- Embedded Systems Lab (17CS. 6 Semester) Lab Experiment No. 8 Designing of Combinational Circuits (Full-Adder & Comparator)Dokument9 SeitenEmbedded Systems Lab (17CS. 6 Semester) Lab Experiment No. 8 Designing of Combinational Circuits (Full-Adder & Comparator)NoorNoch keine Bewertungen

- Student Kit MCA-IDokument24 SeitenStudent Kit MCA-ImilinjdNoch keine Bewertungen

- DE LAB Question BankDokument2 SeitenDE LAB Question BankMalayalam TechNoch keine Bewertungen

- 3 NotesDokument122 Seiten3 NoteschinnarrrNoch keine Bewertungen

- Assignment ModelDokument8 SeitenAssignment ModelKarthik KarthiksNoch keine Bewertungen

- Design & Study of A Low Power High Speed Full Adder Using GDI Multiplexer DocumentationDokument15 SeitenDesign & Study of A Low Power High Speed Full Adder Using GDI Multiplexer Documentationbharath kishore reddyNoch keine Bewertungen