Beruflich Dokumente

Kultur Dokumente

PDH Definicion

Hochgeladen von

Andres Felipe Sierra CorreaOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

PDH Definicion

Hochgeladen von

Andres Felipe Sierra CorreaCopyright:

Verfügbare Formate

JERARQUIA DIGITAL PLESIOCRONA (PDH)

DEFINICIN

Es una tecnologa usada en telecomunicacin tradicionalmente para telefona

que permite enviar varios canales telefnicos sobre un mismo medio (ya sea

cable coaxial, radio o micro ondas) usando tcnicas de multiplexacin por

divisin de tiempo y equipos digitales de transmisin. Tambin puede enviarse

sobre fibra ptica (SDH).

El trmino plesicrono se deriva del gr. plesio, cercano y chronos, tiempo, y se

refiere al hecho de que las redes PDH funcionan en un estado donde las

diferentes partes de la red estn casi, pero no completamente sincronizadas.

PDH permite la transmisin de flujos de datos que, nominalmente, estn

funcionando a la misma velocidad (bit rate), pero permitiendo una cierta

variacin alrededor de la velocidad nominal gracias a la forma en la que se

forman las tramas.

Las jerarquas Plesicronas PDH usan un reloj para cada nivel de

multiplexacin independiente de los otros niveles. En oposicin se encuentra la

jerarqua Sincrnica SDH que adopta un solo reloj para toda la red.

JERARQUIAS DIGITALES

En la transmisin de seales digitales se recurre a la multiplexacin con el fin

de agrupar varios canales en un mismo vnculo. Si bien la velocidad bsica

usada en las redes digitales se encuentra estandarizada en 64 kb/s, las

velocidades de los rdenes de multiplexacin en cambio forman varias

jerarquas.

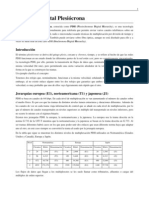

Existen tres jerarquas PDH: la europea, la americana y la japonesa.

La europea usa la trama descrita en la norma G.732 de la UIT-T mientras que

la americana y la japonesa se basan en la trama descrita en G.733.

Al ser tramas diferentes habr casos en los que para poder unir dos enlaces

que usan diferente norma haya que adaptar uno al otro, en este caso siempre

se convertir la trama al usado por la jerarqua europea:

LA JERARQUA EUROPEA, USADA TAMBIN EN LATINOAMRICA

La trama bsica utilizada pertenece al estndar Europeo y es de 2 Mbps

denominada trama E1, la cual resulta de la agrupacin de 32 canales de 64

kbps: 30 de voz y 2 de control (sincronismo y sealizacin). La trama E1 se

repite cada 125 s.

Luego, al multiplexar 4 tributarios sucesivamente, se obtiene las velocidades

de 8.448 kb/s para la trama E2; 34.368 kb/s para la E3, y 139.264 kb/s en la

trama E4.

LA JERARQUA NORTEAMERICANA (T1)

T1 define la trama bsica del estndar PDH de Norteamrica que consiste de

24 canales de 64 Kbps dando una capacidad total de 1.544 Mbps

Posteriormente generan 2 rdenes superiores (x4) a 6.312 kb/s y (x7) a 44.736

kb/s.

JERARQUIA JAPONESA (J1)

J1 define el estndar PDH japons para una velocidad de transmisin de 1.544

Mbps consistente de 24 canales de 64 Kbps

La jerarqua japonesa recupera el valor de 6.312 kb/s pero obtiene los rdenes

jerrquicos de (x5) 32.064 kb/s y (x3) 97.728 kb/s.

La longitud de la trama del estndar J1 es de 193 bits (24 x 8 bit, canales de

voz/datos ms un bit de sincronizacin), el cual es transmitido a una tasa de

8000 tramas por segundo. As, 193 bits/trama x 8000 tramas/segundo = 1,

544,000 bps o 1.544 Mbps

Las velocidades de cada orden son levemente superiores al producto de la

velocidad de tributario por el nmero de entradas, debido al agregado de

informacin adicional (OverHead).

PDH se basa en canales de 64 Kbps En cada nivel de multiplexacin se van

aumentando el nmero de canales sobre el medio fsico. Es por eso que las

tramas de distintos niveles tienen estructuras y duraciones diferentes. Adems

de los canales de voz en cada trama viaja informacin de control que se aade

en cada nivel de multiplexacin, por lo que el nmero de canales transportados

en niveles superiores es mltiplo del transportado en niveles inferiores.

En la siguiente tabla podemos observar distintos niveles de multiplexacin PDH

que tiene cada una de las jerarquas mencionadas anteriormente.

Nivel

Norteamrica Europa Japn

Circuitos kbit/s Denominacin Circuitos kbit/s Denominacin Circuitos kbit/s Denominacin

1 24 1544 (T1) 30 2048 (E1) 24 1544 (J1)

2 96 6312 (T2) 120 8448 (E2) 96 6312 (J2)

3 672 44 736 (T3) 480 34 368 (E3) 480 32 064 (J3)

4 4032 274 176 (T4) 1920 139 264 (E4) 1440 97 728 (J4)

Los flujos de datos que llegan a los multiplexores se les suele llamar como

tributarios, afluentes o cargas del mltiplex de orden superior la mayora de las

veces.

JERARQUA EUROPEA

La velocidad bsica de transferencia de informacin, o primer nivel jerrquico,

es un flujo de datos de 2,048 Mbps Para transmisiones de voz, se digitaliza la

seal mediante MIC usando una frecuencia de muestreo de 8 kHz (una

muestra por cada 125 s) y cada muestra se codifica con 8 bits con lo que se

obtiene un rgimen binario de 64 kbps Agrupando 30 canales de voz ms otros

2 canales de 64 kbps, utilizados para sealizacin y sincronizacin, formamos

un flujo PDH E1. De forma alternativa es posible tambin utilizar el flujo

completo de 2 megas para usos no vocales, tales como la transmisin de

datos.

La velocidad del flujo de datos de 2 megas es controlada por un reloj en el

equipo que la genera. A esta velocidad se le permite una variacin, alrededor

de la velocidad exacta de 2,048 Mbps, de 50 ppm (partes por milln). Esto

significa que dos flujos diferentes de 2 megas pueden estar (y probablemente

lo estn) funcionando a velocidades ligeramente diferentes uno de otro.

Al fin de poder transportar mltiples flujos de 2 megas de un lugar a otro, estos

son combinados, o multiplexados en grupos de cuatro en un equipo multiplexor.

La multiplexacin se lleva a cabo tomando un bit del flujo 1, seguido por un bit

del flujo 2, luego otro del 3 y finalmente otro del 4. El multiplexor adems aade

bits adicionales a fin de permitir al demultiplexor del extremo distante

decodificar qu bits pertenecen a cada flujo de 2 megas y as reconstituir los

flujos originales.

Estos bit adicionales son, por un lado, los denominados bits de justificacin o

de relleno y por otro una combinacin fija de unos y ceros que es la

denominada palabra de alineamiento de trama que se transmite cada vez que

se completa el proceso de transmisin de los 30+2 canales de los 4 flujos de 2

megas, que es lo que constituye una trama del orden superior (8 megas).

La necesidad de los bits de relleno o justificacin es que como cada uno de los

flujos de 2 megas no est funcionando necesariamente a la misma velocidad

que los dems, es necesario hacer algunas compensaciones. Para ello el

multiplexor asume que los cuatro flujos estn trabajando a la mxima velocidad

permitida, lo que conlleva que, a menos que realmente est sucediendo esto,

en algn momento el multiplexor buscar el prximo bit, pero este no llegar,

por ser la velocidad del flujo inferior a la mxima.

En este caso el multiplexor sealizar (mediante los bits de justificacin) al

demultiplexor que falta un bit. Esto permite al demultiplexor reconstruir

correctamente los flujos originales de los cuatro 2 megas y a sus velocidades

plesicronas correctas.

La velocidad del flujo resultante del proceso antes descrito es de 8,448 Mbps (8

megas) que corresponde al segundo nivel jerrquico.

Por procedimientos similares se llega a los niveles tercero, constituido por 4

flujos de 8 megas y una velocidad de 34,368 Mbps (34 megas) y cuarto,

formado por 4 flujos de 34 megas y una velocidad de 139,264 Mbps (140

megas).

De la misma forma, mediante la multiplexacin de 4 flujos de 140 megas, se

forma un flujo de 565 Mbit/s, pero su estructura y proceso de multiplexacin, al

contrario de lo que sucede con los cuatro niveles precedentes, no han sido

normalizados por los organismos de normalizacin especializados UIT y CEPT,

por lo que los flujos generados por los equipos de un fabricante pueden ser, y

de hecho lo son, incompatibles con los de otro fabricante, lo que obliga a que el

enlace completo de 565 Mbps est constituido con terminales del mismo

fabricante.

La velocidad de 565 Mbps es la tpica de los sistemas de transmisin por fibra

ptica, aunque en el pasado se ha utilizado, pero con escaso xito por sus

estrictos requerimientos, sobre cables coaxiales.

MULTIPLEXACION

La multiplexacion en la jerarqua PDH, se realiza utilizando el mtodo de

entrelazado bit a bit.

Esto quiere decir que la seal de entrada de un dado multiplexor aparecer

solamente cada 4 bits de la seal de salida del mismo.

En la multiplexacin, habra que diferenciar dos casos:

a) Las seales originales son sincrnicas, por ejemplo tienen exactamente el

mismo reloj. En este caso el proceso de multiplexacin se reduce a una simple

conversin paralelo- serie de las palabras codificadas de 8 bits.

b) Las seales originales no son sincrnicas, por ejemplo sus relojes provienen

de distintos lugares. Aqu es necesario tomar medidas apropiadas con el fin de

compensar las diferencias de relojes.

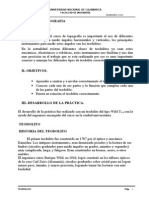

En el sistema europeo, se tiene hasta cinco jerarquas, como se puede

observar en la siguiente tabla.

Jerarqua Velocidad Canales Trama

E1 2048 Kbit/s 30 256 bits = 125 us

E2 8448 Kbit/s 120 848 bits = 100.38 us

E3 34368 Kbit/s 480 1536 bits = 44,7 us

E4 139268 Kbit/s 1920 2904 bits = 20.85 us

E5 564992 Kbit/s 7680 2688 bits = 4.7 us

Un equipo multiplexor recibe un nmero N de seales numricas, llamadas

tributarios, que se presentan a su entrada en paralelo y produciendo una seal

digital de mayor velocidad de informacin como mnimo N veces superior a la

de los tributarios.

fm >= N ft

fm = frecuencia mltiplo.

ft = frecuencia de tributario.

Los tributarios de entrada debern estar en fase y en igualdad de

frecuencia entre s, pero en realidad no es as sino que tienen distinta

fase entre s y variacin de las frecuencias.

A cada seal tributaria se le aaden unos bits que se llaman de relleno

o de justificacin, y unos bits que se llaman de control de justificacin,

para que el extremo receptor pueda distinguir los bits que son de

informacin y los que son de relleno. Este proceso es conocido como

justificacin, y tiene por objeto absorber las ligeras diferencias de

frecuencia que pueden presentar los distintos tributarios, ya que pueden

haberse constituido con fuentes de reloj diferentes. De esta forma, a los

tributarios ms lentos es necesario aadirles ms bits de relleno que a

los tributarios ms rpidos. En el extremo receptor, los bits de relleno

son oportunamente reconocidos y cancelados gracias a la informacin

que transportan consigo los bits de control de la justificacin. En

consecuencia, la velocidad de la seal agregada es mayor que la suma

de las velocidades de las seales tributarias.

fm > N ft ---> fm = (N ft) + fr

fr = frecuencia de los bits de redundancia.

Los equipos PDH estn siendo actualmente reemplazados por equipos de

tecnologa SDH en la mayora de las redes de telecomunicacin debido a las

mayores capacidades de transmisin de estos y a sus mejores condiciones

para la operacin y mantenimiento centralizado.

Equipos Mltiplex PDH de la Jerarqua de Transmisin Europea

Modelos:

Equipo Mltiplex digital plesicrono de 2/8 Mbit/s: Equipo que en transmisin

combina 4 seales tributarias a 2,048 Mbit/s, de forma que a la salida se

obtiene una seal mltiplex de 8,448 Mbit/s. En recepcin lleva a cabo la

funcin complementaria.

Equipo Mltiplex digital plesicrono de 8/34 Mbit/s: Equipo que en transmisin

combina 4 tributarios de 8,448 Mbit/s, de forma que a la salida se obtiene una

seal mltiplex de 34,368 Mbit/s. En recepcin lleva a cabo la funcin

complementaria.

Equipo Mltiplex digital plesicrono de 34/140 Mbit/s: Equipo que en

transmisin combina 4 tributarios de 34,368 Mbit/s, de forma que a la salida se

obtiene una seal mltiplex de 139,264 Mbit/s. En recepcin lleva a cabo la

funcin complementaria.

Equipo Mltiplex digital plesicrono de 140/565 Mbit/s: Equipo que en

transmisin combina 4 tributarios de 139,264 Mbit/s, de forma que a la salida

se obtiene una seal mltiplex de 564,992 Mbit/s. En recepcin lleva a cabo la

funcin complementaria. No est normalizado por la ITU-T. Tambin se

denomina mltiplex digital 4 x 140 Mbit/s

Caractersticas:

Multiplexan 4 tributarios, N = 4.

El tipo de multiplexacin de los tributarios es bit a bit.

Los bits de cada tributario no se presentan en la entrada en una posicin fija

(seales plesicronas), ya que estn controlados por relojes diferentes, que

son a su vez distintos del reloj que controla la seal mltiplex, por lo que puede

darse una superposicin de bits al constituir la trama. Para resolver este

problema se emplea la justificacin positiva.

La ITU-T define en la G.701 que dos seales digitales que tengan la misma

velocidad nominal V (bit/s), que mantengan sus desviaciones mximas

respecto a esta cadencia dentro de lmites especificados V (bit/s) y que no

provengan del mismo reloj son seales digitales plesicronas.

ESTRUCTURA DE TRAMA:

La trama de un equipo mltiplex digital plesicrono estar formada por:

bits de alineacin de trama para la sincronizacin de la parte receptora

del equipo mltiplex JDP distante.

bit de alarma (A). Indicacin de alarma a la parte receptora del mltiplex

JDP distante, cuando A=1.

bits de servicio (S) de uso nacional.

bits de informacin (Ii) de cada tributario (i), multiplexados bit a bit.

bits de control de justificacin (Ci1Ci N). Son de 3 a 5 bits por cada

tributario i, que estn situados en posiciones fijas de la trama. Para cada

tributario, indica al receptor distante que s hay / no hay justificacin para

ese tributario en esa trama.

bits de justificacin (Ji). Es 1 bit por cada tributario i, que est situado en

una posicin fija de la trama. Para cada tributario, puede ser un bit de

justificacin (valor 1) o un bit de informacin (valor 0 1), de pendiendo

del valor de los bits de control de ese tributario:

Si Ci1 Ci N = 111, ser un bit de justificacin valor 1

Si Ci1... Ci N = 000, ser un bit de informacin valor 0 1

CANAL DE ADMINISTRACION TIME SLOT 0

Contiene los bits de encabezado de la norma g.704

Se utiliza para enviar:

Sincronizacin

Alineamiento de trama (FAS)

Informacin de supervisin del enlace.

Indicador de alarma remota

Verificacin de Redundancia cclica (CRC)

PROCESO DE ALINEAMIENTO DE TRAMA

El alineamiento de la trama consiste en 10 bits que permiten el sincronismo del

receptor.

- Cuando se detectan con error 4 palabras consecutivas se produce la perdida

el alineamiento de trama LOF; para recuperar el alineamiento de la trama se

deben leer correctamente 3 palabras consecutivas.

- En tanto dura la falta de alineamiento, la seal de los tributarios se remplaza

por una seal de indicacin de alarma AIS consistente en una secuencia de

bits 1.

Cuando se multiplexan diferentes seales en una de nivel superior (por ejemplo

4 E1 en una E2), cada una con su propia seal de reloj, es preciso

sincronizarlas en el multiplexor.

Canal de Sealizacin TS16

Existen dos formas genricas de enviar la sealizacin de los canales de

telefona en el multiplexor E1:

1. Sealizacin por Canal Asociado (CAS): Es una sealizacin que requiere la

disponibilidad de un canal exclusivo para tareas de sealizacin. Define los

protocolos que deben establecerse entre usuarios para los siguientes casos:

Cuando el usuario levanta el telfono.

Cuando uno de los usuarios empieza a marcar el nmero.

Cuando el usuario llama, etc.

2. Sealizacin por Canal Comn CCS o SSNo7: Es un conjunto de protocolos

de sealizacin telefnica empleado en la mayor parte de redes telefnicas

mundiales. Su principal propsito es el establecimiento y finalizacin de

llamadas, no requiere la disposicin de un canal exclusivo, liberando el TS16

en el caso del E1.

DETECCIN DE ERRORES

La deteccin de errores se ejecuta sobre la secuencia de alineamiento de

trama (TS0 de las tramas pares), de forma que el receptor que ejecuta la

medida compara la secuencia recibida en este octeto con el patrn.

Este mtodo es poco exhaustivo, pues testea nicamente 8 bits de cada 512,

pero es el que se utiliza en ausencia de implementacin de CRC.

La CRC por sus siglas en ingls, es un mtodo de control de errores y una de

sus finalidades es el monitoreo de errores, donde controla el BER de un enlace

digital de extremo a extremo, el cdigo CRC se coloca al crear la trama y se

mantiene con ella hasta el final donde el receptor la analiza para ver si ocurri

un error. El CRC no es ms que un conjunto de bits de paridad usados para el

control de la tasa de error.

ALARMAS

Encontramos las siguientes:

Prdida de Trama (LOS)

La alarma en PDH denominada LOS (Lost of frame), se dispara cuando el nivel

de la seal se encuentra por debajo de un BER de 1 en 10, esto puede ocurrir

cuando se corta el cable de transmisin o existe mucha atenuacin en la seal.

La alarma ser retirada cuando se detecten dos tramas PDH y no nuevas

seales de LOS.

Algunos criterios para la deteccin y desaparicin de la seal de LOS segn la

norma G.775 son:

Se detecta una seal de LOS en una interfaz de 64 kbps cuando se tiene

una ausencia de seal por un periodo de 31 us a 30 ms.

Se detecta una seal de LOS en una interfaz de 2048 Kbps cuando se tiene

una ausencia de seal por un periodo de 5 us a 1 ms.

Se detecta una seal de LOS en una interfaz de 8448 Kbps cuando se tiene

una ausencia de seal por un periodo de 1.2us a 1 ms.

Se detecta una seal de LOS en una interfaz de 34368 Kbps cuando se

tiene una ausencia de seal por un periodo de 0.3us a 1 ms.

Se detecta una seal de LOS en una interfaz de 139264 Kbps cuando se

tiene una ausencia de seal por un periodo de 36ns a 1 ms.

En todos los casos la alarma desaparecer cuando se detecte la transmisin

de seales, el trmino de las alarmas debe ser comunicado casi en el mismo

periodo sealado en la aparicin de la alarma.

SEAL INDICADORA DE ALARMA (AIS)

La alarma denominada AIS (AlarmIndicationSignal) es una seal de

informacin caracterstica que poseen todas las jerarquas SDH. Es generada

para reemplazar el trfico normal cuando este contiene una condicin

defectuosa para poder prevenir fallos.

Algunos criterios para la deteccin y desaparicin de la seal de AIS segn la

norma G.775 son:

- Dos criterios diferentes para la deteccin de AIS en una interfaz de 64 kbps:

La seal de 64 kbps contiene 5 o menos ceros en una secuencia de 128

unos.

La seal de 64 kbps de unos sin trama con una duracin de 15.6 ms no

debe contener ms de 0.20.1% ceros.

- Dos criterios diferentes para la deteccin de AIS en una interfaz de 2048

kbps:

La seal de 2048 kbps contiene 2 o menos ceros en una secuencia de 512

bits (250 us).

La seal de 64 kbps de unos sin trama con una duracin de 0.5 ms no debe

contener ms de 0.20.1% ceros.

La seal de entrada tiene 1 o menos ceros en cada una de dos periodos de

tramas consecutivas (512 bits por doble trama).

En todos los casos la alarma desaparece cuando dos o menos ceros son

detectados en una secuencia de 3156 bits.

REMOTEDEFECTINDICATION (RDI)

La alarma denominada RDI (RemoteDefectIndication) es una seal que se

enva al equipo transmisor cuando se detectan alarmas como Lost of Frame,

Lost of Signal o AIS. Algunos criterios para la deteccin y desaparicin de la

seal de RDI segn la norma G.775 son:

- Criterio para la deteccin de una alarma RDI en un nivel TS-16:

La alarma se activa con un solo bit y se configura como un 1 binario

durante un perodo de muestreo de 5ms. La alarma desaparece cuando el

bit y se configura como un binario 0 durante un periodo de muestreo de 5

ms.

- Criterio para la deteccin de una alarma RDI en una interfaz de 2048 kbps:

La alarma se activa con un solo bit A se configura como un 1 binario

durante un periodo de muestreo de 5 ms. La alarma desaparece cuando el

bit A se configura como un binario 0 durante un periodo de muestreo de 5

ms.

LIMITACIONES DE LA PDH

El proceso de justificacin por una parte, y por otra el hecho de que la

temporizacin vaya ligada a cada nivel jerrquico, hace que en la

prctica sea imposible identificar una seal de orden inferior dentro de

un flujo de orden superior sin demultiplexar completamente la seal de

lnea.

Uno de los mayores inconvenientes de la demultiplexacin plesicrona

es que una vez formada la seal mltiplex, no es posible extraer un

tributario concreto sin demultiplexar completamente la seal.

Supongamos por ejemplo que tenemos un flujo de 140 Mbit/s, y que en

un punto intermedio deseamos extraer un canal a 2 Mbit/s; es necesario

para ello recurrir a las voluminosas y rgidas cadenas de multiplexacin,

que de forma esquemtica se representan en la siguiente figura:

Las diferentes jerarquas plesicronas existentes: Americana, europea y

japonesa, hacen muy difcil el interfuncionamiento. La escasa

normalizacin ha conducido a que los cdigos de lnea, la modulacin o

las funciones de supervisin, sean especficas de cada suministrador, de

forma que equipos de diferentes fabricantes son incompatibles entre s.

BIBLIOGRAFIA

http://www.spw.cl/05mar07_mobile/Transporte/Jerarquia_digital_plesiocr

ona_PDH.pdf

https://sites.google.com/site/3cuelectronica/home/pdh

http://es.wikipedia.org/wiki/Jerarqu%C3%ADa_Digital_Plesi%C3%B3cro

na

http://www.slideshare.net/fralbe007/pdh

Universidad Nacional Experimental de la fuerza armada nacional:

TRANSMISION TELEFONICA PDH-SDH Ingeniero Eduardo Gutirrez

Das könnte Ihnen auch gefallen

- Jerarquía Digital Plesiócrona - PDHDokument4 SeitenJerarquía Digital Plesiócrona - PDHChristian Silva Arrieta100% (1)

- PDH Jerarquía Digital PlesiócronaDokument5 SeitenPDH Jerarquía Digital PlesiócronaEugenio Puche SánchezNoch keine Bewertungen

- La Jerarquía Digital PlesiócronaDokument11 SeitenLa Jerarquía Digital PlesiócronaMarcos HerreraNoch keine Bewertungen

- Jerarquía Digital PlesiócronaDokument7 SeitenJerarquía Digital PlesiócronaedgarfransNoch keine Bewertungen

- PDH SDHDokument8 SeitenPDH SDHrodiaz65Noch keine Bewertungen

- Jerarquía Digital Plesiócrona: ÍndiceDokument9 SeitenJerarquía Digital Plesiócrona: ÍndiceNeycerAnchundiaNoch keine Bewertungen

- Tecnología de Transporte PDH, SDH, OTNDokument12 SeitenTecnología de Transporte PDH, SDH, OTNGrace Romualdo LazaroNoch keine Bewertungen

- Jerarquía Digital Plesiócrona - Wikipedia, La Enciclopedia LibreDokument10 SeitenJerarquía Digital Plesiócrona - Wikipedia, La Enciclopedia LibreJosHerreraNoch keine Bewertungen

- PDHDokument18 SeitenPDHkiyipi123100% (1)

- Jerarquía Digital PlesiócronaDokument11 SeitenJerarquía Digital PlesiócronaEberSantaCruzBerriosNoch keine Bewertungen

- Técnica de SupermercadoDokument7 SeitenTécnica de SupermercadoLuis LópezNoch keine Bewertungen

- Descripción Del Protocolo PDHDokument7 SeitenDescripción Del Protocolo PDHManuel Alberto Segobia MuñozNoch keine Bewertungen

- Jerarquía Digital PlesiócronaDokument40 SeitenJerarquía Digital PlesiócronaWilson RodriguezNoch keine Bewertungen

- Trabajo de Investigacion de AuxiliaturaDokument41 SeitenTrabajo de Investigacion de AuxiliaturaJimenez Meneces BrianNoch keine Bewertungen

- Jerarquias Digitales de TransmisiónDokument29 SeitenJerarquias Digitales de TransmisiónSagitta LyraeNoch keine Bewertungen

- Presentación PDHDokument9 SeitenPresentación PDHMargarita AndradeNoch keine Bewertungen

- PDH y SDHDokument4 SeitenPDH y SDHDavid AvilaNoch keine Bewertungen

- Universidad Estatal Peninsula de Santa Elena UPSE: Facultad de Sistemas y Telecomunicaciones WDM, SDH Y PDHDokument57 SeitenUniversidad Estatal Peninsula de Santa Elena UPSE: Facultad de Sistemas y Telecomunicaciones WDM, SDH Y PDHYimabel TumbacoNoch keine Bewertungen

- Jerarquia Digital PlesiocronaDokument4 SeitenJerarquia Digital PlesiocronaJaime Humberto Pech CarmonaNoch keine Bewertungen

- Jerarquía Digital PlesiócronaDokument4 SeitenJerarquía Digital PlesiócronaEddy AyalaNoch keine Bewertungen

- PDHDokument24 SeitenPDHDeiviNoch keine Bewertungen

- Monografía PDH y SDHDokument32 SeitenMonografía PDH y SDHwilliamolivares_Noch keine Bewertungen

- Jerarquía Digital SíncronaDokument11 SeitenJerarquía Digital SíncronaRoberto VásquezNoch keine Bewertungen

- SDH y PDHDokument44 SeitenSDH y PDHJuan Carlos G HNoch keine Bewertungen

- SDHDokument0 SeitenSDHJuanPabloAANoch keine Bewertungen

- Cambiosv 2 Av 3Dokument11 SeitenCambiosv 2 Av 3MarceloNoch keine Bewertungen

- PDH SDH PCM Ss7Dokument6 SeitenPDH SDH PCM Ss7Lenin Antonio Juela TorresNoch keine Bewertungen

- E1 Trama de TXDokument19 SeitenE1 Trama de TXHeidi SharpeNoch keine Bewertungen

- Trama E1Dokument19 SeitenTrama E1Jaime Garcia De Paredes100% (1)

- ELT3863 Tema7 Jerarquías Digitales2Dokument93 SeitenELT3863 Tema7 Jerarquías Digitales2Antonio MoyaNoch keine Bewertungen

- Marco Teórico PASANTIAS (En Ejecución)Dokument14 SeitenMarco Teórico PASANTIAS (En Ejecución)Alfredo Guánchez VillegasNoch keine Bewertungen

- SDH II 2010 Examen 2012Dokument178 SeitenSDH II 2010 Examen 2012Michael Punguil75% (4)

- Transmision PDH SDH-SONETDokument59 SeitenTransmision PDH SDH-SONETLuis Mario De La Paz VizqueiraNoch keine Bewertungen

- Consulta 1 PDHDokument21 SeitenConsulta 1 PDHMontes Silva EryNoch keine Bewertungen

- PORTADORASDokument5 SeitenPORTADORASEdwin TonatoNoch keine Bewertungen

- Jerarquia Digital Plesiócrona PresentacionDokument15 SeitenJerarquia Digital Plesiócrona PresentacionJefferson GonzálezNoch keine Bewertungen

- Clase 5 NDokument24 SeitenClase 5 Npablo.nano.arevaloNoch keine Bewertungen

- Telefonia SDHDokument16 SeitenTelefonia SDHAngel SczNoch keine Bewertungen

- Redes ConmutadasDokument17 SeitenRedes ConmutadasMairon SanchezNoch keine Bewertungen

- Exposicion PDH SDHDokument21 SeitenExposicion PDH SDHfimoxNoch keine Bewertungen

- PDH SDH TDMDokument6 SeitenPDH SDH TDMdarr3Noch keine Bewertungen

- Jerarquia Digital PlesiocronaDokument6 SeitenJerarquia Digital PlesiocronaKarlita M.Noch keine Bewertungen

- Jerarquía Digital Plesiócrona (PDH) : Web SiteDokument9 SeitenJerarquía Digital Plesiócrona (PDH) : Web Sitevvd1011Noch keine Bewertungen

- Ensayo 1Dokument6 SeitenEnsayo 1STEPHANYE JAZMIN ACUTA MORATAYANoch keine Bewertungen

- RedesDokument3 SeitenRedesJoe Chanco ONoch keine Bewertungen

- Capitulo IVDokument9 SeitenCapitulo IVGeovanny GabrielNoch keine Bewertungen

- SDHDokument15 SeitenSDHginethalexandraNoch keine Bewertungen

- Exposicion PDH SDHDokument30 SeitenExposicion PDH SDHJuan Soto Hernández100% (1)

- Jerarquia Digital Plesiocrona PDHDokument11 SeitenJerarquia Digital Plesiocrona PDHTacoMedinaOscarNoch keine Bewertungen

- Redes Conmutadas Por CircuitoDokument12 SeitenRedes Conmutadas Por Circuitofabiola97Noch keine Bewertungen

- Multiplexacion SDHDokument2 SeitenMultiplexacion SDHMarco Calizaya MartinezNoch keine Bewertungen

- Inf 3742 (Redes de Banda Ancha) : JDP O PDH (Jerarquía Digital Plesiocrona)Dokument17 SeitenInf 3742 (Redes de Banda Ancha) : JDP O PDH (Jerarquía Digital Plesiocrona)Jhamil VillegasNoch keine Bewertungen

- SONETDokument4 SeitenSONETJhonatan EspinozaNoch keine Bewertungen

- Multiplexación SDHDokument3 SeitenMultiplexación SDHandrea30mvNoch keine Bewertungen

- Jerarquias de ComunicacionDokument10 SeitenJerarquias de ComunicaciondennisNoch keine Bewertungen

- Banco de filtros: Información sobre las técnicas del banco de filtros de Computer VisionVon EverandBanco de filtros: Información sobre las técnicas del banco de filtros de Computer VisionNoch keine Bewertungen

- Prácticas de redes de datos e industrialesVon EverandPrácticas de redes de datos e industrialesBewertung: 4 von 5 Sternen4/5 (5)

- UF1874 - Mantenimiento de la infraestructura de la red de comunicacionesVon EverandUF1874 - Mantenimiento de la infraestructura de la red de comunicacionesNoch keine Bewertungen

- UF1869 - Análisis del mercado de productos de comunicacionesVon EverandUF1869 - Análisis del mercado de productos de comunicacionesNoch keine Bewertungen

- Equipos de interconexión y servicios de red. IFCT0410Von EverandEquipos de interconexión y servicios de red. IFCT0410Noch keine Bewertungen

- Gestion de Capital BinariasDokument4 SeitenGestion de Capital BinariasPatricio MillsNoch keine Bewertungen

- Spanish Manual Korg PadKONTROLDokument87 SeitenSpanish Manual Korg PadKONTROLJuan Manuel FerrariNoch keine Bewertungen

- 3-1-Distribucion BinomialDokument16 Seiten3-1-Distribucion BinomialCristian Humberto Badillo AgredoNoch keine Bewertungen

- Teoria Administrativa Cuadro ComparativoDokument14 SeitenTeoria Administrativa Cuadro ComparativoAlejandro Cadavid MárquezNoch keine Bewertungen

- Becas para Estudiar en SingapurDokument2 SeitenBecas para Estudiar en Singapurcarlos cardozoNoch keine Bewertungen

- Tercer Parcial RedaccionDokument6 SeitenTercer Parcial RedaccionmagdalenaNoch keine Bewertungen

- Simulación de MontecarloDokument9 SeitenSimulación de MontecarloMarimar Díaz RamírezNoch keine Bewertungen

- Trabajo Social 2Dokument1 SeiteTrabajo Social 2Tamy Zerpa HernándezNoch keine Bewertungen

- Primera Parte Del Proyecto OsirisDokument11 SeitenPrimera Parte Del Proyecto OsirisKat CastilloNoch keine Bewertungen

- Actividad Semana 1Dokument5 SeitenActividad Semana 1Catherin ZartoNoch keine Bewertungen

- Carta #03.22 Opinion Sobre Ampliacion de PlazoDokument2 SeitenCarta #03.22 Opinion Sobre Ampliacion de PlazoOmar Apaza QuispeNoch keine Bewertungen

- Certificado ServirDokument2 SeitenCertificado ServirPercyPajsiBautistaLoßoNoch keine Bewertungen

- Red HFCDokument7 SeitenRed HFCAndresNoch keine Bewertungen

- Cuaderno de Senderos Sierra de Aracena WebDokument60 SeitenCuaderno de Senderos Sierra de Aracena WebMaría López GonzálezNoch keine Bewertungen

- OSSENBACH-Estado y Educación en América Latina A Partir de Su IndependenciaDokument15 SeitenOSSENBACH-Estado y Educación en América Latina A Partir de Su IndependenciaJulian VivarNoch keine Bewertungen

- Procedimiento Aplicacion Fitosanitarios OkDokument7 SeitenProcedimiento Aplicacion Fitosanitarios OkMarines Piera Lobos PeñaNoch keine Bewertungen

- Analisis Eonomico Social y ... de La PobrezaDokument19 SeitenAnalisis Eonomico Social y ... de La PobrezaIvonv100% (9)

- Onapi, Trabajo FinalDokument15 SeitenOnapi, Trabajo FinalJudelka del carmen Garcia DiazNoch keine Bewertungen

- Informe de Topografia IDokument10 SeitenInforme de Topografia IDaniel ReyNoch keine Bewertungen

- Caso Practico 2Dokument2 SeitenCaso Practico 2Arturo Lobatón0% (1)

- Estudio de Caso: La Oportunidad de Formarme: Actividad 3.2Dokument5 SeitenEstudio de Caso: La Oportunidad de Formarme: Actividad 3.2Vanessa ObandoNoch keine Bewertungen

- Estándares de Calidad en El Ervicio de A&bDokument4 SeitenEstándares de Calidad en El Ervicio de A&bNadieska GutierrezNoch keine Bewertungen

- Sistemas de Archivos Variado (Mico)Dokument11 SeitenSistemas de Archivos Variado (Mico)Javier DelgadoNoch keine Bewertungen

- ChillersDokument107 SeitenChillersAnonymous e318j0SsANoch keine Bewertungen

- MIS01Dokument26 SeitenMIS01Garikoitz Mendióroz LizarragaNoch keine Bewertungen

- Curso LacteosDokument40 SeitenCurso LacteosEliojeanNoch keine Bewertungen

- Curriculum Profesor 07Dokument1 SeiteCurriculum Profesor 07mher001Noch keine Bewertungen

- Determinacion de FosfatosDokument7 SeitenDeterminacion de FosfatosJose Kalvin Rojas SosaNoch keine Bewertungen

- Ensayo Unidad 5 Tecnologias de La InforacionDokument6 SeitenEnsayo Unidad 5 Tecnologias de La InforacionCesar Daniel Campos Gonzalez100% (1)

- 20 PDFDokument12 Seiten20 PDFAna TeruelNoch keine Bewertungen