Beruflich Dokumente

Kultur Dokumente

Lecture25 fm5

Hochgeladen von

VLSI_IITROriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Lecture25 fm5

Hochgeladen von

VLSI_IITRCopyright:

Verfügbare Formate

EE 105 Spring 1997

Lecture 25

Common-Drain Amplifier

I

Similar conguration to common collector.

Analysis: much the same as for CC amplier -- if

V

SB

isnt zero, then the voltage

gain is degraded from about 1 to 0.8-0.9

V

BIAS

+

V

+

R

L

i

SUP

R

S

v

s

v

OUT

+

V

BIAS

V

+

I

SUP

+

V

OUT

EE 105 Spring 1997

Lecture 25

Common-Drain Two-Port Model

I

Two-Port model:

If

V

SB

= 0, then the input resistance is

A

v

= 1 and

R

out

= 1 /

g

m

(for hand analysis)

The CD amplier is a reasonable voltage buffer, especially for large (

W

/

L

) -->

large

g

m

.

v

in

+

v

in

+

v

out

+

(g

m

+ g

mb

)

1

(g

m

+ g

mb

)

g

m

EE 105 Spring 1997

Lecture 25

Single-Stage Amplier Congurations

I

Two complemetary versions exist for each amplier type.

I

CS/CE, CG/CB, and CD/CC have similar topologies (and properties)

Amplier

Type

Transistor Type

Common

Source/

Common

Emitter

(CS/CE)

Common

Gate/

Common

Base

(CG/CB)

Common

Drain/

Common

Collector

(CD/CC)

NMOS

npn pnp

i

SUP

V

+

V

OUT

IN

PMOS

i

SUP

V

+

V

+

V

OUT

OUT OUT

IN

IN

IN

V

i

SUP

i

SUP

V

V

+

IN

i

SUP

V

V

+

IN

i

SUP

V

V

+

V

+

OUT

OUT

IN

V

i

SUP

V

+

OUT

OUT

IN

V

i

SUP

i

SUP

V

+

V

OUT

IN

i

SUP

V

+

V

OUT

IN

i

SUP

V

+

V

OUT

IN

i

SUP

V

+

V

OUT

IN

EE 105 Spring 1997

Lecture 25

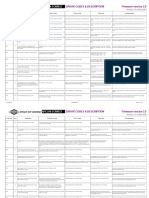

Two-Port Parameters for

Single-Stage Ampliers

Note: appropriate two-port model is used, depending on controlled source

Amplier Type Controlled Source

Input Resistance

R

in

Output Resistance

R

out

Common

Emitter

G

m

=

g

m

r

r

o

||

r

oc

Common

Emitter +

R

E

G

m

=

g

m

/ (1+

g

m

R

E

)

r

( 1 +

g

m

R

E

)

r

oc

||

[(1 +

g

m

R

E

)

r

o

]

for

r

>>

R

E

,

R

S

Common

Source

G

m

=

g

m

innity

r

o

||

r

oc

Common

Base

A

i

= -1 1 /

g

m

r

oc

|| [(1 +

g

m

(

r

||

R

S

))

r

o

],

for

g

m

R

S

>> 1

Common

Gate

A

i

= -1

1 /

g

m

, (

v

sb

= 0)

-otherwise-

1 / (

g

m

+

g

mb

)

r

oc

||[(1 +

g

m

R

S

)

r

o

], (

v

sb

=0)

-otherwise-

r

oc

|| [(1+

(g

m

+ g

mb

)

R

S

)

r

o

]

both for

g

m

R

S

>> 1

Common

Collector

A

v

= 1 r

(r

o

|| r

oc

|| R

L

) (1 / g

m

) + R

S

/

Common

Drain

A

v

= 1 if v

sb

= 0,

-otherwise-

g

m

/ (g

m

+ g

mb

)

innity 1 / g

m

if v

sb

= 0,

-otherwise-

1 / (g

m

+ g

mb

)

EE 105 Spring 1997

Lecture 25

Ultra-Simplied Two-Port Parameters

I g

mb

= 0, common base has reasonable source resistance --> R

S

>> r

I this table is adequate for rst-cut hand design

Amplier Type Controlled Source Input Resistance R

i

Output Resistance R

o

Common

Emitter

G

m

= g

m

r

r

o

|| r

oc

Common

Source

G

m

= g

m

innity r

o

|| r

oc

Common

Base

A

i

= -1 1 / g

m

r

oc

|| (

r

o

)

Common

Gate

A

i

= -1 1 / g

m

r

oc

||[(1+g

m

R

S

) r

o

]

Common

Collector

A

v

= 1 r

+ (r

o

|| r

oc

|| R

L

) (1 / g

m

) + R

S

/

Common

Drain

A

v

= 1 innity 1 / g

m

EE 105 Spring 1997

Lecture 25

Multistage Ampliers

I Single-stage transistor ampliers are inadequate for meeting most design

requirements for any of the four amplier types (voltage, current,

transconductance, and transresistance.)

I Therefore, we use more than one amplifying stage. The challenge is to gain

insight into when to use which of the 12 single stages that are available in a

modern BiCMOS process:

Bipolar Junction Transistor: CE, CB, CC -- in npn and pnp

*

versions

MOSFET: CS, CG, CD -- in n-channel and p-channel versions

*

in many BiCMOS technologies, only the npn BJT is available

I How to design multi-stage ampliers that satisfy the required performance

goals?

* Two fundamental requirements:

1. Impedance matching:

output resistance of stage n, R

out, n

and input resistance of stage n + 1, R

in, (n+1)

,

must be in the proper ratio

R

in, (n+1)

/ R

out, n

--> or

R

in, (n+1)

/ R

out, n

--> 0

to avoid degrading the overall gain parameter for the amplier

2. DC coupling:

direct connection between stages --> interaction between biasing sources must

be considered (later)

EE 105 Spring 1997

Lecture 25

Cascaded Voltage Amplier

I Want R

in

--> infinity, R

out

--> 0, with high voltage gain.

Try CS as rst stage, followed by CS to get more gain ... use 2-port models

I solve for overall voltage gain ... higher, but R

out

= R

out2

which is too large

r

o1

r

oc1

r

o2

r

oc2 v

in1

v

s

g

m1

v

in1

g

m2

v

in2

R

L

R

S

CS CS

+

+

v

in2

+

v

out

+

EE 105 Spring 1997

Lecture 25

Three-Stage Voltage Amplier

I Fix output resistance problem by adding a common drain stage (voltage buffer)

I Output resistance is not that low ... few k for a typical MOSFET and bias -->

could pay an area penalty by making (W/L) very large to fix.

(r

o2

r

oc2

)

v

in

v

s

A

v

v

in

(g

m3

+ g

mb3

)

R

L

R

S

CS CS CD

+

+

v

in3

v

in3

+

v

out

+

+

1

EE 105 Spring 1997

Lecture 25

Transconductance Amplier

I input resistance should be high; output resistance should also be high

I initial idea: use CS stages (they are natural transconductance amps)

I Overall G

m

= - g

m1

(r

o1

|| r

oc1

) g

m2

= A

v1

g

m2

... can be very large

I Output resistance is only moderately large

r

o2

r

oc2 v

in1

v

s

g

m1

(r

o1

r

oc1

)g

m2

v

in1

R

L

R

S

i

out

+

+

EE 105 Spring 1997

Lecture 25

Improved Transconductance Amplier

I Output resistance: boost using CB or CG stage

I high-resistance current sources are needed to avoid having r

oc3

limit the

resistance

(r

o2

r

oc2

)

v

in

v

s

A

v1

g

m2

v

in

R

L

R

S

i

out

+

+

i

in3

g

m3

1

i

in3

CS CS CG

g

m3

r

o3

(r

o2

r

oc2

)

r

oc3

EE 105 Spring 1997

Lecture 25

Two-Stage Current Buffers

I since one CB stage boosted the output resistance substantially, why not add

another one ...

I The base-emitter resistance of the 2

nd

stage BJT is r

2

which is much less than

the 2

nd

stage source resistance = 1

st

stage output resistance

I Therefore, the output resistance expression reduces to

... no improvement over a single CB stage

i

s

R

L

R

S

i

out

i

in1

i

in2

i

in2

i

in1

[ g

m2

r

o2

(r

2

o1

r

o1

r

oc1

)]

r

oc2

CB CB

o1

r

o1

r

oc1

g

m1

1

g

m2

1

R

S2

R

out1

o1

r

o1

r

oc1

= =

R

out

g

m2

r

o2

r

2

r

oc2

o2

r

o2

r

oc2

=

EE 105 Spring 1997

Lecture 25

Improved Current Buffer: CB/CG

I The addition of a common-gate stage results in further increases in the output

resistance, making the current buffer closer to an ideal current source at the

output port

I The product of transconductance and output resistance g

m2

r

o2

can be on the

order of 500 - 900 for a MOSFET --> R

out

is increased by over two orders of

magnitude

Of course, the current supply for the CG stage has to have at least the same order

of output resistance in order for it not to limit the overall R

out

.

Practical limit ... on the order of 100 M

i

s

R

L

R

S

i

out

i

in1

i

in2

i

in2

i

in1

[g

m2

r

o2

(

o1

r

o1

r

oc1

)]

r

oc2

CB CG

o1

r

o1

r

oc1

g

m1

1

g

m2

1

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Wharfedale EVP X15PDokument12 SeitenWharfedale EVP X15PttnaingNoch keine Bewertungen

- Pocketpico Manual PDFDokument17 SeitenPocketpico Manual PDFRichard BedellNoch keine Bewertungen

- CMS16P55 CmsemiconDokument32 SeitenCMS16P55 CmsemiconRicardo PiovanoNoch keine Bewertungen

- DS - 20201123 - MVS3150-LV Datasheet - V1.2.2 - ENDokument2 SeitenDS - 20201123 - MVS3150-LV Datasheet - V1.2.2 - ENGabooNoch keine Bewertungen

- B.E E&C Seventh Semester Syllabus Microwaves and AntennasDokument15 SeitenB.E E&C Seventh Semester Syllabus Microwaves and AntennasKausthubha BkNoch keine Bewertungen

- Ee6502 Microprocessors and MicrocontrollersDokument2 SeitenEe6502 Microprocessors and MicrocontrollersgokulchandruNoch keine Bewertungen

- Wa0017Dokument2 SeitenWa0017Rohit VetrivelNoch keine Bewertungen

- Ldoms Io Best Practices PDFDokument34 SeitenLdoms Io Best Practices PDFKuswahyudi UtomoNoch keine Bewertungen

- 0.3-3.0 GHZ High Dynamic Range Amplifier: Features Functional Block Diagram Cmm6004-ScDokument10 Seiten0.3-3.0 GHZ High Dynamic Range Amplifier: Features Functional Block Diagram Cmm6004-Scgonzalo2205Noch keine Bewertungen

- Carlo - Gavazzi G34405543230 Datasheet Transceiver For Digital SignalsDokument3 SeitenCarlo - Gavazzi G34405543230 Datasheet Transceiver For Digital SignalsGoran MladenovicNoch keine Bewertungen

- CT Sat Calculator (PSRC)Dokument274 SeitenCT Sat Calculator (PSRC)Eduardo777_777100% (1)

- Datasheet 0.3m & 0.6m Parabolic AntennaDokument3 SeitenDatasheet 0.3m & 0.6m Parabolic Antennazulkarnain lubisNoch keine Bewertungen

- CLAA201WA04Dokument31 SeitenCLAA201WA04Иван Алексиев100% (1)

- Synchronous vs. AsynchronousDokument2 SeitenSynchronous vs. AsynchronousDiptendu PramanikNoch keine Bewertungen

- Vlsi Lab Manual7Dokument8 SeitenVlsi Lab Manual7Atit PatelNoch keine Bewertungen

- Embedde, D SystemsDokument91 SeitenEmbedde, D SystemsVijay PreethamNoch keine Bewertungen

- APC200 ECM-ECI Error Codes Ver1.3Dokument10 SeitenAPC200 ECM-ECI Error Codes Ver1.3Amel Abbas Abbas AbbakerNoch keine Bewertungen

- Altivar 71: Modbus Plus Card User's ManualDokument25 SeitenAltivar 71: Modbus Plus Card User's ManualMohamed ElbanadiNoch keine Bewertungen

- Parameter Design For A 6.78-MHz Wireless Power Transfer SystemDokument12 SeitenParameter Design For A 6.78-MHz Wireless Power Transfer Systemagmnm1962Noch keine Bewertungen

- Manual de Uso de HC-06Dokument20 SeitenManual de Uso de HC-06Alejandro GonzálezNoch keine Bewertungen

- Pi SQF CCL Traf 435Dokument5 SeitenPi SQF CCL Traf 435maheshNoch keine Bewertungen

- APC MX5000 DatasheetDokument3 SeitenAPC MX5000 Datasheettruonghq45Noch keine Bewertungen

- Syllabus - Engineering ElectromagneticsDokument1 SeiteSyllabus - Engineering ElectromagneticssrihariNoch keine Bewertungen

- Lect # 06, Floyd, CH # 06 - Adder, Subtractor, Multiplier, Comparator PDFDokument35 SeitenLect # 06, Floyd, CH # 06 - Adder, Subtractor, Multiplier, Comparator PDFMuhammad Adnan KhalidNoch keine Bewertungen

- Features: Mechanical DataDokument2 SeitenFeatures: Mechanical DataFida HussainNoch keine Bewertungen

- Mitsubishi F700 VFD Instruction Manual-BasicDokument149 SeitenMitsubishi F700 VFD Instruction Manual-BasicMROstop.comNoch keine Bewertungen

- HZ Series: Silicon Epitaxial Planar Zener Diode For Stabilized Power SupplyDokument7 SeitenHZ Series: Silicon Epitaxial Planar Zener Diode For Stabilized Power SupplyCarlos BaezNoch keine Bewertungen

- Low Power CMOS VLSI Circuit Design (LPVD) : Dr. Veena S ChakravarthiDokument43 SeitenLow Power CMOS VLSI Circuit Design (LPVD) : Dr. Veena S ChakravarthiVeena SridharNoch keine Bewertungen

- Flying Capacitor Multilevel InvertersDokument4 SeitenFlying Capacitor Multilevel Invertersmd alikhanNoch keine Bewertungen

- Assignment 1Dokument3 SeitenAssignment 1Suhas MathapatiNoch keine Bewertungen