Beruflich Dokumente

Kultur Dokumente

Lecture10 fm5

Hochgeladen von

VLSI_IITROriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Lecture10 fm5

Hochgeladen von

VLSI_IITRCopyright:

Verfügbare Formate

The Inverted MOS Capacitor (VGB > VTn)

We consider the surface potential as xed (pinned) at s,max = - 2 p

Charge Storage in the MOS Structure

Three regions of operation:

Accumulation: qG = Cox (vGB - vFB) ... parallel plate capacitor

(x)

Depletion: qG = - qB(vGB), with the bulk (depletion) charge in the

silicon being a nonlinear function of vGB

1.5 V

Inversion: qG = - qN - qB,max , where qB,max = qB(vGB = VT) is the

depletion charge at the onset of inversion and

1.0 V

Vox

Sketch of the gate charge as a function of gate-bulk voltage:

500 mV

- tox

VGB - VFB

s,max = 420 mV

QG

Xd,max

2 p

ion

ers

inv

- 500 mV

letio

dep

What is the inversion charge QN?

consider: bulk charge is constant for VGB > VTn --> all of the additional charge in

the silicon is stored in the inversion layer, once inversion occurs. The inversion

layer is separated from the gate by the gate oxide; we can relate the inversion

charge (per cm2) to the applied voltage over VTn through Cox the capacitance

(per cm2) of the oxide

on

ati

ul

VFB = 0.97 V

QB,max

QB(VGB)

0

see Section 3.7 for the derivation

QN(VGB)

VGB (V)

VTn = 0.6 V

cu

ac

Q N = C ox ( V GB V Tn )

EE 105 Spring 1997

Lecture 10

EE 105 Spring 1997

Lecture 10

MOS Capacitance

Physical Interpretation of MOS Capacitance

The capacitance of the MOS structure is dened as

dq G

C = ------------dv GB

V GB

Accumulation: parallel plate capacitor --> C = Cox

Depletion: increment in gate charge is mirrored at bottom of depletion region, so

capacitance model is Cox in series with the depletion region capacitance Cb

From sketch, determine the slope and plot as the capacitance

gate

ion

qG

ers

inv

qN(vGB)

Si/SiO2 surface

on

pleti

de

QB,max

qB(vGB)

s

C b = -----Xd

Note that Xd is

a function of VGB

vGB (V)

C = C ox C b

VTn = 0.6 V

VFB = 0.97 V

cu

i

lat

on

bulk

ox

C ox = -------t ox

ac

(a)

C/Cox

accumulation

inversion

1.0

Inversion: bulk charge is no longer changing with VGB --> an increment in

gate charge is mirrored in the inversion layer under the gate.

The capacitance is therefore the same as in accumulation --> C = Cox

0.8

ion

t

ple

de

0.6

0.4

VFB = 0.97 V

2

0.2

VTn = 0.6 V

1

1

VGB (V)

(b)

EE 105 Spring 1997

Lecture 10

EE 105 Spring 1997

Lecture 10

Understanding MOS Capacitors

MOS Capacitance-Voltage Curve

Step 1: identify the atband voltage from the gate and bulk potentials in

equilibrium

Step 2: determine whether VGB > VFB leads to accumulation or to depletion

substrate is n-type --> accumulation

2q s N d ( 2 n )

V Tp = V FB 2 n ------------------------------------- = 1.03 2 ( 0.48 ) 3.28 = 3.21 V

C

ox

substrate is p-type --> depletion

Why? positive charge on gate ( since VGB - VFB > 0 V) must be mirrored by a

negative charge in the substrate.

n-type substrate: negatively charged electrons are accumulated under the gate

p-type substrate: negatively charged ionized acceptors are left, after holes are

repelled away from positive charge on gate

Step 3: construct C(VGB) plot, using the knowledge that the substrate is depleted

on the other side of VFB from accumulation in Step 2 and that inversion occurs

after depletion. Calculation of VT and Cmin is necessary to quantify the plot

Evaluate threshold voltage VTp

Minimum capacitance occurs just prior to inversion and is the series

combination of the oxide capacitance and the maximum depletion capacitance:

ox s

3.45 10 13 1.04 10 12

2

C min = -------- ------------------ = ---------------------------- ---------------------------- = 1.16 fF/cm

t ox X d, max

2 10 6 2.9 10 6

Maximum capacitance is Cox = 1.72 fF/cm2.

C/Cox

Additional data point: determine state of MOS structure in thermal equilibrium

(VGB = 0 V) ... accumulation or [depletion/inversion]

Example:

0.75

1.16/1.72 = 0.67

gate:

polysilicon (where p+ = - 550 mV); gate oxide thickness = 200 ,

substrate: n type silicon, n = 480 mV (Nd = 1018 cm-3)

p+

0.5

VFB = - (-550 mV - 480 mV) = + 1.03 V

0.25

VGB - VFB > 0 V --> accumulated; substrate is depleted for VGB < 1.03 V

Check: VGB = 0 --> negative charge on gate; positive in bulk (since gate is at

- 0.55 V and substrate is at + 0.48 V in thermal equilibrium) --> positive donors in

depletion region under gate ... and possibly holes due to inversion

EE 105 Spring 1997

Lecture 10

1.03 V

-3.21 V

0

-4

-3

-2

-1

VGB

EE 105 Spring 1997

Lecture 10

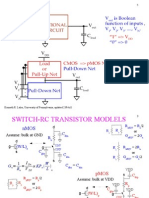

MOS Field Effect Transistors

Two complementary devices (each with two symbols): both are very useful

,,,

,,,,,,,,,

,,, , , , , , ,

, , ,,,,,,,,,,,,,,,,

,,,,,,, ,,,,,,,,,,,,,,

,,,,,,, ,,,,,,,,,,,,,,

,,,,,,,

,,,,,,,,,, ,,,,,,,,,,,,,,,,,,,,

,,,,,,,

,,,,,,,,,,,,,,,,,,,,

,,

,

,,

,,

,,

,,

MOSFET Circuit Symbols

gate

interconnect

gate contact

active area (thin

oxide area)

p-substrate (n-type channel under gate oxide)

polysilicon gate

n-substrate (p-type channel under gate oxide)

contact

n+ polysilicon gate

metal

interconnect

IDn

D

+

IDn

VDS > 0

G

+

VGS

B

+

VBS

_ _

S

+ S

+

_

(a) n-channel MOSFET

VSG

VSB

_

B

VSD > 0

IDp

IDp

(b) p-channel MOSFET

source contacts

Drain

Gate

drain

contacts

Source

n+

Source

Bulk or

Body

Gate

Drain

p+

Bulk or

Body

p+

edge of

active area

drain

interconnect

source

interconnect

n+

bulk

contact

(a)

gate oxide

source

interconnect

n+ polysilicon gate

bulk

drain

interconnect

interconnect

,

,,,,,,

,

,

,,,,

,,,,

,

,,

,,,

,,,,

,,,,,,

deposited

oxide

n+ drain diffusion

Ldiff

+

field n source diffusion

oxide

[ p-type ]

p+

Four electrical terminals: source (lowest potential for n-channel, highest for pchannel), drain, gate, and bulk.

Basic concept: inversion layer (called the channel) formed under gate between

source and drain enables drift current

(b)

EE 105 Spring 1997

Lecture 10

EE 105 Spring 1997

Lecture 10

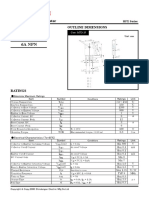

n-Channel MOSFET Drain Characteristics

Set-up: IG = 0, VDB = VDS > 0 to reverse-bias pn junctions to bulk.

p-Channel MOSFET Drain Characteristics

Set-up: IG = 0, VBD = VSD > 0 to reverse-bias pn junctions to bulk.

Measurement scheme: short bulk to source to make it a three terminal device,

vary gate voltage, drain voltage and see effect on drain current.

Measurement scheme: short bulk to source to make it a three terminal device,

vary gate voltage, drain voltage and see effect on drain current -ID

+ S+

IDn(VGS , VDS)

D

G

+

VSD

G

+ V

DS

B

VGS

VSG

_

VG

_

D

IDp

5V

+ V

D

ID(VSG ,VSD)

(a)

(a)

VGS = 3.5 V

VSG = 3.5 V

600

500

300

VDS = VGS VTn = VGS 1 V

(triode

region)

250

VGS = 3 V

400

IDn

(A)

constant current

(saturation) region

300

IDp

(A)

VGS = 2.5

100

150

100

VSG = 0, 0.5, 1 V

(cutoff region)

VSG = 2 V

50

VGS = 1.5 V

1

VSG = 3 V

(saturation region)

VSG = 25

VGS = 0, 0.5, 1 V

(cutoff region)

VGS = 2 V

200

VSD = VSG + VTp = VSG 1 V

(triode

region)

200

VDS (V)

VSG = 1.5 V

1

(b)

VSD (V)

(b)

EE 105 Spring 1997

Lecture 10

EE 105 Spring 1997

Lecture 10

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Zener DiodeDokument2 SeitenZener DiodeRamanaButterflyNoch keine Bewertungen

- Comb LogicDokument56 SeitenComb Logicpraritlamba25Noch keine Bewertungen

- Vlsi Question BankDokument14 SeitenVlsi Question BankGokila Vani50% (2)

- Chapter 00Dokument13 SeitenChapter 00Saeed YavariNoch keine Bewertungen

- Taiwan Semiconductor Manufacturing Company LTD.: TSMC 0.35um Mixed Signal Polycide 3.3V/5V Design RuleDokument72 SeitenTaiwan Semiconductor Manufacturing Company LTD.: TSMC 0.35um Mixed Signal Polycide 3.3V/5V Design RuleAlex WongNoch keine Bewertungen

- 1-VLCI ItrodutionDokument15 Seiten1-VLCI Itrodutionbhieestudents100% (1)

- DE QuestionsDokument42 SeitenDE QuestionsK P DHANALAKSHMI100% (1)

- 2SD1691 SavantICDokument3 Seiten2SD1691 SavantICNana Dwi WahanaNoch keine Bewertungen

- EE 4350 MOSFET Design Simulation IDokument4 SeitenEE 4350 MOSFET Design Simulation IalNoch keine Bewertungen

- Draw Input and Output Characteristics of A JFET (BFW10) PDFDokument7 SeitenDraw Input and Output Characteristics of A JFET (BFW10) PDFKirti ChandraNoch keine Bewertungen

- Using Leds - It'S Easy!: Jaycar Electronics Reference Data Sheet: Ledusej PDFDokument2 SeitenUsing Leds - It'S Easy!: Jaycar Electronics Reference Data Sheet: Ledusej PDFluis mendozaNoch keine Bewertungen

- P-N Junction Diode Characteristics: Edc Lab ManualDokument72 SeitenP-N Junction Diode Characteristics: Edc Lab ManualPraneeth KUMAR.PNoch keine Bewertungen

- Gate Turn-Off ThyristorsDokument14 SeitenGate Turn-Off ThyristorsSubhash Murkute0% (1)

- Catalog Diode Supresoare PDFDokument52 SeitenCatalog Diode Supresoare PDFvalidaeNoch keine Bewertungen

- Junction Field Effect Transistors Field Effect TransistorsDokument22 SeitenJunction Field Effect Transistors Field Effect TransistorsderejeNoch keine Bewertungen

- Static and Dynamic Performance of Complementary Inverters Based on Nanosheet α-MoTe2 p-Channel and MoS2 n-Channel TransistorsDokument8 SeitenStatic and Dynamic Performance of Complementary Inverters Based on Nanosheet α-MoTe2 p-Channel and MoS2 n-Channel TransistorsNaureena FirdousNoch keine Bewertungen

- Multiple Choice Questions and Answers On Semiconductor TheoryDokument36 SeitenMultiple Choice Questions and Answers On Semiconductor TheoryHENRY SINGCOL75% (4)

- IIT Delhi VLSI PlacementsDokument6 SeitenIIT Delhi VLSI PlacementsHimanshu ChauhanNoch keine Bewertungen

- 2SC4236 PDFDokument12 Seiten2SC4236 PDFsNoch keine Bewertungen

- The Gunn EffectDokument53 SeitenThe Gunn Effectdesta18Noch keine Bewertungen

- Global Semiconductor Value Chain - October 2020Dokument30 SeitenGlobal Semiconductor Value Chain - October 2020Sarut BeerNoch keine Bewertungen

- Cross Reference GudieDokument36 SeitenCross Reference Gudiegrace1881Noch keine Bewertungen

- Gifi - AbstractDokument16 SeitenGifi - AbstractAakiv Bhatia80% (5)

- E8 & E9Dokument4 SeitenE8 & E9hatemh82Noch keine Bewertungen

- 2 Sa 1141Dokument3 Seiten2 Sa 1141Jesus GCNoch keine Bewertungen

- Csa 1585 BCDokument3 SeitenCsa 1585 BCRodolfo CabreraNoch keine Bewertungen

- CMOS Fabrication Steps 3Dokument54 SeitenCMOS Fabrication Steps 3Yogesh MisraNoch keine Bewertungen

- Chenming Hu Ch3Dokument30 SeitenChenming Hu Ch3Green HeartNoch keine Bewertungen

- 05682957Dokument4 Seiten05682957Praveenkumar ViswanathanNoch keine Bewertungen

- Mid - I: Objective Type & Essay Questions With KeyDokument5 SeitenMid - I: Objective Type & Essay Questions With Keyduddala1srikanthNoch keine Bewertungen