Beruflich Dokumente

Kultur Dokumente

ALU

Hochgeladen von

ItoroItaCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

ALU

Hochgeladen von

ItoroItaCopyright:

Verfügbare Formate

Arithmetic-Logic Unit 101

The IEEE 754 standard offers four rounding modes, so that the programmer

can use the desired approximation. The rounding modes are the following:

Round toward plus infinity (always round up);

Round toward minus infinity (always round down);

Round toward zero (truncate);

Round to nearest even.

Two extra bits (guard and round) are always enough for the first three

rounding modes. The last rounding mode is provided for the situations when the ac-

tual number is exactly halfway between two floating-point representations. To always

obtain the correct rounding for the last case, the standard specifies a third bit in addi-

tion to guard and round. This is called sticky bit (s) and it is set whenever there are

non-zero bits to the right of the round bit. Once set, the sticky bit remains set. This

bit might be set, for example, during addition, when the smaller number is shifted to

the right.

Rounding to nearest minimizes the mean error introduced by rounding. If

uniform distribution of digits are assumed, rounding to nearest has a mean error of 0.

3.5. Problems

3.5.1. Design combinational circuits for a half subtracter and a full subtracter. For

each circuit: (a) Derive the truth table; (b) Write the Boolean expression;

(c) Draw the logic diagram.

3.5.2. Design an n-bit subtracter whose operation is analogous to that of a ripple

carry adder.

3.5.3. Illustrate how to connect n half adders to form an n-bit combinational incre-

menter whose function is to add 1 (modulo 2

n

) to an n-bit number X.

3.5.4. Design a 2s complement adder-subtracter that computes the values X + Y,

X Y, and Y X. The circuit has an overflow flag and a zero flag. First design

a 4-bit adder module using ripple-carry propagation, and then use this module

to construct an 8-bit adder-subtracter.

3.5.5. Table 3.13 describes a procedure for the addition of n-bit sign-magnitude

numbers. Addition and subtraction of sign-magnitude numbers is compli-

cated by the fact that to compute X + Y, the magnitudes | X| and | Y| must

be compared to determine the operation to perform and the order of oper-

ands. Design a circuit to compute the functions X + Y, X Y, and Y X for

sign-magnitude numbers. Assume that the word size is 16 bits and that the

standard design components are available, including a 16-bit unsigned adder,

a 16-bit unsigned subtracter, and a 16-bit magnitude comparator.

Structure of Computer Systems 102

Table 3.13. Algorithm for the addition of sign-magnitude numbers.

Condition Operations

X >0, Y >0 Add X =xn-1xn-2x0 and Y =yn-1yn-2y0 (modulo 2

n

) to form the result

Z =zn-1zn-2z0 (n-bit unsigned addition).

X >0, Y <0 Let |X| =xn-2xn-3x0 and |Y| =yn-2yn-3y0. If |X| <|Y|, subtract X from Y

(modulo 2

n

). If |X| |Y|, set yn-1 to 0 and subtract Y from X (modulo 2

n

).

X <0, Y >0 If |Y| <|X|, subtract Y from X (modulo 2

n

). If |Y| |X|, set xn-1 to 0 and

subtract X from Y (modulo 2

n

).

X <0, Y <0 Add X and Y (modulo 2

n

) and set zn-1 to 1.

3.5.6. Suppose that the adder-subtracter circuit of Figure 3.32 has been designed for

2s complement numbers. The circuit computes the sum Z = X + Y when the

control line SUB = 0 and the difference Z = X Y when SUB = 1. An over-

flow flag OF is to be added to the circuit, but it is not possible to access in-

ternal lines. That is, only those data and control lines appearing in the figure

can be used to set the overflow flag. Construct a logic circuit for OF.

Figure 3.32. An n-bit adder-subtracter circuit.

3.5.7. Consider the adder-subtracter circuit of Figure 3.32, assuming now that it has

been designed for sign-magnitude numbers. The circuit computes Z = X + Y

when SUB = 0 and Z = X Y when SUB = 1. Assume that the circuit con-

tains an n-bit ripple carry adder and a similar n-bit ripple borrow subtracter,

and that it is possible to access all the internal lines. Derive a logic equation

that defines an overflow flag OF for this circuit.

3.5.8. Derive a general expression for the carry signal C

k

in a carry lookahead adder.

3.5.9. Derive the Boolean expressions for the carry signals C

12

and C

16

in a carry

lookahead adder that adds two 16-bit numbers. Assume that fan-in is limited

to 4.

3.5.10. Write the equations for the carry logic of a 64-bit carry lookahead adder using

16-bit adders as building blocks.

3.5.11. Design a 4-bit carry select adder using full adders and multiplexers.

Arithmetic-Logic Unit 103

3.5.12. Design a carry save adder for adding four 4-bit numbers. Draw the logic dia-

gram of the adder using full adders. Note that the sum of four n-bit numbers

can take n+2 bits.

3.5.13. Assume that the delay introduced by each full adder is 2T. Calculate the time

of adding four 4-bit numbers using three ripple-carry adders versus the time

using the carry save adder from Problem 3.5.12.

3.5.14. Design a serial adder that adds four unsigned binary numbers instead of two

handled by a conventional serial adder. The adder has four input lines x, y, z,

u and a single output line S. The numbers are presented at the inputs with the

least significant bits first.

3.5.15. Design a serial subtracter analogous to the serial adder. The inputs of the

subtracter are two unsigned binary numbers x and y; the output is the differ-

ence x y.

3.5.16. Design a sequential circuit that multiplies an unsigned binary number N of

arbitrary length by 3. N is entered serially via the input line x with its least sig-

nificant bit first. The result appears serially on the output line z.

3.5.17. Design a BCD adder by using five full adders, two half adders, three two-

input NAND gates, and one three-input NAND gate.

3.5.18. A faster version of Booths multiplication algorithm for 2s complement

numbers, known as the modifiedBooth algorithm, examines three adjacent bits

y

i+1

y

i

y

i-1

of the multiplier Y at a time, instead of two bits. Besides the three

basic actions performed by the original Booth algorithm, which can be ex-

pressed as add 0, X, or X to the accumulated partial product (A), the modi-

fied algorithm performs two more actions: add +2X or 2X to register A.

These operations have the effect of increasing the radix from 2 to 4 and allow

an n-bit multiplication to be performed in n/ 2 clock cycles instead of n.

(a) Construct a table that defines the basic actions of the modified Booth al-

gorithm as a function of y

i+1

y

i

y

i-1

. (b) Show the steps of the algorithm for two

8-bit 2s complement numbers (including the sign bit). (c) Describe the modi-

fied Booth algorithm in VHDL.

3.5.19. Draw the detailed logic diagram of a 4-bit multiplier using a Wallace tree

(Figure 3.15). Use full adders as basic components.

3.5.20. Draw the block diagram of a multiple-operand adder with multiple levels of

carry save adders and one carry lookahead adder, arranged in a Wallace tree.

The adder can receive 10 input numbers, where each number has 4 bits. As-

suming that each carry save adder has a delay of T, and the carry lookahead

adder has a delay of 2T, estimate the total time required to add 100 4-bit

numbers.

Structure of Computer Systems 104

3.5.21. Suppose the combinational array multiplier of Figure 3.18 is given the un-

signed integer operands X = 1010 and Y = 1001. Determine the output sig-

nals generated by every adder cell when the array computes X Y.

3.5.22. Use the multiplier cell of Figure 3.19 to construct a combinational array mul-

tiplier for 5-bit unsigned numbers. Draw the logic diagram of the multiplier

and show all the signals applied to every cell.

3.5.23. Design a basic cell for implementing Booths algorithm by a combinational

array. Such a cell must be capable of addition, subtraction, and no operation.

Draw the structure of the array multiplier for 44-bit numbers. Suppose the

array multiplier is given the signed integer operands X = 1010 and Y = 1001.

Determine the output signals generated by every cell when the array com-

putes X Y.

3.5.24. Divider circuits usually include logic to detect a dividend-divisor combination

that will cause the quotient to overflow. Suppose that a divider circuit for n-

bit unsigned integers has a double-word (2n-bit) dividend and a single-word

divisor. (a) What condition must be satisfied for quotient overflow to occur?

(b) How can be modified the divider circuit of Figure 3.23 to introduce an

overflow detector using as little extra logic as possible?

3.5.25. Write a nonrestoring division algorithm using the notation of Figure 3.22.

Show by an example how the algorithm works.

3.5.26. Write the logic equations for the outputs z and u of cell D in Figure 3.25.

3.5.27. Consider the array divider of Figure 3.26 that is designed for a word size of

n = 3, with a double-length (6 bit) dividend. (a) Why there are four rows of D

cells instead of three? (b) Supposing that dividends are restricted to 3 bits in-

stead of 6, which cells can be deleted from the array?

3.5.28. Consider the following 9-bit floating-point format, where the 4-bit exponent

is biased by 8.

8 7 4 3 0

S Exponent Mantissa

(a) Assume that the exponent base is 2, and consider only normalized repre-

sentations. What are the largest positive value and the smallest negative value

representable in this format? (b) Repeat part (a) when the exponent base is 4.

3.5.29. Add the numbers 6.42 10

1

to 9.51 10

2

, assuming that there are only three

significant decimal digits, first with guard and round digits, and then without

them.

3.5.30. Derive the floating-point division algorithm using a format similar to the

multiplication algorithm in Figure 3.31. Then perform the division of num-

bers 1.11010 10

10

and 1.10010 10

5

, showing the steps of the operation.

Das könnte Ihnen auch gefallen

- Matrices with MATLAB (Taken from "MATLAB for Beginners: A Gentle Approach")Von EverandMatrices with MATLAB (Taken from "MATLAB for Beginners: A Gentle Approach")Bewertung: 3 von 5 Sternen3/5 (4)

- Two's Complement Adder/Subtractor: Lab L03Dokument7 SeitenTwo's Complement Adder/Subtractor: Lab L03Darrel VeluzNoch keine Bewertungen

- VHDL Ass1 Binary Multiplier 2005Dokument2 SeitenVHDL Ass1 Binary Multiplier 2005rahulm135Noch keine Bewertungen

- Lab 1Dokument10 SeitenLab 1sibarama20k100% (1)

- For More PracticeDokument5 SeitenFor More PracticeMarwan SamiNoch keine Bewertungen

- Unit 4 Combinational CircuitDokument22 SeitenUnit 4 Combinational CircuitAnurag GoelNoch keine Bewertungen

- 3 Adder SubtractorDokument10 Seiten3 Adder SubtractorHadeer GamalNoch keine Bewertungen

- Implementation of A High Speed Single Precision Floating Point Unit Using VerilogDokument5 SeitenImplementation of A High Speed Single Precision Floating Point Unit Using VerilogVikas PakhretiaNoch keine Bewertungen

- B1 Group3Dokument13 SeitenB1 Group3Kausar ParvejNoch keine Bewertungen

- Computer Organization and Architecture: UNIT-2Dokument29 SeitenComputer Organization and Architecture: UNIT-2CloudNoch keine Bewertungen

- Lab6 VerilogDokument6 SeitenLab6 VerilogVận MặcNoch keine Bewertungen

- 32 Bit Floating Point ALUDokument7 Seiten32 Bit Floating Point ALUBalachandarVetrivelan80% (5)

- CaccDokument106 SeitenCaccArvind VishnubhatlaNoch keine Bewertungen

- Chapter 3 - ExerciesDokument5 SeitenChapter 3 - ExerciesJorge Franco IbañezNoch keine Bewertungen

- Lab Report #5 by MungunsukhDokument7 SeitenLab Report #5 by MungunsukhoyunpurevoyunaaNoch keine Bewertungen

- Chapter 6 LogicDokument49 SeitenChapter 6 LogicProspect Teaches MathematicsNoch keine Bewertungen

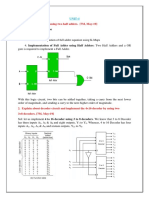

- Design A Full Adder by Using Two Half Adders. (7M, May-19)Dokument10 SeitenDesign A Full Adder by Using Two Half Adders. (7M, May-19)Sri Silpa Padmanabhuni100% (1)

- EE1110, Assignment No. 1. 16 August. Due Date: 26 August.: TH THDokument1 SeiteEE1110, Assignment No. 1. 16 August. Due Date: 26 August.: TH THjetrokimutNoch keine Bewertungen

- UntitledDokument63 SeitenUntitled魏延任Noch keine Bewertungen

- DK CsaDokument12 SeitenDK Csadeepakkr22781Noch keine Bewertungen

- Final Apr 03 SolnsDokument16 SeitenFinal Apr 03 Solnsapi-3755462Noch keine Bewertungen

- DIGITAL CIRCUIT AND SYSTEM End TermDokument2 SeitenDIGITAL CIRCUIT AND SYSTEM End TermRavindra KumarNoch keine Bewertungen

- EE200 Experiment 07Dokument5 SeitenEE200 Experiment 07xanxus2012Noch keine Bewertungen

- Mod 1 2Dokument20 SeitenMod 1 2Naseef RahmanNoch keine Bewertungen

- Final Note Arithmetic VtuDokument30 SeitenFinal Note Arithmetic VtuadddataNoch keine Bewertungen

- Assignment#1 SolutionDokument4 SeitenAssignment#1 SolutioneidmohdNoch keine Bewertungen

- Final Homework 2023 (To Be Graded)Dokument3 SeitenFinal Homework 2023 (To Be Graded)Nishad MandlikNoch keine Bewertungen

- Design and Simulation of A Modified Architecture of Carry Save AdderDokument12 SeitenDesign and Simulation of A Modified Architecture of Carry Save AdderromanazNoch keine Bewertungen

- This Chapter Introduces Various Algorithms and Techniques To Perform Some Basic Arithmetic Operations Related To A ComputerDokument5 SeitenThis Chapter Introduces Various Algorithms and Techniques To Perform Some Basic Arithmetic Operations Related To A ComputerarjuNoch keine Bewertungen

- Chapter 4 Combinational LogicDokument54 SeitenChapter 4 Combinational LogicKaran RegmiNoch keine Bewertungen

- Module 2 DSDV (Nep)Dokument17 SeitenModule 2 DSDV (Nep)ramkumar.sNoch keine Bewertungen

- International Journal of Engineering Research and Development (IJERD)Dokument6 SeitenInternational Journal of Engineering Research and Development (IJERD)IJERDNoch keine Bewertungen

- Module 2 DSDVDokument16 SeitenModule 2 DSDVAnanya A MNoch keine Bewertungen

- DSD Assignment-IDokument2 SeitenDSD Assignment-IGuranshpartap SinghNoch keine Bewertungen

- 4bit Array MultiplierDokument4 Seiten4bit Array MultiplierRahul TiwariNoch keine Bewertungen

- CA Assignment IIDokument9 SeitenCA Assignment IISomesh ThakurNoch keine Bewertungen

- Chapter 4 Combinational LogicDokument54 SeitenChapter 4 Combinational LogicAkrur NeupaneNoch keine Bewertungen

- A Vlsi: DSP Chip For Real Time Iterative DeconvolutionDokument4 SeitenA Vlsi: DSP Chip For Real Time Iterative DeconvolutionAjinkya DeshmukhNoch keine Bewertungen

- Mentor Graphics Tutorial: Schematic Capture, Simulation, & Placement/RoutingDokument22 SeitenMentor Graphics Tutorial: Schematic Capture, Simulation, & Placement/RoutingHairil HanifNoch keine Bewertungen

- 03 Numeric BasicsDokument68 Seiten03 Numeric BasicsGîrju AndradaNoch keine Bewertungen

- Implement A Verilog Model and Display The Output For A Set of Sample Data Together With The Wave Form Obtained For The Problems Given BelowDokument6 SeitenImplement A Verilog Model and Display The Output For A Set of Sample Data Together With The Wave Form Obtained For The Problems Given Belowlilly pushparaniNoch keine Bewertungen

- Explain FLYNN Classification With Suitable ExamplesDokument7 SeitenExplain FLYNN Classification With Suitable Examplesjishupanja33Noch keine Bewertungen

- DesignofCombinationalCircuits NotesDokument12 SeitenDesignofCombinationalCircuits NotesRohitNoch keine Bewertungen

- EN TP1 DocDokument3 SeitenEN TP1 DocSmail SmartNoch keine Bewertungen

- Digital Arithmatic Operations L 37 - 39Dokument30 SeitenDigital Arithmatic Operations L 37 - 39Nethmi LokusuriyaNoch keine Bewertungen

- Carry Save AdderDokument19 SeitenCarry Save Adderarshadshareefmd100% (2)

- Tutorial Sheet - 5Dokument4 SeitenTutorial Sheet - 5Vidit MathurNoch keine Bewertungen

- Matlab TutorialDokument34 SeitenMatlab TutorialrtloquiasNoch keine Bewertungen

- Chapter 3 Arithmetic For Computers-NewDokument32 SeitenChapter 3 Arithmetic For Computers-NewStephanieNoch keine Bewertungen

- 4-Input Decimal Adder Using 90 NM CMOS Technology: Meena Aggarwal, Aastha Agarwal, MR - Rajesh MehraDokument4 Seiten4-Input Decimal Adder Using 90 NM CMOS Technology: Meena Aggarwal, Aastha Agarwal, MR - Rajesh MehraIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalNoch keine Bewertungen

- Problem Set 1Dokument4 SeitenProblem Set 1Pradyumn PaliwalNoch keine Bewertungen

- Simulation and Implementation of Vedic Multiplier Using VHDL CodeDokument5 SeitenSimulation and Implementation of Vedic Multiplier Using VHDL CodeSagar S PoojaryNoch keine Bewertungen

- PorjDokument4 SeitenPorjTaimenTaiNoch keine Bewertungen

- Parallel Implementation of A 4 X 4-Bit MultiplierDokument4 SeitenParallel Implementation of A 4 X 4-Bit MultiplierMathew GeorgeNoch keine Bewertungen

- DSP Assingmnet 1Dokument27 SeitenDSP Assingmnet 1Info StudioNoch keine Bewertungen

- Practice Problems 1Dokument34 SeitenPractice Problems 1akbisoi1Noch keine Bewertungen

- Test Bench For Exponential FunctionDokument4 SeitenTest Bench For Exponential Functionfarzian1Noch keine Bewertungen

- A Brief Introduction to MATLAB: Taken From the Book "MATLAB for Beginners: A Gentle Approach"Von EverandA Brief Introduction to MATLAB: Taken From the Book "MATLAB for Beginners: A Gentle Approach"Bewertung: 2.5 von 5 Sternen2.5/5 (2)

- Kepware Modbus AsciiDokument30 SeitenKepware Modbus Asciizvonkomihajlovic4891Noch keine Bewertungen

- MSP430 Micro Controller Assember DirectivesDokument68 SeitenMSP430 Micro Controller Assember Directivesbkvuvce8170Noch keine Bewertungen

- Introduction To JavaDokument142 SeitenIntroduction To JavaAAbid ALi KhAnNoch keine Bewertungen

- C NotesDokument114 SeitenC NotesSri PramodhNoch keine Bewertungen

- Giao Trinh Pythong EngDokument436 SeitenGiao Trinh Pythong EngdungNoch keine Bewertungen

- SCJPBy NagarajuDokument250 SeitenSCJPBy NagarajulaxmankurnoolNoch keine Bewertungen

- DSG Data LoadingDokument23 SeitenDSG Data LoadingAaheli BhattacharjeeNoch keine Bewertungen

- COBOLDokument272 SeitenCOBOLbadsoft100% (6)

- Master ONE: Modbus TCP/IP Option Instruction ManualDokument25 SeitenMaster ONE: Modbus TCP/IP Option Instruction ManualCarlos Enrique Godoy SifontesNoch keine Bewertungen

- Dubs Maxscript TutorialsDokument42 SeitenDubs Maxscript TutorialsAdam AmbrusNoch keine Bewertungen

- Floating Point ArithmeticDokument15 SeitenFloating Point Arithmeticprabhabathi deviNoch keine Bewertungen

- SXIPM IEC870 5 101 104 - V200 - User - ManualDokument97 SeitenSXIPM IEC870 5 101 104 - V200 - User - ManualCorl1971Noch keine Bewertungen

- Binary To Decimal Number ConversionDokument6 SeitenBinary To Decimal Number Conversionhifzan786100% (1)

- Unit 1Dokument61 SeitenUnit 1Anil PenumachaNoch keine Bewertungen

- GII-07 Training MaterialDokument191 SeitenGII-07 Training MaterialIris Amati MartinsNoch keine Bewertungen

- 09 Java HandoutDokument238 Seiten09 Java HandoutAbhishek AmbekarNoch keine Bewertungen

- Hardware Manual 26-737 EDokument285 SeitenHardware Manual 26-737 EfjbragaNoch keine Bewertungen

- 02 SlideDokument62 Seiten02 SlideAnonymous ThBYSWNoch keine Bewertungen

- The Joy of ProgrammingDokument97 SeitenThe Joy of ProgrammingDhivya GaneshNoch keine Bewertungen

- Vtu 1st Sem Programming in C and Data Structures Notes 14pcd13Dokument126 SeitenVtu 1st Sem Programming in C and Data Structures Notes 14pcd13Ullas M100% (1)

- Data Types - SAP HANA SQL and System Views Reference - SAP LibraryDokument15 SeitenData Types - SAP HANA SQL and System Views Reference - SAP Libraryaadesh.snNoch keine Bewertungen

- Open Shading LanguageDokument93 SeitenOpen Shading LanguageRafael CamposNoch keine Bewertungen

- Chapter 02Dokument44 SeitenChapter 02sellaryNoch keine Bewertungen

- Ansa v12.0.3 Release Notes PDFDokument73 SeitenAnsa v12.0.3 Release Notes PDFsuhas110Noch keine Bewertungen

- Lec9 Fixed Point RepresentationDokument19 SeitenLec9 Fixed Point RepresentationRaman KalraNoch keine Bewertungen

- Boulanger Lazzarini AudioProgrammingBook PDFDokument916 SeitenBoulanger Lazzarini AudioProgrammingBook PDFghostarbeiter67% (3)

- SCILAB EditedDokument55 SeitenSCILAB EditedRama Sugavanam100% (1)

- Methode Des Elements Finis Cours Annexe 04 Element Quadrilatere Q4Dokument45 SeitenMethode Des Elements Finis Cours Annexe 04 Element Quadrilatere Q4kamlNoch keine Bewertungen

- C++ Programming: From Problem Analysis To Program Design: Chapter 2: Basic Elements of C++Dokument81 SeitenC++ Programming: From Problem Analysis To Program Design: Chapter 2: Basic Elements of C++kyle_tosh3484Noch keine Bewertungen