Beruflich Dokumente

Kultur Dokumente

Ch6 I MOS Inverters Switching Characteristics I 2 13

Hochgeladen von

asad_raza4uCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Ch6 I MOS Inverters Switching Characteristics I 2 13

Hochgeladen von

asad_raza4uCopyright:

Verfügbare Formate

1

CMOS Digital Integrated Circuits

Ch6 CMOS Inverters:

Switching Characteristics

and Interconnect Effects I

2

CMOS Inverters Dynamic Analysis and Design

Goals

Understand the detail dynamic analysis of the

CMOS inverter.

Understand one set of design from CMOS

equations.

Understand the basic CMOS design process

using the CMOS static and CMOS design form

dynamic equations.

6.1 Introduction

3

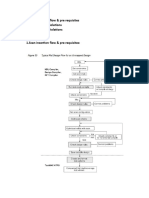

CMOS Dynamic Analysis: Capacitance Model for CMOS

V

out

V

DD

V

in

Cgs,p

Cint

Csb,p

Cgs,n

Cgd,n

Cgd,p

Csb,n

Cdb,p

Cdb,n

Cg

FO

Fig. 6.1 Cascoded CMOS Inverter stages

4

CMOS Dynamic Analysis: Capacitance Model for CMOS

The aggregate capacitance driven by the output

node of a CMOS inverter is in detail working from

left to right,

C

load

= C

input

+ C

int

+ C

g

in which

C

input

= C

gd,n

+ C

gd,p

+ C

db,n

+ C

db,p

(intrinsic

component)

C

int

= interconnect capacitance

C

g

= thin-oxide capacitance over the gate area

(extrinsic component)

6

CMOS Dynamic Analysis: Delay-Time Definitions

PHL

VOH

V50%

VOL

Vin

t

idealized

step input

VOH

V50%

VOL

Vout

t

Vout

PLH

t0 t1 t2 t3

fall

V90%

V10%

t

rise

tA tB tC tD

V

50

%

= V

OL

+(V

OH

-V

OL

)/2

. = (V

OH

+V

OL

)/2

PHL

= t

1

-t

0

PLH

= t

3

-t

2

P

= (

PHL

+

PLH

)/2

V

10%

= V

OL

+0.1(V

OH

-V

OL

)

V

90%

= V

OL

+0.9(V

OH

-V

OL

)

fall = t

B

-t

A

rise = t

C

-t

D

Fig. 6.3

Fig. 6.4

7

CMOS Dynamic Analysis

Delay-Time Calculation (First Order Estimates)

The simplest approach of calculating the propagation

delay is based on estimating the average capacitance

current during charge down/up.

where

I

V V C

I

V V C

LH avg

OL load

PLH

HL avg

OH load

PHL

,

% 50

,

% 50

) (

) (

[ ]

[ ] ) , ( ) , (

2

1

) , ( ) , (

2

1

% 50 ,

% 50 ,

V V V V i V V V V i I

V V V V i V V V V i I

OL out OL in C out OL in C LH avg

out OH in C OH out OH in C HL avg

= = + = = =

= = + = = =

6.3 Calculation of Delay Times

8

CMOS Dynamic Analysis

Delay-Time Calculation (More Accurate)(1/4)

The propagation delay can be found more accurately by

solving the state equation of the output node. The current

flowing through C

load

is a function V

out

as

PHL

: PMOS is off. The equivalent circuit during high-to-

low output transition is

i i i

dt

dV

C n D p D C

out

out , ,

= =

V

in

nMOS

i

D,n

C

load

V

out

i i

dt

dV

C n D C

out

out ,

= =

V

in

V

out

i

C

i

D,p

i

D,n

Fig. 6.5

9

CMOS Dynamic Analysis: Delay-Time Calculation (2/4)

The nMOS operates in two regions, saturation and linear,

during the interval of

PHL

.

Saturation Region

i

D,n

=(k

n

/2)(V

in

-V

T,n

)

2

=(k

n

/2)(V

OH

-V

T,n

)

2

Plug i

D,n

into C

load

dV

out

/dt=-i

D,n

, and integrate both sides,

we get

t

1

-t

0

= 2C

load

V

T,n

/[k

n

(V

OH

-V

T,n

)

2

]

PHL

V

OH

=V

DD

V

50%

V

OH

-V

T,n

V

out

t

t

0

t

1

nMOS in saturation

nMOS in linear region

t

1

Fig. 6.6

10

CMOS Dynamic Analysis: Delay-Time Calculation (3/4)

Linear Region

i

D,n

= (k

n

/2)[2(V

in

- V

T,n

)V

out

- V

out

2

]

= (k

n

/2)[2(V

OH

- V

T,n

)V

out

- V

out

2

]

Plug i

D,n

into C

load

dV

out

/dt=-i

D,n

, and integrate both

sides, we have

Finally, since V

OH

=V

DD

and V

OL

=0, we have

, ,

, ,

4( )

2

ln 1

( )

T n DD T n load

n DD T n DD T n D

HL

D

P

V V V C

V V V V V

= +

PHL

VOH

V50%

VOH -VT,n

Vout

t

t

0

t

1

nMOS in saturation

nMOS in linear region

t

1

,

, 50%

4( )

ln

( )

DD T n load

n DD T n

V V C

V V V

'

1 1

t t

Fig. 6.6

11

CMOS Dynamic Analysis: Delay-Time Calculation (4/4)

PLH

: NMOS is off. The equivalent circuit during low-to-

high output transition is

With the similar way (t

0

t

1

t

1

0|V

T,p

|V

50%

saturation linear ), we can have

V

in

pMOS

i

D,p

C

load

V

out

V

DD

, ,

, ,

2 4( )

ln 1

( )

T p DD T p

load

p DD T p D D

L

D T p

P H

D

V V V

C

V V V V V

= +

12

CMOS Inverter Design

Design for Performance

Keep capacitance small

Increase transistor size

Watch out for self-loading!

Increase V

DD

6.4 Inverter Design with Delay Constraints

14

CMOS Inverter Design: Delay as a Function of V

DD

V

DD

increases

PHL

/

PLH

decreases. However,

the power consumption also increases.

0.8 1 1.2 1.4 1.6 1.8 2 2.2 2.4

1

1.5

2

2.5

3

3.5

4

4.5

5

5.5

V

DD

(V)

p

H

L

(

n

o

r

m

a

l

i

z

e

d

)

15

CMOS Inverter Design: Device Sizing (1/5)

2 4 6 8 10 12 14

2.

0

2.2

2.4

2.6

2.8

3.2

3.4

3.6

3.8

x 10

-11

S

p

(

s

e

c

)

3.0

Self-loading effect:

Intrinsic capacitances

dominate

(for fixed load)

16

CMOS Inverter Design: Device Sizing (2/5)

NMOS/PMOS Ratio

R = W

p

/ W

n

1 1.5 2 2.5 3 3.5 4 4.5 5

3

3.5

4

4.5

5

x 10

-11

R

p

(

s

e

c

)

PLH

PHL

P

17

CMOS Inverter Design: Device Sizing (3/5)

Self-Loading Effect

C

load

= C

gd,n

(W

n

) + C

gd,p

(W

p

) + C

db,n

(W

n

) + C

db,p

(W

p

) + C

int

+C

g

= f(W

n

,W

p

)

Using the junction capacitance expressions in Chapter 3, we have

C

db,n

= (W

n

D

drain

+x

j

D

drain

)C

j0,n

K

eq,n

+(W

n

+2D

drain

)C

jsw,n

K

eq,n

C

dp,n

= (W

p

D

drain

+x

j

D

drain

)C

j0,p

K

eq,p

+(Wp+2D

drain

)C

jsw,p

K

eq,p

Therefore, C

load

can be rewritten as

C

load

=

0

+

n

W

n

+

p

W

p

where

0

= D

drain

(2C

jsw,n

K

eq,n

+2C

jsw,p

K

eq,p

+x

j

C

j0,n

K

eq,n

+x

j

C

j0,p

K

eq,p

)+C

int

+C

g

n

= K

eq,n

(C

j0,n

D

drain

+C

jsw,n

)

p

= K

eq,p

(C

j0,p

D

drain

+C

jsw,p

)

small

18

CMOS Inverter Design: Device Sizing (4/5)

Therefore,

PHL

and

PLH

are

The ratio between the channel widths W

n

and W

p

is

usually dictated by other design constraints such as

noise margins and the logic inversion threshold.

Lets this transistor aspect ratio be defined as R

W

p

/W

n

. Then, the propagation delay can be

represented as

( )

( )

( )

( )

, ,

, ,

, ,

, ,

0

0

4

2

ln 1

4 2

ln 1

DD T n T n n

PHL

ox DD T n DD T n DD n

DD T p T p p

P

n n p p

n

n

LH

DD T p DD ox DD T p n

n p p

p

W W

W

W

V V V L

C V V V V V

V V V L

V V V C V V

W

W

= +

=

+ +

+ +

0

0

( )

( )

PHL

PLH

n p n

n

n

n

p p

p

p

R W

W

W

R

W

+ +

+ +

=

=

19

CMOS Inverter Design: Device Sizing (5/5)

As we continue increase the values of W

n

and

W

p

, the propagation delay will asymptotically

approach a limit value for lager W

n

and W

p

,

The propagation delay times cannot be

reduced beyond the above limits, and the

limit is independent of the extrinsic

capacitances.

( )

( )

limit

PHL

limit

P

n n p

n

p

H

p

L

R

R

=

=

+

20

CMOS Inverter Design: Impact of Rise Time on Delay

p

H

L

(

n

s

e

c

)

0.35

0.3

0.25

0.2

0.15

rise

(nsec)

1 0.8 0.6 0.4 0.2 0

( )

( )

2

(stepinput)

2

(stepinput)

2

2

2

2

PHL PHL

P

r

f

LH PLH

= +

= +

Propagation delay increases

since both PMOS and

NMOS are on during the

charge-up and charge-down

events.

21

CMOS Inverter Design

Impact of Channel Velocity Saturation

The drain current is linearly dependent on V

GS

I

sat

= W

n

(V

GS

-V

T

)

Propagation delay only has a weak dependence on the

supply voltage V

DD

( )

( )

50%

/2

load DD

n

load

PH

D T

L

sat

D

C V

W V

C V

I

V

22

CMOS Dynamic Analysis: Dynamic Power Dissipation (1/2)

The dynamic power dissipation can be derived as

follows.

P

dyn,avg

= V

DD

I

DD,avg

With I

DD,avg

taken over one clock period T. The

capacitance current which equals the current from the

power supply (assuming I

Dn

= 0 during charging) is

Rearranging and integrating over one clock period T

Gives

I

DD,avg

T = C

load

V

DD

dt

dV

C I

out

load D

=

=

V

out load

T

D

DD

dV C

dt

I

0 0

23

CMOS Dynamic Analysis: Dynamic Power Dissipation (2/2)

Solving for I

DD,avg

and substituting in P

avg

:

In terms of SPICE simulation, the authors offer

a circuit called power meter.

It should be noted here the our simple Cload

may underestimate the power dissipated.

In terms of SPICE simulation, it offers a circuit

called power meter.

f

V C V C

T

P

DD load DD load avg

2 2

1

= =

24

Das könnte Ihnen auch gefallen

- Lab Report On ECE 210 Lab1Dokument6 SeitenLab Report On ECE 210 Lab1Joanne Lai100% (1)

- Solutions To Homework 4: Problem 1 (15 Points)Dokument15 SeitenSolutions To Homework 4: Problem 1 (15 Points)joa91189100% (1)

- Tabela e Shperndarjes NormaleDokument2 SeitenTabela e Shperndarjes NormaleAnonymous wGpvZAKNoch keine Bewertungen

- Cadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyDokument6 SeitenCadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyUtsavNoch keine Bewertungen

- Vlsi Lab 1Dokument11 SeitenVlsi Lab 1Shawon karmokar JotyNoch keine Bewertungen

- Analog Integrated Circuits LabDokument10 SeitenAnalog Integrated Circuits Labruchi0690Noch keine Bewertungen

- Chapter2-Microcontroller Architecture & Assembly Language Pt3Dokument36 SeitenChapter2-Microcontroller Architecture & Assembly Language Pt3adamwaiz100% (2)

- PLC Ushtrime PDFDokument21 SeitenPLC Ushtrime PDFKristi GjokaNoch keine Bewertungen

- NETWORK ANALYSIS Chap.8 TWO PORT NETWORK & NETWORK FUNCTIONS PDFDokument34 SeitenNETWORK ANALYSIS Chap.8 TWO PORT NETWORK & NETWORK FUNCTIONS PDFsudarshan poojaryNoch keine Bewertungen

- Pyetje Me Alternative (Cdo Pyetje Vleresohet Me 5 Pike)Dokument11 SeitenPyetje Me Alternative (Cdo Pyetje Vleresohet Me 5 Pike)Iris Parruca100% (1)

- Transmetimet RadioDokument31 SeitenTransmetimet RadioIvo GjokaNoch keine Bewertungen

- Epoka University: Academic Year 2020-2021 Fall Final Exam Course: Physics 101Dokument10 SeitenEpoka University: Academic Year 2020-2021 Fall Final Exam Course: Physics 101bnfxnNoch keine Bewertungen

- Termo 1' Modeli 3.doc EraldiDokument12 SeitenTermo 1' Modeli 3.doc EraldiFeritNoch keine Bewertungen

- Chapter 6Dokument18 SeitenChapter 6Ralph Luigie JebulanNoch keine Bewertungen

- Termo 1' Modeli 9.nuk e NjohDokument10 SeitenTermo 1' Modeli 9.nuk e NjohFeritNoch keine Bewertungen

- Termo 1' Modeli 5. Migeni.Dokument12 SeitenTermo 1' Modeli 5. Migeni.FeritNoch keine Bewertungen

- Simple FSKDokument6 SeitenSimple FSKFaten AliNoch keine Bewertungen

- Finite Element Method Magnetics - FEMM 4Dokument10 SeitenFinite Element Method Magnetics - FEMM 4Antonio MoraisNoch keine Bewertungen

- Termo 1' Modeli 8. BesmiriDokument11 SeitenTermo 1' Modeli 8. BesmiriFeritNoch keine Bewertungen

- Expt # 6 Two Port Network - Z ParametersDokument10 SeitenExpt # 6 Two Port Network - Z ParametersRohanNoch keine Bewertungen

- Chapter2pp010 020 PDFDokument11 SeitenChapter2pp010 020 PDFInderMaheshNoch keine Bewertungen

- Lab 6 - Transient Analysis (Transient Response) of Series RL Circuit Using OscilloscopeDokument3 SeitenLab 6 - Transient Analysis (Transient Response) of Series RL Circuit Using OscilloscopehamzaNoch keine Bewertungen

- Exam 2 SolDokument6 SeitenExam 2 Soldummy1957jNoch keine Bewertungen

- Full Report - E1Dokument13 SeitenFull Report - E1Naddy MohdNoch keine Bewertungen

- 3.1 Analog MultipliersDokument17 Seiten3.1 Analog MultipliersMarykutty CyriacNoch keine Bewertungen

- EEE 3571 Assignment 3 and 4Dokument3 SeitenEEE 3571 Assignment 3 and 4Emmanuel Nama HasalamaNoch keine Bewertungen

- Sampling PDFDokument187 SeitenSampling PDFAhmed ShujaNoch keine Bewertungen

- PSK Qam2 PDFDokument43 SeitenPSK Qam2 PDFKim Kenneth UgayNoch keine Bewertungen

- Electrical Engineering Lab ReportDokument7 SeitenElectrical Engineering Lab ReportFrancis Paul SantiagoNoch keine Bewertungen

- Co-Planar Waveguide (Driven Terminal) : GroundDokument6 SeitenCo-Planar Waveguide (Driven Terminal) : GroundRohini ManchaiahNoch keine Bewertungen

- Paraqitja Ne DiagramatDokument12 SeitenParaqitja Ne DiagramatLeti HanajNoch keine Bewertungen

- AFM Lab ReportDokument14 SeitenAFM Lab Reportsmoothieboy0% (1)

- Vsat Doc PDFDokument24 SeitenVsat Doc PDFV'nod Rathode BNoch keine Bewertungen

- Week 4Dokument39 SeitenWeek 4EVTNoch keine Bewertungen

- Ammeter DesignDokument17 SeitenAmmeter Designnord2500Noch keine Bewertungen

- Low Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron TechnologyDokument5 SeitenLow Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron Technologyeditor_ijtel100% (1)

- Chapter 31B - Transient Currents and InductanceDokument30 SeitenChapter 31B - Transient Currents and Inductanceqwivy.comNoch keine Bewertungen

- 01 RLC Circuit and ResonanceDokument46 Seiten01 RLC Circuit and ResonanceLatif Nurohman Bayu Nugroho60% (5)

- Generation of High Voltage DC Using Diodes & Capacitors in Ladder NetworkDokument6 SeitenGeneration of High Voltage DC Using Diodes & Capacitors in Ladder NetworkEditor IJRITCCNoch keine Bewertungen

- Lab#7 I&M 078Dokument9 SeitenLab#7 I&M 078Asad saeedNoch keine Bewertungen

- Skin Effect and Dielectric Loss Models of Power Cables 04784562Dokument8 SeitenSkin Effect and Dielectric Loss Models of Power Cables 04784562Gilberto Mejía100% (1)

- Optimal Design of A Reversible Full AdderDokument17 SeitenOptimal Design of A Reversible Full AdderMohamedNoch keine Bewertungen

- ELEC425 Assignment5 SolutionsDokument19 SeitenELEC425 Assignment5 SolutionsAzina KhanNoch keine Bewertungen

- AC DC Analysis BJT Diffrential Amp PDFDokument8 SeitenAC DC Analysis BJT Diffrential Amp PDFtanishk jainNoch keine Bewertungen

- Monte Carlo Simulation of Solar CellsDokument12 SeitenMonte Carlo Simulation of Solar Cellsmani_vlsiNoch keine Bewertungen

- Sepic Converter Based DC Motor Speed ControlDokument18 SeitenSepic Converter Based DC Motor Speed ControlCrispNoch keine Bewertungen

- Charge Carriers in SemiconductorsDokument31 SeitenCharge Carriers in SemiconductorsMohammad Gulam AhamadNoch keine Bewertungen

- Magnetostatics - MATLAB & Simulink PDFDokument5 SeitenMagnetostatics - MATLAB & Simulink PDFNguyễn Thành CôngNoch keine Bewertungen

- BE OPAMP Operational Amplifiers by TJ ShivaprasadDokument56 SeitenBE OPAMP Operational Amplifiers by TJ ShivaprasadVedang PavanjeNoch keine Bewertungen

- Minimum Spanning TreeDokument11 SeitenMinimum Spanning TreeAjayChandrakarNoch keine Bewertungen

- Arduino SPWM Sine InverterDokument5 SeitenArduino SPWM Sine InvertermaurilioctbaNoch keine Bewertungen

- 2 Bit Comparator PDFDokument12 Seiten2 Bit Comparator PDFSunith CkNoch keine Bewertungen

- Triangular Wave Generator Using Op Amp - EEEGUIDE PDFDokument6 SeitenTriangular Wave Generator Using Op Amp - EEEGUIDE PDFDeepanshi RuhelaNoch keine Bewertungen

- Conversion of Galvanometer Into Voltmeter by Mr. Charis Israel AnchaDokument6 SeitenConversion of Galvanometer Into Voltmeter by Mr. Charis Israel AnchaCharis Israel Ancha50% (2)

- Lecture 2 (Communication Channel)Dokument23 SeitenLecture 2 (Communication Channel)baginno20014262Noch keine Bewertungen

- Lec 9 Super Buffer DesignDokument8 SeitenLec 9 Super Buffer DesignAbhishek GowdaNoch keine Bewertungen

- Fundamentals of MicroelectronicsDokument40 SeitenFundamentals of MicroelectronicsshankarNoch keine Bewertungen

- The Cmos Inverter: OutlineDokument20 SeitenThe Cmos Inverter: OutlinehappyharrNoch keine Bewertungen

- Dynamic CircuitDokument19 SeitenDynamic Circuitk.jp914733Noch keine Bewertungen

- S98 Lecture13Dokument12 SeitenS98 Lecture13manohar487Noch keine Bewertungen

- JAVA Interview Questions: Dinanath ThakurDokument5 SeitenJAVA Interview Questions: Dinanath Thakurasad_raza4uNoch keine Bewertungen

- Curriculum Vitae: E-Mail: PHONE: +917867942972 Permanent AddressDokument4 SeitenCurriculum Vitae: E-Mail: PHONE: +917867942972 Permanent Addressasad_raza4uNoch keine Bewertungen

- StrutsDokument99 SeitenStrutsasad_raza4u50% (2)

- Test FileDokument1 SeiteTest Fileasad_raza4uNoch keine Bewertungen

- Hello World Portlet Rendered With JSP For WebSphere Portal Version 4.1Dokument11 SeitenHello World Portlet Rendered With JSP For WebSphere Portal Version 4.1asad_raza4uNoch keine Bewertungen

- Web Page Designing Using HTML Complete CourseDokument178 SeitenWeb Page Designing Using HTML Complete CourseRavi Chandran R100% (1)

- Etl and Informatica TopicsDokument4 SeitenEtl and Informatica TopicsHussain ManzoorNoch keine Bewertungen

- Abap Step by Step BapiDokument18 SeitenAbap Step by Step Bapiskumar478775% (4)

- Sap - CRM TechnicalDokument3 SeitenSap - CRM Technicalasad_raza4uNoch keine Bewertungen

- Ant PDFDokument13 SeitenAnt PDFasad_raza4uNoch keine Bewertungen

- SAP QuestionsDokument37 SeitenSAP Questionsasad_raza4uNoch keine Bewertungen

- Java Means Durgasoft: An Introduction To AntDokument13 SeitenJava Means Durgasoft: An Introduction To Antasad_raza4uNoch keine Bewertungen

- Spring IntroductionDokument27 SeitenSpring Introductionasad_raza4uNoch keine Bewertungen

- Innoplexus Technical Test PaperDokument11 SeitenInnoplexus Technical Test Paperasad_raza4uNoch keine Bewertungen

- Innoplexus Technical Test PaperDokument11 SeitenInnoplexus Technical Test Paperasad_raza4uNoch keine Bewertungen

- PA GTC 04 2016 LecturerDokument3 SeitenPA GTC 04 2016 Lecturerasad_raza4uNoch keine Bewertungen

- What Is Object Orientation?: Object Oriented Approach - Key FeaturesDokument14 SeitenWhat Is Object Orientation?: Object Oriented Approach - Key Featuresasadraza123Noch keine Bewertungen

- Coupon 1Dokument1 SeiteCoupon 1asad_raza4uNoch keine Bewertungen

- Spring IntroductionDokument27 SeitenSpring Introductionasad_raza4uNoch keine Bewertungen

- Linux by Zoom Tech PDFDokument141 SeitenLinux by Zoom Tech PDFasad_raza4uNoch keine Bewertungen

- 3rd Round Interview Q SigniwisDokument1 Seite3rd Round Interview Q Signiwisasad_raza4uNoch keine Bewertungen

- Linux Notes by Jitendra SirDokument125 SeitenLinux Notes by Jitendra Sirasad_raza4uNoch keine Bewertungen

- Reversible Watermarking Based On Invariant ImageDokument10 SeitenReversible Watermarking Based On Invariant Imageasad_raza4uNoch keine Bewertungen

- Audit LogDokument1 SeiteAudit Logasad_raza4uNoch keine Bewertungen

- XML Complete Notes JavaEra Com PDFDokument104 SeitenXML Complete Notes JavaEra Com PDFasad_raza4uNoch keine Bewertungen

- LicenseDokument5 SeitenLicensebnburkNoch keine Bewertungen

- Microsoft SQL Server Black Book PDFDokument397 SeitenMicrosoft SQL Server Black Book PDFasad_raza4uNoch keine Bewertungen

- AuditDokument1 SeiteAuditasad_raza4uNoch keine Bewertungen

- General Studies-II PDFDokument48 SeitenGeneral Studies-II PDFasad_raza4uNoch keine Bewertungen

- SOLUTIONS OF Ytha Yu Charles Marut-Assem PDFDokument129 SeitenSOLUTIONS OF Ytha Yu Charles Marut-Assem PDFSamira MahmoodNoch keine Bewertungen

- Micro Holtek 48R50A-1Dokument39 SeitenMicro Holtek 48R50A-1GlennNoch keine Bewertungen

- Scan Insertion FlowDokument9 SeitenScan Insertion Flowsharath ANoch keine Bewertungen

- Coa Unit-2Dokument25 SeitenCoa Unit-2PARTEEK RANANoch keine Bewertungen

- Gates Institute of Technology:: Gooty Digital Circuits and Systems 2 Marks With AnswersDokument20 SeitenGates Institute of Technology:: Gooty Digital Circuits and Systems 2 Marks With AnswersNaveen YallapuNoch keine Bewertungen

- VlsiDokument79 SeitenVlsimdhuq1Noch keine Bewertungen

- Flynn's ClassificationDokument13 SeitenFlynn's ClassificationManikandanVpNoch keine Bewertungen

- William Stallings Computer Organization and Architecture 7 Edition Computer Evolution and PerformanceDokument44 SeitenWilliam Stallings Computer Organization and Architecture 7 Edition Computer Evolution and Performancekhalil ahmadNoch keine Bewertungen

- EE103 Exp9 TOSHIT - 2101CB59Dokument5 SeitenEE103 Exp9 TOSHIT - 2101CB59Rahul PalNoch keine Bewertungen

- BSC (Hons) Electronics Computer Science - E33Dokument7 SeitenBSC (Hons) Electronics Computer Science - E33kriskl03Noch keine Bewertungen

- ST10R167 Q3Dokument63 SeitenST10R167 Q3Thiago LarangeiraNoch keine Bewertungen

- Altera Training Course Altera Training CourseDokument222 SeitenAltera Training Course Altera Training CoursetptuyenNoch keine Bewertungen

- Ucn5833 Bimos II 32-Bit Serial-InputDokument9 SeitenUcn5833 Bimos II 32-Bit Serial-InputOlga PlohotnichenkoNoch keine Bewertungen

- Eec 553,3RD Year Ece Lab Manual PDFDokument5 SeitenEec 553,3RD Year Ece Lab Manual PDFKumar Er AnupamNoch keine Bewertungen

- 7 Series Fpgas Data Sheet: Overview: General DescriptionDokument18 Seiten7 Series Fpgas Data Sheet: Overview: General DescriptionPraveen MeduriNoch keine Bewertungen

- (Engineering Series) Botros, Nazeih-HDL With Digital Design - VHDL and Verilog-Mercury Learning and Information (2015) PDFDokument565 Seiten(Engineering Series) Botros, Nazeih-HDL With Digital Design - VHDL and Verilog-Mercury Learning and Information (2015) PDFAhmed Aydın100% (2)

- Types and Characteristics of Processors: - ProcessorDokument50 SeitenTypes and Characteristics of Processors: - ProcessorOPie UPieNoch keine Bewertungen

- OpenWrt USB Print StorageDokument2 SeitenOpenWrt USB Print StoragefatadefacebookNoch keine Bewertungen

- LPC2148 TimersDokument4 SeitenLPC2148 TimersAnand BhaskarNoch keine Bewertungen

- Textile Based Capacitive SensorDokument12 SeitenTextile Based Capacitive SensorKrishna PrakashNoch keine Bewertungen

- Digital Systems Design (Ecen 2002)Dokument2 SeitenDigital Systems Design (Ecen 2002)Vikash KumarNoch keine Bewertungen

- Ds bl2600Dokument2 SeitenDs bl2600coiNoch keine Bewertungen

- Memory Ram Gigabyte b450m d3hDokument8 SeitenMemory Ram Gigabyte b450m d3hbeivaNoch keine Bewertungen

- Samsung 1G X 8 Bit - 2G X 8 Bit - 4G X 8 Bit NAND Flash Memory DatasheetDokument50 SeitenSamsung 1G X 8 Bit - 2G X 8 Bit - 4G X 8 Bit NAND Flash Memory Datasheetapi-3802214Noch keine Bewertungen

- Ytha Yu, Charles Marut-Assembly Language Programming Organization of The IBM PC (1992)Dokument551 SeitenYtha Yu, Charles Marut-Assembly Language Programming Organization of The IBM PC (1992)harini90% (72)

- Building A MUX-DEMUX Circuit Lab: OverviewDokument10 SeitenBuilding A MUX-DEMUX Circuit Lab: OverviewKaran MohiteNoch keine Bewertungen

- DH67CL Product Guide 02 EnglishDokument78 SeitenDH67CL Product Guide 02 EnglishTimm PetersonNoch keine Bewertungen

- SGH A188 Service SchematicsDokument22 SeitenSGH A188 Service SchematicsDinesh JenekarNoch keine Bewertungen

- Digital Design: An Embedded Systems Approach Using Verilog: Sequential BasicsDokument73 SeitenDigital Design: An Embedded Systems Approach Using Verilog: Sequential Basicsavinash_yuvarajNoch keine Bewertungen

- KTU S5 Microprocessor and Microcontroller CSE May 2019 Question PaperDokument2 SeitenKTU S5 Microprocessor and Microcontroller CSE May 2019 Question PaperAnand Baburajan0% (1)