Beruflich Dokumente

Kultur Dokumente

Design of High Speed Area Optimized Binary Coded

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Design of High Speed Area Optimized Binary Coded

Copyright:

Verfügbare Formate

IJRET: International Journal of Research in Engineering and Technology eISSN: 2319-1163 | pISSN: 2321-7308

__________________________________________________________________________________________

Volume: 03 Special Issue: 03 | May-2014 | NCRIET-2014, Available @ http://www.ijret.org 374

DESIGN OF HIGH SPEED AREA OPTIMIZED BINARY CODED

DECIMAL DIGIT ADDER

Deepak Rao

1

, Anuradha

2

1

Department of ECE, VLSI Design & Embedded System, Appa Institute of Engineering &Technology, Gulbarga

2

Department of ECE, VLSI Design & Embedded System, Appa Institute of Engineering & Technology, Gulbarga

Abstract

Decimal arithmetic is necessary for computations in the field of banking systems,tax calculations,telephone billings etc. The main

problem in the prevailing decimal arithmetic is the requirement of the correction of the result in its binary form. This results in larger

area and implementation delay. The proposed adder is improved for less delay and area requirement as a correction free mechanism

provides the result without adding any correction values.

Keywords:BCD Adder, Verilog code, Xilinx 9.2i.

-------------------------------------------------------------------------***-----------------------------------------------------------------

1. INTRODUCTION

Inthe era of electronic computing, decimal arithmetic plays a

vital role in commercial, financial, internet and industrial

control applications. Most of the computing applications are

based on binary arithmetic, but the real problem is that binary

approximation does not produce accurate result. For example if

a telecommunication company approximates a 5% sale tax on

an. Binary decimal arithmetic is required to avoid such

incorrect approximations. Also, in most of the applications,

decimal software runs on custom binary hardware in order to

produce precise decimal results, leading to another problem of

excessive delays. Software implementation of decimal

arithmetic is about 100 to 1000 times slower than the binary

implementation in hardware. In a survey of IBM corporation

showed that almost 55% of the numeric data columns, used by

51 major organizations databases, were decimal data types and

43.7% were integer types which can be stored as decimals. In

order to meet the need for growing evolution of decimal

arithmetic, its necessary to develop efficient

algorithms.Decimal digit adders and decimal digitmultipliers

are the building blocks of anydecimal hardware to support

decimalarithmetic.Here is a proposed high speed and area

optimized decimal digit adder. The design is described and

simulated using verilog hardware description language.

2. LITERATURE SURVEY

A combined binary and decimal adder was introduced by

I.S.Hwang[3]. The binary carry look ahead adder adds two

input operands which are either binary or decimal. Also a

reduced delay bcd adder with improved delay was proposed by

AlpArslaBayrakci and Ahmet Akkas[1]. Here a parallel prefix

network was used to generate carry thereby reducing the delay

in multi digit addition. Decimal Multiplication via carry-save

addition was introduced by Mark A.Erle and Michael

J.Schulte[5] where carry save addition was used to reduce

critical path delay.

3. PROPOSED BCD ADDER

Here an optimized correction free BCD digit adder is proposed.

The 2 decimal input digits of the BCD adder are A

{0, 9} and

B

{0, 9} and the decimal carry input is C

in

. We can represent

the decimal sum and the decimal carry as as S

{0, 9} and C

out

respectively. The decimal value of A, B, and S can be used to

obtain their 8421 BCD representation. In general, we can write

A =a

3

a

2

a

1

a

0

, B = b

3

b

2

b

1

b

0

, and S =s

3

s

2

s

1

s

0

, where a

i

, b

i

, and s

i

{0, 1} i {0, 1, 2, 3}. A and B can be expressed in terms of

two integers m = a

3

a

2

a

1

and n = b

3

b

2

b

1

as:

A = 2 m+ a

0

and B = 2 n + b

0

, where 0 m 4 and 0 n

4.This implies that the output of the BCD adder can be

expressed as

{COUT, SUM} = A+B+CIN

We can rearrange the above expression for BCD adder output

as:

{COUT,SUM} = (2 x m + a0) + (2 x n + b0) + Cin

=(2 x n +m) + (a0+b0+Cin)

Using the above formula, BCD digit adder is designed that

consists of two stages: Stage1 and Stage2. The inputs to Stage1

are m and n. Stage1 generates the partial decimal sum: Z =

z

3

z

2

z

1

z

0

0 = 2 (n + m). It should be observed that this decimal

partial sum consists of an even decimal digit (z

2

z

1

z

0

0) and a

decimal carry z

3

that can be either 1 or 0 based on the values of

m and n.

IJRET: International Journal of Research in Engineering and Technology eISSN: 2319-1163 | pISSN: 2321-7308

__________________________________________________________________________________________

Volume: 03 Special Issue: 03 | May-2014 | NCRIET-2014, Available @ http://www.ijret.org 375

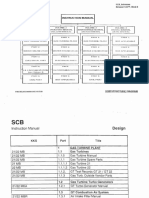

4. BLOCK DIAGRAM.

This block diagram consists of two stages wherein the first

stage computes the n and m values from the given input values.

Stage 1 generatespartial decimal sum Z = Z0Z1Z2Z3 =2 x (n +

m). This partial sum consists of even decimal digit z2z1z00

and a decimal carry z3 based on m & n. The second stage

generates the required sum. Since result of stage1 is always

even, only z2z1z00 are passed to stage2. The outputs of Stage1

along with a0, b0, and Cin are given as input to Stage2. In order

to design Stage2, the values of Cout, s3, s2, s1, and s0 are

calculated for all possible combinations of z3, z2, z1, z0, a0, b0,

and Cin and optimized boolean equations for Stage2 are

derived.

Fig 1Block Diagram of proposed Adder

5. SIMULATION RESULTS

Fig 2 Simulation result of correction free BCD Adder

Fig 3 Design Summary

Figure 2 here shows the simulation result of the proposed BCD

adder. Two decimal numbers less than 9 are added. Figure 3

shows the device utilization summary iwhich shows the number

of LUTs required, number of slices and number of IOB,s

sequentially.

6. CONCLUSIONS

In this report, direct Boolean expression binary coded decimal

digit adder will produce the output in the BCD form. As a result

a correction free BCD digit adder is obtained when compared

with the existing system which needs an analyzer circuit for

determining the whether the output value is greater than 9.Here

the Boolean expression is obtained using two-level logic

optimization is modified to multilevel logic optimization for

reducing the area and delay. The design is synthesized, verified

and tested for correct functionality using verilog coding and

simulation.

REFERENCES

[1].Alp ArslanBayrakci and Ahmed Akkas Reduced Delay

BCD Adder IEEE International Conf. on Apllication specific

Systems, Architectures and Processors (ASAP 2007). Volume-

Issue: 9-11,Page(s):266-271 July2007

[2]. A.Vazquez,E. Antelo, Conditional speculative decimal

addition, Nancy,France,2006, pp. 47-57.

[3]. I.S. Hwang, High Speed Binary and Decimal Arithmetic

Unit, United States Patent 2007.

[4]. Osama Al-Khaleel,Mohammad Al-Khaleel, Zakariah Al-

Qudah Fast Binary/Decimal Adder/Subtracter with a novel

correction free BCD Addition in IEEE Cinferece on Computer

arithmetic, 2011.

[5].M.A.Erleand M.J.Shulte Decimal Multiplication via Carry-

Save Addition (June 2003) IEEE lntl Conference on

Application Specific system Architectures and Processors, pp

.348-358.

Das könnte Ihnen auch gefallen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5795)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Datalogic Gryphon GM4100 User GuideDokument52 SeitenDatalogic Gryphon GM4100 User Guidebgrabbe92540% (1)

- Redseer Consulting Report On Vernacular LanguagesDokument36 SeitenRedseer Consulting Report On Vernacular LanguagesMalavika SivagurunathanNoch keine Bewertungen

- Exact Solution Tank DrainageDokument8 SeitenExact Solution Tank DrainageFelipe CastNoch keine Bewertungen

- ADPlaylistEditor3 (Network Version)Dokument42 SeitenADPlaylistEditor3 (Network Version)Dramane BonkoungouNoch keine Bewertungen

- Congratulations On The Purchase of Your New Antari Z Series Fog MachineDokument20 SeitenCongratulations On The Purchase of Your New Antari Z Series Fog MachineWalter SeidlNoch keine Bewertungen

- Methodology - Static Load Test PDFDokument5 SeitenMethodology - Static Load Test PDFEngr. MahmudNoch keine Bewertungen

- Voice Recognition Using MatlabDokument10 SeitenVoice Recognition Using MatlabSneha Muralidharan100% (1)

- Off Budgell FRCR - VerificationDokument46 SeitenOff Budgell FRCR - VerificationAmr MuhammedNoch keine Bewertungen

- Street Quality Identification Device (SQUID)Dokument6 SeitenStreet Quality Identification Device (SQUID)viviolaNoch keine Bewertungen

- Nitrile RubberDokument1 SeiteNitrile RubberMohamedNoch keine Bewertungen

- Safe Work Method StatementDokument176 SeitenSafe Work Method StatementMohamed Rizwan100% (2)

- ODAA Support LetterDokument2 SeitenODAA Support LetterStatesman JournalNoch keine Bewertungen

- EXCEL To Tally LeggerImport-ok - 2Dokument7 SeitenEXCEL To Tally LeggerImport-ok - 2Mukesh MakadiaNoch keine Bewertungen

- KX Tde600 FeatureDokument460 SeitenKX Tde600 Featureabg121Noch keine Bewertungen

- Modeling Complex Zo For Op AmpsDokument28 SeitenModeling Complex Zo For Op Ampswalid OUNISNoch keine Bewertungen

- Tugs - Developments For PDFDokument28 SeitenTugs - Developments For PDFP Venkata SureshNoch keine Bewertungen

- Assessment of Rotational Capacity Test Procedure FINALDokument21 SeitenAssessment of Rotational Capacity Test Procedure FINALzaheerahmed77Noch keine Bewertungen

- Part Submission ChecklistDokument8 SeitenPart Submission ChecklistGeovanny HernándezNoch keine Bewertungen

- Gas Turbine Manual PDFDokument721 SeitenGas Turbine Manual PDFZakki Afifi100% (2)

- Fpcroute User GuideDokument34 SeitenFpcroute User GuideJosé EireneNoch keine Bewertungen

- AB-505 Risk Based Inspection Programs For Pressure EquipmentDokument23 SeitenAB-505 Risk Based Inspection Programs For Pressure Equipmentjeswin100% (1)

- CAL-ST-070!17!01 Rev01 Shipping Saddles CalculationDokument11 SeitenCAL-ST-070!17!01 Rev01 Shipping Saddles CalculationgiubelloNoch keine Bewertungen

- Hoses & AppliancesDokument92 SeitenHoses & Appliancestheguy 21100% (1)

- LAPORAN PRAKTIK KERJA LAPANGAN - Id.enDokument25 SeitenLAPORAN PRAKTIK KERJA LAPANGAN - Id.enAhmad JupriNoch keine Bewertungen

- Waste To Energy: A Possibility For Puerto Rico, 5-2007Dokument57 SeitenWaste To Energy: A Possibility For Puerto Rico, 5-2007Detlef LoyNoch keine Bewertungen

- Project On RaymondDokument36 SeitenProject On Raymonddinesh beharaNoch keine Bewertungen

- TCSP10403R0Dokument30 SeitenTCSP10403R0BADRI VENKATESHNoch keine Bewertungen

- Boiler Safety ProgramDokument8 SeitenBoiler Safety ProgramHussain KhanNoch keine Bewertungen

- pLINES Datasheet FP V2.22Dokument2 SeitenpLINES Datasheet FP V2.22TrinhDinhLoc0% (1)

- Numerical Modeling of MHD Convective Heat and Mass Transfer in Presence of First-Order Chemical Reaction and Thermal RadiationDokument20 SeitenNumerical Modeling of MHD Convective Heat and Mass Transfer in Presence of First-Order Chemical Reaction and Thermal Radiationmanasdutta3495Noch keine Bewertungen