Beruflich Dokumente

Kultur Dokumente

Mpeg

Hochgeladen von

jnax101Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Mpeg

Hochgeladen von

jnax101Copyright:

Verfügbare Formate

MPEG

Compression

MPEG-2 and MPEG-4

MPEG 2

Video Compression

Bandwidth is precious!

MPEG compression helps get the most out of available bandwidth

A trade off between amount of data to be sent and acceptable picture

quality

Uncompressed high-definition pictures take too much bandwidth

to send down a 6MHz or 8MHz cable channel (up to 40Mbps)

1920 x 1080 24-bit pixels @ 30 frames per second = 1.49Gbps!

Storage of content is also much more efficient with video

compression

Definition Lines/Frame Pixels/Line Aspect Ratios Frame Rates

High (HD) 1080 1920 16:9 23.976p, 24p, 29.97p, 29.97i, 30p, 30i

High (HD) 720 1280 16:9 23.976p, 24p, 29.97p 30p, 59.94p, 60p

Standard (SD) 480 704 4:3, 16:9 23.976p, 24p, 29.97p, 29.97i, 30p, 30i, 59.94p, 60p

Standard (SD) 480 640 16:9 23.976p, 24p, 29.97p, 29.97i, 30p, 30i, 59.94p, 60p

ATSC Table III

MPEG 3

MPEG Applications

5 Kbps

100 Kbps 1 Mbps

10 Mbps

Video Phones

GSM/3G Phones

Internet Video

Streaming Apps

Digital Cinema

Studio Profile

100 Mbps 1 Gbps

Xilinx Solution

Partial MPEG-4

H/W acceleration

Peripherals (IrDA,

UART, I2C, SPI)

Memory Interfaces

(SRAM, SDRAM,

Flash)

Xilinx Solution

Peripherals (IrDA,

UART, I2C, SPI)

Memory Interfaces

(SRAM, SDRAM,

Flash)

Xilinx Solution

Full/Partial H/W

acceleration

High performance

parallel DSP

algorithms

Multiple processor

instantiations (PPC,

uBlaze)

Custom logic

Xilinx Solution

Full H/W acceleration

Ultra High

performance parallel

DSP algorithms

Multiple processor

instantiations (PPC,

uBlaze)

Custom logic

MPEG 4

HDTV and Bandwidth

HDTV may eventually prove popular with consumers

HDTV might even be legislated as must carry in the US

Operators face adding channel capacity

Could mean rebuilding entire facility!

Much rather use better compression techniques

Squeeze more down the same coax/fibre

Relatively inexpensive to implement

Also concern about cost of providing high-definition

capability at customer premise

Ship out new set-top boxes or upgrade in the field?

MPEG 5

MPEG Compression

Spatial Processing

Uses DCT within a single picture

to enable removal of high frequencies

not discernable to human eye

Temporal Processing

Seeking out and removing redundancy

between successive images/frames

Variable Length Coding (VLC)

Use shortest codes for most common samples

Run Length Encoding (RLE)

Replace long strings of zeros with single command code

MPEG 6

Spatial Redundancy

DCT

Returns the discrete cosine transform of video/audio input

Can be referred to as the even part of the Fourier series

Converts an image or audio block into its equivalent frequency

coefficients

IDCT

Inverse of the DCT function

IDCT reconstructs a sequence from its discrete cosine

transform (DCT) coefficients

MPEG 7

DCT in MPEG Compression

Spatial Frequency

S

e

n

s

i

t

i

v

i

t

y

Scan macroblock

in 8x8 blocks

Determine luma &

chromapixel values

Luma samples shown here

(Chroma processed

seperately)

Convert to frequency

components (DCT)

Human eye less sensitive to

high frequencies

Compress using zigzag scan

and run length encoding for

zero values (in blue)

Further compression with

Huffman encoding (VLC)

Output DCT coefficients Quantize higher frequencies

with less bits (weighting)

Zero values for frequencies

below perception threshold

2

2

3

3

4

4

5

5

6

6

7

7

8

8

1

1

Scan picture using 16x16

pixel macroblock

MPEG 8

I B B P B B P B B I B B P B B P B B I

GOP (Group Of Pictures)

Temporal Redundancy

I - Intra coded (spatially coded) pictures

Forms the anchor for a GOP

P - Forward Predicted pictures

Predicted from previous I or P pictures

P picture made up of vectors showing where to get pixel data from in previous pictures and/or

values that must be added to previous picture to get current pixel value

B - Bidirectional Predicted pictures

Predicted from previous or later I or P pictures (never from other B pictures)

Made up of vectors showing where to get pixel data from in previous pictures

MPEG 9

Picture Difference

Difference between successive pictures easy to calculate

using subtractor

Picture difference can also be spatially compressed

DCT, VLC, RLE etc. as before

Current

Picture

Current

Picture

Previous

Picture

Previous

Picture

Delay Buffer

Delay Buffer

Picture

Difference

Picture

Difference

+

-

MPEG 10

DCT

DCT

Inverse DCT

Inverse DCT

Quantization

Quantization

Inverse

Quantization

Inverse

Quantization

Frame

Memory

Frame

Memory

Motion

Compensation

Motion

Compensation

Motion

Estimation

Motion

Estimation

Encoding

Encoding

MPEG-2 Encoder

Hardware acceleration

particularly suited to most

complex parts of MPEG-2

algorithm

DCT/IDCT

Motion Estimation/

Compensation

Acceleration techniques

similar for MPEG-4 or other

compression schemes

MPEG 11

MPEG-4 Encoder

DCT

DCT

Inverse DCT

Inverse DCT

Quantization

Quantization

Inverse

Quantization

Inverse

Quantization

Frame

Memory

Frame

Memory

Motion

Compensation

Motion

Compensation

Motion

Estimation

Motion

Estimation

Encoding

Encoding

Shape Coding

Shape Coding

Multiplex

Multiplex

MPEG 12

Bogging down the processor

Processors excellent for sequential and control tasks

Implementing MPEG-4 compression algorithms can very

easily bog down a traditional processor

Over 50% of processor cycles may be spent evaluating one

block of an algorithm (motion estimation, etc.)

Necessitates the need for dedicated H/W acceleration

FPGAs are ideal

Processor vendors have bolted on dedicate DSP blocks

for H/W acceleration

Inflexible and still performance limited

Not suitable for Studio and Digital Cinema applications

MPEG 13

Offloading MPEG Algorithms

Why?

Saves valuable processor cycles

Increased quality and performance

Potential system cost savings

Ability to add more capabilities (codecs) to the system

Which portions prime targets?

Motion estimation, Motion Compensation, DCT/IDCT,

Color Space Conversion

MPEG 14

Motion Estimation

Estimation predicts next picture by shifting data from previous picture along a

calculated motion vector

In encoder, predicted picture is compared to actual picture and any prediction

errors calculated

Transmitting motion vectors and prediction errors takes much less bandwidth

than coding entire picture

Part of image that is common

between frames but has moved

Original position of picture

segment in previous frame

Mption vector sent with

any prediction errors

MPEG 15

Calculating Motion

Estimation Requirements

For CIF (352x288) resolutions

Each block has 16x16 = 256 pixels

16x16 = 256 search positions

Each frame has 396 (352/16 * 288/16) blocks

20 frames per second

256 x 256 x 396 x 20 = 778,567,680 calculations

Requires 779MHz general-purpose processor that can perform

addition and subtraction in one clock cycle!

Ideal for implementation inside FPGA

MPEG 16

Motion Compensation

Process of compensating for the displacement of moving

objects from one frame to the next

The use of motion vectors to improve the efficiency of the

prediction of pel values. The prediction uses motion

vectors to provide offsets into the past and/or future

reference pictures containing previously decodedpel

values that are used to form the prediction error signal.

Replaces a picture or portion of a picture based on displaced

pelsof a previously transmitted frame in an image sequence

MPEG 17

2-D DCT Operation

1

1

-

-

D DCT on Rows

D DCT on Rows

1

1

-

-

D DCT on Columns

D DCT on Columns

Application Note and Reference Design Available

http://www.xilinx.com/xapp/xapp610.pdf

MPEG 18

2-D IDCT Operation

Application Note and Reference Design Available

http://www.xilinx.com/xapp/xapp611.pdf

1

1

-

-

D IDCT on Rows

D IDCT on Rows

1

1

-

-

D IDCT on Columns

D IDCT on Columns

MPEG 19

2-D DCT/IDCT Utilisation

2-D DCT

2-D IDCT

MPEG 20

SRAM

SDRAM

32-bit

Embedded

CPU

P

r

o

c

e

s

s

o

r

I

n

t

e

r

f

a

c

e

Memory Controller

Other Custom Logic

Partial MPEG H/W

Acceleration

DCT / IDCT

Motion Compensation

Motion Estimation

Applications

Web Tablets

Internet Appliances

Telematics

High-end PDAs

Dedicated

H/W

acceleration

blocks

MPEG 21

Customized MPEG

Implementation

SRAM

SDRAM

P

r

o

c

e

s

s

o

r

I

n

t

e

r

f

a

c

e

Memory Controller

Other Peripherals

DCT / IDCT

Motion Compensation

Motion Estimation

32-bit Soft-CPU

up to 100 D-MIPS

32-bit Soft-CPU

up to 100 D-MIPS

.

.

.

Multiple-

processor

instantiations

Resolution,

frame rate,

profile, level &

QoRdependent

Dedicated

H/W

acceleration

blocks

Applications

Digital TV

Plasma Displays

LCD Displays

Set-top Boxes

MPEG 22

High Performance

MPEG Applications

SRAM

SDRAM

P

r

o

c

e

s

s

o

r

I

n

t

e

r

f

a

c

e

Memory Controller

Other Peripherals

DCT / IDCT

Motion Compensation

Motion Estimation

32-bit Soft-CPU

up to 100 D-MIPS

Up to 4

PowerPC and

Multiple

MicroBlaze

instantiations

Resolution,

frame rate,

profile, level &

QoRdependent

Pipelined

and Parallel

Dedicated

H/W

acceleration

blocks

32-bit Hard CPU

420 D-MIPS

.

.

.

.

.

.

Applications

Studio Applications

Digital Cinema

MPEG 23

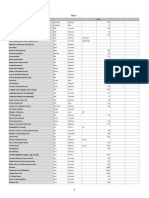

MPEG IP for Xilinx FPGAs

IP Core or Reference Design

XAPP610 Video Compression using DCT

XAPP611 Video Compression using IDCT

XAPP208 IDCT Implementation in Virtex

2-D DCT

1-D DCT

2-D DCT

2-D DCT/IDCT

2-D IDCT

2-D DCT

2-D DCT/IDCT

DCT/IDCT

MPEG-2 SDTV I & P Encoder

MPEG-2 HDTV I & P Encoder

Provider

Xilinx Inc.

Xilinx Inc.

Xilinx Inc.

Xilinx Inc.

Xilinx Inc.

eInfochips

BARCO-SILEX

CAST Inc.

CAST Inc.

CAST Inc.

TILAB

DumaVideo

DumaVideo

See http://www.xilinx.com/ipcenter for more details

See http://www.xilinx.com/ipcenter for more details

MPEG 24

FPGA Performance Advantage

Flexible architecture

Distributed DSP resources (LUT,

registers, multipliers, & memory)

Parallel processing maximizes

data throughput

Support any level of parallelism

Optimal performance/cost tradeoff

All 256 MAC operations

in 1 clock cycle

FPGA

....

C0

Data Out

C1 C2 C255

Reg0

Reg1 Reg2 Reg255

Data In

Example

256 Tap FIR Filter = 256 multiply and accumulate

(MAC) operations per data sample

MPEG 25

Loop

Algorithm

256 times

Performance Limitation of

Conventional DSP

Fixed inflexible architecture

Typically 1-4 MAC units

Fixed data width

Serial processing limits data

throughput

Time-shared MAC unit

High clock frequency creates

difficult system-challenge

Conventional DSP Device

(Von Neumann architecture, or

extensions thereof)

Example

256 Tap FIR Filter = 256 multiply and accumulate

(MAC) operations per data sample

Data Out

Reg

Data In

MAC unit

MPEG 26

Unrivalled DSP Performance

TeraMAC/s via FPGA and Embedded Multiplier fabric for:

Multimedia Compression - MPEG2, MPEG4, H.26L, MJPEG, JPEG2000

Video Processing - Integrated Line Buffers, Enhancement, Pattern Recognition, Noise

Reduction, Resizing, Rotation, Scalability

Convergence of emerging technologies in Multimedia over IP & wireless

For Standard Definition Pixel Rates (13.5 MHz pixels)

SDTV Test equipment, Broadcast test equipment, Studio effects equipment, scan rate

converters, frame rate converters, MPEG-2 codecs

For High Definition Pixel Rates or Multiple Channels of Standard

Definition (74.25 MHz pixels)

HDTV Test equipment, Broadcast test equipment, Home Theatre

projection devices, Advanced studio effects, Conversions from SDTV,

MPEG-2 4:2:2 profile codecs

XtremeDSP for Video

MPEG 27

Traditional Processing

Control Tasks

Control Tasks

FIR Filter

C++ Code Stack

Control Tasks

FIR Filter

Math-intensive algorithms dominate the

processing capacity

CPU

CPU

RAM

RAM

FIR Filter FIR Filter

Processing time

Traditional

MPEG 28

Xtreme Processing

Control Tasks

Control Tasks

FIR Filter

C++ Code Stack

Control Tasks

FIR Filter

FIR Filter FIR Filter

Processing time

Traditional

PowerPC

Processor

PowerPC

Processor

XTREME

Processing

FIR Engine

(fabric/multipliers)

OCM

RAM

OCM

RAM

3

+

2

+

0 1

+

n

+

PowerPC with Application-Specific

Hardware Acceleration

The Virtex-II Pro Advantage

MPEG 29

Chroma Downsampling

Most MPEG-2 applications use 8-bit 4:2:0 sampling

But incoming data usually 10-bit 4:2:2 video

Maybe via SDI (Serial Digital Interface) for example

Conversion therefore needed before MPEG processing

This chroma downsampling is lossyform of data compression

4:2:2

to

4:2:0

4:2:2

to

4:2:0

DCT

DCT

Quantize

Coefficents

Quantize

Coefficents

Zig Zag

(Run

Length)

Encoding

Zig Zag

(Run

Length)

Encoding

Huffman

(Variable

Length)

Encoding

Huffman

(Variable

Length)

Encoding

10

8

SDI

Compressed

Video Out

Pixel Data In

MPEG Processing

Chroma

Downsampling

MPEG 30

4:2:2 and 4:2:0 Sampling

16x16 Macroblock Luma (Y) Sample Points Chroma(CrCb) Sample Points

4:2:2

4:2:0

Only interpolated Cr Cbvalues used

Only one horizontal Cr Cbvalue used for every Y

-

S

a

m

p

l

e

d

V

a

l

u

e

-

V

a

l

u

e

u

s

e

d

f

o

r

I

n

t

e

r

p

o

l

a

t

i

o

n

Easy in an FPGA!

Easy in an FPGA!

MPEG 31

FIR Filters for Xilinx FPGAS

IP Core or Reference Design

XAPP219 Transposed Form FIR Filters

MAC FIR

Serial Distributed Arithmetic FIR Filter

Parallel Distributed Arithmetic FIR Filter

Distributed Arithmetic FIR Filter

Provider

Xilinx Inc.

Xilinx Inc.

Xilinx Inc.

Xilinx Inc.

Xilinx Inc.

See http://www.xilinx.com/ipcenter for more details

See http://www.xilinx.com/ipcenter for more details

MPEG 32

Xilinx MPEG Encoder Solutions

Allow offload of complex processing to hardware

Leave host processor to manage the system

Increase system performance of ASSP based design

Software incapable of supporting smooth, high-quality, full-screen video

streaming

Hardware acceleration becomes a necessity!

MPEG sub-blocks, filters, image quality analysis

Support for multiple channels

ASSPssupport one or two channels at most

FPGAs can support many more and decrease overall system cost

Lower bill of materials, easier system management

Wide range of network interfaces supported

Flexibility, scalability, ease of integration

MPEG 33

Differentiation Around a

Mature Standard

FPGA implementation enables differentiation of product

MPEG really only definesbitstreamsyntax

Difficult to add value to totally ASSP-based algorithms

Proprietary compression and/or image improvements possible whilst still

conforming to standard

IP available for time-to-market advantage

Reprogrammable platform such as Virtex-II Pro ideal for

compression research

Hidden costs associated with ASIC development (e.g. NRE, risk)

not a factor with Xilinx FPGAs

Results in lower overall costs for production

Questions?

espteam@xilinx.com

Das könnte Ihnen auch gefallen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (894)

- Death and Life After DeathDokument16 SeitenDeath and Life After DeathCarol KitakaNoch keine Bewertungen

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Hendrix Jimi The Wind Cries MaryDokument5 SeitenHendrix Jimi The Wind Cries MaryJalil Choueiry50% (2)

- Stunning Digital Photography-PWYCDokument240 SeitenStunning Digital Photography-PWYCbucatarum_1100% (1)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Design of Masonry StructuresDokument33 SeitenDesign of Masonry StructuresBhushan Raisinghani100% (2)

- Yamaha Music ClassDokument15 SeitenYamaha Music Classhafiz_yaakop0% (1)

- 10 Dance Lesson PlansDokument31 Seiten10 Dance Lesson PlansCrystal TkachNoch keine Bewertungen

- O14 Tower: Stack Effect and Mechanical Floor DesignDokument1 SeiteO14 Tower: Stack Effect and Mechanical Floor Designprerna100% (1)

- The Music of Paul HindemithDokument18 SeitenThe Music of Paul Hindemith31088380% (5)

- Matt Morris VideosDokument9 SeitenMatt Morris VideosZiyaa Boghani100% (1)

- Final Test For Touchstone 4Dokument4 SeitenFinal Test For Touchstone 4Хүн ХүнийNoch keine Bewertungen

- Classd Digital Amplifier TutorialDokument54 SeitenClassd Digital Amplifier TutorialemerychNoch keine Bewertungen

- Elt 1 Practical 1.WpdDokument1 SeiteElt 1 Practical 1.Wpdjnax101Noch keine Bewertungen

- Box ExampleDokument6 SeitenBox Examplejnax101Noch keine Bewertungen

- Artwork SpecificationDokument4 SeitenArtwork Specificationjnax101Noch keine Bewertungen

- ELT 1 Prac 4Dokument2 SeitenELT 1 Prac 4jnax101Noch keine Bewertungen

- SG 3524Dokument3 SeitenSG 3524florianosNoch keine Bewertungen

- SG 3524Dokument15 SeitenSG 3524jnax101Noch keine Bewertungen

- 28701-En LZT14606 en A PDFV1R2Dokument3 Seiten28701-En LZT14606 en A PDFV1R2jnax101Noch keine Bewertungen

- Transistor NPN 2n222aDokument8 SeitenTransistor NPN 2n222aRoberto Eduardo Tenorio RamosNoch keine Bewertungen

- Electronics 1 Practical 6: Equipment RequiredDokument1 SeiteElectronics 1 Practical 6: Equipment Requiredjnax101Noch keine Bewertungen

- MC 14093Dokument8 SeitenMC 14093rrebollarNoch keine Bewertungen

- LM78XX Series Voltage Regulators: General DescriptionDokument6 SeitenLM78XX Series Voltage Regulators: General DescriptiondebabratalogonNoch keine Bewertungen

- SG3524 Application NotesDokument6 SeitenSG3524 Application NotesSANDEEP KUMAR RAHEJANoch keine Bewertungen

- Applications Using The SG3524: Integrated CircuitsDokument3 SeitenApplications Using The SG3524: Integrated Circuitsjnax101Noch keine Bewertungen

- Electronics 1 Practical 3 Circuit WaveformsDokument2 SeitenElectronics 1 Practical 3 Circuit Waveformsjnax101Noch keine Bewertungen

- Electronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment RequiredDokument1 SeiteElectronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment Requiredjnax101Noch keine Bewertungen

- LM317Dokument22 SeitenLM317jnax101Noch keine Bewertungen

- Electronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment RequiredDokument1 SeiteElectronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment Requiredjnax101Noch keine Bewertungen

- MAX619Dokument7 SeitenMAX619jnax101Noch keine Bewertungen

- LM393Dokument15 SeitenLM393Izabela AlcântaraNoch keine Bewertungen

- Data Sheet IC LM 723Dokument13 SeitenData Sheet IC LM 723Wahyu Sulistyo NugrohoNoch keine Bewertungen

- LM2524D/LM3524D Regulating Pulse Width Modulator: General DescriptionDokument22 SeitenLM2524D/LM3524D Regulating Pulse Width Modulator: General DescriptionrutayanpNoch keine Bewertungen

- LM337Dokument12 SeitenLM337jnax101Noch keine Bewertungen

- MAX608Dokument12 SeitenMAX608jnax101Noch keine Bewertungen

- Max 1642Dokument12 SeitenMax 1642jnax101Noch keine Bewertungen

- MAX606Dokument12 SeitenMAX606jnax101Noch keine Bewertungen

- Max 1672Dokument12 SeitenMax 1672jnax101Noch keine Bewertungen

- Max 1674Dokument12 SeitenMax 1674jnax101Noch keine Bewertungen

- Max 1672Dokument12 SeitenMax 1672jnax101Noch keine Bewertungen

- Max 1686Dokument4 SeitenMax 1686jnax101Noch keine Bewertungen

- Zillion TV CorporationDokument1 SeiteZillion TV Corporationmdaniels1901Noch keine Bewertungen

- Example of Maxim Violation and Speech Act AnalysisDokument4 SeitenExample of Maxim Violation and Speech Act AnalysisJuhari Yusuf FatahillahNoch keine Bewertungen

- Macbeth Is An Ancient Text That Has No Relevance or Parallels With Our Society Today.Dokument2 SeitenMacbeth Is An Ancient Text That Has No Relevance or Parallels With Our Society Today.Anubhav PunethaNoch keine Bewertungen

- The Hunger Game Book - EditedDokument6 SeitenThe Hunger Game Book - Editedjoseph mainaNoch keine Bewertungen

- The Old HouseDokument16 SeitenThe Old HouseAnonymous qXklPgGnMVNoch keine Bewertungen

- 18 - OPTIONAL - Lutz and Collins, 'The Photography As An Intersection of GazesDokument16 Seiten18 - OPTIONAL - Lutz and Collins, 'The Photography As An Intersection of GazesEmanon LNoch keine Bewertungen

- Odissi dancer and actress Nandini GhosalDokument5 SeitenOdissi dancer and actress Nandini GhosalAbhinav A AshishNoch keine Bewertungen

- How To Chant On BeadsDokument2 SeitenHow To Chant On BeadsvdaNoch keine Bewertungen

- GMM - Fabric Cutting AssignmentDokument10 SeitenGMM - Fabric Cutting AssignmentsatexNoch keine Bewertungen

- Dota 2 Item List PricesDokument3 SeitenDota 2 Item List PricesLabador LeoNoch keine Bewertungen

- AZEVEDO, Aina - Drawing Close - On Visual Engagements - in PDFDokument26 SeitenAZEVEDO, Aina - Drawing Close - On Visual Engagements - in PDFedgarcunhaNoch keine Bewertungen

- Memorex Mt1130c TV Service ManualDokument13 SeitenMemorex Mt1130c TV Service Manualricardo_MassisNoch keine Bewertungen

- EAL Booster: Writing SkillsDokument4 SeitenEAL Booster: Writing SkillssolitudeNoch keine Bewertungen

- Buddhist Heritage City of AmaravatiDokument26 SeitenBuddhist Heritage City of AmaravatiVenkat Aha ANoch keine Bewertungen

- World Music LessonDokument2 SeitenWorld Music Lessonapi-323143699Noch keine Bewertungen

- Common and Consumable Item Price ListDokument9 SeitenCommon and Consumable Item Price ListAl Patrick Dela CalzadaNoch keine Bewertungen

- The History and Development of the Armenian LanguageDokument2 SeitenThe History and Development of the Armenian Languageetna26Noch keine Bewertungen

- TeclisDokument4 SeitenTeclisCharlie BowenNoch keine Bewertungen

- Character Autopsy MacbethDokument1 SeiteCharacter Autopsy Macbethapi-331852131Noch keine Bewertungen

- DAGMAR Advertising Model ExplainedDokument11 SeitenDAGMAR Advertising Model ExplainedAmit KumarNoch keine Bewertungen