Beruflich Dokumente

Kultur Dokumente

AD9831EB

Hochgeladen von

jnax101Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

AD9831EB

Hochgeladen von

jnax101Copyright:

Verfügbare Formate

EVAL- AD9831EB

a

FEATURES

Full-Featured Evaluation Board for the AD9831

Various Linking Options

PC Software for Control of AD9831

Information furnished by Analog Devices is believed to be accurate and

reliable. However, no responsibility is assumed by Analog Devices for

its use; nor for any infringements of patents or other rights of third parties

which may result from its use. No license is granted by implication or

otherwise under any patent or patent rights of Analog Devices.

One Technology Way; P.O.BOX 9106; Norwood, MA 02062-9106 U.S.A.

Tel: 617/329-4700 Twx: 710/394-6577

Telex: 174059 Cables: ANALOG NORWOOD MASS

REV O

source via a B N C connector. L atches (74H C 574) are also on

the board, these latches being used to hold the 16-bit data

w ord being w ritten from the P C to the A D 9831.

OPERATING THE AD9831 EVALUATION BOARD

Power Supplies

T his evaluation board has tw o analog pow er supply inputs:

A V D D and A G N D . A V D D equals + 5 V or + 3.3 V and is

used to provide the A V D D for the A D 9831. D G N D and

D V D D connections are also available. T he D V D D is used to

provide the D V D D for the A D 9831, the 25 M H z oscillator

and the D V D D for the logic chips. D G N D and A G N D are

connected at the A D 9831. T herefore, it is recom m ended not

to connect A G N D and D G N D elsew here in the system .

A ll pow er supplies are decoupled to ground. A V D D and

D V D D are decoupled using 10F tantalum capacitors and

0.1F ceram ic capacitors at the input to the evaluation board.

T he pow er supplies are again decoupled using 0.1F capaci-

tors at the A D 9831, the crystal and the logic.

Eval uat i on Boar d f or t he AD9831

Di r ect Di gi t al Synt hesi zer

INTRODUCTION

T his A pplication N ote describes the evaluation board for the

A D 9831 D irect D igital Synthesizer (D D S). T he A D 9831 is a

num erically controlled oscillator em ploying a phase accum ula-

tor, a sine look-up table and a 10-bit D /A converter. T he

part can be operated w ith clock frequencies up to 25 M H z.

B oth phase m odulation and frequency m odulation can be per-

form ed w ith the A D 9831. F ull data on the A D 9831 is avail-

able in the A D 9831 datasheet available from A nalog D evices

and should be consulted in conjunction w ith this A pplication

N ote w hen using the evaluation board.

T he evaluation board interfaces to the parallel port of an IB M

com patible P C . Softw are is available w ith the evaluation

board w hich allow s the user to easily program the A D 9831.

C om ponents on the A D 9831 E valuation B oard include a 25

M H z oscillator w hich provides the M C L K for the A D 9831.

T he user can rem ove this oscillator, if required, and drive the

A D 9831 w ith a different clock oscillator or an external clock

Evaluation Board Setup

Parallel Port Centronics

Printer Cable

IBM Compatible PC

AD9831.EXE

AD9831 Evaluation

Board

- 2 -

REV O

EVAL- AD9831EB

Link and Switch Options

T here are five link options w hich m ust be set for the required operating setup before using the evaluation board. T he functions

of these options are outlined below .

Link No. Function

L K 1 T he P SE L 1 input can be controlled by the user via a B N C connector or, alternatively, by sw itch SW .

W hen L K 1 is arranged so that P SE L 1 is connected to SW , the user can control the P SE L 1 signal using the

double throw sw itch.

A lternatively, P SE L 1 can be tied to a B N C connector by altering L K 1 so that the user can provide the P SE L 1

control from a logic source.

L K 2 T he P SE L 0 input can be controlled by the user via a B N C connector or, alternatively, by sw itch SW .

W hen L K 2 is arranged so that P SE L 0 is connected to SW , the user can control the P SE L 0 signal using the

double throw sw itch.

A lternatively, P SE L 0 can be tied to a B N C connector by altering L K 2 so that the user can provide the P SE L 0

control from a logic source.

L K 3 T he F SE L E C T input can be controlled by the user via a B N C connector or, alternatively, by sw itch SW .

W hen L K 3 is arranged so that F SE L E C T is connected to SW , the user can control the F SE L E C T signal using

the double throw sw itch.

A lternatively, F SE L E C T can be tied to a B N C connector by altering L K 3 so that the user can provide the

F SE L E C T control from a logic source.

L K 4 L K 4 is used to place the A D 9831 in sleep m ode.

W hen L K 4 is connected so that SLEEP is tied to D G N D , the A D 9831 is placed in sleep m ode w hereby the

A D 9831's internal clocks, R E F O U T and the D A C are disabled.

W hen L K 4 is connected so that SLEEP is tied to D V D D , the A D 9831 is pow ered up.

L K 5 T he reference to the A D 9831 can be provided by the on-board reference, w hich is available at R E F O U T , or an

external reference of nom inal value 1.21 V can be used. W hen L K 5 is closed, the on-board reference is used.

W hen this link is opened, R E F IN is disconnected from R E F O U T and the reference can be provided by the

user via a B N C connector.

- 3 - REV O

Preliminary Technical Data AD7002

EVAL- AD9831EB

36-Way Connector Pin Description

D G N D D igital G round. T hese lines are connected

to the digital ground plane on the evaluation

board.

D B 0 - D B 7 D ata B it 0 to D ata B it 7. D ata transfers

from the P C are 8 bits w ide. T herefore, the

16 bit w ord is split into tw o 8 bit w ords.

F or each w rite operation, there are 3 trans-

fers of data from the P C : the 8 M SB s of the

16 bit w ord, the 8 L SB s of the 16 bit w ord

and the address data to bits A 0, A 1 and A 2.

T he A D 9831 accepts C M O S logic.

L O A D W hen the 8 M SB s of the 16 bit w ord are

w ritten to the evaluation board from the P C ,

the w ord is held in a latch, a 74H C 574 latch.

T his latch latches in the data on the rising

edge of the C K signal. T he L O A D signal

provides this rising edge.

L A T C H T he 8 L SB s of the 16 bit w ord are held in

the latch U 3. T he rising C K edge to this

part is provided by L A T C H .

WR W rite. T his is an active low logic input

w hich is used to w rite the digital data to the

A D 9831. W hen the address bits A 0, A 1 and

A 2 are being w ritten to, the WR signal is

generated also. O n the rising edge of WR,

the A D 9831 reads in the 16 bit w ord from

the 74H C 574 latches along w ith the address

values.

RESET R eset. W hen RESET is taken low , the

A D 9831 is reset. O n reset, the phase accu-

m ulator is reset to zero.

SET-UP CONDITIONS

C are should be taken before applying pow er and signals to the

evaluation board to ensure that all link positions are as per the

required operating m ode. T able 1 show s the position in w hich

all the links are set w hen the evaluation board is sent out.

Table 1. Initial Link and Switch Positions

Link No. Function

L K 1 L K 1 is arranged so that P SE L 1 is tied to

SW .

L K 2 L K 2 is arranged so that P SE L 0 is tied to

SW .

L K 3 L K 3 is arranged so that F SE L E C T is tied to

SW .

L K 4 L K 4 is connected so that SLEEP is tied to

D V D D and, hence, the A D 9831 is pow ered

up.

L K 5 R E F O U T is tied to R E F IN .

SW A ll the SW sw itches are arranged so that

D V D D is selected.

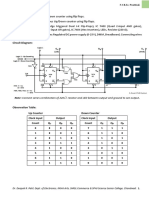

EVALUATION BOARD INTERFACING

Interfacing to the evaluation board is via a 36-w ay centronics

fem ale connector, J1. T he pinout for the J1 connector is

show n in F igure 1 and its pin designations are given in T able

2.

Figure 1. Pin Configuration for the 36-Way Connector, J1.

36 19

1 18

- 4 -

REV O

EVAL- AD9831EB

Table 2. 36-Way Connector Pin Funtions

PIN NO. MNEMONIC

1 L A T C H

2 D 0

3 D 1

4 D 2

5 D 3

6 D 4

7 D 5

8 D 6

9 D 7

14 RESET

19 D G N D

20 D G N D

21 D G N D

22 D G N D

23 D G N D

24 D G N D

25 D G N D

26 D G N D

27 D G N D

28 D G N D

29 D G N D

30 D G N D

31 L O A D

36 WR

N ote: T he rem ainder of the pins on the 36-w ay connector are no connects.

SOCKETS

T here are six sockets relevant to the operation of the A D 9831

on this evaluation board. T he function of these sockets is out-

lined in T able 3.

Table 3. Socket Functions

Socket Function

R E F IN Sub-M iniature B N C Socket for R E F IN .

IO U T Sub-M iniature B N C Socket for IO U T .

M C L K Sub-M iniature B N C Socket for the M C L K

input.

F SE L Sub-M iniature B N C Socket for F SE L E C T .

P SE L 0 Sub-M iniature B N C Socket for P SE L 0.

P SE L 1 Sub-M iniature B N C Socket for P SE L 1.

CONNECTORS

T here are three connectors on the A D 9831 evaluation board

as outlined in T able 4.

Table 4. Connector Functions

Connector Functions

J1 36-W ay C entronics C onnector.

J2 P C B M ounting T erm inal B lock. T he D igital

P ow er Supply to the E valuation B oard is

provided via this C onnector.

J3 P C B M ounting T erm inal B lock. T he A na-

log P ow er Supply to the E valuation B oard is

provided via this C onnector.

SWITCHES

T here is one sw itch on the A D 9831 evaluation board. T his

sw itch is a double throw , end stackable sw itch. T his sw itch

can be used to control the F SE L E C T , P SE L 0 and P SE L 1

inputs.

- 5 - REV O

Preliminary Technical Data AD7002

EVAL- AD9831EB

SOFTWARE DESCRIPTION

Included in the E V A L -A D 9831E B evaluation board package is a P C -com patible disk w hich contains softw are for controlling the

A D 9831 using the printer port of a P C . T he disk contains the executable program w hich runs under W indow s and it is advised

that the user copy this file to the system hard disk to obtain optim um perform ance from the softw are.

PC Configuration

T he executable program contains tw o m enus. T he first m enu gives options on the type of P C being used. T he printer port

needs to be configured correctly for one of the three different P C -types for interfacing to the A D 9831. C hoose the required

printer type from the m enu. T he P C printer port is now configured for operation w ith the A D 9831 evaluation board.

Figure 2. Parallel Port Selection

Running the AD9831 Software

T he second m enu gives options for running the A D 9831. A ll registers of the A D 9831 can be w ritten to using this softw are.

T he M C L K frequency is set to 25 M H z by default in the program . H ow ever, the user has the capability of changing the M C L K

frequency. W hen the m aster clock has a frequency other than 25 M H z, the user can change the value of the M C L K frequency

in the program so that the softw are can correctly calculate the digital w ords corresponding to the different output frequencies.

T he F requency R egisters are w ritten to by w riting in the required frequency in M H z to the P C . T he A D 9831 softw are w ill

calculate the corresponding w ord w hich w ill be w ritten to the A D 9831 and display the w ord in hex on the screen. T he P hase

R egisters are w ritten to by w riting in the required value in decim al to the P C . T he softw are w ill then control the loading of this

inform ation into the A D 9831.

T o w rite to a P hase R egister, three transfers of data from the P C are needed since the P C uses 8-bit transfers. T he 16 bit w ord

along w ith the address of the destination register is transferred from the P C to the A D 9831. T he sixteen bit w ord is split into

tw o 8-bit w ords (the 8 M SB s and the 8 L SB s). T he first transfer of data involves transferring the 8 M SB s of the 16-bit w ord.

W hen these 8 bits are being transferred, a pulse is also generated on the L O A D pin so that the 8 bits of data are latched into U 2

on the rising edge of L O A D .

D uring the second transfer, the 8 L SB s are transferred to U 3, a pulse being generated on the L A T C H pin so that these 8 bits are

latched into U 3.

T he third transfer involves transferring the address of the destination register (A 0, A 1 and A 2). W hen the P C outputs the

address inform ation (w hich is available on D 0, D 1 and D 2 respectively), the P C also generates the WR pulse. O n the rising

edge of WR, the 16 bits of data are read from the 74H C 574 latches and the address of the destination register is read from the

data bus.

B ecause the F requency R egisters are 32 bits w ide, there w ill be six transfers from the P C w hen these registers are being w ritten

to. W riting the 16 L SB s to the F requency R egister involves transferring the destination register address (000 or 010) and the 16

bits of data. Sim ilarly, the destination address for the 16 M SB s (001 or 011) and 16 bits of data need to be transferred w hen

w riting to the 16 M SB s of the F requency R egister.

T he logic inputs F SE L E C T , P SE L 0 and P SE L 1 are not controlled by the P C . T hese inputs can be controlled using the sw itch

SW or, alternatively, these inputs can be controlled using an external source via the B N C connectors.

- 6 -

REV O

EVAL- AD9831EB

T he A D 9831 softw are also contains a dem onstration procedure w hereby the A D 9831 can be m ade to step through a series of

output frequencies. T he user only needs to load the start frequency, the stop frequency and the step size and, the A D 9831

softw are w ill program the A D 9831 appropriately so that a frequency sw eep w ill be perform ed at the A D 9831 output.

Figure 3. Main Menu

- 7 - REV O

Preliminary Technical Data AD7002

EVAL- AD9831EB

Links

L K 1 - L K 4 T hree P in L ink

L K 5 T w o P in L ink

Sw itch

SW E nd Stackable Sw itch (SD C D ouble

T hrow )

Sockets

M C L K , P SE L 0, Sub-M iniature B N C C onnector

P SE L 1, F SE L E C T ,

IO U T , R E F IN

Connectors

J1 36-P in E dge C onnector

J2, J3 P C B M ounting T erm inal B lock

COMPONENT LIST

Integrated Circuits

X T A L 1 O SC X T A L 25 M H z

U 2, U 3 74H C 574 L atches

U 4 A D 9831 (48-P in T Q F P )

Capacitors

C 1 - C 6 0.1F C eram ic C hip C apacitor

C 7, C 8 10nF C eram ic C apacitor

C 9, C 11, C 13 - C 15 0.1F C eram ic C apacitor

C 10, C 12 10F T antalum C apacitor

Resistors

R 1 - R 3 10k R esistor

R 4 50 R esistor

R 5 3.9k R esistor

R 6 300 R esistor

AD9831

COMP

10 nF

REFIN

REFOUT

LK5

10 nF

FSADJUST

AVDD DVDD

D15

D8

LOAD

LATCH

42

41

2

40

RESET

32

21

14

4, 5, 9, 25 38, 43, 47

DVDD AVDD

0.1F 10F 10F 0.1F

C10 C9 C11 C12

J2

U2

DVDD

0.1F

C1, C2, C3

AVDD

0.1F

C4, C5, C6

AVDD

C7

C8

WR

MCLK

DGND

U1

50 R4

DVDD

DVDD

0.1F

C13

OUT

XTAL1

74HC574

CK

D7

D0 31

22

U3

74HC574

CK

IOUT

3.9k

300

A2

A0

WR

PSEL1

PSEL0

FSELECT

39

10

11

12

35

RESET

8

34

MCLK

DVDD

1, 36, 46

SLEEP

DGND AGND

6, 13, 29

U4

R5

R6

3

7

PC Interface

D7

D0

WR

RESET

LATCH

LOAD

J1

LK4

10K

R1

LATCH

D0

D1

D2

D3

D4

D5

D6

D7

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

34

35

36

33

RESET

LOAD

WR

LK3

LK2

LK1

DVDD SW

VDD

DVDD

0.1F

C15

VDD

DVDD

0.1F

C14

R2

R3

10K

10K

IOUT

REFIN

MCLK

PSEL1

PSEL0

FSELECT

J3

Das könnte Ihnen auch gefallen

- Box ExampleDokument6 SeitenBox Examplejnax101Noch keine Bewertungen

- Artwork SpecificationDokument4 SeitenArtwork Specificationjnax101Noch keine Bewertungen

- Classd Digital Amplifier TutorialDokument54 SeitenClassd Digital Amplifier TutorialemerychNoch keine Bewertungen

- SG 3524Dokument3 SeitenSG 3524florianosNoch keine Bewertungen

- Electronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment RequiredDokument1 SeiteElectronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment Requiredjnax101Noch keine Bewertungen

- 28701-En LZT14606 en A PDFV1R2Dokument3 Seiten28701-En LZT14606 en A PDFV1R2jnax101Noch keine Bewertungen

- Transistor NPN 2n222aDokument8 SeitenTransistor NPN 2n222aRoberto Eduardo Tenorio RamosNoch keine Bewertungen

- Applications Using The SG3524: Integrated CircuitsDokument3 SeitenApplications Using The SG3524: Integrated Circuitsjnax101Noch keine Bewertungen

- SG 3524Dokument15 SeitenSG 3524jnax101Noch keine Bewertungen

- SG3524 Application NotesDokument6 SeitenSG3524 Application NotesSANDEEP KUMAR RAHEJANoch keine Bewertungen

- MC 14093Dokument8 SeitenMC 14093rrebollarNoch keine Bewertungen

- Electronics 1 Practical 6: Equipment RequiredDokument1 SeiteElectronics 1 Practical 6: Equipment Requiredjnax101Noch keine Bewertungen

- Data Sheet IC LM 723Dokument13 SeitenData Sheet IC LM 723Wahyu Sulistyo NugrohoNoch keine Bewertungen

- Elt 1 Practical 1.WpdDokument1 SeiteElt 1 Practical 1.Wpdjnax101Noch keine Bewertungen

- Electronics 1 Practical 3 Circuit WaveformsDokument2 SeitenElectronics 1 Practical 3 Circuit Waveformsjnax101Noch keine Bewertungen

- Max 1642Dokument12 SeitenMax 1642jnax101Noch keine Bewertungen

- Electronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment RequiredDokument1 SeiteElectronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment Requiredjnax101Noch keine Bewertungen

- ELT 1 Prac 4Dokument2 SeitenELT 1 Prac 4jnax101Noch keine Bewertungen

- MAX608Dokument12 SeitenMAX608jnax101Noch keine Bewertungen

- LM2524D/LM3524D Regulating Pulse Width Modulator: General DescriptionDokument22 SeitenLM2524D/LM3524D Regulating Pulse Width Modulator: General DescriptionrutayanpNoch keine Bewertungen

- LM337Dokument12 SeitenLM337jnax101Noch keine Bewertungen

- LM78XX Series Voltage Regulators: General DescriptionDokument6 SeitenLM78XX Series Voltage Regulators: General DescriptiondebabratalogonNoch keine Bewertungen

- LM317Dokument22 SeitenLM317jnax101Noch keine Bewertungen

- MAX606Dokument12 SeitenMAX606jnax101Noch keine Bewertungen

- LM393Dokument15 SeitenLM393Izabela AlcântaraNoch keine Bewertungen

- Max 1672Dokument12 SeitenMax 1672jnax101Noch keine Bewertungen

- MAX619Dokument7 SeitenMAX619jnax101Noch keine Bewertungen

- Max 1674Dokument12 SeitenMax 1674jnax101Noch keine Bewertungen

- Max 1672Dokument12 SeitenMax 1672jnax101Noch keine Bewertungen

- Max 1686Dokument4 SeitenMax 1686jnax101Noch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5783)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (890)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (72)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Improvement of The Orthogonal Code Convolution Capabilities Using Fpga ImplementationDokument50 SeitenImprovement of The Orthogonal Code Convolution Capabilities Using Fpga Implementationscribdashokram100% (2)

- Laboratory Exercise 10: An Enhanced ProcessorDokument6 SeitenLaboratory Exercise 10: An Enhanced ProcessorRyan ReasNoch keine Bewertungen

- Electronic SymbolDokument28 SeitenElectronic Symbolsponge bobNoch keine Bewertungen

- 3-bit asynchronous Up/Down counter flip-flopsDokument2 Seiten3-bit asynchronous Up/Down counter flip-flopsIshtiaque Ahmed TanimNoch keine Bewertungen

- ECE Proposed New Syllabus PDFDokument79 SeitenECE Proposed New Syllabus PDFE.ramakrishnaNoch keine Bewertungen

- 1 Physics Vi Sem - 6a QP MPDokument5 Seiten1 Physics Vi Sem - 6a QP MPNAGESWARA RAo college AKKINENINoch keine Bewertungen

- Digital System Design Syllabus For EC 3 Sem 2018 Scheme - VTU CBCS 18EC34 SyllabusDokument2 SeitenDigital System Design Syllabus For EC 3 Sem 2018 Scheme - VTU CBCS 18EC34 SyllabusSYAMALA100% (1)

- Ecad and VLSI Lab Front PagesDokument2 SeitenEcad and VLSI Lab Front PagessurekhaNoch keine Bewertungen

- 16-Bit, 100 Ksps/200 Ksps Bicmos A/D Converter: W 10 V, 5 V and 3.3 VDokument24 Seiten16-Bit, 100 Ksps/200 Ksps Bicmos A/D Converter: W 10 V, 5 V and 3.3 Vlongtrandang5867Noch keine Bewertungen

- Aeroflex 04 Manual DT400HDokument222 SeitenAeroflex 04 Manual DT400HKonstantina GlezakouNoch keine Bewertungen

- Digital Electronics Assignment QuizDokument5 SeitenDigital Electronics Assignment QuizVinnu KumarNoch keine Bewertungen

- BD9486FDokument37 SeitenBD9486F94430s19684Noch keine Bewertungen

- Filip FlopsDokument4 SeitenFilip FlopsMohammed JeelanNoch keine Bewertungen

- Asic Implementation of Digital Pulse Shaping Fir FilterDokument22 SeitenAsic Implementation of Digital Pulse Shaping Fir FilteryasmeenkhanNoch keine Bewertungen

- The 8051 Microcontroller: (Please Ignore Repeated Slides If Any. Also, Refer Text Too While Studying All The Slides)Dokument78 SeitenThe 8051 Microcontroller: (Please Ignore Repeated Slides If Any. Also, Refer Text Too While Studying All The Slides)Nicky SanthoshNoch keine Bewertungen

- JNTU Digital System Design Supplementary Exam September 2010Dokument2 SeitenJNTU Digital System Design Supplementary Exam September 2010Ravula VenkateshNoch keine Bewertungen

- ATF2500C CPLD Family Datasheet ATF2500C: FeaturesDokument9 SeitenATF2500C CPLD Family Datasheet ATF2500C: FeaturesSolikin AjNoch keine Bewertungen

- Co Po DLCDokument31 SeitenCo Po DLCramachandranNoch keine Bewertungen

- mt8880 PDFDokument18 Seitenmt8880 PDFnazimaghabayovNoch keine Bewertungen

- Jawahar Navodaya Vidyalaya student's AND gate projectDokument16 SeitenJawahar Navodaya Vidyalaya student's AND gate projectnagarjunNoch keine Bewertungen

- Design and Analysis of Dual Edge Triggered (DET) Flip-Flops Using Multiple C-ElementsDokument8 SeitenDesign and Analysis of Dual Edge Triggered (DET) Flip-Flops Using Multiple C-ElementsArpita MukherjeeNoch keine Bewertungen

- Switchinng Theory and Logic Design July 2022Dokument2 SeitenSwitchinng Theory and Logic Design July 2022drkhamuruddeenNoch keine Bewertungen

- P3G30 32 en M D004 Print IEC PDFDokument392 SeitenP3G30 32 en M D004 Print IEC PDFsureshbabum85Noch keine Bewertungen

- Multifunction Programmable Controller Installation and User Manual of The AC10 - AC20 - AC30 ControllerDokument210 SeitenMultifunction Programmable Controller Installation and User Manual of The AC10 - AC20 - AC30 ControllerSaddam MzaadNoch keine Bewertungen

- PIC16F84ADokument88 SeitenPIC16F84ASantosNoch keine Bewertungen

- Mini Project Report Format 1Dokument18 SeitenMini Project Report Format 1pallavi shindeNoch keine Bewertungen

- DLD Paper - 2 - SolutionDokument20 SeitenDLD Paper - 2 - Solutionsinner4everyoneNoch keine Bewertungen

- ePWM Sprug04aDokument13 SeitenePWM Sprug04aEduardo Calle100% (1)

- Latches and Flip-Flops: Building Blocks of Sequential CircuitsDokument7 SeitenLatches and Flip-Flops: Building Blocks of Sequential CircuitspresumidololoNoch keine Bewertungen

- APM PSRAM QSPI APS6404L SQRH v3 6 PKG-1954817Dokument26 SeitenAPM PSRAM QSPI APS6404L SQRH v3 6 PKG-1954817ManunoghiNoch keine Bewertungen