Beruflich Dokumente

Kultur Dokumente

+2.7V, Low-Power, 12-Bit Serial Adcs in 8-Pin So

Hochgeladen von

jnax101Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

+2.7V, Low-Power, 12-Bit Serial Adcs in 8-Pin So

Hochgeladen von

jnax101Copyright:

Verfügbare Formate

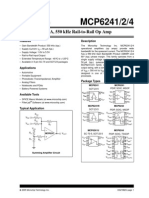

__________________General Desc ription

The M A X1240/M A X1241 are low -pow er, 12-bit analog-

to-digital converters (A D C s) available in 8-pin pack-

ages. The M A X1240 operates w ith a single + 2.7V to

+ 3.6V supply, and the M A X1241 operates w ith a single

+ 2.7V to + 5.25V supply. B oth devices feature a 7.5s

successive-ap p roxim ation A D C , a fast track/hold

(1.5s), an on-chip clock, and a high-speed, 3-w ire ser-

ial interface.

Pow er consum ption is only 37m W (V

D D

= 3V) at the

73ksps m axim um sam pling speed. A 2A shutdow n

m ode reduces pow er at slow er throughput rates.

The M A X1240 has an internal 2.5V reference, w hile the

M A X1241 requires an external reference. The M A X1241

accepts signals from 0V to V

R EF

, and the reference

input range includes the positive supply rail. A n exter-

nal clock accesses d ata from the 3-w ire interface,

w hich connects directly to standard m icrocontroller I/O

ports. The interface is com patible w ith SPI , Q SPI ,

and M icrow ire .

Excellent A C characteristics and very low pow er com -

bined w ith ease of use and sm all package size m ake

these converters ideal for rem ote-sensor and data-

acq uisition ap p lications, or for other circuits w ith

dem anding pow er consum ption and space require-

m ents. The M A X1240/M A X1241 are available in 8-pin

D IP and SO packages.

___________________________Applic ations

B attery-Pow ered System s

Portable D ata Logging

Isolated D ata A cquisition

Process C ontrol

Instrum entation

________________________________Features

o Single-Supply Operation:

+2.7V to +3.6V (MAX1240)

+2.7V to +5.25V (MAX1241)

o 12-Bit Resolution

o Internal 2.5V Reference (MAX1240)

o Small Footprint: 8-Pin DIP/SO Packages

o Low Power: 3.7W (73ksps, MAX1240)

3mW (73ksps, MAX1241)

66W (1ksps, MAX1241)

5W (power-down mode)

o Internal Track/Hold

o SPI/QSPI/Microwire 3-Wire Serial Interface

o Internal Clock

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

________________________________________________________________ Maxim Integrated Products 1

19-1155; R ev 1a; 9/97

SPI and Q SPI are tradem arks of M otorola, Inc. M icrow ire is a tradem ark of N ational Sem iconductor C orp.

Ordering Information continued at end of data sheet.

*D ice are specified at T

A

= +25C , D C param eters only.

TOP VIEW

1

2

3

4

8

7

6

5

SCLK

CS

DOUT

GND

REF

SHDN

AIN

V

DD

DIP/SO

MAX1240

MAX1241

__________________Pin Configuration

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800

For small orders, phone 408-737-7600 ext. 3468.

PART

MAX1240A C PA

M A X1240B C PA 0C to + 70C

0C to + 70C

TEMP. RANGE

PIN-

PACKAGE

8 Plastic D IP

8 Plastic D IP

INL

(LSB)

1

/2

1

M A X1240A C SA 0C to + 70C 8 SO

1

/2

M A X1240B C /D 0C to + 70C D ice* 1

_________________Ordering Information

EVALUATION KIT

AVAILABLE

M A X1240B C SA 0C to + 70C 8 SO 1

________________Func tional Diagram

7

AIN

T/ H

DOUT

6

1

OUTPUT

SHIFT

REGISTER

CONTROL

LOGIC

INT

CLOCK

12- BIT

SAR

8

2

3

5

REF

4

SHDN

2.5V REFERENCE

(MAX1240 ONLY)

GND

SCLK

CS

MAX1240

MAX1241

V

DD

M A X1240C C PA 0C to + 70C 8 Plastic D IP 1

M A X1240C C SA 0C to + 70C 8 SO 1

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

2 _______________________________________________________________________________________

ELECTRICAL CHARACTERISTICS

(V

D D

= + 2.7V to + 3.6V (M A X1240); V

D D

= + 2.7V to + 5.25V (M A X1241); 73ksps, f

SC LK

= 2.1M H z (50% duty cycle); M A X12404.7F

capacitor at R EF pin, M A X1241external reference; V

R EF

= 2.500V applied to R EF pin; T

A

= T

M IN

to T

M A X

; unless otherw ise noted.)

V

D D

to G N D .............................................................-0.3V to + 6V

A IN to G N D ................................................-0.3V to (V

D D

+ 0.3V)

R EF to G N D ...............................................-0.3V to (V

D D

+ 0.3V)

D igital Inputs to G N D ...............................................-0.3V to + 6V

D O U T to G N D ............................................-0.3V to (V

D D

+ 0.3V)

D O U T C urrent.................................................................. 25m A

C ontinuous Pow er D issipation (T

A

= + 70C )

Plastic D IP (derate 9.09m W /C above + 70C )...........727m W

SO (derate 5.88m W /C above + 70C )........................471m W

C ER D IP (derate 8.00m W /C above + 70C )................640m W

O perating Tem perature R anges

M A X1240_C _A /M A X1241_C _A .........................0C to + 70C

M A X1240_E_ A /M A X1241_E_ A .....................-40C to + 85C

M A X1240_M JA /M A X1241_M JA ...................-55C to + 125C

Storage Tem perature R ange............................-60C to + 150C

Lead Tem perature (soldering, 10sec)............................+ 300C

ABSOLUTE MAXIMUM RATINGS

Stresses beyond those listed under A bsolute M axim um R atingsm ay cause perm anent dam age to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not im plied. Exposure to

absolute m axim um rating conditions for extended periods m ay affect device reliability.

71.5 M A X124_C

Input Voltage R ange 0 V

R EF

V

Input C apacitance

A perture Jitter < 50 ps

16 pF

M A X124_A

M A X124_B /C

A perture D elay t

A PR

30 ns Figure 8

Track/H old A cquisition Tim e t

A C Q

1.5 s

Throughput R ate 73 ksps f

SC LK

= 2.1M H z

C onversion Tim e

PARAMETER SYMBOL MIN TYP MAX UNITS

0.5 3.0

O ffset Error LSB

D ifferential N onlinearity D N L 1 LSB

1.0

G ain Tem perature C oefficient

0.5 4.0

G ain Error (N ote 3) LSB 0.5 4.0

R esolution 12 B its

R elative A ccuracy (N ote 2) IN L

0.5

LSB

t

C O N V

5.5 7.5 s

Sm all-Signal B andw idth

Signal-to-N oise Plus

D istortion R atio

SIN A D

70

dB

2.25 M H z

Full-Pow er B andw idth

Total H arm onic D istortion TH D

-80

dB

1.0

-3dB rolloff

M H z

CONDITIONS

Spurious-Free D ynam ic R ange

ppm /C

N o m issing codes over tem perature

M A X124_B /C

0.25

SFD R

M A X124_A /B

80

U p to the 5th harm onic

dB

M A X124_A /B

M A X124_A

M A X124_A /B

M A X124_C -88

M A X124_C -88

ANALOG INPUT

CONVERSION RATE

DYNAMIC SPECIFICATIONS (10kH z sine-w ave input, 0V to 2.500Vp-p, 73ksps, f

SC LK

= 2.1M H z)

DC ACCURACY (N ote 1)

ppm /C

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

_______________________________________________________________________________________ 3

ELECTRICAL CHARACTERISTICS (continued)

(V

D D

= + 2.7V to + 3.6V (M A X1240); V

D D

= + 2.7V to + 5.25V (M A X1241); 73ksps, f

SC LK

= 2.1M H z (50% duty cycle); M A X12404.7F

capacitor at R EF pin, M A X1241external reference; V

R EF

= 2.500V applied to R EF pin; T

A

= T

M IN

to T

M A X

; unless otherw ise noted.)

V

IN

= 0V or V

D D

A

T

A

= + 25C

A 100 150

0.01 1 I

IN SC LK , CS Input Leakage

V 0.2

Input C urrent

CONDITIONS

SHDN = 0V A 0.01 10

V

H YST SC LK , CS Input H ysteresis

SHDN = 0V or V

D D

A

R EF Input C urrent in Shutdow n

k 18 25

4.0 SHDN Input C urrent

Input R esistance

V 0.4 V

SL SHDN Input Low Voltage

V

(N ote 5)

V

D D

- 0.4 V

SH SHDN Input H igh Voltage

pF 15 C

IN

V R EF O utput Voltage

SC LK , CS Input C apacitance

SHDN = float nA

SHDN = float

100

SHDN M ax A llow ed Leakage,

M id Input

V V

D D

/2 V

FLT SHDN Voltage, Floating

V 1.1 V

D D

- 1.1 V

SM SHDN Input M id Voltage

I

SIN K

= 5m A

UNITS MIN TYP MAX SYMBOL PARAMETER

V

0.4

V

O L

O utput Voltage Low

CS = V

D D

(N ote 5) pF 15 C

O U T

Three-State O utput C apacitance

CS = V

D D

A

I

SO U R C E

= 0.5m A

0.01 10 I

L

Three-State Leakage C urrent

V V

D D

- 0.5 V

O H

V

V

D D

3.6V

0.8 V

IL

F 0.1 C apacitive B ypass at R EF

SC LK , CS Input Low Voltage

V

2.0

V

IH SC LK , CS Input H igh Voltage

O utput Voltage H igh

I

SIN K

= 16m A

V

D D

> 3.6V (M A X1241)

0.8

3.0

2.480 2.500 2.520

V Input Voltage R ange 1.00

V

D D

+

50m V

M A X1240A C /B C

ppm /C R EF Tem perature C oefficient

30 50

R EF Short-C ircuit C urrent 30

M A X1240A E/B E 30 60

M A X1240A M /B M 30 80

0m A to 0.2m A output load Load R egulation (N ote 4) 0.35

m A

F C apacitive B ypass at R EF 4.7

M A X1240C 30

DIGITAL OUTPUT: DOUT

DIGITAL INPUTS: SCLK, CS, SHDN

EXTERNAL REFERENCE (V

R EF

= 2.500V)

INTERNAL REFERENCE (M A X1240 only)

V

D D

= 3.6V

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

4 _______________________________________________________________________________________

ELECTRICAL CHARACTERISTICS (continued)

(V

D D

= + 2.7V to + 3.6V (M A X1240); V

D D

= + 2.7V to + 5.25V (M A X1241); 73ksps, f

SC LK

= 2.1M H z (50% duty cycle); M A X12404.7F

capacitor at R EF pin, M A X1241external reference; V

R EF

= 2.500V applied to R EF pin; T

A

= T

M IN

to T

M A X

; unless otherw ise noted.)

Note 1: Tested at V

D D

= + 2.7V.

Note 2: R elative accuracy is the deviation of the analog value at any code from its theoretical value after the full-scale range and

offset have been calibrated.

Note 3: M A X1240internal reference, offset nulled; M A X1241external reference (V

R EF

= + 2.500V), offset nulled.

Note 4: External load should not change during conversion for specified accuracy.

Note 5: G uaranteed by design. N ot subject to production testing.

Note 6: M easured as [V

FS

(2.7V) - V

FS

(V

D D (M A X

)].

Note 7: To guarantee acquisition tim e, t

A C Q

is the m axim um tim e the device takes to acquire the signal, and is also the m inim um

tim e needed for the signal to be acquired.

SC LK Pulse W idth Low t

C L

200 ns

SC LK Pulse W idth H igh t

C H

200 ns

SC LK C lock Frequency f

SC LK

0 2.1 M H z

CS R ise to O utput D isable t

TR

240 ns

SC LK Low to CS Fall Setup Tim e t

C S0

50 ns

D O U T Rise to SC LK Rise (N ote 5) t

STR

0 ns

CS Pulse W idth t

C S

240 ns

Figure 2, C

LO A D

= 50pF

CS Fall to O utput Enable t

D V

240 ns Figure 1, C

LO A D

= 50pF

PARAMETERS SYMBOL MIN TYP MAX UNITS CONDITIONS

A cquisition Tim e t

A C Q

1.5 s CS = V

D D

(N ote 6)

TIMING CHARACTERISTICS (Figure 8)

(V

D D

= + 2.7V to + 3.6V (M A X1240); V

D D

= + 2.7V to + 5.25V (M A X1241); T

A

= T

M IN

to T

M A X

, unless otherw ise noted.)

PARAMETERS SYMBOL MIN TYP MAX UNITS CONDITIONS

2.7 3.6 M A X1240

2.7 5.25 M A X1241

V

D D

Supply Voltage V

0.3 (N ote 5) PSR Supply R ejection m V

20 240

SC LK Fall to O utput D ata Valid t

D O

20 200

ns

Figure 1,

C

LO A D

= 50pF

M A X124_ _C /E

M A X124_ _M

1.4 2.0

O perating

m ode

1.6 2.5

V

D D

= 3.6V

3.5 15

V

D D

= 5.25V

V

D D

= 3.6V

V

D D

= 5.25V

I

D D

1.9 10

Pow er-dow n, digital inputs

at 0V or V

D D

1.4 3.5

A

0.9 1.5

V

D D

= 3.6V

M A X1240C

M A X1241A /B

Supply C urrent

M A X1240A /B

m A

1.6 3.8

V

D D

= 3.6V

V

D D

= 5.25V

0.9 2.8

M A X1241C

POWER REQUIREMENTS

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

_______________________________________________________________________________________ 5

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

0.9

1.0

2.25 2.75 3.25 3.75 4.25 4.75 5.25

OFFSET ERROR

vs. SUPPLY VOLTAGE

M

A

X

1

2

4

1

-

0

3

SUPPLY VOLTAGE (V)

O

F

F

S

E

T

E

R

R

O

R

(

L

S

B

)

__________________________________________Typic al Operating Charac teristic s

(V

D D

= 3.0V, V

R EF

= 2.5V, f

SC LK

= 2.1M H z, C

L

= 20pF, T

A

= + 25C , unless otherw ise noted.)

0

0.2

0.4

0.6

0.8

1.0

1.2

1.4

1.6

1.8

2.0

2 4 3 5 6

OPERATING SUPPLY CURRENT

vs. SUPPLY VOLTAGE

M

A

X

1

2

4

1

-

D

SUPPLY VOLTAGE (V)

O

P

E

R

A

T

I

N

G

S

U

P

P

L

Y

C

U

R

R

E

N

T

(

m

A

)

R

L

=

CODE = 101010100000

MAX1241

MAX1240

0.8

0.9

1.0

1.1

1.2

1.3

- 60 - 20 20 60 100 140

SUPPLY CURRENT vs. TEMPERATURE

TEMPERATURE (C)

S

U

P

P

L

Y

C

U

R

R

E

N

T

(

m

A

)

M

A

X

1

2

4

1

-

A

/N

E

W

MAX1241

MAX1240

R

LOAD

=

CODE = 10101010000

DOUT DOUT

6k

DGND

C

LOAD

= 50pF C

LOAD

= 50pF

6k

DGND

+2.7V

b) Hi gh- Z to V

OL

and V

OH

to V

OL

a) Hi gh- Z to V

OH

and V

OL

to V

OH

Figure 1. Load C ircuits for D O U T Enable Tim e

DOUT DOUT

6k

DGND

C

LOAD

= 50pF C

LOAD

= 50pF

6k

DGND

+2.7V

b) V

OL

to Hi gh- Z a) V

OH

to Hi gh- Z

Figure 2. Load C ircuits for D O U T D isable Tim e

2.494

2.495

2.496

2.497

2.498

2.499

2.500

2.501

- 60 - 20 20 60 100 140

MAX1240

INTERNAL REFERENCE VOLTAGE

vs. TEMPERATURE

TEMPERATURE (C)

V

R

E

F

(

V

)

M

A

X

1

2

4

1

-

0

Y

V

DD

= 2.7V

V

DD

= 3.6V

0

0.4

0.2

0.8

0.6

1.0

1.2

2.25 3.25 3.75 2.75 4.25 4.75 5.25

INTEGRAL NONLINEARITY

vs. SUPPLY VOLTAGE

M

A

X

1

2

4

1

-

0

9

/N

E

W

SUPPLY VOLTAGE (V)

I

N

L

(

L

S

B

)

MAX1240

MAX1241

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

6 _______________________________________________________________________________________

____________________________Typic al Operating Charac teristic s (c ontinued)

(V

D D

= 3.0V, V

R EF

= 2.5V, f

SC LK

= 2.1M H z, C

L

= 20pF, T

A

= + 25C , unless otherw ise noted.)

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

2.25 2.75 3.25 3.75 4.25 4.75 5.25

GAIN ERROR

vs. SUPPLY VOLTAGE

M

A

X

1

2

4

1

-

0

7

SUPPLY VOLTAGE (V)

G

A

I

N

E

R

R

O

R

(

L

S

B

)

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

- 55 - 30 - 5 20 45 70 145 120 95

GAIN ERROR

vs. TEMPERATURE

M

A

X

1

2

4

1

-

0

8

TEMPERATURE (C)

G

A

I

N

E

R

R

O

R

(

L

S

B

)

V

DD

= 2.7V

2.5020

2.4990

2.25 2.75

MAX1240

INTERNAL REFERENCE VOLTAGE

vs. SUPPLY VOLTAGE

2.5015

2.5005

2.5010

2.5000

2.4995

V

DD

(V)

V

R

E

F

(

V

)

3.75 5.25 3.25 4.25 4.75

M

A

X

1

2

4

1

-

0

X

0

0.5

1.0

1.5

2.0

2.5

3.0

3.5

4.0

4.5

5.0

- 60 - 20 20 60 100 140

SHUTDOWN SUPPLY CURRENT

vs. TEMPERATURE

M

A

X

1

2

4

1

-

B

TEMPERATURE (C)

S

H

U

T

D

O

W

N

S

U

P

P

L

Y

C

U

R

R

E

N

T

(

A

)

0

0.1

0.2

0.3

0.4

0.5

0.6

0.7

0.8

- 55 - 30 - 5 20 45 70 95 120 145

OFFSET ERROR vs. TEMPERATURE

M

A

X

1

2

4

1

-

0

6

TEMPERATURE (C)

O

F

F

S

E

T

E

R

R

O

R

(

L

S

B

)

V

DD

= 2.7V

4.0

3.5

0

2.25 2.75

SHUTDOWN SUPPLY CURRENT

vs. SUPPLY VOLTAGE

3.0

2.5

1.5

2.0

1.0

0.5

SUPPLY VOLTAGE (V)

S

H

U

T

D

O

W

N

S

U

P

P

L

Y

C

U

R

R

E

N

T

(

A

)

3.75 5.25 3.25 4.25 4.75

M

A

X

1

2

4

1

-

C

/N

E

W

0

0.6

0.4

0.2

0.8

1.0

1.2

- 60 20 0 - 40 - 20 40 60 80 100 120 140

INTEGRAL NONLINEARITY

vs. TEMPERATURE

M

A

X

1

2

4

1

-

1

0

/N

E

W

TEMPERATURE (C)

I

N

L

(

L

S

B

)

V

DD

= 2.7V

MAX1240

MAX1241

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

_______________________________________________________________________________________ 7

_______________________________________________________________________Pin Desc ription

6 D O U T

Serial D ata O utput. D ata changes state at SC LK s falling edge. D O U T is high im pedance w hen CS is

high.

8 SC LK

3 SHDN

Three-Level Shutdow n Input. Pulling SHDN low shuts the M A X1240/M A X1241 dow n to 15A (m ax)

supply current. B oth the M A X1240 and M A X1241 are fully operational w ith either SHDN high or float-

ing. For the M A X1240, pulling SHDN high enables the internal reference, and letting SHDN float dis-

ables the internal reference and allow s for the use of an external reference.

4 R EF

R eference Voltage for A nalog-to-D igital C onversion. Internal 2.5V reference output for M A X1240;

bypass w ith 4.7F capacitor. External reference voltage input for M A X1241, or for M A X1240 w ith the

internal reference disabled. B ypass R EF w ith a m inim um of 0.1F w hen using an external reference.

7 CS

A ctive-Low C hip Select initiates conversions on the falling edge. W hen CS is high, D O U T is high

im pedance.

5 G N D A nalog and D igital G round

2 A IN Sam pling A nalog Input, 0V to V

R EF

range

NAME FUNCTION

1 V

D D

Positive Supply Voltage: 2.7V to 3.6V, (M A X1240); 2.7 to 5.25V (M A X1241)

PIN

Serial C lock Input. SC LK clocks data out at rates up to 2.1M H z.

0.6

INTEGRAL NONLINEARITY

vs. CODE

- 0.6

0

- 0.2

- 0.4

0.4

0.2

M

A

X

1

2

4

1

-

1

1

A

/N

E

W

I

N

L

(

L

S

B

)

CODE

1024 2048 3072 4096 0

20

- 140

0 37.50

FFT PLOT

- 120

0

- 80

- 100

- 40

- 20

- 60

18.75

A

M

P

L

I

T

U

D

E

(

d

B

)

FREQUENCY (kHz)

f

AIN

= 10kHz, 2.5Vp- p

f

SAMPLE

= 73ksps

M

A

X

1

2

4

1

-

T

O

C

1

2

A

____________________________Typic al Operating Charac teristic s (c ontinued)

(V

D D

= 3.0V, R EF = 2.5V, f

SC LK

= 2.1M H z, C

L

= 20pF, T

A

= + 25C , unless otherw ise noted.)

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

8 _______________________________________________________________________________________

_______________Detailed Desc ription

Converter Operation

The M A X1240/M A X1241 use an input track/hold (T/H )

and successive-approxim ation register (SA R ) circuitry

to convert an analog input signal to a digital 12-bit out-

put. N o external-hold capacitor is needed for the T/H .

Figure 3 show s the M A X1240/M A X1241 in its sim plest

configuration. The M A X1240/M A X1241 convert input

signals in the 0V to V

R EF

range in 9s, including T/H

acquisition tim e. The M A X1240s internal reference is

trim m ed to 2.5V, w hile the M A X1241 requires an external

reference. B oth devices accept voltages from 1.0V to

V

D D

. The serial interface requires only three digital lines

(SC LK , CS, and D O U T) and provides an easy interface

to m icroprocessors (Ps).

The M A X1240/M A X1241 have tw o m odes: norm al and

shutdow n. Pulling SHDN low shuts the device dow n and

reduces supply current below 10A (V

D D

3.6V), w hile

pulling SHDN high or leaving it open puts the device

into operational m ode. Pulling CS low initiates a conver-

sion. The conversion result is available at D O U T in

unipolar serial form at. The serial data stream consists

of a high bit, signaling the end of conversion (EO C ), fol-

low ed by the data bits (M SB first).

Analog Input

Figure 4 illustrates the sam pling architecture of the ana-

log-to-digital converters (A D C s) com parator. The full-

scale input voltage is set by the voltage at R EF.

Track/Hold

In track m ode, the analog signal is acquired and stored

in the internal hold capacitor. In hold m ode, the T/H

sw itch opens and m aintains a constant input to the

A D C s SA R section.

D uring acquisition, the analog input (A IN ) charges

capacitor C

H O LD

. B ringing CS low ends the acquisition

interval. A t this instant, the T/H sw itches the input side

of C

H O LD

to G N D . The retained charge on C

H O LD

repre-

sents a sam ple of the input, unbalancing node ZER O at

the com parators input.

In hold m ode, the capacitive digital-to-analog converter

(D A C ) adjusts during the rem ainder of the conversion

cycle to restore node ZER O to 0V w ithin the lim its of 12-

bit resolution. This action is equivalent to transferring a

charge from C

H O LD

to the binary-w eighted capacitive

D A C , w hich in turn form s a digital representation of the

analog input signal. A t the conversions end, the input

sid e of C

H O LD

sw itches b ack to A IN , and C

H O LD

charges to the input signal again.

The tim e required for the T/H to acquire an input signal

is a function of how quickly its input capacitance is

charged. If the input signals source im pedance is high,

the acquisition tim e lengthens and m ore tim e m ust be

allow ed betw een conversions. The acquisition tim e

(t

A C Q

) is the m axim um tim e the device takes to acquire

the signal, and is also the m inim um tim e needed for the

signal to be acquired. A cquisition tim e is calculated by:

t

A C Q

= 9(R

S

+ R

IN

) x 16pF

w here R

IN

= 9k, R

S

= the input signals source im ped-

ance, and t

A C Q

is never less than 1.5s. Source im ped-

ances below 1k do not significantly affect the A D C s

A C perform ance.

AIN

TRACK

INPUT

HOLD

GND

TRACK

HOLD

9k

R

IN

C

HOLD

16pF

- +

C

SWITCH

COMPARATOR

ZERO

REF

12- BIT CAPACITIVE DAC

AT THE SAMPLING INSTANT,

THE INPUT SWITCHES FROM

AIN TO GND.

SHUTDOWN

INPUT

ANALOG INPUT

0V TO V

REF

+2.7V to +3.6V* *

* *

V

DD,MAX

= +5.25V (MAX1241)

4.7F (MAX1240)

0.1F (MAX1241)

1

2

3

4

V

DD

AIN

SHDN

REF

8

7

6

5

SCLK

CS

DOUT

GND

SERIAL

INTERFACE

C* *

4.7F 0.1F

REFERENCE

INPUT

(MAX1241 ONLY)

MAX1240

MAX1241

Figure 3. O perational D iagram Figure 4. Equivalent Input C ircuit

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

_______________________________________________________________________________________ 9

H igher source im pedances can be used if a 0.01F

capacitor is connected to the analog input. N ote that

the input capacitor form s an R C filter w ith the input

source im p ed ance, lim iting the A D C s input signal

bandw idth.

Input Bandwidth

The A D C sinput tracking circuitry has a 2.25M H z sm all-

signal bandw idth, so it is possible to digitize high-

speed transient events and m easure periodic signals

w ith bandw idths exceeding the A D C s sam pling rate by

using undersam pling techniques. To avoid aliasing of

unw anted high-frequency signals into the frequency

band of interest, anti-alias filtering is recom m ended.

Analog Input Protection

Internal protection diodes, w hich clam p the analog

input to V

D D

and G N D , allow the input to sw ing from

G N D - 0.3V to V

D D

+ 0.3V w ithout dam age. H ow ever,

for accurate conversions near full scale, the input m ust

not exceed V

D D

by m ore than 50m V, or be low er than

G N D by 50m V.

If the analog input exceeds 50mV beyond the sup-

plies, limit the input current to 2mA.

Internal Reference (MAX1240)

The M A X 1240 has an on-chip voltag e reference

trim m ed to 2.5V. The internal reference output is con-

nected to R EF and also drives the internal capacitive

D A C . The output can be used as a reference voltage

source for other com ponents and can source up to

400A . B ypass R EF w ith a 4.7F capacitor. Larger

capacitors increase w ake-up tim e w hen exiting shut-

dow n (see the section U sing SHDN to R educe Supply

C urrent). The internal reference is enabled by pulling the

SHDN pin high. Letting SHDN float disables the internal

reference, w hich allow s the use of an external reference,

as described in the External R eference section.

External Reference

The M A X1240/M A X1241 operate w ith an external refer-

ence at the R EF pin. To use the M A X1240 w ith an

external reference, disable the internal reference by let-

ting SHDN float. Stay w ithin the + 1.0V to V

D D

voltage

range to achieve specified accuracy. The m inim um

input im pedance is 18k for D C currents. D uring con-

version, the external reference m ust be able to deliver

up to 250A of D C load current and have an output

im pedance of 10 or less. The recom m ended m ini-

m um value for the bypass capacitor is 0.1F. If the ref-

erence has hig her outp ut im p ed ance or is noisy,

bypass it close to the R EF pin w ith a 4.7F capacitor.

____________________Serial Interfac e

Initialization after Power-Up and

Starting a Conversion

W hen pow er is first applied, and if SHDN is not pulled

low , it takes the fully d ischarg ed 4.7F reference

bypass capacitor up to 20m s to provide adequate

charge for specified accuracy. W ith an external refer-

ence, the internal reset tim e is 10s after the pow er

supplies have stabilized. N o conversions should be

perform ed during these tim es.

To start a conversion, pull CS low . A t CSs falling edge,

the T/H enters its hold m ode and a conversion is initiat-

COMPLETE CONVERSION SEQUENCE

t

WAKE

POWERED UP POWERED DOWN POWERED UP

CONVERSION 0 CONVERSION 1

DOUT

CS

SHDN

Figure 5. Shutdow n Sequence

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

10 ______________________________________________________________________________________

ed. A fter an internally tim ed conversion period, the end

of conversion is signaled by D O U T pulling high. D ata

can then be shifted out serially w ith the external clock.

Using SHDN to Reduc e Supply Current

Pow er consum ption can be reduced significantly by

shutting dow n the M A X1240/M A X1241 betw een con-

versions. Figure 6 show s a plot of average supply cur-

rent versus conversion rate. B ecause the M A X1241

uses an external reference voltage (assum ed to be pre-

sent continuously), it w akes upfrom shutdow n m ore

quickly (in 4s) and therefore provides low er average

supply currents. The w ake-up tim e (t

W A K E

) is the tim e

from w hen SHDN is deasserted to the tim e w hen a con-

version m ay be initiated (Figure 5). For the M A X1240,

this tim e depends on the tim e in shutdow n (Figure 7)

because the external 4.7F reference bypass capacitor

loses charge slow ly during shutdow n.

External Cloc k

The actual conversion does not require the external

clock. This allow s the conversion result to be read back

at the Ps convenience at any clock rate from up to

2.1M H z. The clock duty cycle is unrestricted if each

clock phase is at least 200ns. D o not run the clock

w hile a conversion is in progress.

Timing and Control

C onversion-start and data-read operations are controlled

by the CS and SC LK digital inputs. The tim ing diagram s

of Figures 8 and 9 outline serial-interface operation.

A CS falling edge initiates a conversion sequence: the

T/H stage holds the input voltage, the A D C begins to

convert, and D O U T changes from high im pedance to

logic low . SC LK m ust be kept low during the conver-

sion. A n internal register stores the data w hen the con-

version is in progress.

10

1

0.01

0.001

0.1 1 10 100 1k 10k 100k

0.1

CONVERSION RATE (Hz)

S

U

P

P

L

Y

C

U

R

R

N

E

T

(

m

A

)

V

DD

=

V

REF

= 3.0V

R

LOAD

= , C

LOAD

= 50pF

CODE = 010101010000

M

A

X

1

2

4

1

F

IG

. 0

6

a

MAX1241

MAX1240

Figure 6. A verage Supply C urrent vs. C onversion R ate

1.0

0.0

0.001 0.01 0.1 1 10

0.8

0.6

0.4

0.2

TIME IN SHUTDOWN

(sec)

P

O

W

E

R

-

U

P

D

E

L

A

Y

(

m

s

)

M

A

X

1

2

4

0

/4

1

-

0

7

a

Figure 7. Typicae R eference Pow er-U p D elay vs. Tim e in

Shutdow n

EOC

INTERFACE IDLE

CONVERSION

IN PROGRESS

EOC

0s

TRAILING

ZEROS

IDLE CLOCK OUT SERIAL DATA

TRACK/ HOLD

STATE TRACK HOLD TRACK

DOUT B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0

SCLK

1 4 8 12 16

7.5s (t

CONV

)

HOLD

0s

(t

CS

)

TOTAL = 13.7s

12.5 0.476s = 5.95s

CYCLE TIME

CS

0.24s

Figure 8. Interface Tim ing Sequence

End of conversion (EO C ) is signaled by D O U T going

high. D O U Ts rising edge can be used as a fram ing

signal. SC LK shifts the data out of this register any tim e

after the conversion is com plete. D O U T transitions on

SC LK s falling edge. The next falling clock edge pro-

duces the M SB of the conversion at D O U T, follow ed by

the rem aining bits. Since there are 12 data bits and one

leading high bit, at least 13 falling clock edges are

needed to shift out these bits. Extra clock pulses occur-

ring after the conversion result has been clocked out,

and prior to a rising edge of CS, produce trailing zeros

at D O U T and have no effect on converter operation.

M inim um cycle tim e is accom plished by using D O U Ts

rising edge as the EO C signal. C lock out the data w ith

12.5 clock cycles at full speed. Pull CS high after read-

ing the conversions LSB . A fter the specified m inim um

tim e (t

C S

), CS can be pulled low again to initiate the

next conversion.

Output Coding and Transfer Func tion

The data output from the M A X1240/M A X1241 is binary,

and Figure 10 depicts the nom inal transfer function.

C ode transitions occur halfw ay betw een successive-

integer LSB values. If V

R EF

= + 2.500V, then 1 LSB =

610V or 2.500V/4096.

____________Applic ations Information

Connec tion to Standard Interfac es

The M A X1240/M A X1241 serial interface is fully com pat-

ible w ith SPI/Q SPI and M icrow ire standard serial inter-

faces (Figure 11).

If a serial interface is available, set the C PU s serial

interface in m aster m ode so the C PU generates the ser-

ial clock. C hoose a clock frequency up to 2.1M H z.

1) U se a general-purpose I/O line on the C PU to pull CS

low . K eep SC LK low .

2) W ait the for the m axim um conversion tim e specified

before activating SC LK . A lternatively, look for a D O U T

rising edge to determ ine the end of conversion.

3) A ctivate SC LK for a m inim um of 13 clock cycles. The

first falling clock edge produces the M SB of the

D O U T conversion. D O U T output data transitions on

SC LK s falling edge and is available in M SB -first for-

m at. O bserve the SC LK to D O U T valid tim ing char-

acteristic. D ata can b e clocked into the P on

SC LK s rising edge.

4) Pull CS high at or after the 13th falling clock edge. If

CS rem ains low , trailing zeros are clocked out after

the LSB .

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

______________________________________________________________________________________ 11

11111

11110

11101

00011

00010

00001

00000

0 1 2 FS

OUTPUT CODE

FS - 3/ 2LSB INPUT VOLTAGE (LSBs)

FS = V

REF

- 1LSB

1LSB =

V

REF

4096

FULL- SCALE

TRANSITION

3

CS

SCLK

DOUT

INTERNAL

T/ H

(TRACK/ ACQUIRE)

t

CS0

t

CONV

t

DV

t

APR

t

STR

(HOLD) (TRACK/ ACQUIRE)

B2 B1 B0

t

CH

t

DO

t

CL t

TR

t

CS

Figure 10. U nipolar Transfer Function, Full Scale (FS) = V

R EF

-

1LSB , Zero Scale (ZS) = G N D

Figure 9. D etailed Serial-Interface Tim ing

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

12 ______________________________________________________________________________________

5) W ith CS = high, w ait the m inim um specified tim e, tC S,

before initiating a new conversion by pulling CS low .

If a conversion is aborted by pulling CS high before

the conversions end, w ait for the m inim um acquisi-

tion tim e, t

A C Q

, before starting a new conversion.

CS m ust be held low until all data bits are clocked out.

D ata can be output in tw o bytes or continuously, as

show n in Figure 8. The bytes contain the result of the

conversion padded w ith one leading 1, and trailing 0s.

SPI and Mic rowire

W hen using SPI or Q SPI, set C PO L = 0 and C PH A = 0.

C onversion begins w ith a CS falling edge. D O U T goes

low , indicating a conversion in progress. W ait until D O U T

goes high or until the m axim um specified 7.5s conver-

sion tim e elapses. Tw o consecutive 1-byte reads are

required to get the full 12 bits from the A D C . D O U T out-

p ut d ata transitions on S C LK s falling ed g e and is

clocked into the P on SC LK s rising edge.

The first byte contains a leading 1, and seven bits of con-

version result. The second byte contains the rem aining

five bits and three trailing zeros. See Figure 11 for con-

nections and Figure 12 for tim ing.

QSPI

Set C PO L = C PH A = 0. U nlike SPI, w hich requires tw o

1-byte reads to acquire the 12 bits of data from the A D C ,

Q SPI allow s the m inim um num ber of clock cycles neces-

sary to clock in the d ata. The M A X 1240/M A X 1241

requires 13 clock cycles from the P to clock out the 12

bits of data w ith no trailing zeros (Figure 13). The m axi-

m um clock frequency to ensure com patibility w ith Q SPI is

2.097M H z.

Layout, Grounding, and Bypassing

For best perform ance, use printed circuit boards. W ire-

w rap boards are not recom m ended. B oard layout should

ensure that digital and analog signal lines are separated

from each other. D o not run analog and digital (especially

clock) lines parallel to one another, or digital lines under-

neath the A D C package.

Figure 14 show s the recom m ended system ground con-

nections. Establish a single-point analog ground (star

ground point) at G N D , separate from the logic ground.

C onnect all other analog grounds and D G N D to this star

ground point for further noise reduction. N o other digital

system ground should be connected to this single-point

analog ground. The ground return to the pow er supply for

this ground should be low im pedance and as short as

possible for noise-free operation.

H igh-frequency noise in the V

D D

pow er supply m ay affect

the A D C s high-speed com parator. B ypass this supply to

the single-point analog ground w ith 0.1F and 4.7F

bypass capacitors. M inim ize capacitor lead lengths for

best supply-noise rejection. If the pow er supply is very

noisy, a 10 resistor can be connected as a low pass filter

to attenuate supply noise (Figure 14).

CS

SCLK

DOUT

I/ O

SCK

MISO

+3V

SS

a) SPI

CS

SCLK

DOUT

CS

SCK

MISO

+3V

SS

b) QSPI

MAX1240

MAX1241

MAX1240

MAX1241

MAX1240

MAX1241

CS

SCLK

DOUT

I/ O

SK

SI

c) MICROWIRE

Figure 11. C om m on Serial-Interface C onnections to the

M A X1241

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

______________________________________________________________________________________ 13

HIGH- Z

D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

t

CONV

DOUT*

CS

SCLK

1ST BYTE READ 2ND BYTE READ

EOC

MSB LSB

* WHEN CS IS HIGH, DOUT = HIGH - Z

D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

t

CONV

DOUT*

CS

SCLK

EOC

MSB LSB

HIGH- Z

* WHEN CS IS HIGH, DOUT = HIGH - Z

Figure 12. SPI/M icrow ire Serial Interface Tim ing (C PO L = C PH A = 0)

Figure 13. Q SPI Serial Interface Tim ing (C PO L = C PH A = 0)

SUPPLIES

+3V +3V GND

DGND +3V

DIGITAL

CIRCUITRY

GND V

DD

MAX1240

MAX1241

* OPTIONAL

R* = 10

4.7F

0.1F

Figure 14. Pow er-Supply G rounding C ondition

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

14 ______________________________________________________________________________________

PART

M A X1240A EPA

M A X1240B ESA

M A X1240B M JA -55C to + 125C

-40C to + 85C

-40C to + 85C

TEMP. RANGE

PIN-

PACKAGE

8 Plastic D IP

8 SO

8 C ER D IP**

M A X1241A EPA -40C to + 85C 8 Plastic D IP

1

/2

M A X1241B EPA -40C to + 85C 8 Plastic D IP 1

M A X1241A ESA -40C to + 85C 8 SO

1

/2

M A X1241B ESA -40C to + 85C 8 SO

INL

(LSB)

1

/2

1

1

1

M A X1241A M JA -55C to + 125C 8 C ER D IP**

1

/2

M A X1241B M JA -55C to + 125C 8 C ER D IP** 1

M A X1240A M JA -55C to + 125C 8 C ER D IP**

1

/2

M A X1241B C /D 0C to + 70C D ice* 1

* D ice are specified at T

A

= +25C , D C param eters only.

**C ontact factory for availability and processing to M IL-STD -883.

__Ordering Information (c ontinued)

___________________Chip Information

TR A N SISTO R C O U N T: 2558

SU B STR A TE C O N N EC TED TO G N D

MAX1241A C PA

M A X1241B C PA

M A X1241B C SA 0C to + 70C

0C to + 70C

0C to + 70C 8 Plastic D IP

8 Plastic D IP

8 SO

1

/2

1

1

M A X1241A C SA 0C to + 70C 8 SO

1

/2

M A X1240A ESA -40C to + 85C 8 SO

1

/2

M A X1240B EPA -40C to + 85C 8 Plastic D IP 1

M A X1240C EPA -40C to + 85C 8 Plastic D IP 1

M A X1240C ESA -40C to + 85C 8 SO 1

M A X1240C M JA -55C to + 125C 8 C ER D IP** 1

M A X1241C C PA 0C to + 70C 8 Plastic D IP 1

M A X1241C C SA 0C to + 70C 8 SO 1

M A X1241C EPA -40C to + 85C 8 Plastic D IP 1

M A X1241C ESA -40C to + 85C 8 SO 1

M A X1241C M JA -55C to + 125C 8 C ER D IP** 1

S

O

IC

N

.E

P

S

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

______________________________________________________________________________________ 15

________________________________________________________Pac kage Information

P

D

IP

N

.E

P

S

M

A

X

1

2

4

0

/

M

A

X

1

2

4

1

+2.7V, Low-Power,

12-Bit Serial ADCs in 8-Pin SO

M axim cannot assum e responsibility for use of any circuitry other than circuitry entirely em bodied in a M axim product. N o circuit patent licenses are

im plied. M axim reserves the right to change the circuitry and specifications w ithout notice at any tim e.

16 ____________________Maxim Integrated Produc ts, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

1997 M axim Integrated Products Printed U SA is a registered tradem ark of M axim Integrated Products.

___________________________________________Pac kage Information (c ontinued)

C

D

IP

S

.E

P

S

Das könnte Ihnen auch gefallen

- Squeezing Unity - Unite 2017Dokument124 SeitenSqueezing Unity - Unite 2017carmatijaNoch keine Bewertungen

- SOC 2 Checklist FinalDokument6 SeitenSOC 2 Checklist FinalEntchenNoch keine Bewertungen

- MCP 3201Dokument28 SeitenMCP 3201Nacer MezghicheNoch keine Bewertungen

- 2.7V Dual Channel 12-Bit A/D Converter With SPI Serial InterfaceDokument34 Seiten2.7V Dual Channel 12-Bit A/D Converter With SPI Serial InterfaceManjunatha Ac100% (1)

- MCP3202 PDFDokument28 SeitenMCP3202 PDFblue11111Noch keine Bewertungen

- Low-Cost, Triple, 8-Bit Voltage-Output Dacs With Serial InterfaceDokument16 SeitenLow-Cost, Triple, 8-Bit Voltage-Output Dacs With Serial InterfaceBboubrahim BbnnNoch keine Bewertungen

- +3 Volt, Serial Input Complete 12-Bit DAC AD8300Dokument8 Seiten+3 Volt, Serial Input Complete 12-Bit DAC AD8300jnax101Noch keine Bewertungen

- Ad 7524Dokument8 SeitenAd 7524Giovanny ContrerasNoch keine Bewertungen

- 2.5V To 6.0V Micropower CMOS Op Amp: FeaturesDokument42 Seiten2.5V To 6.0V Micropower CMOS Op Amp: Featuresinside121Noch keine Bewertungen

- Microchip TC962 DatasheetDokument13 SeitenMicrochip TC962 DatasheetCale McColloughNoch keine Bewertungen

- Integrated Circuit True RMS-to-DC Converter: C To +125 C Operation (AD536AS)Dokument8 SeitenIntegrated Circuit True RMS-to-DC Converter: C To +125 C Operation (AD536AS)Decker JamesNoch keine Bewertungen

- LCD Inverter Sumida NotebookDokument16 SeitenLCD Inverter Sumida NotebookIlie DragutaNoch keine Bewertungen

- MCP3040 DatasheetDokument40 SeitenMCP3040 Datasheetjiajun898Noch keine Bewertungen

- Datasheet - AX5312 12-Bit 10 12 15V DAC MAX5312Dokument19 SeitenDatasheet - AX5312 12-Bit 10 12 15V DAC MAX5312carrubaNoch keine Bewertungen

- DAC0800/DAC0802 8-Bit Digital-to-Analog Converters: General DescriptionDokument0 SeitenDAC0800/DAC0802 8-Bit Digital-to-Analog Converters: General DescriptionMiguel Angel García ValerioNoch keine Bewertungen

- General Description Features: Bipolar/CMOS/DMOSDokument13 SeitenGeneral Description Features: Bipolar/CMOS/DMOSjavierrincon800Noch keine Bewertungen

- CN0350Dokument7 SeitenCN0350Narayan ApteNoch keine Bewertungen

- Voltage-Controlled Oscillator: ... The Analog Plus CompanyDokument24 SeitenVoltage-Controlled Oscillator: ... The Analog Plus CompanyMoltrevNoch keine Bewertungen

- LM3530 High Efficiency White LED Driver With Programmable Ambient Light Sensing Capability and I C-Compatible InterfaceDokument45 SeitenLM3530 High Efficiency White LED Driver With Programmable Ambient Light Sensing Capability and I C-Compatible Interfacethoth2487Noch keine Bewertungen

- DAC0800/DAC0802 8-Bit Digital-to-Analog Converters: Features DescriptionDokument21 SeitenDAC0800/DAC0802 8-Bit Digital-to-Analog Converters: Features DescriptionRaul CruzNoch keine Bewertungen

- 2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI™ Serial InterfaceDokument20 Seiten2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI™ Serial Interfacejoseleomi_limaNoch keine Bewertungen

- 12-Bit ADC AD1674Dokument12 Seiten12-Bit ADC AD1674anjanbsNoch keine Bewertungen

- Low-Power, Single-Channel 22-Bit Delta-Sigma Adcs: Features DescriptionDokument36 SeitenLow-Power, Single-Channel 22-Bit Delta-Sigma Adcs: Features Descriptionikaro181083Noch keine Bewertungen

- AFT05MP075NDokument21 SeitenAFT05MP075NjeremyAW2SNoch keine Bewertungen

- Max127 Max128bDokument16 SeitenMax127 Max128bwhynot05Noch keine Bewertungen

- DS26LS32C/DS26LS32M/DS26LS32AC/DS26LS33C/ DS26LS33M/DS26LS33AC Quad Differential Line ReceiversDokument8 SeitenDS26LS32C/DS26LS32M/DS26LS32AC/DS26LS33C/ DS26LS33M/DS26LS33AC Quad Differential Line Receiversjnax101Noch keine Bewertungen

- OpAmp - MCP6241Dokument28 SeitenOpAmp - MCP6241Ludwig SchmidtNoch keine Bewertungen

- Ad633 Multiplicador AnalogicoDokument8 SeitenAd633 Multiplicador AnalogicombocoNoch keine Bewertungen

- U708Dokument28 SeitenU708Sol De GabrielNoch keine Bewertungen

- Low Cost Analog Multiplier: AD633JN/AD633ANDokument8 SeitenLow Cost Analog Multiplier: AD633JN/AD633ANNarendra BholeNoch keine Bewertungen

- SN 65 HVD 232Dokument30 SeitenSN 65 HVD 232pj_chaudhary3796Noch keine Bewertungen

- AD667 Microprocessor Compatible 12-Bit D-A Converter AD667Dokument8 SeitenAD667 Microprocessor Compatible 12-Bit D-A Converter AD667skiziltoprakNoch keine Bewertungen

- OpAmp - MCP6244Dokument38 SeitenOpAmp - MCP6244Ludwig SchmidtNoch keine Bewertungen

- Max7490 Max7491Dokument18 SeitenMax7490 Max7491xo9o6Noch keine Bewertungen

- Max3160 Max3162Dokument23 SeitenMax3160 Max3162jb2015831Noch keine Bewertungen

- Low-Power, 12-Bit Voltage-Output Dacs With Serial InterfaceDokument16 SeitenLow-Power, 12-Bit Voltage-Output Dacs With Serial InterfaceMarcelo FerreiraNoch keine Bewertungen

- Features Applications: X+ X - Y+ YDokument35 SeitenFeatures Applications: X+ X - Y+ YAlvaro ChaconNoch keine Bewertungen

- Ca3306 (A, C)Dokument17 SeitenCa3306 (A, C)notaden1849Noch keine Bewertungen

- HS-2420RH - Fast Sample and HolDokument8 SeitenHS-2420RH - Fast Sample and HolDeepa DevarajNoch keine Bewertungen

- Max7426 Max7427Dokument12 SeitenMax7426 Max7427ridzim4638100% (1)

- Datasheet L272MDokument10 SeitenDatasheet L272MJavier JaviNoch keine Bewertungen

- Vishay Siliconix: Dual-In-Line and SOICDokument10 SeitenVishay Siliconix: Dual-In-Line and SOICابو ياسينNoch keine Bewertungen

- sc7001q Ay 961Dokument18 Seitensc7001q Ay 961r2c1Noch keine Bewertungen

- Conversor D-A M62352FPDokument6 SeitenConversor D-A M62352FPagus2kNoch keine Bewertungen

- NCV47821 3.3 V To 20 V Adjustable Dual LDO With Adjustable Current Limit and Diagnostic FeaturesDokument15 SeitenNCV47821 3.3 V To 20 V Adjustable Dual LDO With Adjustable Current Limit and Diagnostic FeaturesTestronicpartsNoch keine Bewertungen

- Dac121 - 12bit DacDokument19 SeitenDac121 - 12bit DackoltearunNoch keine Bewertungen

- Maxim MAX1771 Boost ConverterDokument16 SeitenMaxim MAX1771 Boost ConverterLeo KralNoch keine Bewertungen

- LCDD Data Bc1602aDokument34 SeitenLCDD Data Bc1602aAnkit AgrawalNoch keine Bewertungen

- Miniature, Low-Voltage, Precision Step-Down Controller: General Description - FeaturesDokument20 SeitenMiniature, Low-Voltage, Precision Step-Down Controller: General Description - Featurescatsoithahuong84Noch keine Bewertungen

- Ca3162 ADokument7 SeitenCa3162 Ajnax101Noch keine Bewertungen

- Micro: Description FeaturesDokument20 SeitenMicro: Description FeaturespopcriNoch keine Bewertungen

- Max 253Dokument18 SeitenMax 253sergey39123Noch keine Bewertungen

- Ua 723Dokument21 SeitenUa 723roozbehxoxNoch keine Bewertungen

- Datasheet L6229Dokument25 SeitenDatasheet L6229Raul Sense MejiaNoch keine Bewertungen

- 28V 2A Step-Down Switching Regulator: Power Management Features DescriptionDokument19 Seiten28V 2A Step-Down Switching Regulator: Power Management Features DescriptionLuis Espino PérezNoch keine Bewertungen

- LM3916 Dot/Bar Display Driver: Features DescriptionDokument31 SeitenLM3916 Dot/Bar Display Driver: Features DescriptionIngeniero Mecánico AgrícolaNoch keine Bewertungen

- LMC555 CMOS Timer: General Description FeaturesDokument10 SeitenLMC555 CMOS Timer: General Description FeaturesJeremy ObriotNoch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Artwork SpecificationDokument4 SeitenArtwork Specificationjnax101Noch keine Bewertungen

- 28701-En LZT14606 en A PDFV1R2Dokument3 Seiten28701-En LZT14606 en A PDFV1R2jnax101Noch keine Bewertungen

- SG3524 Application NotesDokument6 SeitenSG3524 Application NotesSANDEEP KUMAR RAHEJANoch keine Bewertungen

- Transistor NPN 2n222aDokument8 SeitenTransistor NPN 2n222aRoberto Eduardo Tenorio RamosNoch keine Bewertungen

- SG 3524Dokument15 SeitenSG 3524jnax101Noch keine Bewertungen

- Classd Digital Amplifier TutorialDokument54 SeitenClassd Digital Amplifier TutorialemerychNoch keine Bewertungen

- Box ExampleDokument6 SeitenBox Examplejnax101Noch keine Bewertungen

- MC 14093Dokument8 SeitenMC 14093rrebollarNoch keine Bewertungen

- Electronics 1 Practical 6: Equipment RequiredDokument1 SeiteElectronics 1 Practical 6: Equipment Requiredjnax101Noch keine Bewertungen

- Electronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment RequiredDokument1 SeiteElectronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment Requiredjnax101Noch keine Bewertungen

- Applications Using The SG3524: Integrated CircuitsDokument3 SeitenApplications Using The SG3524: Integrated Circuitsjnax101Noch keine Bewertungen

- Elt 1 Practical 3.Dokument2 SeitenElt 1 Practical 3.jnax101Noch keine Bewertungen

- SG 3524Dokument3 SeitenSG 3524florianosNoch keine Bewertungen

- Elt 1 Practical 1.WpdDokument1 SeiteElt 1 Practical 1.Wpdjnax101Noch keine Bewertungen

- LM317Dokument22 SeitenLM317jnax101Noch keine Bewertungen

- Electronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment RequiredDokument1 SeiteElectronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment Requiredjnax101Noch keine Bewertungen

- LM78XX Series Voltage Regulators: General DescriptionDokument6 SeitenLM78XX Series Voltage Regulators: General DescriptiondebabratalogonNoch keine Bewertungen

- LM2524D/LM3524D Regulating Pulse Width Modulator: General DescriptionDokument22 SeitenLM2524D/LM3524D Regulating Pulse Width Modulator: General DescriptionrutayanpNoch keine Bewertungen

- MAX608Dokument12 SeitenMAX608jnax101Noch keine Bewertungen

- ELT 1 Prac 4Dokument2 SeitenELT 1 Prac 4jnax101Noch keine Bewertungen

- Data Sheet IC LM 723Dokument13 SeitenData Sheet IC LM 723Wahyu Sulistyo NugrohoNoch keine Bewertungen

- LM393Dokument15 SeitenLM393Izabela AlcântaraNoch keine Bewertungen

- LM337Dokument12 SeitenLM337jnax101Noch keine Bewertungen

- MAX619Dokument7 SeitenMAX619jnax101Noch keine Bewertungen

- Max 1672Dokument12 SeitenMax 1672jnax101Noch keine Bewertungen

- Max 1674Dokument12 SeitenMax 1674jnax101Noch keine Bewertungen

- Max 1642Dokument12 SeitenMax 1642jnax101Noch keine Bewertungen

- MAX606Dokument12 SeitenMAX606jnax101Noch keine Bewertungen

- Max 1672Dokument12 SeitenMax 1672jnax101Noch keine Bewertungen

- Max 1686Dokument4 SeitenMax 1686jnax101Noch keine Bewertungen

- Roba Gamal CSE 566 Training Software Leaders Project TemplateDokument3 SeitenRoba Gamal CSE 566 Training Software Leaders Project Templatemaram mahmoodNoch keine Bewertungen

- DK0014B4 Modbus RTU (ENG)Dokument10 SeitenDK0014B4 Modbus RTU (ENG)Pauls KrūmiņšNoch keine Bewertungen

- Guidance For Industry - Part 11, Electronic Records Electronic Signatures - Scope and ApplicationDokument12 SeitenGuidance For Industry - Part 11, Electronic Records Electronic Signatures - Scope and ApplicationSandeep KumarNoch keine Bewertungen

- Effective Email WritingDokument42 SeitenEffective Email WritingSRIKANTH. GNoch keine Bewertungen

- Tutorial Universal Theme Patcher, Take Ownership, and Windows Theme InstallerDokument8 SeitenTutorial Universal Theme Patcher, Take Ownership, and Windows Theme InstallerchitraNoch keine Bewertungen

- Lesson 6 - MathMATH Q1 Lesson 6 Comparing Numbers Up To 100 000 Using Relational Symbols MarvietblancoDokument24 SeitenLesson 6 - MathMATH Q1 Lesson 6 Comparing Numbers Up To 100 000 Using Relational Symbols MarvietblancoRuselle Navarro DiñoNoch keine Bewertungen

- TFT 2.8 - QuickGuide - Guia Rapida - Guide RapideDokument4 SeitenTFT 2.8 - QuickGuide - Guia Rapida - Guide RapidegianfrancoNoch keine Bewertungen

- Las q1 w3 Empo Tech TorrefielDokument23 SeitenLas q1 w3 Empo Tech TorrefielRubenNoch keine Bewertungen

- Time: 3hours Max. Marks: 100: Printed Pages: 02 Sub Code: ECS701 Paper ID: Roll NoDokument2 SeitenTime: 3hours Max. Marks: 100: Printed Pages: 02 Sub Code: ECS701 Paper ID: Roll NoMayank PandeyNoch keine Bewertungen

- Browsers and The DOM: CSI 3140 WWW Structures, Techniques and StandardsDokument177 SeitenBrowsers and The DOM: CSI 3140 WWW Structures, Techniques and StandardsLuis GarciaNoch keine Bewertungen

- KonduruChandana Designer PDFDokument4 SeitenKonduruChandana Designer PDFkkNoch keine Bewertungen

- Dole Stanfilco Banana Spray Scheduling and Monitoring System (DS-BSSMS)Dokument21 SeitenDole Stanfilco Banana Spray Scheduling and Monitoring System (DS-BSSMS)Jessa Wen GipulaoNoch keine Bewertungen

- Chapter 11 - Lighting and SoundDokument2 SeitenChapter 11 - Lighting and SoundKristin RichinsNoch keine Bewertungen

- APPIUM DocumentDokument68 SeitenAPPIUM Documentvaditya2005Noch keine Bewertungen

- Ramdump Wcss Msa0 2022-11-13 03-28-59 PropsDokument14 SeitenRamdump Wcss Msa0 2022-11-13 03-28-59 PropsYoussef MahmoudNoch keine Bewertungen

- HTML + CSS Blogger 911Dokument6 SeitenHTML + CSS Blogger 911Ashlin KATASTROPHENoch keine Bewertungen

- Fundamentals of Data Structures: Name GR - No Roll NoDokument13 SeitenFundamentals of Data Structures: Name GR - No Roll NoATHARVA DOIFODENoch keine Bewertungen

- Website Design and Development AgreementDokument38 SeitenWebsite Design and Development AgreementROZHNoch keine Bewertungen

- DST 4601 Technical ManualDokument103 SeitenDST 4601 Technical ManualPetar Markov100% (2)

- S120 Control Unit Equip Man 0619 en-US-2Dokument360 SeitenS120 Control Unit Equip Man 0619 en-US-2DmitriyNoch keine Bewertungen

- Group 2 - Final ExamDokument15 SeitenGroup 2 - Final ExamFernando PascualNoch keine Bewertungen

- Av LogDokument11 SeitenAv LogJuan SegundoNoch keine Bewertungen

- Software Required: MatlabDokument8 SeitenSoftware Required: MatlabVidur KohliNoch keine Bewertungen

- Series C: From 10 To 60 kVADokument20 SeitenSeries C: From 10 To 60 kVAOleg KuryanNoch keine Bewertungen

- FMEA Errata Sheet ENG AIAG VDA FMEA Handbook 202000602 PDFDokument10 SeitenFMEA Errata Sheet ENG AIAG VDA FMEA Handbook 202000602 PDFBonny BonitoNoch keine Bewertungen

- Central University of Karnataka: Introduction To Computer Programming SyllabusDokument1 SeiteCentral University of Karnataka: Introduction To Computer Programming SyllabusNokhwrang BrahmaNoch keine Bewertungen

- Series: User ManualDokument28 SeitenSeries: User ManualMamdouh AwadNoch keine Bewertungen

- Data Science RoadmapDokument8 SeitenData Science Roadmapshiza asgharNoch keine Bewertungen