Beruflich Dokumente

Kultur Dokumente

DS1705

Hochgeladen von

jnax101Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

DS1705

Hochgeladen von

jnax101Copyright:

Verfügbare Formate

ECopyright 1995 by Dallas Semiconductor Corporation.

All Rights Reserved. For important information regarding

patents and other intellectual property rights, please refer to

Dallas Semiconductor data books.

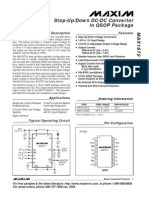

DS1705/DS1706

3.3 and 5.0 Volt MicroMonitor

DSDS1705/DS1706

062097 1/11

FEATURES

Halts and restarts an outofcontrol microprocessor

Holds microprocessor in check during power tran-

sients

Automatically restarts microprocessor after power

failure

Monitors pushbutton for external override

Accurate 5%, 10% or 20% resets for 3.3 systems and

5% or 10% resets for 5.0 volt systems

Eliminates the need for discrete components

3.3 volt 20% tolerance for use with 3.0 volt systems

Pin compatible with the MAXIM MAX705/MAX706 in

8pin DIP and 8pin SOIC

8pin DIP, 8pin SOIC and 8pin SOP packages

Industrial temperature range 40C to +85C

PIN ASSIGNMENT

WDS

RST (*RST)

ST

NMI

1

2

3

4

PBRST

V

CC

GND

IN

8

7

6

5

8

7

6

5

1

2

3

4

PBRST

V

CC

GND

IN

WDS

RST (*RST)

ST

NMI

8PIN DIP

(300 MIL)

8PIN SOIC

(150 MIL)

1

2

3

4

8

7

6

5

PBRST

VCC

GND

IN

WDS

RST

ST

NMI

8PIN SOP

(118 MIL)

See Mech. Drawings

Section

DS1705 and DS1706_/R/S/T (*DS1706L and DS1706P)

PIN DESCRIPTION

PBRST Pushbutton Reset Input

V

CC

Power Supply

GND Ground

IN Input

NMI Nonmaskable Interrupt

ST Strobe Input

RST Active Low Reset Output

*RST Active High Reset Output

(DS1706P and DS1706L only)

WDS Watchdog Status Output

DESCRIPTION

The DS1705/DS1706 3.3 or 5.0 Volt MicroMonitor moni-

tors three vital conditions for a microprocessor: power

supply, software execution, and external override. A

precision temperature compensated reference and

comparator circuit monitors the status of V

CC

at the

device and at an upstream point for maximum protec-

tion. When the sense input detects an outoftolerance

condition a nonmaskable interrupt is generated. As

the voltage at the device degrades an internal power fail

signal is generated which forces the reset to an active

state. When V

CC

returns to an intolerance condition,

the reset signal is kept in the active state for a minimum

of 130 ms to allow the power supply and processor to

stabilize.

DS1705/DS1706

062097 2/11

The second function the DS1705/DS1706 performs is

pushbutton reset control. The DS1705/DS1706

debounces the pushbutton input and guarantees an

active reset pulse width of 130 ms minimum.

The third function is a watchdog timer. The

DS1705/DS1706 has an internal timer that forces the

WDO signal to the active state if the strobe input is not

driven low prior to timeout.

OPERATION

Power Monitor

The DS1705/DS1706 detects outoftolerance power

supply conditions and warns a processorbased sys-

tem of impending power failure. When V

CC

falls below

the minimum V

CC

tolerance, a comparator outputs the

RST (or RST) signal. RST (or RST) is an excellent con-

trol signal for a microprocessor, as processing is

stopped at the last possible moment of valid V

CC

. On

powerup, RST (or RST) are kept active for a minimum

of 130 ms to allow the power supply and processor to

stabilize.

Pushbutton Reset

The DS1705/DS1706 provides an input pin for direct

connection to a pushbutton reset (see Figure 2). The

pushbutton reset input requires an active low signal.

Internally, this input is debounced and timed such that a

RST (or RST) signal of at least 130 ms minimum will be

generated. The 130 ms delay commences as the push-

button reset input is released from the low level. The

pushbutton can be initiated by connecting the WDS or

NMI outputs to the PBRST input as shown in Figure 3.

NonMaskable Interrupt

The DS1705/DS1706 generates a nonmaskable inter-

rupt (NMI) for early warning of a power failure. A preci-

sion comparator monitors the voltage level at the IN pin

relative to an onchip reference generated by an inter-

nal band gap. The IN pin is a high impedance input

allowing for a userdefined sense point. An external

resistor voltage divider network (Figure 5) is used to

interface with high voltage signals. This sense point

may be derived from a regulated supply or from a higher

DC voltage level closer to the main system power input.

Since the IN trip point V

TP

is 1.25 volts, the proper val-

ues for R1 and R2 can be determined by the equation as

shown in Figure 5. Proper operation of the

DS1705/DS1706 requires that the voltage at the IN pin

be limited to V

CC

. Therefore, the maximum allowable

voltage at the supply being monitored (V

MAX

) can also

be derived as shown in Figure 5. A simple approach to

solving the equation is to select a value for R2 high

enough to keep power consumption low, and solve for

R1. The flexibility of the IN input pin allows for detection

of power loss at the earliest point in a power supply sys-

tem, maximizing the amount of time for system shut

down between NMI and RST (or RST).

When the supply being monitored decays to the voltage

sense point, the DS1705/DS1706 pulses the NMI out-

put to the active state for a minimum 200 s. The NMI

power fail detection circuitry also has builtin hysteresis

of 100 V. The supply must be below the voltage sense

point for approximately 5 s before a low NMI will be

generated. In this way, power supply noise is removed

from the monitoring function, preventing false inter-

rupts. During a powerup, any detected IN pin levels

below V

TP

by the comparator are disabled from gener-

ating an interrupt until V

CC

rises to V

CCTP

. As a result,

any potential NMI pulse will not be initiated until V

CC

reaches V

CCTP

.

Connecting NMI to PBRST would allow nonmaskable

interrupt to generate an automatic reset when an out

oftolerance condition occurred in a monitored supply.

An example is shown in Figure 3.

Watchdog Timer

The watchdog timer function forces WDS signals active

when the ST input is not clocked within the 1 second

time out period. Timeout of the watchdog starts when

RST (or RST) becomes inactive. If a hightolow transi-

tion occurs on the ST input pin prior to timeout, the

watchdog timer is reset and begins to timeout again. If

the watchdog timer is allowed to time out, the WDS sig-

nal is driven active (low) for a minimum of 130 ms. The

ST input can be derived from many microprocessor out-

puts. The typical signals used are the microprocessors

address signals, data signals, or control signals. When

the microprocessor functions normally, these signals

would, as a matter of routine, cause the watchdog to be

reset prior to timeout. To guarantee that the watchdog

timer does not timeout, a hightolow transition must

occur at or less than the minimum watchdog timeout of

1 second. A typical circuit example is shown in Figure 6.

DS1705/DS1706

062097 3/11

MICROMONITOR BLOCK DIAGRAM Figure 1

+

T.C.

REFERENCE

DIGITAL

SAMPLER

DIGITAL

SAMPLER DIGITAL

DELAY

WATCHDOG

STATUS

LATCH

LEVEL SENSE

AND

DEBOUNCE

IN

V

CC

PBRST

ST

NMI

RST

WDS

RST

DS1706_/A/R/S/T

DS1706L/DS1706P

PUSHBUTTON RESET Figure 2

GND

IN

ALE

RST

ST

RST

PBRST

V

CC

DS1706P

WDS

NMI

8051

P

PUSHBUTTON RESET CONTROLLED BY NMI AND WDS Figure 3

GND

IN

ALE

ST

RST

PBRST

V

CC

DS1706

WDS

NMI

P

RST UPSTREAM

SUPPLY

VOLTAGE

DS1705/DS1706

062097 4/11

TIMING DIAGRAM: PUSHBUTTON RESET Figure 4

RST

PBRST

RST

V

IH

t

RST

V

IL

t

PDLY

t

PB

V

OH

V

OL

NONMASKABLE INTERRUPT CIRCUIT EXAMPLE Figure 5

GND

IN

ST

RST

PBRST

V

CC

DS1706

WDS

NMI

TO P

R1

R2

V

SENSE

V

SENSE

+

R1 )R2

R2

x 1.25 V

MAX

+

V

SENSE

V

TP

x V

CC

Example: V

SENSE

= 4.50 volts at the trip point

V

CC

= 3.3 volts

10K = R2

Therefore:

4.50

1.25

x 3.3 +12.4 volts maximum

4.5 +

R1 )10K

10K

x 1.25 R1 +26KW

V

IN

> 1.25V

NMI

V

OL

V

OH

V

TP(MAX)

V

TP(MAX)

V

TP

V

TP

V

TP(MIN)

V

TP(MIN)

t

IPD

t

IPD

DS1705/DS1706

062097 5/11

WATCHDOG TIMER Figure 6

GND

IN

ST

RST

PBRST

V

CC

DS1706

WDS

NMI

Z80

P

RST

DECODER

ADDRESS

BUS

MREQ

TIMING DIAGRAM: STROBE INPUT Figure 7

INDETERMINATE

STROBE

INVALID

STROBE

MIN. MAX.

VALID

STROBE

ST

t

TD

RST

WDS

RESET INITIATED

BY PUSHBUTTON

TIMING DIAGRAM: NONMASKABLE INTERRUPT Figure 8

DS1705/DS1706

062097 6/11

TIMING DIAGRAM: POWER DOWN Figure 9

RST SLEWS WITH V

CC

WDS SLEWS WITH V

CC

V

OL

V

OH

V

CCTP(MIN)

V

CCTP(MAX)

V

CCTP

t

RPD

t

F

V

CC

RST

(DS1705 AND DS1706_/R/S/T)

RST

(DS1706L AND DS1706P ONLY)

WDS

DS1705/DS1706

062097 7/11

TIMING DIAGRAM: POWER UP Figure 10

RST

(DS1705 AND DS1706_/R/S/T)

RST

(DS1706L AND DS1706P ONLY)

RST

RST

V

OH

V

OL

t

RPU

V

CCTP(MAX)

V

CCTP

V

CCTP(MIN)

V

CC

WDS

DS1705/DS1706

062097 8/11

ABSOLUTE MAXIMUM RATINGS*

Voltage on V

CC

Pin Relative to Ground 0.5V to +7.0V

Voltage on I/O Relative to Ground** 0.5V to V

CC

+ 0.5V

Operating Temperature 40C to +85C

Storage Temperature 55C to +125C

Soldering Temperature 260C for 10 seconds

* This is a stress rating only and functional operation of the device at these or any other conditions above those

indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods of time may affect reliability.

**The voltage input on IN, ST, and PBRST can be exceeded if the input current is less than 10 mA.

RECOMMENDED DC OPERATING CONDITIONS (40C to +85C)

PARAMETER SYMBOL MIN TYP MAX UNITS NOTES

Supply Voltage V

CC

1.0 5.5 V 1

ST and PBRST Input High Level V

IH

2.0

V

CC

0.5

V

CC

+0.3 V 1, 3

1, 4

ST and PBRST Input Low Level V

IL

0.03 +0.5 V 1

DC ELECTRICAL CHARACTERISTICS (40C to +85C; V

CC

=1.2V to 5.5V)

PARAMETER SYMBOL MIN TYP MAX UNITS NOTES

V

CC

Trip Point DS1705/DS1706L V

CCTP

4.50 4.65 4.75 V 1

V

CC

Trip Point DS1706 V

CCTP

4.25 4.40 4.50 V 1

V

CC

Trip Point DS1706T V

CCTP

3.00 3.08 3.15 V 1

V

CC

Trip Point DS1706S V

CCTP

2.85 2.93 3.00 V 1

V

CC

Trip Point DS1706P or R V

CCTP

2.55 2.63 2.70 V 1

Input Leakage I

IL

1.0 +1.0 A 2

Output Current @ 2.4 volts I

OH

350 A 3

Output Current @ 0.4 volts I

OL

10 mA 3

Output Voltage @ 500 A V

OH

V

CC

+0.3 V

CC

0.1 V 3

Operating Current

@ V

CC

< 5.5 volts I

CC

60 A 5

Operating Current

@ V

CC

< 3.6 volts I

CC

50 A 5

IN Input Trip Point V

TP

1.20 1.25 1.30 V 1

CAPACITANCE (t

A

=25C)

PARAMETER SYMBOL MIN TYP MAX UNITS NOTES

Input Capacitance C

IN

5 pF

Output Capacitance C

OUT

7 pF

DS1705/DS1706

062097 9/11

AC ELECTRICAL CHARACTERISTICS (40C to +85C; V

CC

=1.2V to 5.5V)

PARAMETER SYMBOL MIN TYP MAX UNITS NOTES

PBRST = V

IL

t

PB

150 ns

Reset Active Time t

RST

130 205 285 ms

ST Pulse Width t

ST

10 ns 6

V

CC

Detect to RST and RST t

RPD

5 8 s 9

V

CC

Slew Rate t

F

20 s

V

CC

Detect to RST and RST t

RPU

130 205 285 ms 7

V

CC

Slew Rate t

R

0 ns

PBRST Stable Low to RST and

RST

t

PDLY

250 ns

Watchdog Timeout t

TD

1.0 1.6 2.2 s 8

VIN Detect to NMI t

IPD

5 8 s 9

NOTES:

1. All voltages are referenced to ground.

2. PBRST is internally pulled up to V

CC

with an internal impedance of 40K typical and the ST input is internally

pulled up to V

CC

with an internal impedance of 180K typical.

3. V

CC

2.4 volts

4. V

CC

< 2.4 volts

5. Measured with outputs open and all inputs at V

CC

or ground.

6. Must not exceed t

TD

minimum.

7. t

R

= 5 s

8. Minimum watchdog timeout tested at 2.7 volts for the 3.3 volt devices and 4.5 volts for the 5.0 volt devices.

9. Noise immunity pulses < 2 s at V

CCTP

minimum will not cause a reset.

DS1705/DS1706

062097 10/11

PART MARKING CODES

8PIN SOP

(118 MIL)

1 2 3 4

8 7 6 5

ABCD

WWY

A, B, C and D represents the device type and tolerance.

ABCD

705_ DS1705

706_ DS1706

706L DS1706L

706P DS1706P

706R DS1706R

706S DS1706S

706T DS1706T

WWY represents the device manufacturing Work

Week, Year.

DS1705/DS1706

062097 11/11

DATA SHEET REVISION SUMMARY

The following represent the key differences between 01/12/96 and 06/17/97 version of the DS1705/06 data sheet.

Please review this summary carefully.

1. Page 8 add the following statement to the Absolute Maximum Ratings

The voltage input limits on IN, ST, and PBRST can be exceeded if the input current is less than 10 mA.

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- 28701-En LZT14606 en A PDFV1R2Dokument3 Seiten28701-En LZT14606 en A PDFV1R2jnax101Noch keine Bewertungen

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Artwork SpecificationDokument4 SeitenArtwork Specificationjnax101Noch keine Bewertungen

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Box ExampleDokument6 SeitenBox Examplejnax101Noch keine Bewertungen

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Classd Digital Amplifier TutorialDokument54 SeitenClassd Digital Amplifier TutorialemerychNoch keine Bewertungen

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- SG 3524Dokument15 SeitenSG 3524jnax101Noch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- SG3524 Application NotesDokument6 SeitenSG3524 Application NotesSANDEEP KUMAR RAHEJANoch keine Bewertungen

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Transistor NPN 2n222aDokument8 SeitenTransistor NPN 2n222aRoberto Eduardo Tenorio RamosNoch keine Bewertungen

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Electronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment RequiredDokument1 SeiteElectronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment Requiredjnax101Noch keine Bewertungen

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- LM317Dokument22 SeitenLM317jnax101Noch keine Bewertungen

- Applications Using The SG3524: Integrated CircuitsDokument3 SeitenApplications Using The SG3524: Integrated Circuitsjnax101Noch keine Bewertungen

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Electronics 1 Practical 6: Equipment RequiredDokument1 SeiteElectronics 1 Practical 6: Equipment Requiredjnax101Noch keine Bewertungen

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- SG 3524Dokument3 SeitenSG 3524florianosNoch keine Bewertungen

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- MC 14093Dokument8 SeitenMC 14093rrebollarNoch keine Bewertungen

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- Electronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment RequiredDokument1 SeiteElectronics 1 Practical 2: AIM: To Determine The Characteristic Curve of A Diode. Equipment Requiredjnax101Noch keine Bewertungen

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- Elt 1 Practical 3.Dokument2 SeitenElt 1 Practical 3.jnax101Noch keine Bewertungen

- ELT 1 Prac 4Dokument2 SeitenELT 1 Prac 4jnax101Noch keine Bewertungen

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- Elt 1 Practical 1.WpdDokument1 SeiteElt 1 Practical 1.Wpdjnax101Noch keine Bewertungen

- Data Sheet IC LM 723Dokument13 SeitenData Sheet IC LM 723Wahyu Sulistyo NugrohoNoch keine Bewertungen

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- LM78XX Series Voltage Regulators: General DescriptionDokument6 SeitenLM78XX Series Voltage Regulators: General DescriptiondebabratalogonNoch keine Bewertungen

- MAX619Dokument7 SeitenMAX619jnax101Noch keine Bewertungen

- LM337Dokument12 SeitenLM337jnax101Noch keine Bewertungen

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- LM2524D/LM3524D Regulating Pulse Width Modulator: General DescriptionDokument22 SeitenLM2524D/LM3524D Regulating Pulse Width Modulator: General DescriptionrutayanpNoch keine Bewertungen

- LM393Dokument15 SeitenLM393Izabela AlcântaraNoch keine Bewertungen

- Max 1672Dokument12 SeitenMax 1672jnax101Noch keine Bewertungen

- Max 1674Dokument12 SeitenMax 1674jnax101Noch keine Bewertungen

- MAX606Dokument12 SeitenMAX606jnax101Noch keine Bewertungen

- MAX608Dokument12 SeitenMAX608jnax101Noch keine Bewertungen

- Max 1642Dokument12 SeitenMax 1642jnax101Noch keine Bewertungen

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Max 1672Dokument12 SeitenMax 1672jnax101Noch keine Bewertungen

- Max 1686Dokument4 SeitenMax 1686jnax101Noch keine Bewertungen

- Focus On The Fundamentals of Shielded MV Power CableDokument3 SeitenFocus On The Fundamentals of Shielded MV Power CableMrNoch keine Bewertungen

- Assignment 3 Tania, 102183029Dokument18 SeitenAssignment 3 Tania, 102183029Tania CENoch keine Bewertungen

- Tech Tip: How To Test For An Alternator Voltage DropDokument2 SeitenTech Tip: How To Test For An Alternator Voltage DropainginerNoch keine Bewertungen

- MCQS From CareerRide (Radio Receivers and Transmitters)Dokument7 SeitenMCQS From CareerRide (Radio Receivers and Transmitters)Qaisar_mast100% (2)

- Unit 2 QB With AnswersDokument13 SeitenUnit 2 QB With AnswersECE SakthivelNoch keine Bewertungen

- Arnold 1941Dokument11 SeitenArnold 1941Gino SuárezNoch keine Bewertungen

- Q Meter NotesDokument2 SeitenQ Meter NotesSanjeevNoch keine Bewertungen

- Air Sensor SAC Ex Manual 2.1Dokument11 SeitenAir Sensor SAC Ex Manual 2.1Durga DeviNoch keine Bewertungen

- Heraeus Megafuge 8, Thermo Scientific SL8 Centrifuge - Service ManualDokument62 SeitenHeraeus Megafuge 8, Thermo Scientific SL8 Centrifuge - Service Manualdescarteso50% (2)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Lufkin Rod Pump BrochureDokument2 SeitenLufkin Rod Pump BrochureAbayNoch keine Bewertungen

- DRV8871 3.6-A Brushed DC Motor Driver With Internal Current Sense (PWM Control)Dokument26 SeitenDRV8871 3.6-A Brushed DC Motor Driver With Internal Current Sense (PWM Control)lovejoypeace4Noch keine Bewertungen

- 8STA Steering Boss SystemDokument4 Seiten8STA Steering Boss SystemAbdo RsvNoch keine Bewertungen

- Ob3316 PDFDokument12 SeitenOb3316 PDFKareka top3Noch keine Bewertungen

- US Navy Course NAVEDTRA 14121 - Interior Communications Electrician, Vol 2Dokument162 SeitenUS Navy Course NAVEDTRA 14121 - Interior Communications Electrician, Vol 2Georges100% (2)

- Reverzibilne Hidroelektrane: Jevto SimićDokument5 SeitenReverzibilne Hidroelektrane: Jevto SimićHuseinNoch keine Bewertungen

- Fundamentals of Optical Waveguides 3Rd Edition Katsunari Okamoto Full ChapterDokument51 SeitenFundamentals of Optical Waveguides 3Rd Edition Katsunari Okamoto Full Chapterbetty.tavares510100% (12)

- Electronic Weighing SystemDokument33 SeitenElectronic Weighing SystemPrakash KumarNoch keine Bewertungen

- TK3701D User Manual ENDokument31 SeitenTK3701D User Manual ENDragan ŠašićNoch keine Bewertungen

- High PassDokument2 SeitenHigh PassMamoon BarbhuyanNoch keine Bewertungen

- Backbone Microwave Technical Proposal V1.1Dokument23 SeitenBackbone Microwave Technical Proposal V1.1Salman LabiadhNoch keine Bewertungen

- Smart DustbinDokument30 SeitenSmart DustbinAditya ConsultancyNoch keine Bewertungen

- Carbon BrushDokument1 SeiteCarbon BrushmannyNoch keine Bewertungen

- 3Dokument4 Seiten3Arnel Pamaos Lopiba MontañezNoch keine Bewertungen

- MI MA10 User's Manual (MR or MI)Dokument70 SeitenMI MA10 User's Manual (MR or MI)MostafAliNoch keine Bewertungen

- MODEL: T.VST26.7X (Asia) : Part Number: SP-10031936Dokument10 SeitenMODEL: T.VST26.7X (Asia) : Part Number: SP-10031936Yoyneer SalinasNoch keine Bewertungen

- HT 66 KV Sf6 Circuit BreakerDokument9 SeitenHT 66 KV Sf6 Circuit BreakerJoint Power ElectricalNoch keine Bewertungen

- Swintec 401DP Service ManualDokument28 SeitenSwintec 401DP Service ManualDaniel & Jennifer DenigNoch keine Bewertungen

- DCLD (3rd) May2018Dokument2 SeitenDCLD (3rd) May2018Karan MiglaniNoch keine Bewertungen

- MIC101 - Koushik DuttaDokument16 SeitenMIC101 - Koushik DuttaKoushik DuttaNoch keine Bewertungen

- LBII ParametrosDokument37 SeitenLBII ParametrosPolinho Donacimento100% (1)

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsVon EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsBewertung: 5 von 5 Sternen5/5 (2)

- Chip War: The Fight for the World's Most Critical TechnologyVon EverandChip War: The Fight for the World's Most Critical TechnologyBewertung: 4.5 von 5 Sternen4.5/5 (82)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyVon EverandChip War: The Quest to Dominate the World's Most Critical TechnologyBewertung: 4.5 von 5 Sternen4.5/5 (227)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Von EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Bewertung: 5 von 5 Sternen5/5 (2)

- Amazon Web Services (AWS) Interview Questions and AnswersVon EverandAmazon Web Services (AWS) Interview Questions and AnswersBewertung: 4.5 von 5 Sternen4.5/5 (3)

- Raspberry Pi for Python Programmers Cookbook - Second EditionVon EverandRaspberry Pi for Python Programmers Cookbook - Second EditionNoch keine Bewertungen

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1714829744?v=1)