Beruflich Dokumente

Kultur Dokumente

UAL 8bits

Hochgeladen von

delducam0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

5 Ansichten4 SeitenOriginaltitel

UAL_8bits

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

5 Ansichten4 SeitenUAL 8bits

Hochgeladen von

delducamCopyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 4

Unidad Aritmtico Logica de 8 bits

Pablo Gabriel Alvarez, Martn Di Federico, Pedro J ulin

Departamento de Ingeniera Elctrica y de Computadoras,

Universidad Nacional del Sur, Baha Blanca, Buenos Aires, Argentina.

Resumen Este articulo presenta el diseo y construccin de

una Unidad Aritmtico Lgica de 8 bits, este es un circuito

totalmente digital que calcula operaciones Lgicas, Aritmticas y

realiza diferentes desplazamientos en uno de sus registros.

Palabras claves alu; vlsi; cmos.

I. INTRODUCION

La tecnologa se hace presente cada vez ms en nuestra

vida cotidiana, en computadoras, lavarropas, calculadoras,

impresoras, etc. La tecnologa es la palabra que comprende a

todos los dispositivos electrnicos que estn compuestos por

algn circuito elctrico, la gran mayora realiza algn tipo de

clculo, para hacer esto posible muchas veces es necesaria una

unidad especializada que realice estos clculos. La unidad que

realiza operaciones aritmticas y lgicas es llamada ALU.

Este trabajo muestra la arquitectura y el diseo de una

ALU que cuenta con 8 funciones lgicas, 5 aritmticas y 4

funciones de desplazamiento. Las celdas bsicas utilizadas

para este diseo, tanto el esquemtico como las mascaras de

fabricacin fueron creadas especialmente para este propsito,

utilizando el paquete se software Tanner EDA. Para este

circuito se utilizo lgica CMOS complementaria, una

alimentacin de 3,3V y todos los transistores son de tamao

mnimo definido por la tecnologa. Este circuito fue fabricado

en la tecnologa ON C5N, ocupa un tamao de 1590 m x

1208 m y consta de 2400 transistores.

El modo de operacin de la ALU es el siguiente,

dependiendo de cual de las seales se activa, ENA o ENB, se

almacenan los 8 bits en el registro A B. La operacin a

realizar depende del valor de la seal SELEC. Por medio de la

entrada ENF se habilita la salida de la operacin.

Este trabajo esta organizado de la siguiente manera:

La seccin I consiste en una breve introduccin del trabajo

que se presenta. En la seccin II se explican las diferentes

funciones que se pueden implementar, la misma se subdivide

en operaciones lgica, aritmticas y desplazamiento.

II. FUNCIONES A IMPLEMENTAR

Esta ALU cuenta con 4 seales de control para seleccionar

una de las 16 operaciones posibles. La tabla I muestra las

distintas funciones que se pueden realizar este circuito y la

configuracin necesaria para llevar a cabo la tarea dependiendo

del valor que tenga la seal selec.

TABLA I. Conjunto de funciones

FIGURA1: DIAGRAMA EN BLOQUES

La Unidad Aritmtico Lgica se compone bsicamente de

dos Registros de Entrada, un Registro de Salida, un Registro

de Estado (overflow) y un Registro de control (selec), el cual

hace posible la seleccin de cada una de las operaciones, tal

IV Congreso Microelectrnica Aplicada (uEA 2013) 130

Universidad Tecnolgica Nacional - Facultad Regional Baha Blanca RED_UIE

como se puede observar en la tabla I. Adems cuenta con dos

seales de habilitacin para los registros de entrada ENA,

ENB y una para la salida el registro de salida ENF. El

diagrama en bloques del circuito, y las seales que lo

componen se pueden ver en la Figura 1.

A. FUNCIONES LOGICAS

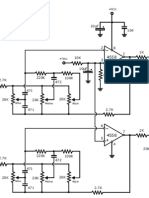

El bloque que calcula las operaciones lgicas se muestra

en la Fig 2. Las entradas son bits de los registros A y B, ambos

correspondientes a la misma direccin. Estas dos entradas estn

conectadas directamente a todas las compuertas lgicas, por

este motivo es que se realiza todas las operaciones

simultneamente. Luego, por medio de un multiplexor, se

selecciona el resultado a obtener a la salida dependiendo del

valor que tenga SELEC. Este bloque se replica ocho veces, una

por cada bit.

(a) (b)

Figura 2: Diagrama de conexin lgica (a); mascara del

multiplexor de 16 x4 (b)

Algunas de las simulaciones de las compuertas bsicas se

pueden observar en la figura 3, donde el eje vertical

corresponde al nivel lgico (0 1) y el eje horizontal es el

tiempo. La seal superior e intermedia son los bits de los

registro de entrada y el inferior es el resultado.

(a) (b) (c)

Figura 3: compuerta nand(a), nor (b), or(c).

B. FUNCIONES ARITMETICAS

La ALU realiza tambin operaciones aritmticas entre las

que se encuentran la suma y la resta. La resta se puede

seleccionar entre (A-B) (B-A).

Diseo e Implementacion del Sumador

Los posibles resultados de una suma de dos dgitos con

carry se sintetizan en la figura 4. Se tiene en cuenta el carry

de entrada Cin.

(a) (b)

Figura 4: Ecuaciones (a); Esquemtico (b).

Diseo e Implementacion del Restador

A partir del sumador se construye el restador. Para poder

realizar la resta de dos nmeros, a uno de los dos operandos

se le calcula el complemento a 2, este nmero va a ser el

negativo; luego se realiza la suma normalmente.

Para obtener el complemento a 2 se invierten todos los

bits y luego se suma uno.

Para invertir la seal de una de las entradas se conecta un

inversor a cada uno de los bits de la palabra de entrada; luego

se le suma uno, colocando un uno en la seal de CARRY IN.

Una vez analizado el sumador y el restador se sintetiza en

un solo esquemtico, como se puede observar en la figura4.

(a) (b)

Figura 4: Esquemtico del sumador (a); Mascara (b)

Al tener cada celda bsica por separado (Lgica y

Aritmtica), se unifico formando un solo bloque, la mascara

correspondiente se puede ver en la figura 5.

Figura 5

IV Congreso Microelectrnica Aplicada (uEA 2013) 131

Universidad Tecnolgica Nacional - Facultad Regional Baha Blanca RED_UIE

Las dimensiones de las mascaras es de 851m de largo y

174m ancho.

C. FUNCION DESPLAZAMIENTO

La funcin de desplazamiento solo puede ser aplicada a la

palabra almacenada en el registro A.

Los desplazamientos que se pueden hacer en esta

arquitectura son:

o SL Los ocho bits rotan hacia la izquierda, una vez

aplicada esta operacin el extremo izquierdo va al primer

lugar del registro desplazamiento. De esta forma se conservan

todos los bits (Figura 6a).

o SHL A diferencia del desplazamiento SL, en este

caso el bit que sale por el extremo izquierdo se elimina, al

desplazar la palabra queda una vacante en el extremo derecho,

en la que se incorpora un cero (Figura 6b).

(a) (b)

Figura 6: desplazamiento SL (a) y (b) el SHL

o SR Es anlogo al desplazamiento SL, en este caso

los bits se rotan hacia la derecha. (Figura 7a).

o SHR Es anlogo al desplazamiento SHL, en este

caso los bits se rotan hacia la derecha. (Figura 7b).

(a) (b)

Figura 7: desplazamiento SR (a) y (b) el SHR

Para indicar a la unidad aritmtica lgica que realice un

desplazamiento, se debe cargar en el registro selec los

siguientes valores:

o S0 =1 y S1 =1

o Con S2 y S3 se selecciona el tipo de corrimiento

como se muestra en la tabla I.

La implementacin de los desplazamientos se realiza

conectando los datos del registro A en ocho multiplexores

diferentes en un determinado orden, en la figura 8 se puede

observar la forma de conexionado.

Esta es una forma de hacer los diferentes desplazamientos,

ya que de otra forma tendramos que haber utilizado registros

desplazamiento.

Figura 8

Como resultado final (figura 9) se puede compara el

diseo de la mascara completa con la construccin fsica.

En la Fig. 9a el recuadro A corresponde a los registros

de entrada, B registro de salida, C funciones lgicas y

aritmticas y D multiplexor de 16x4. La estructura C y D se

replica 8 veces.

(a) (b)

Figura 9: Mascara completa de la ALU, (a) y (b) Foto

fsica.

III. CONCLUSIONES

En el transcurso de este trabajo se pudo terminar de

reforzar y relacionar los conceptos tericos con la prctica. Al

terminar de analizar la arquitectura que se utilizara en la

Unidad Aritmtico Lgica se comenz a desarrollar los

esquemticos y sus mascaras. Este diseo se inici desde la

unidad mnima, diseando el transistor PMOS y el NMOS.

Una vez que se dimensionaron correctamente los transistores

de tamao mnimo se comenz a construir el inversor, luego

compuertas bsicas (nor, nand, xor, ect.) y as se sigui

creciendo en complejidad.

Para conectar los diferentes transistores se utilizo metal 1

de forma horizontal y metal 2 vertical.

Para probar el funcionamiento de la ALU se construyo

una placa de prueba con el programa Proteus, la rutina de de

verificacin se escribi en Code Vision para un Atmega168,

de esta forma se pudo observar el correcto funcionamiento de

la Unidad Aritmtico Lgica. Esta Unidad Aritmtico Lgica

se piensa usar en un proyecto futuro que ser un Micro de

8bits.

IV Congreso Microelectrnica Aplicada (uEA 2013) 132

Universidad Tecnolgica Nacional - Facultad Regional Baha Blanca RED_UIE

REFERENCIAS

-Thomas Schubert, Jr Ernest Kim, Active Nolinear Electronics,

John Wiley and Sons, 1996.

-Sedra y Smith, microelectronics Circuits, oxford University

Press, 2004.

-Jan M. Rebaey, anantha Chandrakasan, Borivoje Nikolic,

Digital Integrated Circuits A design perspective, Pearson,

2004.

IV Congreso Microelectrnica Aplicada (uEA 2013) 133

Universidad Tecnolgica Nacional - Facultad Regional Baha Blanca RED_UIE

Das könnte Ihnen auch gefallen

- La Guia Maestra de Los Amplificadores Operacionales Primera EdiciónDokument149 SeitenLa Guia Maestra de Los Amplificadores Operacionales Primera EdiciónLuis EstradaNoch keine Bewertungen

- Amplificadores en CascadaDokument27 SeitenAmplificadores en CascadaTaimir Alain Morales RocheNoch keine Bewertungen

- Directrices para La Preservación Del Patrimonio Digital Preparado Por La Biblioteca Nacional de AustraliaDokument176 SeitenDirectrices para La Preservación Del Patrimonio Digital Preparado Por La Biblioteca Nacional de AustraliaCursoBD2008Noch keine Bewertungen

- Dialnet LaRevolucionFrancesaYElDerechoAdministrativoFrance 1706971Dokument24 SeitenDialnet LaRevolucionFrancesaYElDerechoAdministrativoFrance 1706971STRAGONNoch keine Bewertungen

- Empresa de DigitalizaciónDokument112 SeitenEmpresa de DigitalizacióndelducamNoch keine Bewertungen

- Instituciones Generales de Derecho Internacional Privado Mas Alla Del Problema ConflictualDokument69 SeitenInstituciones Generales de Derecho Internacional Privado Mas Alla Del Problema ConflictualseguridadanonimaNoch keine Bewertungen

- Dialnet OrientacionesParaResolverCasosDeTeoriaDelDelito 4773617 PDFDokument10 SeitenDialnet OrientacionesParaResolverCasosDeTeoriaDelDelito 4773617 PDFSilvia Patricia Pat GonzàlezNoch keine Bewertungen

- DOXA. Francois Ost. para Qué Sirve El DerechoDokument34 SeitenDOXA. Francois Ost. para Qué Sirve El DerechoRoque F. Trueba GuzmánNoch keine Bewertungen

- I 2 62. Bibliografia Programas de Derecho AdmiDokument179 SeitenI 2 62. Bibliografia Programas de Derecho AdmidelducamNoch keine Bewertungen

- Los Tratados No Son Leyes. Eugenio Hernández-Bretón BolACPS - 1995!62!131 - 83-87Dokument5 SeitenLos Tratados No Son Leyes. Eugenio Hernández-Bretón BolACPS - 1995!62!131 - 83-87delducamNoch keine Bewertungen

- Catálogo de Publicaciones PDFDokument55 SeitenCatálogo de Publicaciones PDFMeily PérezNoch keine Bewertungen

- Requisitos para Presentar Trabajo de LicenciaturaDokument1 SeiteRequisitos para Presentar Trabajo de LicenciaturaEBA-UCVNoch keine Bewertungen

- Planescerrados Prepagomovil PDFDokument1 SeitePlanescerrados Prepagomovil PDFdelducamNoch keine Bewertungen

- WebsitesefectosDokument6 SeitenWebsitesefectosdelducamNoch keine Bewertungen

- Accesorios de TuberiasDokument28 SeitenAccesorios de TuberiasOvidio Canaviri AchoNoch keine Bewertungen

- II Convencion Colectiva UniDokument37 SeitenII Convencion Colectiva Unianon_282378678Noch keine Bewertungen

- Valvulas Retenciones y FiltrosDokument28 SeitenValvulas Retenciones y FiltrosKevin CangoNoch keine Bewertungen

- Instructivo Inscripcion PREGRADO FINAL 2017-2018 Precio NDokument6 SeitenInstructivo Inscripcion PREGRADO FINAL 2017-2018 Precio NdelducamNoch keine Bewertungen

- Dia de La Capa de Ozono PDFDokument4 SeitenDia de La Capa de Ozono PDFdelducamNoch keine Bewertungen

- Información Sobre La Tarjeta de AlimentaciónDokument1 SeiteInformación Sobre La Tarjeta de AlimentacióndelducamNoch keine Bewertungen

- La Capa de OzonoDokument1 SeiteLa Capa de OzonodelducamNoch keine Bewertungen

- AHG, AmparoKelsen PDFDokument28 SeitenAHG, AmparoKelsen PDFRobin PagolaNoch keine Bewertungen

- El Amparo SobrevenidoDokument116 SeitenEl Amparo SobrevenidodelducamNoch keine Bewertungen

- EstabilidadDokument8 SeitenEstabilidaddelducamNoch keine Bewertungen

- La Terminacion Relacion TrabajoDokument33 SeitenLa Terminacion Relacion TrabajoMery RodriguezNoch keine Bewertungen

- Ley Orgánica Procesal Del Trabajo - NotilogiaDokument47 SeitenLey Orgánica Procesal Del Trabajo - NotilogiaNotilogía.com67% (3)

- Letra Unica de CambioDokument5 SeitenLetra Unica de CambiodelducamNoch keine Bewertungen

- Emergencias HipertensivasDokument11 SeitenEmergencias Hipertensivasiker455100% (1)

- El AmparoDokument14 SeitenEl AmparodelducamNoch keine Bewertungen

- Ley Orgánica de Amparo Sobre Derechos y Garantías ConstitucionalesDokument11 SeitenLey Orgánica de Amparo Sobre Derechos y Garantías ConstitucionalesJuan Carlos HerreraNoch keine Bewertungen

- 00 - Texto de La Constitucion de OitDokument15 Seiten00 - Texto de La Constitucion de OitdelducamNoch keine Bewertungen

- 2009 Iso 15489 Caracas PDFDokument24 Seiten2009 Iso 15489 Caracas PDFneiskerNoch keine Bewertungen

- Trabajo Evaluacion Circuitos Electricos Teorema de Thevenin y SuperposiciónDokument10 SeitenTrabajo Evaluacion Circuitos Electricos Teorema de Thevenin y Superposiciónmiguel gtzNoch keine Bewertungen

- Informe 1 Digitales FINALDokument20 SeitenInforme 1 Digitales FINALErik Samanez GalianoNoch keine Bewertungen

- Informe FinalDokument11 SeitenInforme FinalDavid CruzNoch keine Bewertungen

- Circuitos Informe Thevenin y Norton 1Dokument5 SeitenCircuitos Informe Thevenin y Norton 1Luis ValenzuelaNoch keine Bewertungen

- Ejercicio 36-41Dokument6 SeitenEjercicio 36-41Shanella ChallcoNoch keine Bewertungen

- Operadores BooleanosDokument8 SeitenOperadores BooleanosYafreymi Pinales BonifacioNoch keine Bewertungen

- Sesión 07, Circuitos CombinacionalesDokument44 SeitenSesión 07, Circuitos CombinacionalesDANIEL ANTONIO ENCALADA SALAZARNoch keine Bewertungen

- Previo 7 Del ViejoDokument4 SeitenPrevio 7 Del ViejojavierNoch keine Bewertungen

- Reguladores de Tensión, Referencias de Tensión yDokument26 SeitenReguladores de Tensión, Referencias de Tensión yWalter GarciaNoch keine Bewertungen

- Fase 3Dokument11 SeitenFase 3Alexander OrtizNoch keine Bewertungen

- JBL LX 2000 Sub ServiceDokument12 SeitenJBL LX 2000 Sub Servicealvhann_1100% (1)

- Practica 5 Amplificador OperacionalDokument3 SeitenPractica 5 Amplificador OperacionalRony Estuardo Reyes PalaciosNoch keine Bewertungen

- Problemas de Amplificacion e Intrumentacion de SeñalesDokument28 SeitenProblemas de Amplificacion e Intrumentacion de SeñaleslmrelatorNoch keine Bewertungen

- EM P01 Guide PDFDokument5 SeitenEM P01 Guide PDFjuanNoch keine Bewertungen

- T 5 Electronic ADokument5 SeitenT 5 Electronic AVentura Dionisio RomeoNoch keine Bewertungen

- Fisica Informatica Examen 1Dokument6 SeitenFisica Informatica Examen 1siNoch keine Bewertungen

- Alcad Tarifa Es Multimedia TV 2022Dokument60 SeitenAlcad Tarifa Es Multimedia TV 2022VEMATELNoch keine Bewertungen

- Informe #9 - Laboratorio Sistemas de Control II - Rondinel Buleje IvanDokument11 SeitenInforme #9 - Laboratorio Sistemas de Control II - Rondinel Buleje IvanIvan Rondinel BulejeNoch keine Bewertungen

- Circuitos Logicos 9Dokument6 SeitenCircuitos Logicos 9Sofia VegaNoch keine Bewertungen

- Guia N°2 EstabilidadDokument3 SeitenGuia N°2 EstabilidadMatíasNoch keine Bewertungen

- Codificacion de Circuitos TTL CmosDokument4 SeitenCodificacion de Circuitos TTL CmosBrisa Aldana MartinezNoch keine Bewertungen

- 2do Parcial Electronica 2Dokument16 Seiten2do Parcial Electronica 2Héctor SolísNoch keine Bewertungen

- Teorema de TheveninDokument32 SeitenTeorema de TheveninRocíoNoch keine Bewertungen

- Amplificador de Audio de 20WDokument13 SeitenAmplificador de Audio de 20WErikaMaldonadoPinedaNoch keine Bewertungen

- Generador Onda Diente de SierraDokument7 SeitenGenerador Onda Diente de SierrabuyesyohanNoch keine Bewertungen

- Amplificadores Diferenciales, de Instrumentación Y de PuenteDokument18 SeitenAmplificadores Diferenciales, de Instrumentación Y de PuenteJuan PeñaNoch keine Bewertungen

- PLL 1Dokument12 SeitenPLL 1alder anthony anahueNoch keine Bewertungen

- Amplificadores de PotenciaDokument5 SeitenAmplificadores de PotenciaSickelNoch keine Bewertungen