Beruflich Dokumente

Kultur Dokumente

A 50nm Depleted-Substrate CMOS Transistor (DST)

Hochgeladen von

Stefn Francis ⎝⏠⏝⏠⎠Originalbeschreibung:

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

A 50nm Depleted-Substrate CMOS Transistor (DST)

Hochgeladen von

Stefn Francis ⎝⏠⏝⏠⎠Copyright:

Verfügbare Formate

A 50nm Depleted-Substrate CMOS Transistor (DST)

Robert Chau, Jack Kavalieros, Brian Doyle, hand Murthy, Nancy Paulsen, Daniel Lionberger,

Douglas Barlage, Reza Arghavani, Brian Roberds and Mark Doczy

Components Research, Logic Technology Development, Intel Corporation, Hillsboro, OR 97 124

I. Abstract

In this paper we show a Depleted-Substrate Transistor

(DST) technology which demonstrates significant

performance gain over bulk Si transistors without the floating

body effect (FBE). We have fabricated depleted-substrate

CMOS transistors on thin silicon body (130nm) with

physical gate lengths down to 50nm which show much

steeper subthreshold slopes (<75mV/decade) and improved

DIBL (15OmVN) over both partially-depleted (P-D) SO1 and

bulk Si, for both PMOS and NMOS transistors. The salicide

formation and high parasitic resistance problems associated

with the use of thin Si body can be overcome by using raised

source/drain. Depleted-substrate PMOS transistors with

50nm physical gate length and raised source/drain were

fabricated and achieved I,,,, =0.65mA/um and I,,@ =9nNum

at V, =1.3V. This PMOS drive current is the highest ever

reported, and is about 30% higher than any previously

published PMOS I,,, value for both PD-SO1 and bulk Si at a

given bff. The use of raised source/drain improved the I,,,, of

the depleted-substrate NMOS transistors by -20%. Depleted-

substrate NMOS transistors with 65nm physical gate length

and raised source/drain achieved DIBL = 45mVN,

subthreshold slope =75mV/decade, I,,,, =1.18mAlum and I,,@

=60nA/um at V,, =1.3V, as well as significant improvement

in Id-Vd characteristics due to a 60% reduction in DIBL and

>25% improvement in subthreshold slope over the bulk Si.

II. Introduction

There are two kinds of planar SO1 transistor structures,

namely the partially-depleted (P-D) SO1 and fully-depleted

(F-D) SOI. Previously we evaluated P-D SO1 CMOS

transistors and concluded that P-D SO1 has diminishing

performance gain with scaling over standard bulk Si CMOS

[l, 21. In addition, standard P-D SO1 transistors exhibit FBE

which puts a significant burden on circuit design. On the

other hand, it is well-known that fully-depleted (F-D) SO1

transistors eliminate the FBE while providing better

subthreshold slopes than bulk Si transistors [3-51. However,

there are very few reports on F-D SO1 transistors with

physical gate lengths less than 100nm, and the scalability of

F-D SO1 technology is unknown. In this paper we evaluate a

thin-silicon-body depleted-substrate transistor technology

with a focus on sub-70nm physical gate lengths and examine

its scalability and performance down to 50nm. We give this

transistor technology a generic name of Depleted-Substrate

- Transistor (DST).

III. Process

Sub-70nm depleted-substrate CMOS transistors were

fabricated on thin silicon body with thickness 530nm on top

of a -200nm buried oxide. The physical gate oxide thickness

was equal to 1 Snm. Figure 1 shows a TEM cross section of a

thin-silicon-body depleted-substrate transistor. To overcome

the salicide formation and high parasitic resistance problems

in thin-silicon-body devices, raised source/drain can be used.

Figure 2 shows a TEM cross section of the DST with raised

source/drain. In this experiment depleted-substrate transistors

with and without raised source/drain were fabricated down to

50nm. Standard 0.1 3um-generation CMOS transistors with

-70nm physical gate length and 1.5nm physical gate oxide

[6] were used as the control.

IV. Device Characteristics and Discussion

Figures 3 and 4 show the subthreshold Id-Vg

characteristics of the 70nm depleted-substrate PMOS and

NMOS transistors respectively without raised source/drain.

Included are the standard bulk Si transistors for reference.

Both the PMOS and NMOS show steeper subthreshold

slopes (5 75mV/decade) and reduced DIBL (I5OmVN)

compared to the control. Figures 5 and 6 show the Id-Vd

family of curves for PMOS and NMOS respectively. There

areno abnormal subthreshold slope changes or kink-effects,

indicating the absence of FBE. The PMOS and NMOS

inversion CV curves are shown in Figure 7. The results show

no abnormality in forming ultra-thin gate oxide on the thin Si

body. Figure 8 shows the channel mobility of the thin-Si-

body DST and the bulk Si transistor. The data shows no

channel mobility degradation in the thin Si body.

To improve salicide formation and reduce parasitic

resistances on thin-silicon-body devices, raised source/drain

technique can be used. Figure 9 shows the Id-Vg

characteristics of a depleted-substrate PMOS transistor with

50nm physical gate length and raised source/drain. It

achieves DIBL = 40mVN, subthreshold slope =

70mV/decade, I,,,, =0.65mA/um and I,,@= 9nA/um at V, =

1.3V. This is the highest PMOS I,,,, value ever reported for a

given I offt and is -30% higher than any previously published

PMOS I,,,, value for both P-D SO1 and bulk Si at a given I,,ff

[6]. Figure 10 shows the Id-Vd family of curves for this

50nm PMOS transistor. Figure 11 shows the PMOS I,,n-I,,H

comparison of the depleted-substrate transistor, the depleted-

substrate transistor with raised source/drain and the standard

0.13um-generation bulk Si transistors at V,, =1.3V. For a

given I,,@ (e.g. 1 .O dum) , the depleted-substrate transistor

with raised source/drain shows the highest I,,n value, about

30% higher than the standard bulk Si transistor. Figure 12

shows that compared to the standard Si bulk PMOS at 1.3V,

depleted-substrate PMOS with raised source/drain is able to

achieve the same &, J, , n performance at 1.1V and reduces the

power by at least 30% (power a voltage*).

0-7803-7050-3/01/$10.00 02001 IEEE 29.1 . I

IEDM 01-62 1

The use of raised source/drain also improves salicide

formation and reduces the parasitic resistance problems in the

case of the depleted-substrate NMOS transistor. Figure 13

shows the L,,& comparison of the NMOS DST with versus

without raised source/drain. The data shows that for a given

LE, raised source/drain improves I,,,, of the NMOS DST by

-20%. This L,, improvement can be increased by further

optimizing the raised source/drain formation and reducing

parasitic resistances. Figures 14 and 15 compare the Id-Vg

and Id-Vd characteristics respectively of the NMOS DST

transistor with raised source/drain and the bulk Si control.

Both transistors have physical gate length of 65nm. The

results show that compared to the bulk Si control, the DST

shows significant device performance improvement. Figure

14 shows that the DST NMOS achieves DIBL =45mVN,

subthreshold slope =75mV/decade, L,, =l.l8mA/um and J ff

=60nA/um at V,, =1.3V (this I,,,, can be increased by further

optimizing the raised source/drain formation). Figure 15

shows the much improved Id-Vd characteristics of the

NMOS DST due to the 60% reduction in DIBL and >25%

improvement in subthreshold slope over the bulk Si control.

V. Summary

We have shown here depleted-substrate transistor (DST)

technology on thin-Si-body can be scaled to 50nm physical

gate length with significant performance gain over bulk Si

without FBE. Sub-70nm depleted-substrate CMOS

transistors were fabricated on thin silicon body &30nm) and

shown to have much steeper subthreshold slopes (I

75mV/decade), reduced DIBL SOmVN), similar CV

characteristics and channel mobility compared to standard

bulk Si CMOS transistors, for both PMOS and NMOS. 50nm

physical-gate-length depleted-substrate PMOS transistors

with raised source/drain achieved L,, =0.65mAlum and I,,E =

9nA/um at V,, =1.3V. This is the highest PMOS drive

current ever reported for a given LE, and is -30% higher than

any previously published PMOS I,,,, value for both P-D SO1

and bulk Si at a given LE. The use of raised source/drain

improved the I,,,, of the depleted-substrate NMOS transistors

by -20%. Depleted-substrate NMOS transistors with 65nm

physical gate length and raised source/drain achieve DIBL =

45mVN, subthreshold slope = 75mVdecade, L,, =

1.18mA/um and I,,B =60nA/um at V,, =1.3V, as well as

much improved Id-Vd characteristics due to the 60%

reduction in DIBL and >25% improvement in subthreshold

slope over the bulk Si.

VI. Acknowledgements

The authors would like to thank Gerald Marcyk, Director of

Components Research, Mark Bohr, Director of Process

Architecture and Integration, and Youssef El-Mansy, Vice

President and Director of Logic Technology Development for

their encouragement and support.

VII. References

[l ] R. Chau et al., EDM Tech. Digest, pp. 591-594, 1997.

[2] K. Mistry et al., Symp. VLSI Tech. Digest, pp. 204-205, 2000.

[3] Y.-K. Choi et al., Spp. VLSI Tech. Digest, pp. 19-20,2001.

[4] T. Ohno et al., Symp. VLSI Tech. Digest, pp. 25-26, 1993

[SI D. Hisamoto et al., Symp. VLSI Tech. Digest, pp. 208-209,2000.

[6] S . Tyagi et al., IEDM Tech. Digest, pp. 567-570.2000.

Fig.1. TEM cross-section of a depleted-substrate transistor (DST) on

thin silicon body.

Fig.2. TEM cross-section of a raised-souddrain depleted-

substrate transistor (DST) on thin silicon body.

1 E a b,. ......

- ....... ~~

. . . .. . . . . . . .. . .

'El 1 E a

lE-10 1 \Y

1E-114 . . . . . . . . I . . . 1 5

-1.3 -12 -1.1 -1 4.0 4d 4.1 4.6 4.6 4.4 4.3 42 4.1 0 0.1

vo (vow

Fig. 3. Subthreshold Id-Vg characteristics of the 70nmdepleted-

substrate PMOS (without raised sourcddrain) and bulk Si PMOS.

622-IEDM 01 29.1.2

1 E43

1 ED0

1 E 4

1 E-Q)

1 E47

1 E48

Inversion

4.1 o ai a2 a3 0.4 as 0.6 a 7 a8 ao 1 1.1 1.2 1.3

ve wow

Fig. 4. Subthreshold Id-Vg characteristics of the 70nmdepleted-subsmte

NMOS (without raised sourcddrain) and bulk Si NMOS.

1.3 -1.1 4.0 4.7 -0.1 -0.3 -0.1 ai a3 as 0.7 0.0 1.1 1.3

ve M

Fig. 7. PMOS and NMOS inversion C-V plots for the thin-Si-body

depleted-substrate transistor. Physical gate oxide thickness =1 Snm.

bE-4

4E-4

g QE.4

9

-2E-4

a

210

150

0.2

-1 U

I Oh 0

Bulk Si

.....

I

-1.1 -1.2 -1.1 -1 4.0 -0.6 -0.7 4.6 4.5 4. 4 4.3 -0.2 -0.1 0

vd (VoW

0.4 a6 0.8 1 1.2 1.4 1.

Eeff (MVkm)

Fig. 5. Id-Vd family of curves for the 70nm depleted-substrate PMOS

(without raised sourcddrain).

Fig. 8. NMOS channel mobility of high and low Vt thin-Si-body

depleted-substrate transistor versus bulk Si transistor.

1 E43

1 E44 6E-4

5E.4

I 4m

I 3E.4

2E-4

lE.4

1 E06

1 E46

1 E47

Phyalcal Gate Length =50nm

Swbthreahold slope I 70mVl d.cade

4. I 0.65mAlurn, Cn =QnNurn at V, =1.3V

DIEL =40mVN

1E48

1 E49

1E-10

o 0.1 0.2 0.3 0.4 0.5 0.6 0.7 a8 0.0 i 1.1 1.2 1

Vd (Volts)

4.3 -11 -1.1 4 4.0 4.8 4.7 9. 6 4.5 -0.4 4.3 41 0.1 0

VP volts)

Fig. 6. Id-Vd family of curves for the 70nmdepleted-substrate NMOS

(without raised sourcddrain).

Fig. 9. Subthreshold Id-Vg characteristics of the 50nmphysical-gate-

length depleted-substrate PMOS transistor with raised sourcddrain.

29.1.3

IEDM 01-623

Fig. 10. Id-Vd family of curves for the 50nm physical-gate-length depleted-

substrate PMOS with raised sourcddrain.

1608

Fig. 13. NMOS I,,&ffcomparison of the depleted-subsmte &sistor (no

raised sourcddrain) and the depleted-substrate transistor with raised

sourcddrain at V, =1.3V.

#

'

0

t

1 E-1 0

1F l

o ai az tu M ae ae a7 a8 ao 1 1.1 i a 1.s

yI(vd.)

.l__-__-ll___l_-_----..--.. .

Depi etedSubstrate Transistor (with Raised YD)

DepietebSubstrate Transistor (no Raised WD)/

1E-8-.

1E-7 .

E

$' 1E-8-

f

1E-9 -

l b l 0 -

Bulk Si

0

- / BulkSi

1E-12 4

0.2 0.3 0.4 a6 0.6 0.7 I

Ion (rnAlprn)

Fig. 11. PMOS L-LE comparison of the depleted-substrate transistor (no

rai sed sourceldrain), the depleted-substrate transistor with rai sed

sourddrain, and the standard 0.13um-generation bulk Si transistor at V, =

1.3V.

Depleted-Substrate (wi th Raised SID), V, = 1.3V

Depleted-Substrate (with Raised YD), V, = 1.1V

Bulk Si, V, =1.3V

I

1

:

.g i

~

Raised SID,

Vcc =1.3V

Transistor with ,

I

Vcc =1.3V

I

l Bl l 4

02 0.3 0.4 OS 0.6 0.7 0.1

b n (mAlpm)

Fig. 12. DST PMOS (with raised SI D) at 1.1V achieves identical Ln-Lr

performance to bulk Si PMOS at 1.3V, with -30% power reduction.

8.OE-04-

0 1 1 2 0.2 0.4 0.6 0.8

Vd (Volts)

Fig. 15. Id-Vd characteristics of the 65nm depleted-substrate NMOS (with

raised sourcddrain) and bulk Si NMOS.

624-IEDM 01 29.1.4

Das könnte Ihnen auch gefallen

- Solution Manual for 100 Genesys Design Examples: Second EditionVon EverandSolution Manual for 100 Genesys Design Examples: Second EditionNoch keine Bewertungen

- EI2403 - VLSI Design 2 Marks With AnswersDokument23 SeitenEI2403 - VLSI Design 2 Marks With AnswersAnand GvphNoch keine Bewertungen

- Bipolar Junction TransistorDokument18 SeitenBipolar Junction TransistorPritam Keshari SahooNoch keine Bewertungen

- 18 - Doyle - Datta - EDL 2003 PDFDokument3 Seiten18 - Doyle - Datta - EDL 2003 PDFajith.ganesh2420Noch keine Bewertungen

- Characteristics of P-Channel SOI LDMOS Transistor With Tapered Field OxidesDokument7 SeitenCharacteristics of P-Channel SOI LDMOS Transistor With Tapered Field OxidesAnonymous G1iPoNOKNoch keine Bewertungen

- Iiiyr Visem Vlsi DesignDokument20 SeitenIiiyr Visem Vlsi DesignlokeshwarrvrjcNoch keine Bewertungen

- SSE 2010-SOI Versus Bulk-Silicon Nanoscale FinFETsDokument4 SeitenSSE 2010-SOI Versus Bulk-Silicon Nanoscale FinFETsWenqi ZhangNoch keine Bewertungen

- 1999 - Fully-Depleted SOI CMOSDokument16 Seiten1999 - Fully-Depleted SOI CMOSrpaucar1979Noch keine Bewertungen

- Ijest12 04 05 285Dokument7 SeitenIjest12 04 05 285Vijay Kumar PulluriNoch keine Bewertungen

- EE6372 Semiconductor Process Integration: Pavan Kumar KotaDokument8 SeitenEE6372 Semiconductor Process Integration: Pavan Kumar KotahanumapNoch keine Bewertungen

- Effect of Substrate Bias in The Capacitive Coupling of SOI UTBB MOSFETsDokument4 SeitenEffect of Substrate Bias in The Capacitive Coupling of SOI UTBB MOSFETs浜本毅司Noch keine Bewertungen

- Engineering Seminar Topics - Seminar Paper - FINFET Technology - Engineering SeminarDokument7 SeitenEngineering Seminar Topics - Seminar Paper - FINFET Technology - Engineering SeminarjeshkakkadNoch keine Bewertungen

- Sub 50-Nm Finfet PmosDokument4 SeitenSub 50-Nm Finfet PmosAnonymous OUnaZ1g9Noch keine Bewertungen

- Silicon-Nanowire Mosfets Cmos Compatible Gate-All-Around VerticalDokument4 SeitenSilicon-Nanowire Mosfets Cmos Compatible Gate-All-Around VerticalMas MoNoch keine Bewertungen

- 7.6.2. Poly-Silicon Gate TechnologyDokument14 Seiten7.6.2. Poly-Silicon Gate TechnologyHarshad KulkarniNoch keine Bewertungen

- Future MOSFET Devices Using High-K (TiO2) DielectricDokument6 SeitenFuture MOSFET Devices Using High-K (TiO2) DielectricIJRASETPublicationsNoch keine Bewertungen

- SO1 and Nanoscale MOSFETsDokument2 SeitenSO1 and Nanoscale MOSFETsAnonymous OUnaZ1g9Noch keine Bewertungen

- Ec6601 Vlsi QBW (R2013)Dokument20 SeitenEc6601 Vlsi QBW (R2013)Bharath PonNoch keine Bewertungen

- Scaling Challenges and Device Design Requirements For High Performance Sub-50 NM Gate Length Planar CMOS TransistorsDokument2 SeitenScaling Challenges and Device Design Requirements For High Performance Sub-50 NM Gate Length Planar CMOS TransistorsSwati MattaNoch keine Bewertungen

- Robert Chau ICSICT Paper 101904Dokument5 SeitenRobert Chau ICSICT Paper 101904yassirkelNoch keine Bewertungen

- Soi Vs Cmos For Analog Circuit: Vivian Ma, 961347420 University of TorontoDokument16 SeitenSoi Vs Cmos For Analog Circuit: Vivian Ma, 961347420 University of TorontoerdvkNoch keine Bewertungen

- Tri Gate Transistor Conference Paper 0603Dokument2 SeitenTri Gate Transistor Conference Paper 0603James YasNoch keine Bewertungen

- Electronic Devices in MTL Annual Report 1998Dokument20 SeitenElectronic Devices in MTL Annual Report 1998tbsuirNoch keine Bewertungen

- Fermi FET Technology Seminar ReportDokument21 SeitenFermi FET Technology Seminar Reportimcoolsha999Noch keine Bewertungen

- Design and Simulation of A Two Stage OPAMPDokument4 SeitenDesign and Simulation of A Two Stage OPAMPAbd TashNoch keine Bewertungen

- Double-Gate Fully-Depleted SOI Transistors For Low-Power High-Performance Nano-Scale Circuit DesignDokument6 SeitenDouble-Gate Fully-Depleted SOI Transistors For Low-Power High-Performance Nano-Scale Circuit Designmrsathish2020Noch keine Bewertungen

- Vlsi QBDokument34 SeitenVlsi QBKaviya dharshini S -ECE-028Noch keine Bewertungen

- Unit Iii Vlsi Circuit Design Processes: MOS Circuits Are Formed On Four Basic LayersDokument21 SeitenUnit Iii Vlsi Circuit Design Processes: MOS Circuits Are Formed On Four Basic Layers121910401008 PRATIK ADHIKARYNoch keine Bewertungen

- Finfet TechnologyDokument29 SeitenFinfet TechnologyPrajwal GowdaNoch keine Bewertungen

- 1Dokument28 Seiten1Ashvinikumar DongreNoch keine Bewertungen

- Question & AnswerDokument10 SeitenQuestion & AnswerArighna BasakNoch keine Bewertungen

- 1987 Samsung SFET Data BookDokument446 Seiten1987 Samsung SFET Data BookAsad AhmedNoch keine Bewertungen

- Junctionless CMOS Transistors With Independent Double GatesDokument3 SeitenJunctionless CMOS Transistors With Independent Double GatesBiswajit BeheraNoch keine Bewertungen

- Fin FETDokument25 SeitenFin FETakash chaudharyNoch keine Bewertungen

- Question AnswerDokument7 SeitenQuestion AnswerSaurabh KumarNoch keine Bewertungen

- AND8026/D Solving EMI and ESD Problems With Integrated Passive Device Low Pass Pi FiltersDokument16 SeitenAND8026/D Solving EMI and ESD Problems With Integrated Passive Device Low Pass Pi FiltersAtakan OzturKNoch keine Bewertungen

- VLSI 45nm HiKMG-PaperDokument2 SeitenVLSI 45nm HiKMG-PaperSimGuyNoch keine Bewertungen

- FINFETDokument29 SeitenFINFETNMAHESWARA REDDY KAYALA100% (6)

- Performance Improvement of FinFET Using Nitride SpacerDokument3 SeitenPerformance Improvement of FinFET Using Nitride SpacerseventhsensegroupNoch keine Bewertungen

- Fin FEtDokument39 SeitenFin FEtqwerty123890Noch keine Bewertungen

- Chapter No: Title No: Page NoDokument6 SeitenChapter No: Title No: Page NoAjay JoshyNoch keine Bewertungen

- Adv CMOS JongholeeDokument45 SeitenAdv CMOS Jongholeeashishj1083Noch keine Bewertungen

- 14 - Chapter 7Dokument9 Seiten14 - Chapter 7SHAIK MUSTHAFANoch keine Bewertungen

- DG MosfetDokument22 SeitenDG MosfetshekhartitNoch keine Bewertungen

- 1.1 Scaling of Bulk CmosDokument16 Seiten1.1 Scaling of Bulk CmosVineetha UmeshNoch keine Bewertungen

- Design of A 100 V High-Side NCH LDMOS Breakdown EnhanceDokument4 SeitenDesign of A 100 V High-Side NCH LDMOS Breakdown EnhanceRon HuangNoch keine Bewertungen

- Performance Analysis of Finfet Using Various Ctatel) IelectricsDokument4 SeitenPerformance Analysis of Finfet Using Various Ctatel) IelectricsSai KishoreNoch keine Bewertungen

- Seminar On CmosDokument8 SeitenSeminar On CmosRoberto HoodNoch keine Bewertungen

- Microelectronic CircuitDokument696 SeitenMicroelectronic CircuitImtiaz AhmedNoch keine Bewertungen

- LDMOS Technology For RF Power AmplifiersDokument10 SeitenLDMOS Technology For RF Power AmplifiersParansaranNoch keine Bewertungen

- Design MarginsDokument17 SeitenDesign MarginsRapolu SushmaNoch keine Bewertungen

- Characteristics of Gate-All-Around Junctionless Polysilicon Nanowire Transistors With Twin 20-nm GatesDokument5 SeitenCharacteristics of Gate-All-Around Junctionless Polysilicon Nanowire Transistors With Twin 20-nm GatesSikender Nawaz Shafi BhatNoch keine Bewertungen

- SOI Implementation Whitepaper Infotech v2Dokument12 SeitenSOI Implementation Whitepaper Infotech v2Võ Đức HiếuNoch keine Bewertungen

- Engineered Substrates: Options at The 45nm Node IncludeDokument4 SeitenEngineered Substrates: Options at The 45nm Node IncludeAnkit PawarNoch keine Bewertungen

- Dynamic Threshold-Voltage MOSFET (DTMOS) For Ultra-Low Voltage VLSIDokument9 SeitenDynamic Threshold-Voltage MOSFET (DTMOS) For Ultra-Low Voltage VLSIBüşra AkyıldızNoch keine Bewertungen

- Nanoscale Cmos Spacer Finfet For The Terabit Era: Yang-Kyu Choi, Tsu-Jae King, and Chenming Hu, Fellow, IeeeDokument3 SeitenNanoscale Cmos Spacer Finfet For The Terabit Era: Yang-Kyu Choi, Tsu-Jae King, and Chenming Hu, Fellow, Ieeeanon_894004254Noch keine Bewertungen

- A Miniature 25-Ghz 9-Db Cmos Cascaded Single-Stage Distributed AmplifierDokument3 SeitenA Miniature 25-Ghz 9-Db Cmos Cascaded Single-Stage Distributed AmplifierLe Nguyen MinhNoch keine Bewertungen

- Industry Standard FDSOI Compact Model BSIM-IMG for IC DesignVon EverandIndustry Standard FDSOI Compact Model BSIM-IMG for IC DesignNoch keine Bewertungen

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysVon EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNoch keine Bewertungen

- 4 Amps N-Channel MOSFET: 600voltsDokument5 Seiten4 Amps N-Channel MOSFET: 600voltsOliveira OliveiraNoch keine Bewertungen

- Steg k24 Service Manual v2Dokument16 SeitenSteg k24 Service Manual v2vnbdyxakNoch keine Bewertungen

- 15N10Dokument6 Seiten15N10garchamanNoch keine Bewertungen

- Full Wave Bridge Rectifiers: Mini-DipsDokument1 SeiteFull Wave Bridge Rectifiers: Mini-DipsHaresh vaghelaNoch keine Bewertungen

- Nand Bypass: Design by Erik VincentDokument22 SeitenNand Bypass: Design by Erik VincentJezz MortNoch keine Bewertungen

- DRCDokument10 SeitenDRCSaurabh Chakravarty0% (1)

- Taiwan Semiconductor Manufacturing CompanyDokument14 SeitenTaiwan Semiconductor Manufacturing CompanyAsrarullah sheriff100% (2)

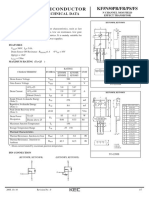

- Semiconductor KF5N50PR/FR/PS/FS: Technical DataDokument7 SeitenSemiconductor KF5N50PR/FR/PS/FS: Technical DataHla Swe OoNoch keine Bewertungen

- Analog BasicDokument29 SeitenAnalog Basicchetan kapoorNoch keine Bewertungen

- Chapter5 PDFDokument128 SeitenChapter5 PDFTonmoyNoch keine Bewertungen

- C 3198Dokument1 SeiteC 3198Kunal Kundanam100% (1)

- CH 05 PowerDokument49 SeitenCH 05 PowerTriếtCỏNoch keine Bewertungen

- Sect. 4.1.1 Single-Quadrant SwitchesDokument11 SeitenSect. 4.1.1 Single-Quadrant SwitchesThinh NguyenNoch keine Bewertungen

- Presentation ON: Scaling of MOSDokument25 SeitenPresentation ON: Scaling of MOSTilottama DeoreNoch keine Bewertungen

- BFQ225Dokument7 SeitenBFQ225cherished5Noch keine Bewertungen

- 2N 6107Dokument5 Seiten2N 6107Alok Pokharel100% (1)

- Optocoupler U Model H21a3Dokument3 SeitenOptocoupler U Model H21a3Mari KhusmaniarNoch keine Bewertungen

- Module 6 MemoryDokument7 SeitenModule 6 MemorynatsuNoch keine Bewertungen

- PTW40N50: General FeaturesDokument9 SeitenPTW40N50: General Featurescharly36Noch keine Bewertungen

- Junction DiodeDokument12 SeitenJunction Diodesekharchandramukhi9Noch keine Bewertungen

- Part I ADokument206 SeitenPart I AsenthilkumaranvNoch keine Bewertungen

- GTODokument29 SeitenGTOAjay TalajiyaNoch keine Bewertungen

- Protected Quad Power DriversDokument8 SeitenProtected Quad Power DriversBraulio Manuel Trejo PerezNoch keine Bewertungen

- 3d IcDokument1 Seite3d IcAbhijithNoch keine Bewertungen

- Vlsi System DesignDokument29 SeitenVlsi System DesignAmar KumarNoch keine Bewertungen

- A SPICE Model of A Thyristor With High Injection Effects and Conductivity ModulationDokument4 SeitenA SPICE Model of A Thyristor With High Injection Effects and Conductivity ModulationTanuj KumarNoch keine Bewertungen

- IRFZ48 55V-64A 140W-N-channelenhancemenT PDFDokument8 SeitenIRFZ48 55V-64A 140W-N-channelenhancemenT PDFZxdIaminxXzlovewithzxXzyouzxNoch keine Bewertungen

- Digital Circuits & Design E-BookDokument42 SeitenDigital Circuits & Design E-Bookpaarthkhera71Noch keine Bewertungen

- 1 Introduction To Analog IC DesignDokument41 Seiten1 Introduction To Analog IC Designnavinkumarrr588Noch keine Bewertungen