Beruflich Dokumente

Kultur Dokumente

WWW - Atmel.in Images Doc0368

Hochgeladen von

VipulJainOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

WWW - Atmel.in Images Doc0368

Hochgeladen von

VipulJainCopyright:

Verfügbare Formate

Features

Compatible with MCS

-51Products

2K Bytes of Reprogrammable Flash Memory

Endurance: 10,000 Write/Erase Cycles

2.7V to 6V Operating Range

Fully Static Operation: 0 Hz to 24 MHz

Two-level Program Memory Lock

128 x 8-bit Internal RAM

15 Programmable I/O Lines

Two 16-bit Timer/Counters

Six Interrupt Sources

Programmable Serial UART Channel

Direct LED Drive Outputs

On-chip Analog Comparator

Low-power Idle and Power-down Modes

Green (Pb/Halide-free) Packaging Option

1. Description

The AT89C2051 is a low-voltage, high-performance CMOS 8-bit microcomputer with

2K bytes of Flash programmable and erasable read-only memory (PEROM). The

device is manufactured using Atmels high-density nonvolatile memory technology

and is compatible with the industry-standard MCS-51 instruction set. By combining a

versatile 8-bit CPU with Flash on a monolithic chip, the Atmel AT89C2051 is a power-

ful microcomputer which provides a highly-flexible and cost-effective solution to many

embedded control applications.

The AT89C2051 provides the following standard features: 2K bytes of Flash, 128

bytes of RAM, 15 I/O lines, two 16-bit timer/counters, a five vector two-level interrupt

architecture, a full duplex serial port, a precision analog comparator, on-chip oscillator

and clock circuitry. In addition, the AT89C2051 is designed with static logic for opera-

tion down to zero frequency and supports two software selectable power saving

modes. The Idle Mode stops the CPU while allowing the RAM, timer/counters, serial

port and interrupt system to continue functioning. The power-down mode saves the

RAM contents but freezes the oscillator disabling all other chip functions until the next

hardware reset.

8-bit

Microcontroller

with 2K Bytes

Flash

AT89C2051

0368HMICRO6/08

2

0368HMICRO6/08

AT89C2051

2. Pin Configuration

2.1 20-lead PDIP/SOIC

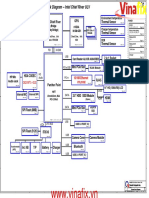

3. Block Diagram

1

2

3

4

5

6

7

8

9

10

20

19

18

17

16

15

14

13

12

11

RST/VPP

(RXD) P3.0

(TXD) P3.1

XTAL2

XTAL1

(INT0) P3.2

(INT1) P3.3

(TO) P3.4

(T1) P3.5

GND

VCC

P1.7

P1.6

P1.5

P1.4

P1.3

P1.2

P1.1 (AIN1)

P1.0 (AIN0)

P3.7

3

0368HMICRO6/08

AT89C2051

4. Pin Description

4.1 VCC

Supply voltage.

4.2 GND

Ground.

4.3 Port 1

The Port 1 is an 8-bit bi-directional I/O port. Port pins P1.2 to P1.7 provide internal pull-ups. P1.0

and P1.1 require external pull-ups. P1.0 and P1.1 also serve as the positive input (AIN0) and the

negative input (AIN1), respectively, of the on-chip precision analog comparator. The Port 1 out-

put buffers can sink 20 mA and can drive LED displays directly. When 1s are written to Port 1

pins, they can be used as inputs. When pins P1.2 to P1.7 are used as inputs and are externally

pulled low, they will source current (I

IL

) because of the internal pull-ups.

Port 1 also receives code data during Flash programming and verification.

4.4 Port 3

Port 3 pins P3.0 to P3.5, P3.7 are seven bi-directional I/O pins with internal pull-ups. P3.6 is

hard-wired as an input to the output of the on-chip comparator and is not accessible as a gen-

eral-purpose I/O pin. The Port 3 output buffers can sink 20 mA. When 1s are written to Port 3

pins they are pulled high by the internal pull-ups and can be used as inputs. As inputs, Port 3

pins that are externally being pulled low will source current (I

IL

) because of the pull-ups.

Port 3 also serves the functions of various special features of the AT89C2051 as listed below:

Port 3 also receives some control signals for Flash programming and verification.

4.5 RST

Reset input. All I/O pins are reset to 1s as soon as RST goes high. Holding the RST pin high for

two machine cycles while the oscillator is running resets the device.

Each machine cycle takes 12 oscillator or clock cycles.

4.6 XTAL1

Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

Port Pin Alternate Functions

P3.0 RXD (serial input port)

P3.1 TXD (serial output port)

P3.2 INT0 (external interrupt 0)

P3.3 INT1 (external interrupt 1)

P3.4 T0 (timer 0 external input)

P3.5 T1 (timer 1 external input)

4

0368HMICRO6/08

AT89C2051

4.7 XTAL2

Output from the inverting oscillator amplifier.

5. Oscillator Characteristics

The XTAL1 and XTAL2 are the input and output, respectively, of an inverting amplifier which can

be configured for use as an on-chip oscillator, as shown in Figure 5-1. Either a quartz crystal or

ceramic resonator may be used. To drive the device from an external clock source, XTAL2

should be left unconnected while XTAL1 is driven as shown in Figure 5-2. There are no require-

ments on the duty cycle of the external clock signal, since the input to the internal clocking

circuitry is through a divide-by-two flip-flop, but minimum and maximum voltage high and low

time specifications must be observed.

Figure 5-1. Oscillator Connections

Note: C1, C2 = 30 pF 10 pF for Crystals

= 40 pF 10 pF for Ceramic Resonators

Figure 5-2. External Clock Drive Configuration

5

0368HMICRO6/08

AT89C2051

6. Special Function Registers

A map of the on-chip memory area called the Special Function Register (SFR) space is shown in

the table below.

Note that not all of the addresses are occupied, and unoccupied addresses may not be imple-

mented on the chip. Read accesses to these addresses will in general return random data, and

write accesses will have an indeterminate effect.

User software should not write 1s to these unlisted locations, since they may be used in future

products to invoke new features. In that case, the reset or inactive values of the new bits will

always be 0.

Table 6-1. AT89C2051 SFR Map and Reset Values

0F8H 0FFH

0F0H

B

00000000

0F7H

0E8H 0EFH

0E0H

ACC

00000000

0E7H

0D8H 0DFH

0D0H

PSW

00000000

0D7H

0C8H

0CFH

0C0H 0C7H

0B8H

IP

XXX00000

0BFH

0B0H

P3

11111111

0B7H

0A8H

IE

0XX00000

0AFH

0A0H

0A7H

98H

SCON

00000000

SBUF

XXXXXXXX

9FH

90H

P1

11111111

97H

88H

TCON

00000000

TMOD

00000000

TL0

00000000

TL1

00000000

TH0

00000000

TH1

00000000

8FH

80H

SP

00000111

DPL

00000000

DPH

00000000

PCON

0XXX0000

87H

6

0368HMICRO6/08

AT89C2051

7. Restrictions on Certain Instructions

The AT89C2051 and is an economical and cost-effective member of Atmels growing family of

microcontrollers. It contains 2K bytes of Flash program memory. It is fully compatible with the

MCS-51 architecture, and can be programmed using the MCS-51 instruction set. However,

there are a few considerations one must keep in mind when utilizing certain instructions to pro-

gram this device.

All the instructions related to jumping or branching should be restricted such that the destination

address falls within the physical program memory space of the device, which is 2K for the

AT89C2051. This should be the responsibility of the software programmer. For example, LJMP

7E0H would be a valid instruction for the AT89C2051 (with 2K of memory), whereas LJMP 900H

would not.

7.1 Branching Instructions

LCALL, LJMP, ACALL, AJMP, SJMP, JMP @A+DPTR These unconditional branching

instructions will execute correctly as long as the programmer keeps in mind that the destination

branching address must fall within the physical boundaries of the program memory size (loca-

tions 00H to 7FFH for the 89C2051). Violating the physical space limits may cause unknown

program behavior.

CJNE [...], DJNZ [...], JB, JNB, JC, JNC, JBC, JZ, JNZ With these conditional branching

instructions the same rule above applies. Again, violating the memory boundaries may cause

erratic execution.

For applications involving interrupts the normal interrupt service routine address locations of the

80C51 family architecture have been preserved.

7.2 MOVX-related Instructions, Data Memory

The AT89C2051 contains 128 bytes of internal data memory. Thus, in the AT89C2051 the stack

depth is limited to 128 bytes, the amount of available RAM. External DATA memory access is

not supported in this device, nor is external PROGRAM memory execution. Therefore, no MOVX

[...] instructions should be included in the program.

A typical 80C51 assembler will still assemble instructions, even if they are written in violation of

the restrictions mentioned above. It is the responsibility of the controller user to know the physi-

cal features and limitations of the device being used and adjust the instructions used

correspondingly.

8. Program Memory Lock Bits

On the chip are two lock bits which can be left unprogrammed (U) or can be programmed (P) to

obtain the additional features listed in the Table 8-1.

Note: 1. The Lock Bits can only be erased with the Chip Erase operation.

Table 8-1. Lock Bit Protection Modes

(1)

Program Lock Bits

LB1 LB2 Protection Type

1 U U No program lock features

2 P U Further programming of the Flash is disabled

3 P P Same as mode 2, also verify is disabled

7

0368HMICRO6/08

AT89C2051

9. Idle Mode

In idle mode, the CPU puts itself to sleep while all the on-chip peripherals remain active. The

mode is invoked by software. The content of the on-chip RAM and all the special functions regis-

ters remain unchanged during this mode. The idle mode can be terminated by any enabled

interrupt or by a hardware reset.

The P1.0 and P1.1 should be set to 0 if no external pull-ups are used, or set to 1 if

external pull-ups are used.

It should be noted that when idle is terminated by a hardware reset, the device normally

resumes program execution, from where it left off, up to two machine cycles before the internal

reset algorithm takes control. On-chip hardware inhibits access to internal RAM in this event, but

access to the port pins is not inhibited. To eliminate the possibility of an unexpected write to a

port pin when Idle is terminated by reset, the instruction following the one that invokes Idle

should not be one that writes to a port pin or to external memory.

10. Power-down Mode

In the power-down mode the oscillator is stopped, and the instruction that invokes power-down

is the last instruction executed. The on-chip RAM and Special Function Registers retain their

values until the power-down mode is terminated. The only exit from power-down is a hardware

reset. Reset redefines the SFRs but does not change the on-chip RAM. The reset should not be

activated before V

CC

is restored to its normal operating level and must be held active long

enough to allow the oscillator to restart and stabilize.

The P1.0 and P1.1 should be set to 0 if no external pull-ups are used, or set to 1 if

external pull-ups are used.

11. Programming The Flash

The AT89C2051 is shipped with the 2K bytes of on-chip PEROM code memory array in the

erased state (i.e., contents = FFH) and ready to be programmed. The code memory array is pro-

grammed one byte at a time. Once the array is programmed, to re-program any non-blank byte,

the entire memory array needs to be erased electrically.

Internal Address Counter: The AT89C2051 contains an internal PEROM address counter

which is always reset to 000H on the rising edge of RST and is advanced by applying a positive

going pulse to pin XTAL1.

Programming Algorithm: To program the AT89C2051, the fol l owi ng sequence i s

recommended.

1. Power-up sequence:

Apply power between V

CC

and GND pins

Set RST and XTAL1 to GND

2. Set pin RST to H

Set pin P3.2 to H

3. Apply the appropriate combination of H or L logic

levels to pins P3.3, P3.4, P3.5, P3.7 to select one of the programming operations

shown in the PEROM Programming Modes table.

8

0368HMICRO6/08

AT89C2051

To Program and Verify the Array:

4. Apply data for Code byte at location 000H to P1.0 to P1.7.

5. Raise RST to 12V to enable programming.

6. Pulse P3.2 once to program a byte in the PEROM array or the lock bits. The byte-write

cycle is self-timed and typically takes 1.2 ms.

7. To verify the programmed data, lower RST from 12V to logic H level and set pins P3.3

to P3.7 to the appropriate levels. Output data can be read at the port P1 pins.

8. To program a byte at the next address location, pulse XTAL1 pin once to advance the

internal address counter. Apply new data to the port P1 pins.

9. Repeat steps 6 through 8, changing data and advancing the address counter for the

entire 2K bytes array or until the end of the object file is reached.

10. Power-off sequence:

set XTAL1 to L

set RST to L

Turn V

CC

power off

Data Polling: The AT89C2051 features Data Polling to indicate the end of a write cycle. During

a write cycle, an attempted read of the last byte written will result in the complement of the writ-

ten data on P1.7. Once the write cycle has been completed, true data is valid on all outputs, and

the next cycle may begin. Data Polling may begin any time after a write cycle has been initiated.

Ready/Busy: The Progress of byte programming can also be monitored by the RDY/BSY output

signal. Pin P3.1 is pulled low after P3.2 goes High during programming to indicate BUSY. P3.1 is

pulled High again when programming is done to indicate READY.

Program Verify: If lock bits LB1 and LB2 have not been programmed code data can be read

back via the data lines for verification:

1. Reset the internal address counter to 000H by bringing RST from L to H.

2. Apply the appropriate control signals for Read Code data and read the output data at

the port P1 pins.

3. Pulse pin XTAL1 once to advance the internal address counter.

4. Read the next code data byte at the port P1 pins.

5. Repeat steps 3 and 4 until the entire array is read.

The lock bits cannot be verified directly. Verification of the lock bits is achieved by observing that

their features are enabled.

Chip Erase: The entire PEROM array (2K bytes) and the two Lock Bits are erased electrically

by using the proper combination of control signals and by holding P3.2 low for 10 ms. The code

array is written with all 1s in the Chip Erase operation and must be executed before any non-

blank memory byte can be re-programmed.

Reading the Signature Bytes: The signature bytes are read by the same procedure as a nor-

mal verification of locations 000H, 001H, and 002H, except that P3.5 and P3.7 must be pulled to

a logic low. The values returned are as follows.

(000H) = 1EH indicates manufactured by Atmel

(001H) = 21H indicates 89C2051

9

0368HMICRO6/08

AT89C2051

12. Programming Interface

Every code byte in the Flash array can be written and the entire array can be erased by using

the appropriate combination of control signals. The write operation cycle is self-timed and once

initiated, will automatically time itself to completion.

Most major worldwide programming vendors offer support for the Atmel AT89 microcontroller

series. Please contact your local programming vendor for the appropriate software revision.

Notes: 1. The internal PEROM address counter is reset to 000H on the rising edge of RST and is advanced by a positive pulse at

XTAL1 pin.

2. Chip Erase requires a 10 ms PROG pulse.

3. P3.1 is pulled Low during programming to indicate RDY/BSY.

13. Flash Programming Modes

Mode RST/VPP P3.2/PROG P3.3 P3.4 P3.5 P3.7

Write Code Data

(1)(3)

12V L H H H

Read Code Data

(1)

H H L L H H

Write Lock

Bit - 1 12V H H H H

Bit - 2 12V H H L L

Chip Erase 12V H L L L

Read Signature Byte H H L L L L

(2)

10

0368HMICRO6/08

AT89C2051

Figure 13-1. Programming the Flash Memory

Figure 13-2. Verifying the Flash Memory

PP

11

0368HMICRO6/08

AT89C2051

Note: 1. Only used in 12-volt programming mode.

15. Flash Programming and Verification Waveforms

14. Flash Programming and Verification Characteristics

T

A

= 0C to 70C, V

CC

= 5.0 10%

Symbol Parameter Min Max Units

V

PP

Programming Enable Voltage 11.5 12.5 V

I

PP

Programming Enable Current 250 A

t

DVGL

Data Setup to PROG Low 1.0 s

t

GHDX

Data Hold after PROG 1.0 s

t

EHSH

P3.4 (ENABLE) High to V

PP

1.0 s

t

SHGL

V

PP

Setup to PROG Low 10 s

t

GHSL

V

PP

Hold after PROG 10 s

t

GLGH

PROG Width 1 110 s

t

ELQV

ENABLE Low to Data Valid 1.0 s

t

EHQZ

Data Float after ENABLE 0 1.0 s

t

GHBL

PROG High to BUSY Low 50 ns

t

WC

Byte Write Cycle Time 2.0 ms

t

BHIH

RDY/BSY\ to Increment Clock Delay 1.0 s

t

IHIL

Increment Clock High 200 ns

12

0368HMICRO6/08

AT89C2051

Notes: 1. Under steady state (non-transient) conditions, I

OL

must be externally limited as follows:

Maximum I

OL

per port pin: 20 mA

Maximum total I

OL

for all output pins: 80 mA

If I

OL

exceeds the test condition, V

OL

may exceed the related specification. Pins are not guaranteed to sink current greater

than the listed test conditions.

2. Minimum V

CC

for Power-down is 2V.

16. Absolute Maximum Ratings*

Operating Temperature ................................. -55C to +125C

*NOTICE: Stresses beyond those listed under Absolute

Maximum Ratings may cause permanent dam-

age to the device. This is a stress rating only and

functional operation of the device at these or any

other conditions beyond those indicated in the

operational sections of this specification is not

implied. Exposure to absolute maximum rating

conditions for extended periods may affect device

reliability.

Storage Temperature..................................... -65C to +150C

Voltage on Any Pin

with Respect to Ground.....................................-1.0V to +7.0V

Maximum Operating Voltage ............................................ 6.6V

DC Output Current...................................................... 25.0 mA

17. DC Characteristics

T

A

= -40C to 85C, V

CC

= 2.7V to 6.0V (unless otherwise noted)

Symbol Parameter Condition Min Max Units

V

IL

Input Low-voltage -0.5 0.2 V

CC

- 0.1 V

V

IH

Input High-voltage (Except XTAL1, RST) 0.2 V

CC

+ 0.9 V

CC

+ 0.5 V

V

IH1

Input High-voltage (XTAL1, RST) 0.7 V

CC

V

CC

+ 0.5 V

V

OL

Output Low-voltage

(1)

(Ports 1, 3)

I

OL

= 20 mA, V

CC

= 5V

I

OL

= 10 mA, V

CC

= 2.7V

0.5 V

V

OH

Output High-voltage

(Ports 1, 3)

I

OH

= -80 A, V

CC

= 5V 10% 2.4 V

I

OH

= -30 A 0.75 V

CC

V

I

OH

= -12 A 0.9 V

CC

V

I

IL

Logical 0 Input Current

(Ports 1, 3)

V

IN

= 0.45V -50 A

I

TL

Logical 1 to 0 Transition Current

(Ports 1, 3)

V

IN

= 2V, V

CC

= 5V 10% -750 A

I

LI

Input Leakage Current

(Port P1.0, P1.1)

0 < V

IN

< V

CC

10 A

V

OS

Comparator Input Offset Voltage V

CC

= 5V 20 mV

V

CM

Comparator Input Common

Mode Voltage

0 V

CC

V

RRST Reset Pull-down Resistor 50 300 k

C

IO

Pin Capacitance Test Freq. = 1 MHz, T

A

= 25C 10 pF

I

CC

Power Supply Current

Active Mode, 12 MHz, V

CC

= 6V/3V 15/5.5 mA

Idle Mode, 12 MHz, V

CC

= 6V/3V

P1.0 & P1.1 = 0V or V

CC

5/1 mA

Power-down Mode

(2)

V

CC

= 6V, P1.0 & P1.1 = 0V or V

CC

100 A

V

CC

= 3V, P1.0 & P1.1 = 0V or V

CC

20 A

13

0368HMICRO6/08

AT89C2051

18. External Clock Drive Waveforms

()

19. External Clock Drive

Symbol Parameter

V

CC

= 2.7V to 6.0V V

CC

= 4.0V to 6.0V

Units Min Max Min Max

1/t

CLCL

Oscillator Frequency 0 12 0 24 MHz

t

CLCL

Clock Period 83.3 41.6 ns

t

CHCX

High Time 30 15 ns

t

CLCX

Low Time 30 15 ns

t

CLCH

Rise Time 20 20 ns

t

CHCL

Fall Time 20 20 ns

20. Serial Port Timing: Shift Register Mode Test Conditions

V

CC

= 5.0V 20%; Load Capacitance = 80 pF

Symbol Parameter

12 MHz Osc Variable Oscillator

Units Min Max Min Max

t

XLXL

Serial Port Clock Cycle Time 1.0 12 t

CLCL

s

t

QVXH

Output Data Setup to Clock Rising Edge 700 10 t

CLCL

-133 ns

t

XHQX

Output Data Hold after Clock Rising Edge 50 2 t

CLCL

-117 ns

t

XHDX

Input Data Hold after Clock Rising Edge 0 0 ns

t

XHDV

Clock Rising Edge to Input Data Valid 700 10 t

CLCL

-133 ns

14

0368HMICRO6/08

AT89C2051

21. Shift Register Mode Timing Waveforms

22. AC Testing Input/Output Waveforms

(1)

Note: 1. AC Inputs during testing are driven at V

CC

- 0.5V for a logic 1 and 0.45V for a logic 0. Timing measurements are made at V

IH

min. for a logic 1 and V

IL

max. for a logic 0.

23. Float Waveforms

(1)

Note: 1. For timing purposes, a port pin is no longer floating when a 100 mV change from load voltage occurs. A port pin begins to

float when 100 mV change from the loaded V

OH

/V

OL

level occurs.

15

0368HMICRO6/08

AT89C2051

24. I

CC

(Active Mode) Measurements

25. I

CC

(Idle Mode) Measurements

26. I

CC

(Power Down Mode) Measurements

AT89C2051

TYPICAL ICC - ACTIVE(85C)

0

5

10

15

20

0 6 12 18 24

FREQUENCY (MHz)

I

C

C

m

A

Vcc=6.0V

Vcc=5.0V

Vcc=3.0V

AT89C2051

TYPICAL ICC - IDLE (85C)

0

1

2

3

0 3 6 9 12

FREQUENCY (MHz)

I

C

C

m

A

Vcc=6.0V

Vcc=5.0V

Vcc=3.0V

AT89C2051

TYPICAL ICC vs. VOLTAGE- POWER DOWN (85C)

0

5

10

15

20

3.0V 4.0V 5.0V 6.0V

Vcc VOLTAGE

I

C

C

A

Notes: 1. XTAL1 tied to GND

2. P.1.0 and P1.1 = V

CC

or GND

3. Lock bits programmed

16

0368HMICRO6/08

AT89C2051

27. Ordering Information

27.1 Green Package Option (Pb/Halide-free)

Speed

(MHz)

Power

Supply Ordering Code Package Operation Range

12 2.7V to 6.0V

AT89C2051-12PU

AT89C2051-12SU

20P3

20S

Industrial

(-40 C to 85 C)

24 4.0V to 6.0V

AT89C2051-24PU

AT89C2051-24SU

20P3

20S

Industrial

(-40 C to 85 C)

Package Type

20P3 20-lead, 0.300 Wide, Plastic Dual In-line Package (PDIP)

20S 20-lead, 0.300 Wide, Plastic Gull Wing Small Outline (SOIC)

17

0368HMICRO6/08

AT89C2051

28. Package Information

28.1 20P3 PDIP

2325 Orchard Parkway

San Jose, CA 95131

TITLE DRAWING NO.

R

REV.

20P3, 20-lead (0.300"/7.62 mm Wide) Plastic Dual

Inline Package (PDIP)

D 20P3

1/23/04

PIN

1

E1

A1

B

E

B1

C

L

SEATING PLANE

A

D

e

eB

eC

COMMON DIMENSIONS

(Unit of Measure = mm)

SYMBOL MIN NOM MAX NOTE

A 5.334

A1 0.381

D 24.892 26.924 Note 2

E 7.620 8.255

E1 6.096 7.112 Note 2

B 0.356 0.559

B1 1.270 1.551

L 2.921 3.810

C 0.203 0.356

eB 10.922

eC 0.000 1.524

e 2.540 TYP

Notes: 1. This package conforms to JEDEC reference MS-001, Variation AD.

2. Dimensions D and E1 do not include mold Flash or Protrusion.

Mold Flash or Protrusion shall not exceed 0.25 mm (0.010").

18

0368HMICRO6/08

AT89C2051

28.2 20S SOIC

0368HMICRO6/08

Headquarters International

Atmel Corporation

2325 Orchard Parkway

San Jose, CA 95131

USA

Tel: 1(408) 441-0311

Fax: 1(408) 487-2600

Atmel Asia

Room 1219

Chinachem Golden Plaza

77 Mody Road Tsimshatsui

East Kowloon

Hong Kong

Tel: (852) 2721-9778

Fax: (852) 2722-1369

Atmel Europe

Le Krebs

8, Rue Jean-Pierre Timbaud

BP 309

78054 Saint-Quentin-en-

Yvelines Cedex

France

Tel: (33) 1-30-60-70-00

Fax: (33) 1-30-60-71-11

Atmel Japan

9F, Tonetsu Shinkawa Bldg.

1-24-8 Shinkawa

Chuo-ku, Tokyo 104-0033

Japan

Tel: (81) 3-3523-3551

Fax: (81) 3-3523-7581

Product Contact

Web Site

www.atmel.com

Technical Support

mcu@atmel.com

Sales Contact

www.atmel.com/contacts

Literature Requests

www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any

intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMELS TERMS AND CONDI-

TIONS OF SALE LOCATED ON ATMELS WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY

WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR

PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-

TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF

THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no

representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications

and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided

otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmels products are not intended, authorized, or warranted for use

as components in applications intended to support or sustain life.

2008 Atmel Corporation. All rights reserved. Atmel

, logo and combinations thereof, and others are registered trademarks or trademarks of

Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Das könnte Ihnen auch gefallen

- At89c2051 Data SheetDokument44 SeitenAt89c2051 Data SheetRavi AhirwarNoch keine Bewertungen

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Von EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Noch keine Bewertungen

- 8-Bit Microcontroller With 2K Bytes Flash AT89C2051: FeaturesDokument24 Seiten8-Bit Microcontroller With 2K Bytes Flash AT89C2051: FeaturesVibhor KaushikNoch keine Bewertungen

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Von EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Noch keine Bewertungen

- 8-Bit Microcontroller With 4K Bytes Flash AT89C4051: FeaturesDokument18 Seiten8-Bit Microcontroller With 4K Bytes Flash AT89C4051: FeaturesAri SoerjantoNoch keine Bewertungen

- At89c2051 PDFDokument16 SeitenAt89c2051 PDFNasim KhanNoch keine Bewertungen

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142Von EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142Noch keine Bewertungen

- 8-Bit Microcontroller With 2K Bytes Flash AT89C2051: FeaturesDokument15 Seiten8-Bit Microcontroller With 2K Bytes Flash AT89C2051: FeaturesTrần Trung HiếuNoch keine Bewertungen

- 8-Bit Microcontroller With 2K Bytes Flash AT89C2051: FeaturesDokument14 Seiten8-Bit Microcontroller With 2K Bytes Flash AT89C2051: FeaturesMinhdung PhanNoch keine Bewertungen

- 8-Bit Microcontroller With 2K Bytes Flash AT89C2051: FeaturesDokument15 Seiten8-Bit Microcontroller With 2K Bytes Flash AT89C2051: FeaturesGomzalez Bin GembozNoch keine Bewertungen

- AT89C2051 Traffic Light ControllerDokument39 SeitenAT89C2051 Traffic Light ControllerNagesh RayNoch keine Bewertungen

- 8-Bit Microcontroller With 2K/4K Bytes Flash AT89S2051 AT89S4051Dokument46 Seiten8-Bit Microcontroller With 2K/4K Bytes Flash AT89S2051 AT89S4051Yoga Dwi CahyonoNoch keine Bewertungen

- Atmel PPT 100718104611 Phpapp01Dokument31 SeitenAtmel PPT 100718104611 Phpapp01Vj BhaskarNoch keine Bewertungen

- At 89c2051 DataDokument20 SeitenAt 89c2051 Datarangana rathnayakaNoch keine Bewertungen

- 89s51 DatasheetDokument27 Seiten89s51 DatasheetazizboysNoch keine Bewertungen

- AT89C51 MicrocontrollerDokument8 SeitenAT89C51 MicrocontrollerSaroj TimsinaNoch keine Bewertungen

- AT89C51Dokument15 SeitenAT89C51vaalginNoch keine Bewertungen

- 89s52 Micro ControllerDokument14 Seiten89s52 Micro ControllerThanga PazhamNoch keine Bewertungen

- Automatic Speed BreakerDokument69 SeitenAutomatic Speed BreakerRohitesh KumarNoch keine Bewertungen

- Cetpa Infotech Pvt. LTD: Department of Embedded SystemDokument42 SeitenCetpa Infotech Pvt. LTD: Department of Embedded SystemKapil VijNoch keine Bewertungen

- 8-Bit Microcontroller With 8K Bytes In-System Programmable Flash AT89S52Dokument38 Seiten8-Bit Microcontroller With 8K Bytes In-System Programmable Flash AT89S52api-284887027Noch keine Bewertungen

- 8-Bit Microcontroller With 4K Bytes In-System Programmable Flash AT89S51Dokument30 Seiten8-Bit Microcontroller With 4K Bytes In-System Programmable Flash AT89S51Arif Febrian MuhammadNoch keine Bewertungen

- Gas Leakage Alerting System in IndustriesDokument44 SeitenGas Leakage Alerting System in IndustriesGanesan S BENoch keine Bewertungen

- At89c55wd DatasheetDokument37 SeitenAt89c55wd DatasheetkwithnallNoch keine Bewertungen

- EM785830AA: 8-Bit Micro-ControllerDokument43 SeitenEM785830AA: 8-Bit Micro-ControllerboleplNoch keine Bewertungen

- 89c51 MCUDokument16 Seiten89c51 MCUyuvakiraniNoch keine Bewertungen

- Part 1Dokument31 SeitenPart 1SarthakGuptaNoch keine Bewertungen

- 8-Bit Microcontroller With 4K Bytes Quickflash Memory At80F51Dokument5 Seiten8-Bit Microcontroller With 4K Bytes Quickflash Memory At80F51RAJKUMARNoch keine Bewertungen

- 8-Bit Microcontroller With 12K Bytes Flash AT89S53: FeaturesDokument35 Seiten8-Bit Microcontroller With 12K Bytes Flash AT89S53: FeaturesOpeolu VictoryNoch keine Bewertungen

- AT89C55Dokument24 SeitenAT89C55Yerson CrespoNoch keine Bewertungen

- Datasheet Atmega 161 PDokument159 SeitenDatasheet Atmega 161 PprincebahariNoch keine Bewertungen

- Industrial Fault Indication System With Over Voltage Over TemperatureDokument46 SeitenIndustrial Fault Indication System With Over Voltage Over Temperaturedivanshu16decNoch keine Bewertungen

- 8-Bit Microcontroller With 8K Bytes Flash AT89C52: FeaturesDokument22 Seiten8-Bit Microcontroller With 8K Bytes Flash AT89C52: FeaturesFabian OrtuzarNoch keine Bewertungen

- AT89S2051Dokument46 SeitenAT89S2051Hr ReferralNoch keine Bewertungen

- AT89s52 MicrocontrollerDokument13 SeitenAT89s52 MicrocontrollerVishnu VardhanNoch keine Bewertungen

- Frequency MeterDokument48 SeitenFrequency MeterSumit AgarwalNoch keine Bewertungen

- Avr AtmegaDokument309 SeitenAvr AtmegakcraussNoch keine Bewertungen

- Distributed byDokument26 SeitenDistributed byMt GrNoch keine Bewertungen

- AT89s52 MicrocontrollerDokument27 SeitenAT89s52 MicrocontrollerDinesh DspNoch keine Bewertungen

- Cetpa Infotech Pvt. LTD: Department of Embedded SystemDokument42 SeitenCetpa Infotech Pvt. LTD: Department of Embedded SystemSiddharthRawatNoch keine Bewertungen

- Microcontroller Lab Manual With Arduino Programe PDFDokument63 SeitenMicrocontroller Lab Manual With Arduino Programe PDFTejasaiNoch keine Bewertungen

- 80C51 Family Derivatives: 8XC552/562 OverviewDokument60 Seiten80C51 Family Derivatives: 8XC552/562 OverviewMiguel MacpNoch keine Bewertungen

- AT89S52Dokument20 SeitenAT89S52Bhargav GoudNoch keine Bewertungen

- Datasheet 1ATMEL MicrocontrolerDokument186 SeitenDatasheet 1ATMEL Microcontrolerida_susantiNoch keine Bewertungen

- Metal Gas Detec RoboDokument37 SeitenMetal Gas Detec RoboVijay SaiNoch keine Bewertungen

- At89lp2052 PDFDokument93 SeitenAt89lp2052 PDFRisnoHamidNoch keine Bewertungen

- AT89S52Dokument19 SeitenAT89S52Nikhith ReddyNoch keine Bewertungen

- MicroDokument17 SeitenMicroNithish RNoch keine Bewertungen

- Doc-A.14-Text Editor On A LCD Using At89c51 Micro Controller and KeyboardDokument48 SeitenDoc-A.14-Text Editor On A LCD Using At89c51 Micro Controller and KeyboardRockson Kwame AgyemanNoch keine Bewertungen

- 8-Bit Microcontroller With 8K Bytes In-System Programmable Flash AT89S52Dokument30 Seiten8-Bit Microcontroller With 8K Bytes In-System Programmable Flash AT89S52Dinesh GodseNoch keine Bewertungen

- Atmel 2513 8 Bit AVR Microntroller ATmega162 DatasheetDokument324 SeitenAtmel 2513 8 Bit AVR Microntroller ATmega162 DatasheetarekkontrakanNoch keine Bewertungen

- Automatic Room Light ControllerDokument36 SeitenAutomatic Room Light Controllerlove2honney100% (1)

- 8-Bit Microcontroller With 16K Bytes In-System Programmable Flash Atmega162 Atmega162VDokument323 Seiten8-Bit Microcontroller With 16K Bytes In-System Programmable Flash Atmega162 Atmega162VszakiahsdNoch keine Bewertungen

- 80C51 8-Bit Microcontroller Family: 4K/128 Otp/Rom/Romless, 8 Channel 8 Bit A/D, Watchdog TimerDokument28 Seiten80C51 8-Bit Microcontroller Family: 4K/128 Otp/Rom/Romless, 8 Channel 8 Bit A/D, Watchdog Timerchecker0815Noch keine Bewertungen

- MICROCONTROLLERDokument5 SeitenMICROCONTROLLERPuja TiwariNoch keine Bewertungen

- Simulation Lab File - EC 708Dokument25 SeitenSimulation Lab File - EC 708Gautam SonkerNoch keine Bewertungen

- ATmega16A Datasheet SummaryDokument19 SeitenATmega16A Datasheet SummaryalgiteanNoch keine Bewertungen

- Sony-Pcg-5k2t SCHEMATICDokument35 SeitenSony-Pcg-5k2t SCHEMATICvideosonNoch keine Bewertungen

- LED Matrix Using Shift RegistersDokument20 SeitenLED Matrix Using Shift RegistersPa RasNoch keine Bewertungen

- MSP430 iSMAİL KAYA SORULARDokument8 SeitenMSP430 iSMAİL KAYA SORULAREmin DokuzNoch keine Bewertungen

- Zero4U UserManualDokument12 SeitenZero4U UserManualAnton MeierNoch keine Bewertungen

- Indian Institute of Technology Goa: EE 232 Digital Circuits and LabDokument1 SeiteIndian Institute of Technology Goa: EE 232 Digital Circuits and LabVishal SharmaNoch keine Bewertungen

- Computer Architecture and Organization 8th EditionDokument18 SeitenComputer Architecture and Organization 8th EditionSana HaqNoch keine Bewertungen

- Module 5 - Cisc Vs RiscDokument3 SeitenModule 5 - Cisc Vs RiscStefania PopescuNoch keine Bewertungen

- PLACA MADRE Manual Ga-f2a55m-Ds2 eDokument48 SeitenPLACA MADRE Manual Ga-f2a55m-Ds2 eMichelNoch keine Bewertungen

- DSP Processors and ArchitecturesDokument1 SeiteDSP Processors and ArchitecturesK S RajasekharNoch keine Bewertungen

- HP Katalog KonsumerDokument37 SeitenHP Katalog KonsumersepNoch keine Bewertungen

- MT6737 LTE Smartphone Application Processor Functional Specification V1.0Dokument288 SeitenMT6737 LTE Smartphone Application Processor Functional Specification V1.0copslockNoch keine Bewertungen

- Sheet7 SolutionDokument11 SeitenSheet7 SolutionMd. Imran AhmedNoch keine Bewertungen

- UG0586 User Guide RTG4 FPGA Clocking ResourcesDokument82 SeitenUG0586 User Guide RTG4 FPGA Clocking ResourcesNguyen Van ToanNoch keine Bewertungen

- Binary Logic Gates: Prepared By: NSZ FSG, Uitm PahangDokument64 SeitenBinary Logic Gates: Prepared By: NSZ FSG, Uitm PahangMuhammad Azizi100% (1)

- Rds P32mcuDokument3 SeitenRds P32mcupablomendivilNoch keine Bewertungen

- Pic 16 F 616Dokument172 SeitenPic 16 F 616Maneesh BakaleNoch keine Bewertungen

- CNE302 Computer Organization and Architecture: Lecture 01 - Introduction InstructorDokument39 SeitenCNE302 Computer Organization and Architecture: Lecture 01 - Introduction InstructorNour Eldeen MohammedNoch keine Bewertungen

- Oracle Server X6-2: Product OverviewDokument6 SeitenOracle Server X6-2: Product OverviewGrace ValenciaNoch keine Bewertungen

- Practical Low Power Digital Vlsi DesignDokument11 SeitenPractical Low Power Digital Vlsi DesignkalaiyarasiNoch keine Bewertungen

- MIPS SC ExtendedDokument39 SeitenMIPS SC ExtendedVimoli MehtaNoch keine Bewertungen

- AsusDokument49 SeitenAsusGikcoklat AmuntaiNoch keine Bewertungen

- Watchdog Timer On The PIC18F4525Dokument6 SeitenWatchdog Timer On The PIC18F4525Carlos LMNoch keine Bewertungen

- New Microsoft Word DocumentDokument33 SeitenNew Microsoft Word DocumentTsy Less DahalNoch keine Bewertungen

- Testing and Troubleshooting 2Dokument4 SeitenTesting and Troubleshooting 2Ian Neil LaenoNoch keine Bewertungen

- 5569 - Print Out SEL 351A Transformador Lado ATDokument4 Seiten5569 - Print Out SEL 351A Transformador Lado ATAlex IgorNoch keine Bewertungen

- Mobile Gm45 Intel Gs45 Gl40 Express Chipsets BriefDokument4 SeitenMobile Gm45 Intel Gs45 Gl40 Express Chipsets BriefUsman034Noch keine Bewertungen

- Static Crosstalk-Noise AnalysisDokument127 SeitenStatic Crosstalk-Noise AnalysisNguyễn Hưng Idiots100% (1)

- Lenovo ThinkCentre by Bizgram Whatsapp 87776955 PDFDokument5 SeitenLenovo ThinkCentre by Bizgram Whatsapp 87776955 PDFBizgram AsiaNoch keine Bewertungen

- CISSP All-in-One Exam Guide, Ninth EditionVon EverandCISSP All-in-One Exam Guide, Ninth EditionBewertung: 5 von 5 Sternen5/5 (1)

- CompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Von EverandCompTIA A+ Complete Review Guide: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Bewertung: 5 von 5 Sternen5/5 (2)

- iPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsVon EverandiPhone 14 Guide for Seniors: Unlocking Seamless Simplicity for the Golden Generation with Step-by-Step ScreenshotsBewertung: 5 von 5 Sternen5/5 (5)

- Chip War: The Quest to Dominate the World's Most Critical TechnologyVon EverandChip War: The Quest to Dominate the World's Most Critical TechnologyBewertung: 4.5 von 5 Sternen4.5/5 (230)

- CompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Von EverandCompTIA A+ Certification All-in-One Exam Guide, Eleventh Edition (Exams 220-1101 & 220-1102)Bewertung: 5 von 5 Sternen5/5 (2)

- iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Von EverandiPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]Bewertung: 5 von 5 Sternen5/5 (5)

- Unlock Any Roku Device: Watch Shows, TV, & Download AppsVon EverandUnlock Any Roku Device: Watch Shows, TV, & Download AppsNoch keine Bewertungen

- Cyber-Physical Systems: Foundations, Principles and ApplicationsVon EverandCyber-Physical Systems: Foundations, Principles and ApplicationsHoubing H. SongNoch keine Bewertungen

- Chip War: The Fight for the World's Most Critical TechnologyVon EverandChip War: The Fight for the World's Most Critical TechnologyBewertung: 4.5 von 5 Sternen4.5/5 (82)

- The comprehensive guide to build Raspberry Pi 5 RoboticsVon EverandThe comprehensive guide to build Raspberry Pi 5 RoboticsNoch keine Bewertungen

- Computer Science: A Concise IntroductionVon EverandComputer Science: A Concise IntroductionBewertung: 4.5 von 5 Sternen4.5/5 (14)

- Arduino and Raspberry Pi Sensor Projects for the Evil GeniusVon EverandArduino and Raspberry Pi Sensor Projects for the Evil GeniusNoch keine Bewertungen

- CompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Von EverandCompTIA A+ Complete Practice Tests: Core 1 Exam 220-1101 and Core 2 Exam 220-1102Noch keine Bewertungen

- How To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsVon EverandHow To Market Mobile Apps: Your Step By Step Guide To Marketing Mobile AppsNoch keine Bewertungen

- Raspberry PI: Learn Rasberry Pi Programming the Easy Way, A Beginner Friendly User GuideVon EverandRaspberry PI: Learn Rasberry Pi Programming the Easy Way, A Beginner Friendly User GuideNoch keine Bewertungen

- CompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Von EverandCompTIA A+ Complete Review Guide: Exam Core 1 220-1001 and Exam Core 2 220-1002Bewertung: 5 von 5 Sternen5/5 (1)

- The User's Directory of Computer NetworksVon EverandThe User's Directory of Computer NetworksTracy LaqueyNoch keine Bewertungen

- Cancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionVon EverandCancer and EMF Radiation: How to Protect Yourself from the Silent Carcinogen of ElectropollutionBewertung: 5 von 5 Sternen5/5 (2)

- iPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XVon EverandiPhone X Hacks, Tips and Tricks: Discover 101 Awesome Tips and Tricks for iPhone XS, XS Max and iPhone XBewertung: 3 von 5 Sternen3/5 (2)

- Debugging Embedded and Real-Time Systems: The Art, Science, Technology, and Tools of Real-Time System DebuggingVon EverandDebugging Embedded and Real-Time Systems: The Art, Science, Technology, and Tools of Real-Time System DebuggingBewertung: 5 von 5 Sternen5/5 (1)

- Creative Selection: Inside Apple's Design Process During the Golden Age of Steve JobsVon EverandCreative Selection: Inside Apple's Design Process During the Golden Age of Steve JobsBewertung: 4.5 von 5 Sternen4.5/5 (49)

- Samsung Galaxy S22 Ultra User Guide For Beginners: The Complete User Manual For Getting Started And Mastering The Galaxy S22 Ultra Android PhoneVon EverandSamsung Galaxy S22 Ultra User Guide For Beginners: The Complete User Manual For Getting Started And Mastering The Galaxy S22 Ultra Android PhoneNoch keine Bewertungen

![iPhone Unlocked for the Non-Tech Savvy: Color Images & Illustrated Instructions to Simplify the Smartphone Use for Beginners & Seniors [COLOR EDITION]](https://imgv2-2-f.scribdassets.com/img/audiobook_square_badge/728318688/198x198/f3385cbfef/1715524978?v=1)