Beruflich Dokumente

Kultur Dokumente

Design

Hochgeladen von

Alvin Jan Yap0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

24 Ansichten21 Seitenaw

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenaw

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

24 Ansichten21 SeitenDesign

Hochgeladen von

Alvin Jan Yapaw

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 21

Combinational Logic Design Process

Create truth table from specification

Generate K-maps & obtain logic equations

Draw logic diagram (sharing common gates)

Simulate circuit for design verification

Debug & fix problems when output is incorrect Debug & fix problems when output is incorrect

Check truth table against K-map population

Check K-map groups against logic equation product terms

Check logic equations against schematic Check logic equations against schematic

Circuit optimization for area and/or performance

Analyze verified circuit for optimization metric Analyze verified circuit for optimization metric

G, G

IO

, G

del

, P

del

Use Boolean postulates & theorems

Re-simulate & verify optimized design

C. E. Stroud ELEC 4200 1

Re-simulate & verify optimized design

K-mapping & Minimization Steps K-mapping & Minimization Steps

Step 1: generate K-map

Put a 1 in all specified minterms

Put a 0 in all other boxes (optional)

Step 2: group all adjacent 1s without including any 0s

All groups (aka prime implicants) must be rectangular and All groups (aka prime implicants) must be rectangular and

contain a power-of-2 number of 1s

1, 2, 4, 8, 16, 32,

An essential group (aka essential prime implicant) contains An essential group (aka essential prime implicant) contains

at least 1 minterm not included in any other groups

A given minterm may be included in multiple groups

Step 3: define product terms using variables common to Step 3: define product terms using variables common to

all minterms in group

Step 4: sum all essential groups plus a minimal set of

remaining groups to obtain a minimum SOP

C. E. Stroud ELEC 4200 2

remaining groups to obtain a minimum SOP

K-map Minimization Goals K-map Minimization Goals

Larger groups:

Smaller product terms Smaller product terms

Fewer variables in common

Smaller AND gates

Alternate method:

Group 0s

Smaller AND gates

In terms of number of inputs

Fewer groups:

Group 0s

Could produce

fewer and/or

smaller product

Fewer groups:

Fewer product terms

Fewer AND gates

smaller product

terms

Invert output

Use NOR instead

Smaller OR gate

In terms of number of inputs

Use NOR instead

of OR gate

C. E. Stroud ELEC 4200 3

Circuit Analysis Circuit Analysis

We can implement different circuits for same logic function that are

functionally equivalent (produce the correct output response for all

input values) input values)

Which implementation is the best?

Depends on design goals and criteria

Area analysis Area analysis

Number of gates, G (most commonly used)

Number of gate inputs and outputs, G

IO

(more accurate)

IO

Bigger gates take up more area

Performance analysis (worst case path from inputs to outputs)

Number of gates in worst case path from input to output, G

del

Number of gates in worst case path from input to output, G

del

More accurate delay measurement per gate

Propagation delay = intrinsic (internal) delay + extrinsic (external) delay

Relative prop delay, P

del

= # inputs to gate (intrinsic) + # loads (extrinsic)

C. E. Stroud ELEC 4200 4

Relative prop delay, P

del

= # inputs to gate (intrinsic) + # loads (extrinsic)

Circuit Analysis Example

From previous example: From previous example:

Z=(A+B)C+ABC

# gates: G = 7

A

A+B

B

2

# gates: G = 7

# gate I/O: G

IO

= 19

Gate delay: G

del

= 4

Z

B

C

A+B

(A+B)C

B

A

2

2

1+1

2+1

2+1

2+0

Gate delay: G

del

= 4

worst case path: BZ

Prop delay: P

del

= 12

ABC

C

1+1

1+1

3+1

2+0

Prop delay: P

del

= 12

worst case path: BZ

C. E. Stroud ELEC 4200 5

Design Verification Guidelines Design Verification Guidelines

Use all audits and analysis aids possible to help find potential design bugs

Investigate and correct all errors/warnings

Simulate thoroughly but use stimuli that eat their way into the design Simulate thoroughly but use stimuli that eat their way into the design

testing one function at a time

more important for complex circuits

When circuit doesnt work, see what works and what doesnt to narrow

down the search space for the problem down the search space for the problem

Which outputs work

Which outputs fail and under what conditions

Monitor lots of internal nodes Monitor lots of internal nodes

Additional simulations (with different vectors) can be helpful

Remember debugging is just solving out a puzzle

Also if something doesnt look right, stop and check it out

Dont overlook potential bugs Dont overlook potential bugs

Always re-run audits and simulation after correcting any problem (or after

any changes)

Another bug could be lurking, or

The fix may have messed up something else

C. E. Stroud ELEC 4200 6

The fix may have messed up something else

Sequential Logic Design Steps

Derive circuit state diagram from design specs Derive circuit state diagram from design specs

Create state table

Choose flip-flops (D, T, SR, JK) Choose flip-flops (D, T, SR, JK)

Create circuit excitation table

use flip-flop excitation tables use flip-flop excitation tables

Construct K-maps for:

flip-flop inputs flip-flop inputs

primary outputs

Obtain minimized SOP equations

Draw logic diagram

Simulate to verify design & debug as needed

C. E. Stroud ELEC 4200 7

Perform circuit analysis & logic optimization

Flip-Flop Excitation Tables & State

Diagrams Diagrams

Q Q+ D T S R J K

0

1

D=1

1

0

Q Q+ D T S R J K

0 0 0 0 0 X 0 X

0 1 1 1 1 0 1 X

0

1

0

1

0

T=1

0 1 1 1 1 0 1 X

1 0 0 1 0 1 X 1

1 1 1 0 X 0 X 0

0

1

T=1

0

0

1

SR=10 JK=1X

0

1

01

X0

0X

0

1

X1

X0

0X

C. E. Stroud ELEC 4200 8

01 X1

Sequential Design Example Sequential Design Example

Design a 3-bit gray code counter with

active low synchronous reset (R) active low synchronous reset (R)

1

R=0

0

State Diagram

Inputs

R

Current state

(X Y Z)

Next state

(X Y Z)

0 XXX 000

State order:

X Y Z

0

001

011

000

100

1

1

R=1

R=0

0

0 XXX 000

1 000 001

1 001 011

1 010 110

X Y Z

101

011

010

100

1 1

0

0

0

0

1 010 110

1 011 010

1 100 000

1 101 100

101 010

111 110

1

1

1

0

0

1 101 100

1 110 111

1 111 101

C. E. Stroud ELEC 4200 9

111 110

1

State Table

3-bit Gray Code Counter

Inputs Current state Next state QX QY QZ

Choose flip-

flops:

Let X be a

Inputs

R

Current state

(X Y Z)

Next state

(X Y Z)

QX

Jx Kx

QY

Dy

QZ

Sz Rz

0 X X X 0 0 0 0 1 0 0 1

1 0 0 0 0 0 1 0 X 0 1 0

Let X be a

JK

Let Y be a D

Let Z be a

1 0 0 0 0 0 1 0 X 0 1 0

1 0 0 1 0 1 1 0 X 1 X 0

1 0 1 0 1 1 0 1 X 1 0 X

1 0 1 1 0 1 0 0 X 1 0 1

Let Z be a

SR

Create circuit

excitation

1 0 1 1 0 1 0 0 X 1 0 1

1 1 0 0 0 0 0 X 1 0 0 X

1 1 0 1 1 0 0 X 0 0 0 1

1 1 1 0 1 1 1 X 0 1 1 0

excitation

table

1 1 1 0 1 1 1 X 0 1 1 0

1 1 1 1 1 0 1 X 0 0 X 0

C. E. Stroud ELEC 4200 10

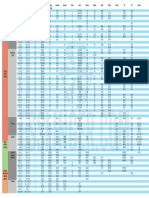

3-bit Gray Code Counter (cont)

Generate K-Maps & obtain minimized SOPs

00 01 11 10

00

RX

YZ

00 01 11 10

00

RX

YZ

00 01 11 10

00

RX

YZ

X 1

00

01

11

X X X X

00

01

11

1

00

01

11

YZ

X 1

1 X

11

10

YZ

X X X X

1

11

10

1

1 1 1

11

10

Jx = RYZ Dy = RYZ + RXZ Sz = RXY + RXY

1 1 1 1

1 1 1 1

00 01 11 10

00

01

RX

YZ

1 1 1 1

1 1 1 1

00 01 11 10

00

01

RX

YZ

Further reductions:

Rz = R + XY 1 1 1 1

1 0 0 0

X X X X

01

11

10

1 1 1 1

X 1

1 X

01

11

10

Rz = R + XY

Sz = R(XY)

= (R + XY)

C. E. Stroud ELEC 4200 11

X X X X 1 X

Kx = R + YZ Rz = R + XY + XY

= Rz

3-bit Gray Code Counter (cont) 3-bit Gray Code Counter (cont)

Logic diagram

Then design

Jx

X

Kx

Y

Z

Then design

verification via

logic simulation

X

Clk

Kx

Dy

Y

Z

Y

Z

logic simulation

Debug as needed

to obtain

working circuit

Dy

Y

Y

Clk

Z

X

working circuit

Update logic

diagram, logic

equations, etc. to

Sz

Z

Rz

Clk

R

X

X

Z

equations, etc. to

reflect fixes

Z

Clk

Rz

X

Y

C. E. Stroud ELEC 4200 12

Sequential Logic Models Sequential Logic Models

Huffman model consists

of two types:

Primary

Inputs

Primary

Outputs

Comb

Logic

of two types:

Mealy model (aka Mealy

machine)

Outputs are function inputs

Next

State

Current

State

Logic

Flip-

Flips

Outputs are function inputs

and current state

Outputs can change when

inputs change or when

current state changes

State Flips

Primary

Primary Output

only for

Mealy

current state changes

Moore model (aka Moore

machine)

Outputs are function of

Inputs

Primary

Outputs

Output

Logic

Next State

Outputs are function of

current state only

Outputs can change only

when current state

changes

Next

State

Current

State

Flip-

Flips

Next State

Logic

C. E. Stroud ELEC 4200 13

changes

State

State

Flips

Mealy & Moore State Diagrams Mealy & Moore State Diagrams

Mealy model

Outputs associated

00

1/1

Input

/

State

order

XY

Outputs associated

with state transition

Output values shown

00

0/1

0/1

0/0

1/1

1/1

/

Output

XY

Output values shown

with inputs

Moore model

10

01

0/0

1/0

States

Outputs associated

with states only

Output values shown

00/1

0

0

1

1

States

/

Output

Output values shown

with states

10/0

01/0

0

0

0

C. E. Stroud ELEC 4200 14

1

Mealy & Moore State Tables Mealy & Moore State Tables

In X Y X

+

Y

+

D

X

D

Y

O

Mealy

O

Moore

0 0 0 0 1 0 1 1 1

00

1/1

0 0 0 0 1 0 1 1 1

0 0 1 1 0 1 0 0 0

0 1 0 0 0 0 0 1 0

00

10

01

0/1

0/1

0/0

1/1

1/1

0 1 0 0 0 0 0 1 0

1 0 0 1 0 1 0 1 1

10

01

0/0

1/0

1 0 1 0 0 0 0 1 0

1 1 0 0 1 0 1 0 0

00/1

0

0

1

1

0 1 1 X X X X X X

10/0

01/0

0

0

0

1

Note: next state (next state logic) is same for

C. E. Stroud ELEC 4200 15

1

Note: next state (next state logic) is same for

both Mealy & Moore only output is different

Mealy & Moore Design Examples Mealy & Moore Design Examples

X Y

X Y

In this example the Dx and Dy circuits are the same for both Mealy and Moore

But the outputs circuits are different with the Moore being a function of X and Y only

00 01 11 10

0 0 1 X 0

1 1 0 X 0

In

X Y

00 01 11 10

0 1 0 X 1

1 1 1 X 0

In

X Y

1 1 0 X 0

D

X

= InY + InXY

X Y

1 1 1 X 0

X Y

O

Mealy

= InY + InX

00 01 11 10

0 1 0 X 0

In

X Y

00 01 11 10

0 1 0 X 0

In

X Y

1 0 0 X 1

D

Y

= InX + InXY

1 1 0 X 0

O

Moore

= XY

C. E. Stroud ELEC 4200 16

Mealy & Moore Design Examples Mealy & Moore Design Examples

D

X

= InY + InXY

D = InX + InXY

O

Mealy

= InY + InX O

Moore

= XY

D

Y

= InX + InXY

X

Y

In

X

Y

In

X

Y

X

X

X

Y

X

X

Y

Y

X

Y

X

Y

Y

X

Y

X

Clk Clk

Y

X

O

Moore

Y

X

O

Mealy

Clk Clk

C. E. Stroud ELEC 4200 17

X

Note: O

Mealy

is a function of In but O

Moore

is not a function of In

Flip-Flop Initialization Flip-Flop Initialization

Preset (aka set) => Q

+

= 1

Clear (aka reset) => Q

+

= 0

Some flip-flops have:

Typical logic symbol

with active high preset

and active low clear

Cannot determine sync

Some flip-flops have:

Both preset and clear (set and reset)

A preset or a clear

D

Q

Pre

Cannot determine sync

or async from symbol

A preset or a clear

Neither (JK & SR flops have set/reset functions)

Preset and/or clear can be

Active high or active low

D

Clk

Q

Q

Active high or active low

Synchronous => with respect to active edge of clock

Asynchronous => independent of clock edges

Initialization important for:

Clr

Initialization important for:

logic simulation to remove undefined logic values

2, 3, U, etc.

system operation to put system in a known state

C. E. Stroud ELEC 4200 18

system operation to put system in a known state

Synchronous vs. Asynchronous Synchronous vs. Asynchronous

Synchronous =>

states of memory

D

Q

Pre

Example: assume

active high sync

states of memory

elements change

only with respect to

active edge of clock

D

Clk

Q

Q

active high sync

preset

and active low

active edge of clock

Asynchronous =>

states of memory

elements can

Clr

async clear

Clk elements can

change without an

active edge of clock

Clk

D

Pre

Asynchronous

designs often have

timing problems

Pre

Clr

Q

C. E. Stroud ELEC 4200 19

Q

System-Level Timing System-Level Timing

System set-up time: P

del

+ P

bufi

+ t

su

- P

clk(min)

P

del

+ P

bufi

+ t

su

P

del

+ P

bufi

+ t

su

System hold time: t

h

+ P

clk

- P

del(min)

- P

bufi(min)

t

h

+ P

clk h clk

System clock-to-output: t

co

+ P

del

+ P

bufo

+ P

clk

Minimum times are difficult to guarantee

Typically assume 0 Typically assume 0

comb

logic

Data

comb

logic

Output

t

su

t

co

logic

P

del

Data

Clock

logic

P

del

Output

t

su

t

co

C. E. Stroud ELEC 4200 20

C

big

P

clk

System-Level Timing System-Level Timing

System set System set--up time: up time: PP

bufi bufi

+ + tt

su su(latch) (latch)

-- PP

clk clk(input)min (input)min

System hold time: System hold time: tt

hh(latch) (latch)

++ PP

clk clk(input) (input)

-- PP

bufi bufi(min) (min)

System hold time: System hold time: tt

hh(latch) (latch)

++ PP

clk clk(input) (input)

-- PP

bufi bufi(min) (min)

System clock System clock--to to--output: output: tt

co co

+ + PP

bufo bufo

++ PP

clk clk(output) (output)

Improvement techniques: Improvement techniques: Improvement techniques: Improvement techniques:

Re Re--clock signals onto/off clock signals onto/off subcircuit subcircuit, chip, PCB, or system , chip, PCB, or system

Fanout Fanout clock into input, main, and output clocks clock into input, main, and output clocks

00--hold hold--time latches on input signals time latches on input signals 00--hold hold--time latches on input signals time latches on input signals

comb

logic

Data

comb

logic

Output

logic

P

del

Data

Clock

logic

P

del

Output

LAT

en

C. E. Stroud ELEC 4200 21

C

big

P

clk

Das könnte Ihnen auch gefallen

- Basic Sequential Design Steps: Flip-Flop Inputs Primary OutputsDokument10 SeitenBasic Sequential Design Steps: Flip-Flop Inputs Primary OutputsAnkur SinghNoch keine Bewertungen

- sc554 2014 Lecture09Dokument34 Seitensc554 2014 Lecture09tharindu12Noch keine Bewertungen

- Notes 326 Set11Dokument16 SeitenNotes 326 Set11Dhanu ChettyNoch keine Bewertungen

- Review: Designing With FSM: Work Together WellDokument11 SeitenReview: Designing With FSM: Work Together Welljatanbhatt89100% (1)

- Review: Additional Boolean OperationsDokument25 SeitenReview: Additional Boolean OperationsthotalnNoch keine Bewertungen

- Sequential Circuit AnalysisDokument15 SeitenSequential Circuit AnalysisJeth Gato VestalNoch keine Bewertungen

- SopDokument7 SeitenSopNiranjan ReddyNoch keine Bewertungen

- Sequential Circuit DesignDokument28 SeitenSequential Circuit DesignNiranda PereraNoch keine Bewertungen

- M.D. BookDokument20 SeitenM.D. Bookjaved alamNoch keine Bewertungen

- So You Are at A Party: Lecture 1 - 1.1, 1.2Dokument8 SeitenSo You Are at A Party: Lecture 1 - 1.1, 1.2jhuma mukherjeeNoch keine Bewertungen

- Introduction To Digital Logic Design Appendix A of CO&A: Dr. FaragDokument22 SeitenIntroduction To Digital Logic Design Appendix A of CO&A: Dr. FaragXaid IbrahimNoch keine Bewertungen

- Cpe358/Cs381 Switching Theory and Logical Design Class 7Dokument55 SeitenCpe358/Cs381 Switching Theory and Logical Design Class 7Santhi SriNoch keine Bewertungen

- Sequential Logic Implementation: Models For Representing Sequential CircuitsDokument18 SeitenSequential Logic Implementation: Models For Representing Sequential CircuitsBrightNoch keine Bewertungen

- Sequential Circuits: Part 2: Implementation, Analysis & DesignDokument45 SeitenSequential Circuits: Part 2: Implementation, Analysis & Designrampravesh kumarNoch keine Bewertungen

- Chapter 4Dokument118 SeitenChapter 4Arham SiddiquiNoch keine Bewertungen

- EECS150 - Digital Design Outline: Lecture 2 - ReviewDokument6 SeitenEECS150 - Digital Design Outline: Lecture 2 - ReviewDuc DucNoch keine Bewertungen

- ECE 331 - Digital System Design: Derivation of State Graphs and State TablesDokument39 SeitenECE 331 - Digital System Design: Derivation of State Graphs and State TablesRizulNoch keine Bewertungen

- Cpe358/Cs381 Switching Theory and Logical Design Class 13Dokument53 SeitenCpe358/Cs381 Switching Theory and Logical Design Class 13Santhi SriNoch keine Bewertungen

- CHPT 4Dokument104 SeitenCHPT 4ahmad khanNoch keine Bewertungen

- CHPT 4Dokument104 SeitenCHPT 4HassnainNoch keine Bewertungen

- 07 DecodersDokument21 Seiten07 DecodersRafena17Noch keine Bewertungen

- Embedded Systems Design: A Unified Hardware/Software IntroductionDokument30 SeitenEmbedded Systems Design: A Unified Hardware/Software IntroductionNaresh Ks100% (1)

- Custom Single Purpose Processor DesignDokument24 SeitenCustom Single Purpose Processor DesignAar Kay GautamNoch keine Bewertungen

- Combinational and Sequential Circuits DesignDokument25 SeitenCombinational and Sequential Circuits DesignJadesh ChandaNoch keine Bewertungen

- Using Practical Examples in Teaching Digital Logic Design v5 PDFDokument14 SeitenUsing Practical Examples in Teaching Digital Logic Design v5 PDFJafar SadiqNoch keine Bewertungen

- Asic DesignDokument18 SeitenAsic DesignoumeiganNoch keine Bewertungen

- Combinational Logic Implementation Technologies: Hai Zhou ECE 303 Advanced Digital Design Spring 2002Dokument40 SeitenCombinational Logic Implementation Technologies: Hai Zhou ECE 303 Advanced Digital Design Spring 2002Aravind Ramesh100% (1)

- ASICandFPGA Finalco1andco2Dokument75 SeitenASICandFPGA Finalco1andco2Jallapally sai chandanaNoch keine Bewertungen

- Chapter01b - Intro To Digital Logic DesignDokument47 SeitenChapter01b - Intro To Digital Logic Designriel_ylayaNoch keine Bewertungen

- Digital Design Assignment 40%Dokument2 SeitenDigital Design Assignment 40%Obada Ar-ruzziNoch keine Bewertungen

- Generacion de Pseudo NumerosDokument19 SeitenGeneracion de Pseudo Numerosnicoletto8Noch keine Bewertungen

- Review: Additional Boolean OperationsDokument25 SeitenReview: Additional Boolean Operationsquickoffice_sqaNoch keine Bewertungen

- 4 Digital ElectronicsDokument29 Seiten4 Digital ElectronicsSwapnil PariharNoch keine Bewertungen

- Flip FlopsDokument5 SeitenFlip Flopsmanishbhardwaj8131Noch keine Bewertungen

- ECN 252 Lab 6 - Design of D Flip-Flop and CountersDokument2 SeitenECN 252 Lab 6 - Design of D Flip-Flop and CountersRUSHIL MOTWANINoch keine Bewertungen

- Modeling Simulation and System Engineering Lecture PDFDokument40 SeitenModeling Simulation and System Engineering Lecture PDFcemokszNoch keine Bewertungen

- Chapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State UniversityDokument6 SeitenChapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State Universitydemos2011Noch keine Bewertungen

- Unit 1: Synchronous Sequential NetworkDokument37 SeitenUnit 1: Synchronous Sequential Networkநட்ராஜ் நாதன்Noch keine Bewertungen

- Designing A Coffee Vending Machine ProjectDokument5 SeitenDesigning A Coffee Vending Machine ProjectWildan Fauzan Wfz100% (1)

- Chapter 3Dokument48 SeitenChapter 3Anonymous gML5pHNoch keine Bewertungen

- For Each Question Use Template in Student Database System!!!Dokument4 SeitenFor Each Question Use Template in Student Database System!!!Mehmethan Ayrım0% (1)

- DLD Unit 2 Combinational Circuits (2022)Dokument35 SeitenDLD Unit 2 Combinational Circuits (2022)Hritik KaulNoch keine Bewertungen

- Sequential Circuit Design Sequence RecognizerDokument4 SeitenSequential Circuit Design Sequence RecognizerKhurram SamiNoch keine Bewertungen

- ch4 Combinational Logic CircuitsDokument90 Seitench4 Combinational Logic CircuitsMinh Mẫn NguyễnNoch keine Bewertungen

- Lab 9 (Group 4) - 1Dokument11 SeitenLab 9 (Group 4) - 1MUHAMMAD HUZAIFANoch keine Bewertungen

- Introduction To ROBOTICS: ControlDokument15 SeitenIntroduction To ROBOTICS: ControlMANOJ MNoch keine Bewertungen

- Sequential Circuit AnalysisDokument13 SeitenSequential Circuit AnalysismankindaNoch keine Bewertungen

- Cao-Notess by Girdhar Gopal Gautam 3gDokument130 SeitenCao-Notess by Girdhar Gopal Gautam 3gGirdhar Gopal GautamNoch keine Bewertungen

- Marwan K. Abbadi Advisor: Dr. Winfred AnakwaDokument35 SeitenMarwan K. Abbadi Advisor: Dr. Winfred AnakwaAniruddha NarkhedeNoch keine Bewertungen

- Presentation 1Dokument33 SeitenPresentation 1Satyajit GantayatNoch keine Bewertungen

- DGD 8 SolDokument6 SeitenDGD 8 SolDolores MakaruinaNoch keine Bewertungen

- Logic GatesDokument42 SeitenLogic Gatesapi-3701035Noch keine Bewertungen

- CH 05Dokument150 SeitenCH 05Purushothama ReddyNoch keine Bewertungen

- Cyclic Symmetry AnalysisDokument26 SeitenCyclic Symmetry AnalysisB Bala Venkata GaneshNoch keine Bewertungen

- Chapter 1 Group 6Dokument36 SeitenChapter 1 Group 6wegeneargow11Noch keine Bewertungen

- EE200 Exp 11Dokument6 SeitenEE200 Exp 11Tarunesh PandeyNoch keine Bewertungen

- Microprocessor System Design: A Practical IntroductionVon EverandMicroprocessor System Design: A Practical IntroductionNoch keine Bewertungen

- Beginning Digital Electronics through ProjectsVon EverandBeginning Digital Electronics through ProjectsBewertung: 5 von 5 Sternen5/5 (1)

- Runtime Calibration and Compensation of RC OscillatorsDokument7 SeitenRuntime Calibration and Compensation of RC OscillatorsILikeScribd5050Noch keine Bewertungen

- Battery Cross Reference Chart - UnknownDokument1 SeiteBattery Cross Reference Chart - UnknownILikeScribd5050Noch keine Bewertungen

- Sae and Metric Thread Pitches: Inch Metric - Common Metric - UncommonDokument1 SeiteSae and Metric Thread Pitches: Inch Metric - Common Metric - UncommonILikeScribd5050Noch keine Bewertungen

- KG UV3D UserManualDokument29 SeitenKG UV3D UserManualILikeScribd5050Noch keine Bewertungen

- Technical Resource Guide - Aluminum Milling Speeds & FeedsDokument4 SeitenTechnical Resource Guide - Aluminum Milling Speeds & FeedsILikeScribd5050Noch keine Bewertungen

- The Fundamentals of End MillsDokument3 SeitenThe Fundamentals of End MillsILikeScribd5050Noch keine Bewertungen

- Raspberry Pi AnnualDokument180 SeitenRaspberry Pi AnnualILikeScribd5050Noch keine Bewertungen

- Sequential Design Using Schematic Capture: ELEC 4200Dokument8 SeitenSequential Design Using Schematic Capture: ELEC 4200ILikeScribd5050Noch keine Bewertungen

- VHDL Modeling & Synthesis of 7-Segment Decoders: ELEC 4200Dokument6 SeitenVHDL Modeling & Synthesis of 7-Segment Decoders: ELEC 4200ILikeScribd5050Noch keine Bewertungen

- VHDL Modeling and Synthesis of Sequential Logic Design: ELEC 4200Dokument6 SeitenVHDL Modeling and Synthesis of Sequential Logic Design: ELEC 4200ILikeScribd5050Noch keine Bewertungen

- FPGAsDokument44 SeitenFPGAsILikeScribd5050Noch keine Bewertungen

- Combinational Design Using Schematic Capture: ELEC 4200Dokument6 SeitenCombinational Design Using Schematic Capture: ELEC 4200ILikeScribd5050Noch keine Bewertungen

- Assembling SRD Products Onto Customers' PwbsDokument23 SeitenAssembling SRD Products Onto Customers' PwbsILikeScribd5050Noch keine Bewertungen

- Bow and TwistDokument5 SeitenBow and TwistILikeScribd5050Noch keine Bewertungen

- Design PrinciplesDokument27 SeitenDesign PrinciplesILikeScribd5050Noch keine Bewertungen

- F Pga OverviewDokument20 SeitenF Pga OverviewILikeScribd5050Noch keine Bewertungen