Beruflich Dokumente

Kultur Dokumente

2011 - Apr - 22 - R09 - STLD

Hochgeladen von

vasuvlsiCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

2011 - Apr - 22 - R09 - STLD

Hochgeladen von

vasuvlsiCopyright:

Verfügbare Formate

J

N

T

U

W

O

R

L

D

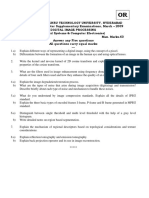

Code No: R09220204 R09 Set No. 2

II B.Tech II Semester Examinations,APRIL 2011

SWITCHING THEORY AND LOGIC DESIGN

Common to Bio-Medical Engineering, Electronics And Telematics,

Electronics And Communication Engineering, Electrical And Electronics

Engineering

Time: 3 hours Max Marks: 75

Answer any FIVE Questions

All Questions carry equal marks

1. Construct a combinational logic circuit which converts a decimal number into an

equivalent Excess -3 number. Implement the same using

(a) Multiplexer

(b) Decoder [15]

2. (a) i. Convert (1596.675)

10

to hexadecimal

ii. Convert (11110.1011)

2

to decimal

iii. Convert (10110001.01101001)

2

to octal

iv. Convert (235.0657)

8

to Binary

(b) Obtain the 1s complement and 2s complement of the binary numbers

i. 1011011

ii. 0110101

iii. 10110

iv. 00110 [8+7]

3. Construct the compatibility graph and obtain the minimal cover table for the

sequential machine described by the state table given. [15]

PS NS,Z

I=0 I=1

1 2,0 3,1

2 1,0 1,1

3 4,1 4,1

4 3,1 6,0

5 1,0 1,1

6 7,0 6,0

7 4,1 4,1

4. (a) Write the conversion procedures of the ip ops. Convert T ip op to JK

ip op.

(b) Convert SR ip op to T ip op. [8+7]

5. Map the following function and simplify using K-Map

(a) F = (A+B+C)(A+B

+C)(A+B

+C

)(A

+B+C)

1

www.jntuworld.com

www.jntuworld.com

J

N

T

U

W

O

R

L

D

Code No: R09220204 R09 Set No. 2

(b) F = (A

BC

+A

BC

D+AB

CD+AB

CD

+ABCD+A

) [15]

6. Write short notes on Integrated circuits. Classify the ICs based on the levels of inte-

gration. Discuss on PLDS. What are the dierent types of programmable devices?

[15]

7. A sequential circuit has three D ip ops, A, B, C and one input x. The minterms

of the D ip ops are given below. Construct the State table and Draw an ASM

chart.

D

A

(X,A,B,C) = (0,3,4,7,9,10,13,14)

D

B

(X,A,B,C) = (4,5,6,7,12,13,14,15)

D

C

(X,A,B,C) = (2,3,6,7,10,11,14,15) [15]

8. (a) Write short notes on Universal gates

(b) Implement Y = AB

+CD + (A

B+C

) using NAND gates

(c) Verify the following Boolean algebraic expression. Justify each step with a

reference to a theorem or postulate.

(AB +C +D) (C

+D) (C

+D +E) = ABC

+ D [4+4+7]

2

www.jntuworld.com

www.jntuworld.com

J

N

T

U

W

O

R

L

D

Code No: R09220204 R09 Set No. 4

II B.Tech II Semester Examinations,APRIL 2011

SWITCHING THEORY AND LOGIC DESIGN

Common to Bio-Medical Engineering, Electronics And Telematics,

Electronics And Communication Engineering, Electrical And Electronics

Engineering

Time: 3 hours Max Marks: 75

Answer any FIVE Questions

All Questions carry equal marks

1. (a) Draw an ASM chart to convert D-Flip op to T ip op.

(b) Give the procedure to design a data processing unit and a control unit [8+7]

2. (a) Dene the following with an example

i. Canonical form

ii. Standard form

iii. Minterm

iv. Maxterm

(b) Draw the truth table and write Boolean expression for the following:

i. F is a 1 only if X is a 1 and Y is a 1 or if X is 0 and Y is a 0.

ii. G is a 0 if any of the three variables X, Y and Z are 1s. G is a 1 for all

other conditions. [8+7]

3. Realize the function F = (A

+C)(AB

+C)(C+D

) in

(a) Decoder

(b) Multiplexer

Explain in detail the procedure to implement the Boolean functions in decoder and

multiplexer. [15]

4. (a) Write short notes on :

i. State transition function.

ii. Finite State model.

iii. Terminal state

iv. Strongly connected machine

(b) Discuss on the capabilities and limitations of nite state machines. [8+7]

5. (a) Use 1s complement arithmetic to subtract

i. (54)

10

from (231)

10

ii. (-27)

10

- (87)

10

(b) Determine the largest and smallest. Hexadecimal numbers that can be used

in a 16-bit digital system. [8+7]

3

www.jntuworld.com

www.jntuworld.com

J

N

T

U

W

O

R

L

D

Code No: R09220204 R09 Set No. 4

6. Implement the following functions using PAL and PLA

F1 = m(2,3,4,7,8,11)

F2 = m(1,3,5,7,9,11,13,15) [15]

7. (a) Design a 4-bit Bidirectional Shift Register.

(b) Convert D ip op to T ip op. [8+7]

8. Design a combinational logic circuit with 4 inputs A, B, C, D. The output Y goes

HIGH if and only if A and C inputs go HIGH. Draw the Truth table. Minimize the

Boolean function using K-map. Draw the circuit diagram. [15]

4

www.jntuworld.com

www.jntuworld.com

J

N

T

U

W

O

R

L

D

Code No: R09220204 R09 Set No. 1

II B.Tech II Semester Examinations,APRIL 2011

SWITCHING THEORY AND LOGIC DESIGN

Common to Bio-Medical Engineering, Electronics And Telematics,

Electronics And Communication Engineering, Electrical And Electronics

Engineering

Time: 3 hours Max Marks: 75

Answer any FIVE Questions

All Questions carry equal marks

1. Simplify the following expressions using K-map

(a) x(y+z)

(b) x+y+xyz

(c) xy+wxyz+xy

(d) wx +xy+wz+yz

[15]

2. Determine a minimal state table equivalent to the state table given below. [15]

PS NS,Z

J1 J2

1 2,0 4,1

2 7,0 1,0

3 4,0 2,1

4 7,0 1,0

5 4,0 1,1

6 5,1 6,1

7 4,1 4,1

3. (a) Dierentiate Hexadecimal codes and Alpha numeric codes.

(b) Write Gray codes for the following decimal numbers:

i. 1000

ii. 724

iii. 83

iv. 37 [7+8]

4. (a) A Digital system is quite often dened by registers it contains and operations

that are executed on the data stored in them. Give examples of symbolic

notation of register operation and its descriptions.

(b) Draw an ASM diagram and explain in detail the conditional box. [8+7]

5. (a) Give a detailed comparison between combinational logic circuits and sequential

logic circuits.

(b) Design a basic ip op and explain its operation. [8+7]

5

www.jntuworld.com

www.jntuworld.com

J

N

T

U

W

O

R

L

D

Code No: R09220204 R09 Set No. 1

6. Tabulate the PLA programming table for the four Boolean functions. Minimize

the following.

(a) F1 (A, B, C) = m (1, 2, 5, 6)

(b) F2 (A, B, C) = m (0, 1, 4, 7)

(c) F3 (A, B, C) = m (2,6,8)

(d) F4 (A, B, C) = m (1,2,3,5,7) [15]

7. Design a Logic circuit which accepts two 5 bit binary numbers. The circuit should

perform binary addition when the carry in is 0 and should perform binary subtrac-

tion using 2s complement addition when the input carry is 1. [15]

8. Draw the logic circuits using AND, OR, NOT elements to represent the following:

(a) AB

+A

B

(b) ((AB)

(CD)

(c) ((A+B)(C+D))E +FG

(d) AB + (AB)

+ A

BC

Implement the above functions using only NAND gates and only NOR gates [15]

6

www.jntuworld.com

www.jntuworld.com

J

N

T

U

W

O

R

L

D

Code No: R09220204 R09 Set No. 3

II B.Tech II Semester Examinations,APRIL 2011

SWITCHING THEORY AND LOGIC DESIGN

Common to Bio-Medical Engineering, Electronics And Telematics,

Electronics And Communication Engineering, Electrical And Electronics

Engineering

Time: 3 hours Max Marks: 75

Answer any FIVE Questions

All Questions carry equal marks

1. Convert the following Mealy machine into a corresponding Moore machine. [15]

PS NS,Z

X=0 X=1

A C,0 B,0

B A,1 D,0

C B,1 A,1

D D,1 C,0

2. (a) Demonstrate by means of truth tables the validity of the following theorems

of Boolean algebra.

i. Commutative laws

ii. Demorgans theorems for 4 variables.

(b) Prove the following:

i. XYZ + XYZ

+ XY

Z + X

Z +X

YZ

= Y

Z + XY +X

YZ

ii. XY

+ Y

Z = XY

Z + XY

+X

Z [8+7]

3. Draw the block diagram of the 3 to 8 decoder. Draw the circuit diagram of the

decoder and explain the operation of the decoder.

(a) If the input 3 bit code is 110, then which decoder output will be HIGH?

(b) If the output of the decoder D3 is HIGH, what is the input code of the decoder?

[15]

4. (a) Explain the complement representation of negative numbers with examples

(b) Obtain the 1s complement and 2s complement of the binary numbers

i. 1010111

ii. 0111001

iii. 1001

iv. 00010 [4+11]

5. Implement the function of converting a Binary number to a BCD number in a

ROM. Write the size of ROM required implementing this function. Give the ROM

truth table. Give the internal connections for the function. [15]

7

www.jntuworld.com

www.jntuworld.com

J

N

T

U

W

O

R

L

D

Code No: R09220204 R09 Set No. 3

6. (a) Draw an ASM chart for designing a circuit which is used to count the number

of bits in a register that have a value 1.

(b) Discuss the procedure to implement an ASM chart using Multiplexer. [8+7]

7. Dene State table. Draw state table for a 4 bit synchronous UP/DOWN counter.

Design UP/DOWN synchronous counters. [15]

8. (a) List down the factors involved in a digital circuit design. Specify the various

criteria to determine minimal cost.

(b) Compare the Minimization procedure using Boolean Postulates and K-map.

[8+7]

8

www.jntuworld.com

www.jntuworld.com

Das könnte Ihnen auch gefallen

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (120)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- Corrupt IMEI and EFSDokument11 SeitenCorrupt IMEI and EFSaldobnaNoch keine Bewertungen

- PLC Software and Hardware LsitDokument12 SeitenPLC Software and Hardware LsitAnonymous BW9mIv22NNoch keine Bewertungen

- Network Design National Case StudyDokument5 SeitenNetwork Design National Case StudyZach PraterNoch keine Bewertungen

- Rr422202 Digital Image ProcessingDokument4 SeitenRr422202 Digital Image ProcessingvasuvlsiNoch keine Bewertungen

- Digital Circuits - Anand KumarDokument340 SeitenDigital Circuits - Anand KumarAkash SupeNoch keine Bewertungen

- Digital Image Processing Question PapersDokument9 SeitenDigital Image Processing Question PapersvasuvlsiNoch keine Bewertungen

- Rr410507 Digital Speech and Image ProcessingDokument6 SeitenRr410507 Digital Speech and Image ProcessingvasuvlsiNoch keine Bewertungen

- Rr410507 Speech and Image ProcessingDokument7 SeitenRr410507 Speech and Image ProcessingvasuvlsiNoch keine Bewertungen

- Real Time Signal Ang Image Processing - VnrvjietDokument2 SeitenReal Time Signal Ang Image Processing - VnrvjietvasuvlsiNoch keine Bewertungen

- Rr410507 Digital Speech and Image Processingspeech and Image ProcessingDokument6 SeitenRr410507 Digital Speech and Image Processingspeech and Image ProcessingSRINIVASA RAO GANTANoch keine Bewertungen

- Rr411103 Image Processing and Pattern RecognitionDokument6 SeitenRr411103 Image Processing and Pattern RecognitionvasuvlsiNoch keine Bewertungen

- r05411206 Image ProcessingDokument5 Seitenr05411206 Image ProcessingvasuvlsiNoch keine Bewertungen

- Rr410507 Digital Speech Image Processing Speech Image ProcessingDokument6 SeitenRr410507 Digital Speech Image Processing Speech Image ProcessingvasuvlsiNoch keine Bewertungen

- Image Processing May2004 or 420456Dokument1 SeiteImage Processing May2004 or 420456Nizam Institute of Engineering and Technology LibraryNoch keine Bewertungen

- r05411101 Image Processing and Pattern RecognitionDokument6 Seitenr05411101 Image Processing and Pattern RecognitionvasuvlsiNoch keine Bewertungen

- Rr410507 Digital Speech and Image Processing Speech and Image ProcessingDokument6 SeitenRr410507 Digital Speech and Image Processing Speech and Image ProcessingvasuvlsiNoch keine Bewertungen

- Nov 2008Dokument5 SeitenNov 2008Vijayalaxmi BiradarNoch keine Bewertungen

- r05321902 Digital Image ProcessingDokument5 Seitenr05321902 Digital Image ProcessingvasuvlsiNoch keine Bewertungen

- R05411101-Image Processing and Patteren RecognitionDokument4 SeitenR05411101-Image Processing and Patteren RecognitionvasuvlsiNoch keine Bewertungen

- Or420456 Image ProcessingDokument2 SeitenOr420456 Image ProcessingvasuvlsiNoch keine Bewertungen

- R09-1!2!25-Image Processing and Pattern Recognition-Dform31.10.12Dokument1 SeiteR09-1!2!25-Image Processing and Pattern Recognition-Dform31.10.12vasuvlsiNoch keine Bewertungen

- R09-Image and Video ProcessingDokument1 SeiteR09-Image and Video ProcessingvasuvlsiNoch keine Bewertungen

- Image Processing Nov2003 or 321151Dokument1 SeiteImage Processing Nov2003 or 321151Nizam Institute of Engineering and Technology LibraryNoch keine Bewertungen

- Image Processing. July2003 or 420456Dokument2 SeitenImage Processing. July2003 or 420456Nizam Institute of Engineering and Technology LibraryNoch keine Bewertungen

- JNTU Affiliated College Barcoded D-Form for Image Processing CourseDokument1 SeiteJNTU Affiliated College Barcoded D-Form for Image Processing CoursevasuvlsiNoch keine Bewertungen

- R09-Image and Video ProcessingDokument1 SeiteR09-Image and Video ProcessingvasuvlsiNoch keine Bewertungen

- Image Processing May2003 or 420456Dokument1 SeiteImage Processing May2003 or 420456Nizam Institute of Engineering and Technology LibraryNoch keine Bewertungen

- Image Processing May2004 or 321151Dokument1 SeiteImage Processing May2004 or 321151Nizam Institute of Engineering and Technology LibraryNoch keine Bewertungen

- Or23decs-Digital Image ProcessingDokument1 SeiteOr23decs-Digital Image ProcessingvasuvlsiNoch keine Bewertungen

- Or 23 Cs Digital Image ProcessingDokument1 SeiteOr 23 Cs Digital Image ProcessingvasuvlsiNoch keine Bewertungen

- OR321151 Image Processing Exam QuestionsDokument2 SeitenOR321151 Image Processing Exam QuestionsvasuvlsiNoch keine Bewertungen

- Or 23 Decs Digital Image ProcessingDokument1 SeiteOr 23 Decs Digital Image ProcessingvasuvlsiNoch keine Bewertungen

- Eleven Rack User GuideDokument130 SeitenEleven Rack User GuideGeocasta AbaddonNoch keine Bewertungen

- WP Miller WPA2Security PDokument10 SeitenWP Miller WPA2Security Pn43.nitin100% (1)

- Pikepdf Readthedocs Io en LatestDokument71 SeitenPikepdf Readthedocs Io en LatestHerit OhwotuNoch keine Bewertungen

- BenQ JoyBook R23Dokument50 SeitenBenQ JoyBook R23alexcastillo100% (2)

- Part 66 Module 5 SyllabusDokument2 SeitenPart 66 Module 5 SyllabusamaiscNoch keine Bewertungen

- DXDokument3.509 SeitenDXDustin SmithNoch keine Bewertungen

- Data Preparation StepsDokument6 SeitenData Preparation StepsJames IshakuNoch keine Bewertungen

- MIS Report (Khalid, Dima, Dana, Jamal)Dokument15 SeitenMIS Report (Khalid, Dima, Dana, Jamal)Khaled SamaraNoch keine Bewertungen

- Service Manual for 130CR/PCR-262/CE-160 Cash RegisterDokument46 SeitenService Manual for 130CR/PCR-262/CE-160 Cash RegisterSebas EuNoch keine Bewertungen

- 3GPP TS 38.141-1Dokument255 Seiten3GPP TS 38.141-1Boby SharifNoch keine Bewertungen

- The Free Lunch Is Over: A Fundamental Turn Toward ConcurrencyDokument31 SeitenThe Free Lunch Is Over: A Fundamental Turn Toward ConcurrencyRaziwanNoch keine Bewertungen

- Standby Bounce StepsDokument5 SeitenStandby Bounce StepsNaresh KumarNoch keine Bewertungen

- DSCDokument3 SeitenDSCYM AnfasNoch keine Bewertungen

- Raspberry Pi DHT11 Humidity and Temperature Sensor InterfaceDokument15 SeitenRaspberry Pi DHT11 Humidity and Temperature Sensor InterfaceTwinkle RatnaNoch keine Bewertungen

- Geo-Location Ap Grouping: Altai A2 Wifi Access Point / BridgeDokument2 SeitenGeo-Location Ap Grouping: Altai A2 Wifi Access Point / BridgeSoft-Tech PerezNoch keine Bewertungen

- SECTION II: Technical Foundations of Database Management: HierarchicalDokument5 SeitenSECTION II: Technical Foundations of Database Management: HierarchicalBoobalan RNoch keine Bewertungen

- Nissin Digital Flash - Di866 USB Firmware Update ProcessDokument8 SeitenNissin Digital Flash - Di866 USB Firmware Update Processpcdproyecto100% (1)

- HP Module Learning Check AnswersDokument5 SeitenHP Module Learning Check AnswersTebogo McDonaldNoch keine Bewertungen

- Evermotion Archmodels Vol 53 PDFDokument2 SeitenEvermotion Archmodels Vol 53 PDFJenniferNoch keine Bewertungen

- Modulo Ethernet - Ifbd-He0506 - SPC - enDokument35 SeitenModulo Ethernet - Ifbd-He0506 - SPC - enE Moy LandaNoch keine Bewertungen

- Subnetting V.L.S.M. Clarito2Dokument8 SeitenSubnetting V.L.S.M. Clarito2An CuNoch keine Bewertungen

- PDF Submission Sites List 2021Dokument7 SeitenPDF Submission Sites List 2021Jakaria hossenNoch keine Bewertungen

- Getting Started PIC16F84A Kit + PIC ProgrammerDokument5 SeitenGetting Started PIC16F84A Kit + PIC Programmerelectron_glowNoch keine Bewertungen

- Read Grimorio do Papa Honório PDF OnlineDokument1 SeiteRead Grimorio do Papa Honório PDF OnlineFredNoch keine Bewertungen

- Foxconn 661FX6617miDokument83 SeitenFoxconn 661FX6617miheckhoxNoch keine Bewertungen

- Sumbilon, Austine Couline G. Basic Computer Bsit-2Nd YearDokument8 SeitenSumbilon, Austine Couline G. Basic Computer Bsit-2Nd YearHayizswahf Yoezs EixorbNoch keine Bewertungen

- UR32 Datasheet V1.1 PDFDokument5 SeitenUR32 Datasheet V1.1 PDFtenry_03Noch keine Bewertungen