Beruflich Dokumente

Kultur Dokumente

Lecture02 Inverter

Hochgeladen von

Bala Krishna0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

10 Ansichten20 SeitenRABAEY LECTURES

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenRABAEY LECTURES

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

10 Ansichten20 SeitenLecture02 Inverter

Hochgeladen von

Bala KrishnaRABAEY LECTURES

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 20

Lecture 1 ECE 425

Lecture 2 -- The Inverter

Lecture 1 ECE 425

Outline

Signalling in Digital Systems

Inverters -- CMOS and Otherwise

Circuit Analysis of CMOS Inverters

Lecture 1 ECE 425

Signaling Conventions

Choose ranges of voltages to represent logic 0 and 1

Decide that logic 0 goes with low voltage, logic 1 with

high voltage

Need to guarantee that an input in the legal range

produces an output in the legal range

Better if the output for any legal input is closer to the

supply rails than the input (restoring logic)

Requires gain in the circuit

Need to tolerate some amount of electrical noise to be

practical

Lecture 1 ECE 425

CMOS Signaling Conventions

Voltage

Input Output

Logic

1

Logic

0

V

ih

V

il

forbidden

region

Logic

1

V

dd

0

V

oh

Logic

0

V

ol

Noise

Margin

Noise

Margin

forbidden

region

Lecture 1 ECE 425

CMOS Inverter

Vin

Vout

D

D

G

S

S

G

Vout

Vin

Vdd

Ground

Slope = 1

Lecture 1 ECE 425

CMOS

Complimentary Metal-Oxide Semiconductor

P-FETs connect output to V

dd

, N-FETs connect output

to ground

Good Points

Rail-to-rail outputs

Restoring logic

In principle, 0 current flows in steady state

In reality, leakage matters

Bad Points

Requires twice as many transistors as some other

logic styles

Lecture 1 ECE 425

Analyzing Inverter I-V Characteristics

KVL and KCL always apply

I

ds

(n) = -I

ds

(p)

V

ds

(n) + [-V

ds

(p)] = V

dd

Lecture 1 ECE 425

Inverter Transfer Characteristics

Lecture 1 ECE 425

Solving the System

Five regions of operation

A: N-FET off, P-FET in linear region

B: N-FET in saturation, P-FET in linear

C: Both devices in saturation

Want this region as small as possible

In this (ideal) case, its a single point at V

dd

/2

D: N-FET linear, P-FET saturated

E: N-FET linear, P-FET off

Lecture 1 ECE 425

Solving the System

Region A

V

in

< V

tn

, no current through N-FET, P-FET pulls V

out

to

V

dd

Region B

N-FET in saturation (current source)

P-FET in linear (resistor)

Lecture 1 ECE 425

Solving the System

Grinding the math, get

V

out

= (V

in

- V

tp

) + sqrt[(V

in

- V

tp

)

2

- 2V

dd

(V

in

- V

dd

/2 - V

tp

)

- (!

n

/!

p

)(V

in

- V

tn

)

2

]

(Remember that ! = * C

ox

* W/L)

Region C

Both FETs in saturation, in our ideal model happens at exactly

one point

If !

n

= !

p

and V

tn

= -V

tp

, this point is at V

in

= V

out

= V

dd

/2

Note that V

tp

is usually defined as a negative quantity to make

the equations symmetric

This input voltage is called the gate threshold

In reality, I

ds

increases slightly as V

ds

increases, even in

saturation, and region C is a small interval, not a point

Lecture 1 ECE 425

Solving the System

Region D:

N-FET in linear region, P-FET in saturation, dual of

region B

Model P-FET as current source, N-FET as resistor

V

out

= (V

in

- V

tn

) + sqrt[(V

in

- V

tn

)

2

- (!

p

/!

n

)(V

in

- V

dd

- V

tn

)

2

]

Region E:

N-FET is off, P-FET in linear region (V

in

> V

dd

- |V

tp

|)

No current through N-FET, P-FET pulls output voltage

to V

dd

Lecture 1 ECE 425

Changing Beta

Transfer curve

affected by ratio of

N, P device betas

Lecture 1 ECE 425

Pass-Gates -- A CMOS Switch

Lots of cases where wed like to be able to connect or

disconnect two wires at will

Multiplexors

Bi-Directional wires

Since one model of a MOS transistor is a switch, can we use

MOS transistors to build pass-gates?

Lecture 1 ECE 425

Idea #1 -- N-FET as Pass Gate

Passing a logic 0, V

gs

= V

dd

at all times

Lecture 1 ECE 425

Idea #1 -- N-FET as Pass Gate

Passing a logic 1 V

ds

= V

gs

, therefore capped at V

dd

- V

t

Lecture 1 ECE 425

Better Pass-Gate: N- and P-FET in Parallel

P-FET alone has opposite problem to N-FET -- passes 1s

well but 0s badly

Connect both types of device in parallel to pass both

signals well

Takes four transistors, though (counting the two to

invert the control signal)

!

!

!

!

Lecture 1 ECE 425

Trade-offs

Full pass-gate takes something like 4x the area of one pass-

transistor, but passes all signals well

However, V

t

and V

dd

- V

t

are typically well within the V

OL

and V

OH

regions

For safety, use full pass-gate anywhere youre not sure exactly what

the transistor will be driving

Single-transistor pass-gates can work in cases where the pass gate

drives a single CMOS gate

Never, ever connect multiple single-transistor pass-gates in series

Use of single-transistor pass-gates can make your design less

portable across fabrication processes -- correctness now depends

on electrical issues

Given the number of transistors/chip these days, the more important

trade-off is the amount of time youll have to spend verifying that a

single-transistor pass gate will work

Lecture 1 ECE 425

Next Time

Designing arbitrary CMOS gates

Lecture 1 ECE 425

Reading

Sections 2.5 - 2.7

Das könnte Ihnen auch gefallen

- Parte2 Clase04 ADC DCADokument56 SeitenParte2 Clase04 ADC DCABala KrishnaNoch keine Bewertungen

- Power Dissipation: Modified From "Digital Integrated Circuits", by J. Rabaey, A. Chandrakasan and B. NikolicDokument14 SeitenPower Dissipation: Modified From "Digital Integrated Circuits", by J. Rabaey, A. Chandrakasan and B. NikolicBala KrishnaNoch keine Bewertungen

- Parte2 - Clase03 - Analog View of Digital SignalsDokument63 SeitenParte2 - Clase03 - Analog View of Digital SignalsBala KrishnaNoch keine Bewertungen

- Lecture10 Power ConsumptionDokument14 SeitenLecture10 Power ConsumptionBala KrishnaNoch keine Bewertungen

- Lecture09 Performance 01Dokument33 SeitenLecture09 Performance 01Bala KrishnaNoch keine Bewertungen

- Lecture09 Performance 01Dokument33 SeitenLecture09 Performance 01Bala KrishnaNoch keine Bewertungen

- Lecture 8 - Gate-Level Delay EstimationDokument40 SeitenLecture 8 - Gate-Level Delay EstimationBala KrishnaNoch keine Bewertungen

- Pilani Campus: Birla Institute of Techonology and Science, PilaniDokument3 SeitenPilani Campus: Birla Institute of Techonology and Science, PilaniBala KrishnaNoch keine Bewertungen

- Lecture06 LatchesDokument30 SeitenLecture06 LatchesBala KrishnaNoch keine Bewertungen

- Lecture03 Static CMOSDokument24 SeitenLecture03 Static CMOSBala KrishnaNoch keine Bewertungen

- Eee CombinedDokument89 SeitenEee CombinedBala KrishnaNoch keine Bewertungen

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- U Cân Laumax W200 BaseDokument36 SeitenU Cân Laumax W200 BaseJose Luna0% (1)

- Handover GSMDokument33 SeitenHandover GSMShashank Prajapati0% (1)

- Formula LTE NewDokument11 SeitenFormula LTE NewInsyafa NalaprajaNoch keine Bewertungen

- 14af45 14af45c SVMDokument50 Seiten14af45 14af45c SVMLuis MorenoNoch keine Bewertungen

- Korg M3 Manual en InglesDokument241 SeitenKorg M3 Manual en InglesElio José Torrez VargasNoch keine Bewertungen

- Semiconductorfet, Called A Misfet) - A Common Special Case of This Type Uses An Oxide Layer As TheDokument10 SeitenSemiconductorfet, Called A Misfet) - A Common Special Case of This Type Uses An Oxide Layer As TheShoumil SachanNoch keine Bewertungen

- Ultra Aire 70H Spec SheetDokument2 SeitenUltra Aire 70H Spec SheetErik BellNoch keine Bewertungen

- 66kv Isolator Universal MakeDokument13 Seiten66kv Isolator Universal MakeRoshni GurungNoch keine Bewertungen

- Diagnostic Code List: Cerrar SISDokument3 SeitenDiagnostic Code List: Cerrar SISHamilton MirandaNoch keine Bewertungen

- Design and Fabrication ofDokument9 SeitenDesign and Fabrication ofKarthi Keyan R KNoch keine Bewertungen

- Laboratory Manual For Ac Electrical CircuitsDokument75 SeitenLaboratory Manual For Ac Electrical CircuitsArnulfo LavaresNoch keine Bewertungen

- Hydrogen IcsDokument16 SeitenHydrogen IcsVũ PhươngNoch keine Bewertungen

- QuestHandbook May 2021Dokument22 SeitenQuestHandbook May 2021Pablo FloresNoch keine Bewertungen

- TUSB9261 USB 3.0 To SATA Bridge: 1 Features 2 ApplicationsDokument27 SeitenTUSB9261 USB 3.0 To SATA Bridge: 1 Features 2 ApplicationsWali SauyunanNoch keine Bewertungen

- Monitor AocDokument58 SeitenMonitor AocjonatanactosNoch keine Bewertungen

- FKG2S We Brochure enDokument2 SeitenFKG2S We Brochure enMichael ManzanoNoch keine Bewertungen

- Leica Sr20: User ManualDokument32 SeitenLeica Sr20: User ManualathalNoch keine Bewertungen

- Electrical Diagrams: Ac Motor Control SystemDokument80 SeitenElectrical Diagrams: Ac Motor Control SystemJohn fredy cuervo100% (1)

- Руководство По Подключению к ПЛК Англ ЯзыкDokument801 SeitenРуководство По Подключению к ПЛК Англ Языкazz zinouNoch keine Bewertungen

- q3 MerDokument78 Seitenq3 Merf20220301Noch keine Bewertungen

- Advantest R6441 ABCDokument4 SeitenAdvantest R6441 ABCbudi0251Noch keine Bewertungen

- Vehicle SimulatorDokument12 SeitenVehicle SimulatorraghavNoch keine Bewertungen

- EB CGAK XX Draft - EN Cambio de PLCDokument10 SeitenEB CGAK XX Draft - EN Cambio de PLCOmar PiñaNoch keine Bewertungen

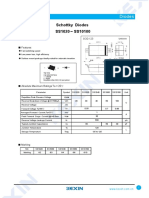

- SMD Type Diodes: Schottky Diodes SS1020 SS10100Dokument2 SeitenSMD Type Diodes: Schottky Diodes SS1020 SS10100Momo MendozaNoch keine Bewertungen

- DRS2663B Amana Service ManualDokument72 SeitenDRS2663B Amana Service ManualJohn TrippNoch keine Bewertungen

- BateriaDokument17 SeitenBateriaGabriel MarzolaNoch keine Bewertungen

- Acc-En (Sci) : Analogue Multi-Sensor With SCIDokument1 SeiteAcc-En (Sci) : Analogue Multi-Sensor With SCIuygar öztürkNoch keine Bewertungen

- 4.5G Solution OverviewDokument23 Seiten4.5G Solution OverviewTelworks RSNoch keine Bewertungen

- Komatsu EGSDokument2 SeitenKomatsu EGSdickyNoch keine Bewertungen

- 14 - 6060 - Electrical Drawings - CATDokument32 Seiten14 - 6060 - Electrical Drawings - CAThectorNoch keine Bewertungen