Beruflich Dokumente

Kultur Dokumente

Expt No.: 2 Design and Implementation of Code Onvertor Aim

Hochgeladen von

senthilvl0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

23 Ansichten18 SeitenTo design and implement 4-bit

Binary to gray code converter

Gray to binary code converter

BCD to excess-3 code converter

Excess-3 to BCD code converter

Originaltitel

prm ex 2

Copyright

© © All Rights Reserved

Verfügbare Formate

DOCX, PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenTo design and implement 4-bit

Binary to gray code converter

Gray to binary code converter

BCD to excess-3 code converter

Excess-3 to BCD code converter

Copyright:

© All Rights Reserved

Verfügbare Formate

Als DOCX, PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

23 Ansichten18 SeitenExpt No.: 2 Design and Implementation of Code Onvertor Aim

Hochgeladen von

senthilvlTo design and implement 4-bit

Binary to gray code converter

Gray to binary code converter

BCD to excess-3 code converter

Excess-3 to BCD code converter

Copyright:

© All Rights Reserved

Verfügbare Formate

Als DOCX, PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 18

EXPT NO.

: 2 DESIGN AND IMPLEMENTATION OF CODE

DATE: CONVERTOR

AIM:

To design and implement 4-bit

(i) Binary to gray code converter

(ii) Gray to binary code converter

(iii) BCD to excess-3 code converter

(iv) Excess-3 to BCD code converter

APPARATUS REQUIRED:

Sl.No. COMPONENT SPECIFICATION QTY.

1. X-OR GATE IC 7486 1

2. AND GATE IC 7408 1

3. OR GATE IC 7432 1

4. NOT GATE IC 7404 1

5. IC TRAINER KIT - 1

6. PATCH CORDS - 35

THEORY:

The availability of large variety of codes for the same discrete elements

of information results in the use of different codes by different systems. A

conversion circuit must be inserted between the two systems if each uses

different codes for same information. Thus, code converter is a circuit that

makes the two systems compatible even though each uses different binary

code. The bit combination assigned to binary code to gray code. Since each

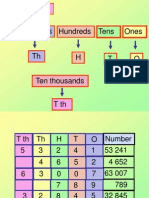

code uses four bits to represent a decimal digit. There are four inputs and

four outputs. Gray code is a non-weighted code. The input variable are

designated as B3, B2, B1, B0 and the output variables are designated as C3,

C2, C1, Co. from the truth table,

LOGIC DIAGRAM:

BINARY TO GRAY CODE CONVERTOR

TRUTH TABLE:

| Binary input | Gray code output

B3 B2 B1 B0 G3 G2 G1 G0

0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 1

0 0 1 0 0 0 1 1

0 0 1 1 0 0 1 0

0 1 0 0 0 1 1 0

0 1 0 1 0 1 1 1

0 1 1 0 0 1 0 1

0 1 1 1 0 1 0 0

1 0 0 0 1 1 0 0

1 0 0 1 1 1 0 1

1 0 1 0 1 1 1 1

1 0 1 1 1 1 1 0

1 1 0 0 1 0 1 0

1 1 0 1 1 0 1 1

1 1 1 0 1 0 0 1

1 1 1 1 1 0 0 0

combinational circuit is designed. The Boolean functions are obtained from

K-Map for each output variable.

A code converter is a circuit that makes the two systems compatible even

though each uses a different binary code. To convert from binary code to

Excess-3 code, the input lines must supply the bit combination of elements

as specified by code and the output lines generate the corresponding bit

combination of code. Each one of the four maps represents one of the four

outputs of the circuit as a function of the four input variables.

A two-level logic diagram may be obtained directly from the Boolean

expressions derived by the maps. These are various other possibilities for a

logic diagram that implements this circuit. Now the OR gate whose output is

C+D has been used to implement partially each of three outputs.

K-Map for G

3

:

G

3

= B

3

K-Map for G

2

:

K-Map for G

1

:

K-Map for G

0

:

LOGIC DIAGRAM:

GRAY CODE TO BINARY CONVERTOR

K-Map for B

3

:

B3 = G3

K-Map for B

2

:

TRUTH TABLE:

| Gray Code | Binary Code |

G3 G2 G1 G0 B3 B2 B1 B0

0 0 0 0 0 0 0 0

0 0 0 1 0 0 0 1

0 0 1 1 0 0 1 0

0 0 1 0 0 0 1 1

0 1 1 0 0 1 0 0

0 1 1 1 0 1 0 1

0 1 0 1 0 1 1 0

0 1 0 0 0 1 1 1

1 1 0 0 1 0 0 0

1 1 0 1 1 0 0 1

1 1 1 1 1 0 1 0

1 1 1 0 1 0 1 1

1 0 1 0 1 1 0 0

1 0 1 1 1 1 0 1

1 0 0 1 1 1 1 0

1 0 0 0 1 1 1 1

K-Map for B

1

:

K-Map for B

0

:

LOGIC DIAGRAM:

BCD TO EXCESS-3 CONVERTOR

K-Map for E

3

:

E3 = B3 + B2 (B0 + B1)

K-Map for E

2

:

TRUTH TABLE:

| BCD input | Excess 3 output |

B3 B2 B1 B0 E3 E2 E1 E0

0 0 0 0 0 0 1 1

0 0 0 1 0 1 0 0

0 0 1 0 0 1 0 1

0 0 1 1 0 1 1 0

0 1 0 0 0 1 1 1

0 1 0 1 1 0 0 0

0 1 1 0 1 0 0 1

0 1 1 1 1 0 1 0

1 0 0 0 1 0 1 1

1 0 0 1 1 1 0 0

1 0 1 0 x x x x

1 0 1 1 x x x x

1 1 0 0 x x x x

1 1 0 1 x x x x

1 1 1 0 x x x x

1 1 1 1 x x x x

K-Map for E

1

:

K-Map for E

0

:

LOGIC DIAGRAM:

EXCESS-3 TO BCD CONVERTOR

K-Map for A:

A = X1 X2 + X3 X4 X1

K-Map for B:

TRUTH TABLE:

| Excess 3 Input | BCD Output |

B3 B2 B1 B0 G3 G2 G1 G0

0 0 1 1 0 0 0 0

0 1 0 0 0 0 0 1

0 1 0 1 0 0 1 0

0 1 1 0 0 0 1 1

0 1 1 1 0 1 0 0

1 0 0 0 0 1 0 1

1 0 0 1 0 1 1 0

1 0 1 0 0 1 1 1

1 0 1 1 1 0 0 0

1 1 0 0 1 0 0 1

K-Map for C:

K-Map for D:

PROCEDURE:

PROCEDURE

(i) Connections were given as per circuit diagram.

(ii) Logical inputs were given as per truth table

(iii) Observe the logical output and verify with the truth tables.

RESULT:

Pre-lab test (20) Signature with

date

Simulation (20)

Circuit connection(30)

Result (10)

Post lab test (20)

Total (100)

Das könnte Ihnen auch gefallen

- 3.code ConvertersDokument7 Seiten3.code ConvertersSudhan HariNoch keine Bewertungen

- Digital Electronics Lab Manual: Prepared by Mr.P.M.Murali, AP/ECE Mr.G.Ramachandran, AP/ECE Mrs.T.Sheela, AP/ECEDokument62 SeitenDigital Electronics Lab Manual: Prepared by Mr.P.M.Murali, AP/ECE Mr.G.Ramachandran, AP/ECE Mrs.T.Sheela, AP/ECEsrichandranidNoch keine Bewertungen

- Ic Lab NewDokument131 SeitenIc Lab NewMrs.S.Divya BMENoch keine Bewertungen

- Exp 4 CODE CONVERTERSDokument8 SeitenExp 4 CODE CONVERTERSkishorebabNoch keine Bewertungen

- Digital Lab ManualDokument77 SeitenDigital Lab ManualSaravanan JaganNoch keine Bewertungen

- Modul Minggu Ke-2 (DB6 Dan DB7)Dokument14 SeitenModul Minggu Ke-2 (DB6 Dan DB7)farrel prambudiNoch keine Bewertungen

- EC2207 Digital Electronics LabDokument145 SeitenEC2207 Digital Electronics Labprajkumar324Noch keine Bewertungen

- De Lab Manual-EEE New1Dokument77 SeitenDe Lab Manual-EEE New1selva_raj215414Noch keine Bewertungen

- DSD Lab Record - 230114 - 203246Dokument33 SeitenDSD Lab Record - 230114 - 203246Angelin ArulNoch keine Bewertungen

- 17BCB0091 DLD Da 6Dokument9 Seiten17BCB0091 DLD Da 6csolutionNoch keine Bewertungen

- Open Ended Experiment: Digital Electronics and Computer OrganizationDokument4 SeitenOpen Ended Experiment: Digital Electronics and Computer OrganizationHarshit AggarwalNoch keine Bewertungen

- Practical 2,4,5,6Dokument26 SeitenPractical 2,4,5,6LaxmiNoch keine Bewertungen

- BINARY TO GRAY CODE CONVERTERDokument14 SeitenBINARY TO GRAY CODE CONVERTERBhuvan BeeraNoch keine Bewertungen

- Aids Dpco Lab 22-23-4-52Dokument49 SeitenAids Dpco Lab 22-23-4-52Acshaya M NNoch keine Bewertungen

- Modul Minggu Ke-2 (DB6 Dan DB7)Dokument15 SeitenModul Minggu Ke-2 (DB6 Dan DB7)Eden HamamNoch keine Bewertungen

- CAO LAB MANUALDokument28 SeitenCAO LAB MANUALabhisheksingh89208Noch keine Bewertungen

- Logic Design Lab ManualDokument72 SeitenLogic Design Lab ManualHitha Gangatkar100% (1)

- CS302 - Lab Manual - Week No PDFDokument15 SeitenCS302 - Lab Manual - Week No PDFattiqueNoch keine Bewertungen

- Digital System Design Lab ExperimentsDokument45 SeitenDigital System Design Lab ExperimentsshivaNoch keine Bewertungen

- Digital Lab ManualDokument69 SeitenDigital Lab ManualRajesh MohanNoch keine Bewertungen

- ADE - Exp 6Dokument16 SeitenADE - Exp 6shashwatNoch keine Bewertungen

- Lecture2 Chapter4 - BCD To Excess-3 Code Converter DesignDokument19 SeitenLecture2 Chapter4 - BCD To Excess-3 Code Converter DesignAyesha HussainNoch keine Bewertungen

- Lab 12Dokument7 SeitenLab 12rakshika2580Noch keine Bewertungen

- Experiment 3 Group 15Dokument12 SeitenExperiment 3 Group 15SIDHARTH A NARAYANANNoch keine Bewertungen

- Assignement 2Dokument13 SeitenAssignement 2Rohit ChaharNoch keine Bewertungen

- Eee 221 Digital Logic 2022 Final ExamDokument4 SeitenEee 221 Digital Logic 2022 Final ExamRegina KadenyiNoch keine Bewertungen

- L04 - Combinational LogicDokument27 SeitenL04 - Combinational LogicPirzada SwatiNoch keine Bewertungen

- Combinational Circuits LDICDokument129 SeitenCombinational Circuits LDIChemanth ramireddyNoch keine Bewertungen

- DC ExDokument7 SeitenDC Exsuchipriya muchandeNoch keine Bewertungen

- Computer Engineering Experiment 3: Carry Lookahead AddersDokument7 SeitenComputer Engineering Experiment 3: Carry Lookahead AddersIn Fee Knee TeaNoch keine Bewertungen

- Chapter 5-1Dokument31 SeitenChapter 5-1Tushar SarkarNoch keine Bewertungen

- DLD Lecture 4Dokument53 SeitenDLD Lecture 4sjbv.hardik582Noch keine Bewertungen

- Digital Lab ReportDokument9 SeitenDigital Lab ReportNg Ming FengNoch keine Bewertungen

- Review of Digital Design FundamentalsDokument75 SeitenReview of Digital Design FundamentalsKurumeti Naga Surya Lakshmana KumarNoch keine Bewertungen

- Ex 6 - Binary To Gray Code ConverterDokument6 SeitenEx 6 - Binary To Gray Code Converterneha yarrapothuNoch keine Bewertungen

- Decoders and EncodersDokument7 SeitenDecoders and EncodersEstefania GuarnizoNoch keine Bewertungen

- Lab 5 Binary ArithmeticDokument5 SeitenLab 5 Binary ArithmeticIfthakharul Alam ShuvoNoch keine Bewertungen

- 8 PLC Program To Implement ExcessDokument5 Seiten8 PLC Program To Implement ExcessMaria GuerreroNoch keine Bewertungen

- Adc Lab Manual - Cycle 2Dokument28 SeitenAdc Lab Manual - Cycle 2Karthik KarthiksNoch keine Bewertungen

- Analog and Digital Circuits Complete Mannual 2013Dokument123 SeitenAnalog and Digital Circuits Complete Mannual 2013EASACOLLEGENoch keine Bewertungen

- DPCO ManualDokument64 SeitenDPCO Manualg2272049Noch keine Bewertungen

- Logic DesignDokument65 SeitenLogic DesignChaudhary WaseemNoch keine Bewertungen

- Combinational Logic CircuitsDokument39 SeitenCombinational Logic CircuitsRhea Daluddung SanchezNoch keine Bewertungen

- De Unit2 SlidesDokument167 SeitenDe Unit2 SlidesAravind RaoNoch keine Bewertungen

- Module 3 STDDokument93 SeitenModule 3 STDmatlabdec12Noch keine Bewertungen

- Digital Electronics LabmanualDokument66 SeitenDigital Electronics LabmanualToaster97Noch keine Bewertungen

- Linear Integrated Circuits Lab ManualDokument74 SeitenLinear Integrated Circuits Lab Manualarivurp100% (2)

- Binary To 9'S ComplementDokument3 SeitenBinary To 9'S ComplementMarco FraquetNoch keine Bewertungen

- DPCO Unit 1Dokument45 SeitenDPCO Unit 1Laks SadeeshNoch keine Bewertungen

- Four Bit Binary To Gray Code ConverterDokument23 SeitenFour Bit Binary To Gray Code ConverterAditya YadavNoch keine Bewertungen

- 27 DLD Lec 27 Combinational Design Dated 11 Nov 2022 Lecture SlidesDokument21 Seiten27 DLD Lec 27 Combinational Design Dated 11 Nov 2022 Lecture SlidesZuha FatimaNoch keine Bewertungen

- Ex No:4 Code Convertors: CS2207-Digital LabDokument7 SeitenEx No:4 Code Convertors: CS2207-Digital LabSuresh Babu PalpandiNoch keine Bewertungen

- Digital Lab ManualDokument87 SeitenDigital Lab ManualKALAIMATHINoch keine Bewertungen

- 6.magnitude ComparatorDokument3 Seiten6.magnitude ComparatorSudhan HariNoch keine Bewertungen

- Dhanush Ade Exp 6Dokument17 SeitenDhanush Ade Exp 6bobNoch keine Bewertungen

- EE/COSC 2390 Homework Set 5 Solutions Spring 2004Dokument4 SeitenEE/COSC 2390 Homework Set 5 Solutions Spring 2004Rohit MurarkaNoch keine Bewertungen

- Basic Digital Logic Design Notes PDFDokument138 SeitenBasic Digital Logic Design Notes PDFnandamsNoch keine Bewertungen

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsVon EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsBewertung: 5 von 5 Sternen5/5 (1)

- REF Probabilistic Gate-Level Power Estimation Using A NovelWaveform Set MethodDokument6 SeitenREF Probabilistic Gate-Level Power Estimation Using A NovelWaveform Set MethodsenthilvlNoch keine Bewertungen

- Fadd ExtendedDokument36 SeitenFadd ExtendedsenthilvlNoch keine Bewertungen

- Pre Internal 1Dokument2 SeitenPre Internal 1senthilvlNoch keine Bewertungen

- Operational Description and Message Format of PGPDokument1 SeiteOperational Description and Message Format of PGPsenthilvlNoch keine Bewertungen

- Fundamentals & Link LayerDokument38 SeitenFundamentals & Link LayersenthilvlNoch keine Bewertungen

- CNS QB 2 MK WaDokument25 SeitenCNS QB 2 MK WasenthilvlNoch keine Bewertungen

- Unit 1 QuestionDokument1 SeiteUnit 1 QuestionsenthilvlNoch keine Bewertungen

- Quartus Ii V7.2: The Signaltap Ii Logic Analyzer LabDokument15 SeitenQuartus Ii V7.2: The Signaltap Ii Logic Analyzer LabsenthilvlNoch keine Bewertungen

- Genetic Algorithm Model ExamDokument1 SeiteGenetic Algorithm Model ExamsenthilvlNoch keine Bewertungen

- Int 1Dokument1 SeiteInt 1senthilvlNoch keine Bewertungen

- Application LayerDokument31 SeitenApplication LayersenthilvlNoch keine Bewertungen

- Data Link Layer ConceptsDokument16 SeitenData Link Layer ConceptssenthilvlNoch keine Bewertungen

- Syllabus CNSDokument2 SeitenSyllabus CNSsenthilvlNoch keine Bewertungen

- Intruders, Passwords, and Intrusion DetectionDokument41 SeitenIntruders, Passwords, and Intrusion DetectionsenthilvlNoch keine Bewertungen

- Internal 1 Answer KeyDokument2 SeitenInternal 1 Answer KeysenthilvlNoch keine Bewertungen

- IT 3 QuestionDokument1 SeiteIT 3 QuestionsenthilvlNoch keine Bewertungen

- Simulated Output: Wallace:tree MR (3..0) MD (3..0) Booth - Encoder:booth Partial:ppDokument5 SeitenSimulated Output: Wallace:tree MR (3..0) MD (3..0) Booth - Encoder:booth Partial:ppsenthilvlNoch keine Bewertungen

- Internal Examination - 1 Internal Examination - 1Dokument1 SeiteInternal Examination - 1 Internal Examination - 1senthilvlNoch keine Bewertungen

- Model ExamDokument1 SeiteModel ExamsenthilvlNoch keine Bewertungen

- Cover PAGEDokument1 SeiteCover PAGEsenthilvlNoch keine Bewertungen

- MEIDokument1 SeiteMEIsenthilvlNoch keine Bewertungen

- Ex. No: Date: Creating Virtual Instrumentation For Simple Application AimDokument3 SeitenEx. No: Date: Creating Virtual Instrumentation For Simple Application AimsenthilvlNoch keine Bewertungen

- Embedded SystemsDokument2 SeitenEmbedded SystemssenthilvlNoch keine Bewertungen

- MEIDokument1 SeiteMEIsenthilvlNoch keine Bewertungen

- Analog To Digital Converters PresentationDokument31 SeitenAnalog To Digital Converters PresentationJitendra MishraNoch keine Bewertungen

- Introduction To ADCs, TutorialDokument58 SeitenIntroduction To ADCs, Tutorialsenthilvl100% (1)

- Department of Electronics and CommunicationDokument3 SeitenDepartment of Electronics and CommunicationsenthilvlNoch keine Bewertungen

- Course WorkDokument7 SeitenCourse WorksenthilvlNoch keine Bewertungen

- Arrer List With Subject Name III Ece-NewDokument18 SeitenArrer List With Subject Name III Ece-NewsenthilvlNoch keine Bewertungen

- PS1 ScanDokument2 SeitenPS1 ScanHarseno BasugewoNoch keine Bewertungen

- 11B-Consecutive Integer Word ProblemsDokument4 Seiten11B-Consecutive Integer Word Problemssasw111 sasw111Noch keine Bewertungen

- Unitary MethodDokument18 SeitenUnitary MethodanilNoch keine Bewertungen

- Calculating Speed, Distance, Time and AreaDokument3 SeitenCalculating Speed, Distance, Time and AreaAubrey Gay Sarabosquez100% (2)

- Equation of Motion PDFDokument2 SeitenEquation of Motion PDFMazvita TakawiraNoch keine Bewertungen

- Vtuupdates - Numerical Solution of PDEDokument39 SeitenVtuupdates - Numerical Solution of PDEShanthi.VNoch keine Bewertungen

- Exponential Distribution Theory and MethodsDokument158 SeitenExponential Distribution Theory and MethodsImad Tantawi100% (2)

- Elementary Statistics 2nd Edition Navidi Solutions Manual 1Dokument28 SeitenElementary Statistics 2nd Edition Navidi Solutions Manual 1suzanne100% (38)

- Pre-Calculus: Updated 09/15/04Dokument14 SeitenPre-Calculus: Updated 09/15/04Neha SinghNoch keine Bewertungen

- Diagnostic Exam Reviewer - Differential CalculusDokument5 SeitenDiagnostic Exam Reviewer - Differential CalculusHarold MangaNoch keine Bewertungen

- Advanced Control Using MatlabDokument541 SeitenAdvanced Control Using Matlabboilerqwerty81100% (2)

- Outline of Academic Disciplines - WikipediaDokument11 SeitenOutline of Academic Disciplines - WikipediamtkliemaNoch keine Bewertungen

- Assignment 1 Sequence Series MathongoDokument4 SeitenAssignment 1 Sequence Series MathongoNagireddy KalluriNoch keine Bewertungen

- Basic Calculus Final Exam ReviewDokument18 SeitenBasic Calculus Final Exam ReviewMafel JumuadNoch keine Bewertungen

- Assignment 3: Mrs. Seema P Diwan Walchand College of EngineeringDokument9 SeitenAssignment 3: Mrs. Seema P Diwan Walchand College of EngineeringSeema P DiwanNoch keine Bewertungen

- 1.1 Place ValueDokument21 Seiten1.1 Place ValueRahayu KasmuNoch keine Bewertungen

- College Algebra and Trigonometry 3rd Edition Ratti Test Bank 1Dokument108 SeitenCollege Algebra and Trigonometry 3rd Edition Ratti Test Bank 1phyllis100% (40)

- Direct Proportionality - Basics - 2Dokument3 SeitenDirect Proportionality - Basics - 2Sidra ShaikhNoch keine Bewertungen

- Army Public School RK Puram Secunderabad (202 - 21)Dokument1 SeiteArmy Public School RK Puram Secunderabad (202 - 21)Review ZodiacNoch keine Bewertungen

- Childrenthinkingmathematically PSRNDokument60 SeitenChildrenthinkingmathematically PSRNmarkus_danusantosoNoch keine Bewertungen

- Vibration Under General Forcing ConditionsDokument22 SeitenVibration Under General Forcing ConditionsespairNoch keine Bewertungen

- Automata PDFDokument21 SeitenAutomata PDFSamurai100% (3)

- Logarithm basics and properties explainedDokument14 SeitenLogarithm basics and properties explainedAnshiiiNoch keine Bewertungen

- Functions GuideDokument10 SeitenFunctions GuideRandy TabaogNoch keine Bewertungen

- Matrices and Determinants GuideDokument11 SeitenMatrices and Determinants GuideSunnyNoch keine Bewertungen

- Hard Margin SVM Dual Problem DerivationDokument2 SeitenHard Margin SVM Dual Problem DerivationSat AdhaNoch keine Bewertungen

- Introduction To Measure Theoretic Probability 2nd Edition Roussas Solutions ManualDokument18 SeitenIntroduction To Measure Theoretic Probability 2nd Edition Roussas Solutions Manualyvonnewelchdoafexwzcs100% (17)

- Robotics Frame Transformations GuideDokument20 SeitenRobotics Frame Transformations GuideBagusAdiwiluhungNoch keine Bewertungen

- Gen Math - Worksheet - 2 PART 2 - Properties of Rational FunctionDokument4 SeitenGen Math - Worksheet - 2 PART 2 - Properties of Rational FunctionJohn Nicholas TabadaNoch keine Bewertungen

- SR Maths Iib - 3Dokument2 SeitenSR Maths Iib - 3Yuga Tejeshwar ReddyNoch keine Bewertungen