Beruflich Dokumente

Kultur Dokumente

ABI 4.0 Spec

Hochgeladen von

Sushant KulkarniOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

ABI 4.0 Spec

Hochgeladen von

Sushant KulkarniCopyright:

Verfügbare Formate

Specification

February 2007

StarCore ABI 4.0

Agere Systems - Proprietary

Introduction

This document is a reference for the StarCore

Application Binary Interface (ABI) for the following

families of StarCore processor cores (and earlier

cores):

SC1000

SC2000

SC3000

The ABI definition ensures interoperability between

different tools, like compiler, assembler, linker and

debugger on object code level.

This document is intended for tool developers as

well as for low level assembly programmers.

To summarize , this document will discuss the

following topics:

The low level binary interface. It contains a

definition of all basic data types and the function

calling conventions.

The high level language issues. It describes the

C++ABI and the runtime functions of the

library.

The object file format. It describes the StarCore

extensions to the ELF object file format.

Specification

February 2007 Contents

Agere Systems - Proprietary 3

Contents

Preface About This Document 13

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Purpose. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Whats covered . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Conformance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Source Level Compatibility. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Whats New in StarCore ABI 4.0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

Additional Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Numbering systems . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Typographic notation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Special terms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Acknowledgements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Chapter 1 Low-Level Binary Interface 19

StarCore Architectures . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Endian Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Fundamental Data Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Aggregates and Unions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Bit Fields. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Argument Passing and Register Usage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Argument Passing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Return Value Passing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Register saving . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Register Saving and Restoring Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

ABI indicators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Argument Passing and Register Usage of ABI Version 2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Argument Passing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Variable Argument Passing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Return Value Passing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Register Saving . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Register Saving and Restoring Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Stack . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Stack Pointer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Frame and global pointers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Stack frame layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Stack unwinding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Field Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Status Register (SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Exception and Mode Register (EMR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

General Configuration Register (GCR). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Specification

Contents February 2007

4 Agere Systems - Proprietary

Modifier Control (MCTL) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Hardware loops. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Static Programming Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Enforce at COF Source. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Enforce at COF Target . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Loop Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Memory Models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Code Memory Models. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Data Memory Models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Chapter 2 High-Level Language Issues 47

Name Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

C Name Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

C++ Name Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

C System Calls . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Libraries. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

Compiler assist libraries . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

setjmp and longjmp layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Dynamic memory allocation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Calling conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Notation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Floating-point routines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Integer and fractional arithmetic routines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Optional long long routines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Register saving and restoring functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

C++ Support Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

C++ ABI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Controlling Object Construction Order . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

DSO Object Destruction API . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Demangler API . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Exception Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

External Names. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Vague Linkage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Chapter 3 Object File Format 63

Interface Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

The ELF Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Sections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Special Sections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

.SC100.delay_slots. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

.mw_info . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

.rom_init_tables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

.bsstab. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

.ovltab . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Relocation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Relocation types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Specification

February 2007 Contents

Agere Systems - Proprietary 5

Relocation stack. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Instruction address vs. VLES address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

NOTE Section . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

Program Headers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Debugging Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

DWARF register number mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Specification

Contents February 2007

6 Agere Systems - Proprietary

Specification

February 2007 Tables

Agere Systems - Proprietary 7

Tables

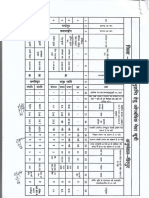

1 Mapping of C data types to the StarCore architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2 Mapping of C fractional types to the StarCore architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

3 C bit field types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

4 Register usage in the ABI 4 calling convention . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5 Register usage in the ABI 2 calling convention . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

6 StarCore ELF sections. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

7 Relocation type definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

8 Relocation stack operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

9 StarCore register number mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Specification

Tables February 2007

8 Agere Systems - Proprietary

Specification

February 2007 Figures

Agere Systems - Proprietary 9

Figures

1 Stack frame layout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

2 Object file format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

3 Vendor identification note format. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

4 User (application-specific) note format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

Specification

Figures February 2007

10 Agere Systems - Proprietary

Specification

February 2007 Examples

Agere Systems - Proprietary 11

Examples

1 Word bit and byte numbering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

2 Long word bit and byte numbering. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3 Double-long word bit and byte numbering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

4 Structure with internal and tail padding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

5 Union allocation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

6 Bit field alignment and padding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

7 Unnamed and zero-width bit fields. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

8 Function calls and allocation of arguments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

9 Function calls and allocation of arguments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

10 Generating stack unwinding symbols in assembly code . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

11 Code memory models. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

12 Data memory models . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

13 Saving and restoring functions usage example . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

14 ELF header structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

15 StarCore specifics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

16 Definition of macros for accessing e_flag parts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

17 Section header structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

18 Definition of opcode IDs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

19 Definition of macros for accessing opcode parts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

20 Relocation entry defined with Elf32_Rela . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

21 Program header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Specification

Examples February 2007

12 Agere Systems - Proprietary

Agere Systems - Proprietary 13

Preface About This Document

Overview

Purpose This document defines a set of standards intended to ensure interoperability between

conforming software components, such as, compilers, assemblers, linkers, debuggers on

object code level. These standards cover run-time aspects as well as object formats to be

used by compatible tool chains from StarCore and third party tools developers.

A benefit of this standard definition is interoperability of conforming tools. This allows

users to select the best tool for each phase of the application development cycle, rather

than being constrained to using an entire tool chain. Another benefit is compatibility of

conforming libraries. Programmers can build compatible binary libraries and assembly

code libraries, and be assured of their continued compatibility over time.

On the other hand, the ABI is designed to include only the minimal set of rules to ensure

object code compatibility. This gives a tool implementation the maximum flexibility.

Whats covered This specification addresses the following types of standards:

Low level run-time binary interface standards

Processor-specific binary interface (the instruction set and representation of

fundamental data types)

Function calling conventions (how arguments are passed and results are returned,

how registers are assigned, and how the calling stack is organized)

Object-file binary interface standards

Header convention

Section layout

Relocation information format

Debugging information format

Library standards

Compiler run-time libraries (integer routines and floating-point routines)

Conformance The ABI defines how separatly compiled and assembled modules can be used together in a

single application. This means that object files from different tool chains may be

combined in a single executable file.

Preface Specification

About This Document February 2007

Overview

14 Agere Systems - Proprietary

The ABI conformance is defined on public visible interfaces (e.g. external visible

functions or variables) of an object file. But a compiler implementation is free to make

deviations to the ABI for internal interfaces.

This means for example if two functions are in the same compilation module,

the compiler may take the set of used resources of the called function into

account. So the caller function may use free hardware loop resources or avoid

saving of untouched scratch registers. For static functions, the compiler may

even change the whole calling convention within a module.

A compiler implementation may implement optional deviations to the ABI, which have to

be explicitly enabled (e.g. by command line options). It must be defined by the compiler

implementation how such deviations are compatible to the standard ABI.

For example a compiler may provide a command line option to specify a

different default setting for mode bits. In this case all object files must be

compiled with this command line option to be compatible.

Features defined in this ABI are mandatory unless specifically stated otherwise. Optional

features, if implemented, must conform to the ABI.

Source Level

Compatibility

Source level compatibility on C or assembly source level is not defined in the ABI. But it

is recommended that compiler and assembler implementations follow the source level

conventions as described in the StarCore compiler and assembler manuals. These include

Assembly syntax

Compiler intrinsics

Pragmas

C/C++language extentions

Inline assembly

Specification Preface

February 2007 About This Document

Whats New in StarCore ABI 4.0

Agere Systems - Proprietary 15

Whats New in StarCore ABI 4.0

StarCore ABI 4.0 supersedes the previous revision (3.0) and includes information that

applies to the following StarCore families:

SC1000

SC2000

SC3000

Major changes from the previous revision include:

Chapter 3, Object File Format:

Added four new relocation types for the SC3000-family cores.

Preface Specification

About This Document February 2007

Additional Resources

16 Agere Systems - Proprietary

Additional Resources

The following standards provide useful reference information:

Tool Interface Standard (TIS) Executable and Linking Format (ELF) Specification,

Version 1.1, UNIX Systems Laboratories, Portable Formats Specification, 1995

DWARF Debugging Information Format, Revision: Version 2.0.0, Industry Review

Draft, UNIX International, Program Languages SIG, J uly 27, 1993

ANSI/IEEE Std 754-1985, IEEE standard for binary floating-point arithmetic data

types

ISO/IEC 9899:1999(E), International Standard - Programming LanguagesC, 2nd

Edition, International Organization for Standardization, December 1, 1999

ISO/IEC 14882:2003(E), International Standard - Programming LanguagesC, 2nd

Edition, International Organization for Standardization, October 15, 2003

Itanium C++ ABI, revision 1.71 (http://www.codesourcery.com/cxx-abi/abi.html)

also referred to as The Generic C++ABI.

The following StarCore documents are included by reference into this ABI.

SC1000-Family Processor Core Reference Manual

Describes the SC1000-family core architecture and programming model, including the

SC1200 and SC1400 instruction set.

SC2000-Family Processor Core Reference Manual

Describes the SC2000-family core architecture and programming model, including the

SC2200 and SC2400 instruction set.

SC3000-Family Processor Core Reference Manual

Describes the SC3000-family core architecture and programming model, including the

SC3200 and SC3400 instruction set.

StarCore C/C++ Compiler User Manual

Describes the StarCore compiler.

StarCore Assembler User Manual

Describes the StarCore assembler.

StarCore Linker User Manual

Describes the StarCore linker.

Specification Preface

February 2007 About This Document

Conventions

Agere Systems - Proprietary 17

Conventions

Introduction This document uses certain conventions to assist you in identifying, locating, and

understanding information.

Numbering systems The following suffixes identify different numbering systems:

Typographic notation The following typographic notations are used throughout this document:

Special terms The following terms have special meanings:

This suffix Identifies a

b Binary number. For example, the binary equivalent of the number 5 is written 101b.

d Decimal number. Decimal numbers are followed by this suffix only when the possibility of

confusion exists. In general, decimal numbers are shown without a suffix.

h Hexadecimal number. For example, the hexadecimal equivalent of the number 60 is written 3Ch.

Example Description

placeholder Items in italics are placeholders for information that you provide. Italicized text is also used

for the titles of publications and for emphasis.

code Fixed-width type indicates text that must be typed exactly as shown. It is used for

instruction mnemonics, symbols, subcommands, parameters, and operators. Fixed-width

type is also used for example code.

Term Meaning

byte An 8-bit data object

double-long A 64-bit data object

long A 32-bit data object

word A 16-bit data object

Preface Specification

About This Document February 2007

Acknowledgements

18 Agere Systems - Proprietary

Acknowledgements

The StarCore Application Binary Interface team included representatives from the

following companies:

We gratefully thank all participants for devoting their time and effort to create this

standard.

Agere Systems Inc. Metrowerks, Inc.

Altium Limited Motorola, Inc.

Green Hills Software, Inc. WindRiver Systems, Inc.

Lineo, Inc.

Agere Systems - Proprietary 19

Chapter 1 Low-Level Binary Interface

This chapter defines low-level system standards for the StarCore architectures of

processor cores, including:

Processor-specific binary interface (the instruction set and representation of

fundamental data types)

Function calling conventions (how arguments are passed and results are returned, how

registers are assigned, and how the calling stack is organized)

StarCore Architectures

The StarCore processor core architectures currently includes six cores: the SC1200, the

SC1400P, the SC2200, the SC2400 , the SC3200, and the SC3400. The architecture and

instruction set for each core is defined in that cores respective reference manual, as listed

in Additional Resources on page16. Programs written for these cores use their

instruction sets, as well as the instruction encodings and semantics of their architecture.

Programmers may assume that the instructions for these cores work as documented. Note

that all cores are backwards compatible to their respective predecessor, but while an

ABI-conforming SC1200 program will run on an ABI-conforming SC1400 processor, the

reverse is not always true.

To conform to the ABI, the processor must execute the architectures instructions and

produce the expected results. This ABI does not define requirements for the services

provided by an operating system, nor does it specify what instructions must be

implemented in hardware. A software emulation of the architecture could conform to the

ABI.

Programs that use non-StarCore instructions or capabilities do not conform to the StarCore

ABI. Such programs may produce unexpected results when run on machines lacking the

non-StarCore capability.

Chapter 1 Specification

Low-Level Binary Interface February 2007

Endian Support

20 Agere Systems - Proprietary

Endian Support

The StarCore architecture supports both big-endian and little-endian implementations.

This standard defines a binary interface for each. Note that program binaries that run on a

big-endian implementation are not portable to a little-endian implementation, and vice

versa. The same applies to the data generated by these programs, as well as to the layout of

data used by these programs (such as the layout of data generated by compilation tools).

The bytes that form the supported data types are ordered in memory according to the

following:

In a big-endian implementation, the most significant byte (MSB) is located in the

lowest address (byte 0).

In a little-endian implementation, the least significant byte (LSB) is located in the

lowest address (byte 0).

Specification Chapter 1

February 2007 Low-Level Binary Interface

Fundamental Data Types

Agere Systems - Proprietary 21

Fundamental Data Types

The StarCore architecture defines the following data types:

An 8-bit byte

A 16-bit word

A 32-bit long word

A 64-bit double-long word

The mapping of these data types depends on whether this data is mapped to registers or

memory. Data stored in registers are always little-endian mapped, whereas data in

memory are mapped according to the current endian mode.

Example1. Word bit and byte numbering

Register mapping

Memory mapping

Example2. Long word bit and byte numbering

Register mapping

Memory mapping

bit 15 8 7 0

byte 1

MSB LSB

byte 0

Little-Endian

bit 15 8 7 0

byte 1

MSB LSB

byte 0

Big-Endian

bit 15 8 7 0

byte 1

MSB LSB

byte 0

Little-Endian

bit 15 8 7 0

byte 0

MSB LSB

byte 1

Big-Endian

bit 31 24 23 16 15 8 7 0

byte 3

MSB LSB

byte 0

Little-Endian

bit 31 24 23 16 15 8 7 0

byte 3

MSB LSB

byte 0

Big-Endian

bit 31 24 23 16 15 8 7 0

byte 3

MSB LSB

byte 0

Little-Endian

bit 31 24 23 16 15 8 7 0

byte 0

MSB LSB

byte 3

Big-Endian

Chapter 1 Specification

Low-Level Binary Interface February 2007

Fundamental Data Types

22 Agere Systems - Proprietary

Example3. Double-long word bit and byte numbering

Register mapping

Memory mapping

Note Support for 64-bit data is optional and an implementation may not accept the long

long C type.

bit 31 24 23 16 15 8 7 0

Little-Endian

byte 3

LSB

byte 0

bit 63 56 55 48 47 40 39 32

byte 7

MSB

byte 4

bit 31 24 23 16 15 8 7 0

Little-Endian

byte 3

LSB

byte 0

bit 63 56 55 48 47 40 39 32

byte 7

MSB

byte 4

bit 31 24 23 16 15 8 7 0

Little-Endian

byte 3

LSB

byte 0

bit 63 56 55 48 47 40 39 32

byte 7

MSB

byte 4

bit 63 56 55 48 47 40 39 32

Big-Endian

byte 0

MSB

byte 3

bit 31 24 23 16 15 8 7 0

byte 4

LSB

byte 7

Specification Chapter 1

February 2007 Low-Level Binary Interface

Fundamental Data Types

Agere Systems - Proprietary 23

Table1 shows the mapping between these fundamental data types and the C language data

types. Note that fundamental data is always naturally aligned; that is, a double-long word

is 8-byte aligned, a long word is 4-byte aligned, and a word is 2-byte aligned.

Table 1. Mapping of C data types to the StarCore architecture

Type C type Size

(bits)

Alignment

(bits)

Limits StarCore

_Bool

1

8 8 0 through 1 Signed byte

Character char 8 8 2

7

through 2

7

1 Signed byte

si gned char

unsi gned char 8 8 0 through 2

8

1 Unsigned byte

shor t 16 16 2

15

through 2

15

1 Signed word

si gned shor t

unsi gned shor t 16 16 0 through 2

16

1 Unsigned word

Integral i nt 32 32 2

31

through 2

31

1 Signed long word

si gned i nt

enum

l ong

si gned l ong

unsi gned i nt 32 32 0 through 2

32

1 Unsigned long word

unsi gned l ong

l ong l ong

1

64 64 2

63

through 2

63

1 Signed double-long

word

si gned l ong l ong

1

unsi gned l ong l ong

1

64 64 0 through 2

64

1 Unsigned double-

long word

Pointer poi nt er t o dat a 32 32 0 through 2

32

1 Unsigned long word

poi nt er t o f unct i on

Floating-

point

2

f l oat 32 32 3.402e

38

through 1.175e

38

1.175e

38

through 3.402e

38

Unsigned long word

doubl e

3

32 or

64

32 or 64 2.225e

308

through 1.797e

308

or 1.175e

38

through 3.402e

38

Unsigned double-

long word

l ong doubl e

3

1

This data type is specified in the latest ISO C definition (ISO/IEC 9899:1999). Support of this data type is optional. If

used, this data type must be implemented with the size and alignment shown.

2

Floating-point types conform to the IEEE 754 format.

3

An implementation may choose between a 32-bit and a 64-bit doubl e type. A 32-bit doubl e is essentially the same

as a f l oat .

Chapter 1 Specification

Low-Level Binary Interface February 2007

Fundamental Data Types

24 Agere Systems - Proprietary

Fractional types are supported in C using intrinsic functions; Table2 shows the fractional

types that are supported.

Table 2. Mapping of C fractional types to the StarCore architecture

C type C type definition Size

(bits)

Alignment

(bits)

Limits

Fractional shor t 16 16

1 through

Long fractional l ong

i nt

32 32

1 through

Long fractional with extension

bits

Little-endian:

t ypedef st r uct {

unsi gned l ong body;

char ext ;

} Wor d40;

Big-endian:

t ypedef st r uct {

unsi gned l ong body;

char gap[ 3] ;

char ext ;

} Wor d40;

64 32

256 through

Double precision fractional t ypedef st r uct {

l ong msb;

unsi gned l ong l sb;

} Wor d64;

64 64

*

1 through

*

A word64 is 8-bytes aligned.

2

15

1 ( )

2

15

----------------------

2

31

1 ( )

2

31

----------------------

2

39

1 ( )

2

31

----------------------

2

63

1 ( )

2

63

----------------------

Specification Chapter 1

February 2007 Low-Level Binary Interface

Aggregates and Unions

Agere Systems - Proprietary 25

Aggregates and Unions

The alignment of aggregates (structures and unions) is the maximum of the following

values:

The alignment of their most strictly aligned member (that is, the member with the

largest alignment).

A minimum alignment of 4.

An implementation may provide a user option that overrides the minimum structure

alignment. In particular, if the user may select a minimum alignment of 0 or 1, the

aggregate alignment is simply the largest alignment of its members.

Modules compiled with different minimum alignments cannot interoperate if they

interface using structures or unions.

For example, a structure containing a char , a shor t , and an i nt must have a 4-byte

alignment to match the alignment of the i nt . Arrays have the same alignment as their

individual elements.

The size of any structure, array, or union must be an integral multiple of its alignment.

Structure and unions may require padding to meet size and alignment constraints:

An entire structure or union is aligned on the same boundary as its most strictly aligned

member.

Each member is allocated starting at the next byte that satisfies the alignment

requirement for that member. This may require internal padding.

If necessary, a structures size is increased to make it a multiple of the structures

alignment. This may require tail padding, depending on the last member.

In both endian modes, members are allocated starting with the low order (lowest

addressed) byte of the structure or union, as shown in the following examples. In

Example4, there is internal padding so that the first shor t (s1) starts at a word boundary.

Tail padding makes the structure size a multiple of the i nt members 4-byte alignment.

Chapter 1 Specification

Low-Level Binary Interface February 2007

Aggregates and Unions

26 Agere Systems - Proprietary

Example4. Structure with internal and tail padding

st r uct { / * 12 byt es, 4- byt e al i gned */

char c;

shor t s1;

i nt i ;

shor t s2;

};

Example5. Union allocation

uni on { / * 4 byt es, 4- byt e al i gned */

shor t s;

char c;

l ong l ;

};

bit 31 16 15 8 7 0

Little-Endian

byte 3

s1 pad c

byte 0

bit 63 32

byte 7

i

byte 4

bit 95 80 79 64

byte 11

pad s2

byte 8

bit 95 88 87 80 79 64

Big-Endian

byte 0

c pad s1

byte 3

bit 63 32

byte 4

i

byte 7

bit 31 16 15 0

byte 8

s2 pad

byte 11

bit 31 16 15 8 7 0

Little-Endian

byte 3

pad s

byte 0

pad c

l

bit 31 24 23 16 15 0

Big-Endian

byte 0

s pad

byte 3

c pad

l

Specification Chapter 1

February 2007 Low-Level Binary Interface

Bit Fields

Agere Systems - Proprietary 27

Bit Fields

Structure and union definitions may have bit fields as listed in Table3.

Support of _Bool is optional, but all other types shown in Table3 must be supported. This

ABI does not have requirements for l ong l ong bit fields.

Unsigned bit-field values range from 0 to 2

w1

, where w is the bit fields width in bits.

Signed bit-field values range from 2

w1

to 2

w1

1.

Table 3. C bit field types

C type Maximum width (bits)

_Bool

1

char

2

si gned char

2

unsi gned char

2

1 to 8

shor t

2

si gned shor t

2

unsi gned shor t

2

1 to 16

i nt

si gned i nt

enum

2

l ong

2

si gned l ong

2

unsi gned i nt

unsi gned l ong

2

1 to 32

1

Support of _Bool is optional. If implemented, it must be implemented with the width and range shown.

2

This bit field type is not required for ISO C conformance, but is required for ABI conformance.

Chapter 1 Specification

Low-Level Binary Interface February 2007

Bit Fields

28 Agere Systems - Proprietary

A plain bit field (one that is not explicitly declared signed or unsigned) is signed.

Although they may have type char , shor t , i nt , or l ong (which can have negative

values), bit fields of these types have the same range as bit fields of the same size with the

corresponding signed type. The same size and alignment rules that apply to other structure

and union members also apply to bit fields. The following rules additionally apply to bit

fields:

In little-endian implementations, bit fields are allocated right to left. The first bit field

occupies the least significant bits while subsequent bit fields occupy more significant

bits.

In big-endian implementations, bit fields are allocated left to right. The first bit field

occupies the most significant bits while subsequent bit fields occupy less significant

bits.

A bit field may not cross a boundary for its type. For example, a signed char bit field

cannot exceed eight bits in width, and it cannot cross a byte boundary.

Bit fields must share a storage unit with other structure and union members (either bit

field or non-bit field) if and only if there is sufficient space within the storage unit.

An unnamed bit field does not affect the alignment of its enclosing structure or union,

although an individual bit fields member offsets obey the alignment constraints. An

unnamed, zero-width bit field prevents any further member (either bit field or non-bit

field) from residing in the storage unit corresponding to the type of the zero-width bit

field.

Note in the following examples that alignments are driven not by the widths of the bit

fields but by the underlying types. Example6 shows a structure that is 4-byte aligned and

has a 4-byte size because of the i nt bit fields. There is internal padding so that the char

bit field does not cross a byte boundary, and so that the shor t member starts at a word

boundary. All members share a long word.

Example6. Bit field alignment and padding

st r uct { / * 4 byt es, 4- byt e al i gned */

i nt a : 3;

i nt b : 4;

char c : 5;

shor t d;

};

bit 31 16 15 13 12 8 7 6 3 2 0

byte 3

d pad c b a

byte 0

Little-Endian

pad

bit 31 28 25 24 23 19 18 16 15 0

byte 0

a b c pad d

byte 3

Big-Endian

pad

Specification Chapter 1

February 2007 Low-Level Binary Interface

Bit Fields

Agere Systems - Proprietary 29

In Example7, the structure is at least 2-byte aligned because the unnamed l ong bit field

does not affect structure alignment. (The actual alignment depends on the type alignment -

2 in this example - and the minimum structure alignment - see Aggregates and Unions

on page25.) The zero-width shor t bit field pads to the next word boundary.

Example7. Unnamed and zero-width bit fields

st r uct { / * 8 byt es, 2- byt e al i gned */

shor t a : 9;

shor t : 0;

char b : 5;

l ong : 15;

};

bit 31 21 20 16 15 9 8 0

Little-Endian

byte 3

pad b pad a

byte 0

bit 63 32

byte 7

pad

byte 4

bit 63 55 54 48 47 43 42 32

Big-Endian

byte 0

a pad b pad

byte 3

bit 31 0

byte 4

pad

byte 7

Chapter 1 Specification

Low-Level Binary Interface February 2007

Argument Passing and Register Usage

30 Agere Systems - Proprietary

Argument Passing and Register Usage

This section describes the argument passing and register usage of the ABI version 4. It

differs from the calling convention of ABI version 2. An implementation may optionally

provide both versions of the calling conventions.

Argument Passing The compiler tries to pass the first function arguments via the registers D0 to D3, and R0

to R3, according to the following rules:

If a function argument is of integral, floating point, or structure type, and its size is less

than or equal to 32bits, the argument is passed in a data register (D0 to D3). All

register bits exceeding the arguments size are defined by the sign of the corresponding

type. For example, an argument of type shor t is passed in bits 150 and bits 3916 are

equal to the value of bit 15 (the sign bit).

If a function argument is of pointer type, it is passed in an address register (R0 to R3).

If an implementation supports 64bits scalar data types (i.e. unsi gned l ong l ong,

l ong l ong or doubl e) and a function argument is of this type, it is passed in a data

register pair (either D0 and D1, or D2 and D3).The data register with the lower number

contains the most significant 32bits (sign or zero extended to 40bits, according to the

type), the other one contains the least significant 32bits (zero extended to 40bits),

regardless of the byte order.

If a function argument is of structure type, and its size is larger than 32bits and less or

equal to 64bits, it is passed in a data register pair (either D0 and D1, or D2 and

D3).The data register with the lower number contains the most significant 32bits, the

other one contains the least significant 32bits.

The register arguments are allocated while working off the argument list from left to

right. Whenever an argument fulfills one of the previously mentioned data type criteria

and a register (or register pair) out of the corresponding register list is still available, it

is assigned.

All arguments that are not passed via registers are passed on the stack. Stack arguments

adhere the rules of the previously specified standard calling convention.

Variable argument passing is handled as previously specified.

Specification Chapter 1

February 2007 Low-Level Binary Interface

Argument Passing and Register Usage

Agere Systems - Proprietary 31

Return Value Passing The return value is handled similar like the function arguments:

If the return value is of integral, floating point, or structure type, and its size is less than

or equal to 32bits, the return value is passed in D0. All register bits exceeding the

return values type size are defined by the sign of the corresponding type. For example,

an argument of type shor t is passed in bits 150 and bits 3916 are equal to the value

of bit 15 (the sign bit).

If an implementation supports 64bits scalar data types (i.e. unsi gned l ong l ong,

l ong l ong or doubl e) and a function return value is of this type, it is passed in the

data register pair D0 and D1. D0 contains the most significant 32bits (sign or zero

extended to 40bits, according to the type), D1contains the least significant 32bits

(zero extended to 40bits), regardless of the byte order.

If the return value is of structure type, and its size is larger than 32bits and less or equal

to 64bits, it is passed in D0 and D1. D0 contains the most significant bits, D1 contains

the least significant 32bits.

If the return value is of pointer type, it is passed in R0.

A st r uct or uni on larger than 64bits causes the compiler to allocate stack space for

the data structure on the caller's stack frame. The called function obtains a pointer to

the stack location in register R0 as a hidden function parameter. Hence the list of

available address registers for argument passing shrinks to R1, R2, R3.

Register saving A function must preserve following registers:

D4, D5, D6, D7: Only bits 0-31 are preserved. The extension bits (32-39) are either

preserved or set to the value of bit 31, i.e. the register is sign extended.

R4, R5, R6, R7

All other registers may be destroyed by a function.

Register Saving and

Restoring Functions

The compiler may use runtime function calls instead of PUSH and POP instructions for

register saving and restoring to reduce code size. These functions are described in

Register saving and restoring functions on page57.

Example8. Function calls and allocation of arguments

Function Call 1:

char count ( char sc, l ong l ong l l , unsi gned shor t us) ;

When the count function is called in the source code, the compiler passes the first

argument (sc) in D0, and the second argument (l l ) in the register pair D2 and D3. Finally

the last argument (us) is passed in D1, as this is the last available data register. Bits398

of D0 are set to bit 7 (sign bit). Bits3932 of D2 are set to zero and bits3932 of D3 are

set to bit 31 (sign bit). The last argument is unsigned, hence bits3916 of D1 are set to

zero. The caller expects the return value in the least significant 8bits of D0. Bits398 of

D0 are equal to the sign bit (bit 7).

Function Call 2:

st r uct poi nt r ot at e ( Wor d40 x, i nt *i , char *f or mat , . . . ) ;

Chapter 1 Specification

Low-Level Binary Interface February 2007

Argument Passing and Register Usage

32 Agere Systems - Proprietary

When the r ot at e function is called in the source code, the compiler passes the first

function argument (x) in the register pair D0 and D1, the second argument (a pointer to i )

in R0, and all further arguments on the stack. However, if the returned structure (st r uct

poi nt ) has a size of more than 64 bits, the compiler uses the address register R0 as

pointer to the structure and the second function argument (pointer to i ) is passed in R1.

Specification Chapter 1

February 2007 Low-Level Binary Interface

Argument Passing and Register Usage

Agere Systems - Proprietary 33

Table4 summarizes register usage in the ABI 4 calling convention.

ABI indicators To avoid an accidentally mismatch of calling conventions, the linker checks if the calling

conventions of caller and callee functions match. The compiler generates special

indication-symbols for all ABI4 functions and function references. The indication-

symbols have following naming convention:

__abi 4. function-label-name

For example the function f oo( ) has the label name _f oo and the ABI4 indication symbol

is named __abi 4. _f oo. These symbols are generated for functions, which are defined in

a module and functions, which are referenced from a module.

With this information the linker prints an error if an ABI4 function calls an ABI2 function

or vice versa. Note that this error checking is not done if a function is called over a

function pointer.

Table 4. Register usage in the ABI 4 calling convention

Register Caller

saved

Callee

saved

Remark

D0 + First numeric argument

Return numeric value

D1-D3 + Second to fourth numeric argument

D4D7 +

D8D15 +

D0.eD3.e +

D3.eD7.e + The extension bits are either not modified by the callee or sign extended,

i.e. bits 31 to 39 are equal.

D8.eD15.e +

R0 + First pointer argument

Return pointer value

Structure or union return address

R1-R3 + Second to fourth pointer argument

R4-R7 +

R8R15, B0B7 +

N0N3, M0M3 +

SP (NSP, ESP) +

Chapter 1 Specification

Low-Level Binary Interface February 2007

Argument Passing and Register Usage of ABI Version 2

34 Agere Systems - Proprietary

Argument Passing and Register Usage of ABI Version 2

This section describes the argument passing and register usage of the ABI version 2. This

version of the calling convention is only provided for backward compatibility. An

implementation should prefer the ABI version 4 calling convention. An implementation

may optionally provide both versions of the calling conventions.

Argument Passing Arguments are passed to functions according to the following standard calling convention.

If the first function argument is 4 or fewer bytes and is an integral type or floating type,

the argument is passed in D0. If it is a pointer, it is passed in R0. If the first argument is

a structure or union, it is passed on the stack.

If the first argument is a l ong l ong (where implemented), doubl e, or l ong

doubl e, it is passed in D0 and D1, D0 containing the most significant long word and

D1 containing the least significant long word, regardless of the endianess mode.

If the second argument is 4 or fewer bytes and is an integral type or floating type and

D1 is not already used by the first argument, the argument is passed in D1. If it is a

pointer, it is passed in R1. If the second argument is a structure or union, it is passed on

the stack.

When an argument is passed in D0 or D1, all the register bytes that are part of the

argument are defined by extension to the corresponding type. For example, a first

argument of type short is passed in D0[15:0], and the contents of D0[31:16] and D0.e

contain the sign of the argument. An argument of type float is passed in D[31:0], sign-

extended to 40 bits.

When an argument is passed in both D0 and D1, D1.e contains zero and D0.e is defined

by extension to the corresponding type: sign-extending the 32 most significant bits for

long long and long double, zero-extending the 32 most significant bits for unsigned

long long.

All other arguments are passed on the stack. Note that the first argument may be passed

on the stack, followed by the second argument being passed in D1 or R1.

Arguments are passed on the stack, in order, from higher addresses to lower addresses.

Each argument on the stack is passed in the byte order appropriate for the endian mode.

An argument that is 8-byte aligned according to Fundamental Data Types on

page21, Aggregates and Unions on page25, and Bit Fields on page27 is passed

8-byte aligned on the stack. All other arguments are passed using their alignment

constrains. For example, a short type is 2-byte aligned.

The constituent bytes of an integral argument of fewer than 4 bytes are located on the

stack using their original size and constrains.

The alignment of aggregates on the stack is at least 4 bytes, even if the compiler

optionally supports an aggregate alignment of less than 4 bytes.

Specification Chapter 1

February 2007 Low-Level Binary Interface

Argument Passing and Register Usage of ABI Version 2

Agere Systems - Proprietary 35

Variable Argument

Passing

ANSI C requires that before a function with a variable argument list is called, it must be

declared with a prototype containing a trailing ellipsis (. . . ). Following rules apply to

functions with variable arguments.

Functions with a variable number of arguments pass the last fixed argument and all

subsequent variable arguments on the stack. Such arguments of fewer than 4 bytes are

located on the stack as if the argument had been promoted to 32 bits. The rules above

apply to arguments before the last fixed argument.

Variable arguments, which have a size of 8 bytes or more, are passed 8-bytes aligned

on the stack.

If the compiler supports aggregates with an alignment of less than 4 bytes then

following rule applies for variable arguments in big endian: The padding bytes of

aggregates with a size, which is not a multiple of 4 bytes, are inserted before the

aggregate. I.e. in big endian, the aggregate stack end address (and not the start address)

of a variable argument is always 4 or 8 bytes aligned.

Return Value Passing Return values are passed according to the following rules

An integral return value, other than a l ong l ong, is sign or zero extended to 40 bits

and returned in D0. A float value is returned in D0, sign-extended to 40 bits. A l ong

l ong, doubl e, or l ong doubl e return value is returned in D0 and D1, D0 containing

the most significant long word and D1 containing the least significant long word,

regardless of the endianess mode. D1 is zero-extended to 40 bits. D0 is sign-extended

to 40 bits for returned values of type long double and long long, and it is zero-extended

to 40 bits for unsigned long long.

A pointer return value is returned in R0.

A function returning a structure or union receives in R2 the address of the returned

structure or union. The caller allocates space for the returned object.

Register Saving A function must preserve following registers:

D6, D7: Only bits 0-31 are preserved. The extension bits (32-39) are either preserved

or set to the value of bit 31, i.e. the register is sign extended.

R6, R7

All other registers may be destroyed by a function.

Register Saving and

Restoring Functions

The compiler may use runtime function calls instead of PUSH and POP instructions for

register saving and restoring to reduce code size. These functions are described in

Register saving and restoring functions on page57.

Chapter 1 Specification

Low-Level Binary Interface February 2007

Argument Passing and Register Usage of ABI Version 2

36 Agere Systems - Proprietary

Example9 shows two function calls and the arguments that are allocated for each call.

Example9. Function calls and allocation of arguments

Function Call 1:

f oo( i nt a1, st r uct f our byt es a2, st r uct ei ght byt es a3, shor t a4)

Arguments:

a1 - i n r egi st er d0

a2 - on t he st ack at SP - 4 ( SP = st ack poi nt er addr ess)

a3 - on t he st ack at SP - 12

a4 - on t he st ack at SP - 14

Function Call 2:

bar ( l ong *b1, i nt b2, char b3, i nt b4[ ] )

Arguments:

b1 - i n r 0

b2 - i n d1

b3 - on st ack at SP - 4

b4 on st ack at SP - 8

Specification Chapter 1

February 2007 Low-Level Binary Interface

Argument Passing and Register Usage of ABI Version 2

Agere Systems - Proprietary 37

Table5 summarizes register usage in the ABI 2 calling convention.

Table 5. Register usage in the ABI 2 calling convention

Register Caller

saved

Callee

saved

Remark

D0 + First numeric argument

Return numeric value

D1 + Second numeric argument

D2D5 +

D6D7 +

D8D15 +

D0.eD5.e +

D6.eD7.e + The extension bits are either not modified by the callee or sign extended,

i.e. bits 31 to 39 are equal.

D8.eD15.e +

R0 + First pointer argument

Return pointer value

R1 + Second pointer argument

R2 + Structure or union return address

R3R5 +

R6-R7 +

R8R15, B0B7 +

N0N3, M0M3 +

SP (NSP, ESP) +

Chapter 1 Specification

Low-Level Binary Interface February 2007

Stack

38 Agere Systems - Proprietary

Stack

Stack Pointer The SP register serves as the stack pointer. SP will point to the first available location,

with the stack direction being towards higher addresses (that is, a push will be

implemented as (sp)+). Initially a long word with value 1 is pushed at offset 0 on the

stack to serve as a top-of-stack marker. The stack pointer must be 8-byte aligned.

Frame and global

pointers

This ABI standard does not require the use of a frame pointer or a global pointer. If,

however, the use of a frame pointer or a global pointer is necessary, a compiler may

allocate R7 as a frame pointer and R6 as a global pointer. When these registers are

allocated for this purpose, they should be saved and restored as part of the function

prologue/epilog code.

Stack frame layout The stack pointer points to the top (high address) of the stack frame. Space at higher

addresses than the stack pointer is considered invalid and may actually be unaddressable.

The stack pointer value must always be a multiple of eight.

Figure1 shows typical stack frames for a function and indicates the relative position of

local variables, arguments, and return addresses. The stack grows upward from low

addresses.

The outgoing arguments area is located at the top (higher addresses) of the frame.

The caller puts argument variables that do not fit in registers into the outgoing arguments

area. If all arguments fit in registers, this area is not required. A caller may allocate

outgoing arguments space sufficient for the worst-case call, use portions of it as necessary,

and not change the stack pointer between calls.

Local variables that do not fit into the local registers are allocated space in the local

variables area of the stack. If there are no such variables, this area is not required.

The caller must reserve stack space for return variables that do not fit in registers. This

return buffer area is typically located with the local variables, but it may be the address of

a global variable. This space is typically allocated only in functions that make calls

returning structures.

A return address value of FFFFFFFFh (1) is used to denote the current frame as the

outermost (oldest) frame on the current call stack. This convention requires that the

outermost frame be manually constructed and that sufficient object file details are

available to determine the sizes of all frames on the current call stack. The sole purpose of

this convention is to stop stack unwinding while debugging.

Beyond these requirements, a function is free to manage its stack frame in any way

desired.

Specification Chapter 1

February 2007 Low-Level Binary Interface

Stack

Agere Systems - Proprietary 39

Figure 1. Stack frame layout

Stack unwinding The compiler will create special symbols when a module is compiled without debug

enabled (for example., the - g compiler option is not used). These symbols will appear as

local symbols in the . symt ab ELF section and will have the following syntax:

Text St ar t _<modul e_name> : modul e s l ow PC

Text End_<modul e_name> : modul e s hi gh PC

St ackOf f set _<l abel > : si ze of st ack at l abel

FuncEnd_<f unct i on_name> : f unct i on s hi gh PC

Where:

<module_name>is the base name of the source file. The base name must follow the

same conventions as assembly language labels. These conventions are outlined in

Symbol names on page103.

<label>is a program label within the function. The value of St ackOf f set _label is

the size of the stack frame at the label. The size is in 4-byte words and does not include

an implied J SR/BSR two-word stack push.

<function_name>is the function name, without a leading underscore.

High addresses

Low addresses

Incoming arguments

Return address

Outgoing arguments

Local variables

SP

and

saved registers

Chapter 1 Specification

Low-Level Binary Interface February 2007

Stack

40 Agere Systems - Proprietary

For example, a hel l o. c program might generate the ELF symbol sequence shown below.

In this example, the binding LOCAL means an ELF symbol binding of STB_LOCAL, the

type NOTYPE means a symbol type of STT_NOTYPE, and the section ABS means a symbol

table entry of SHN_ABS.

Example10 illustrates how these symbols might be defined in an assembly-language

program.

Example10. Generating stack unwinding symbols in assembly code

sect i on . t ext l ocal

Text St ar t _hel l o

; **************************************************************

; Exampl e f unct i on _mai n

; **************************************************************

gl obal _mai n

_mai n t ype f unc

[ push r 6

push r 7

]

DW_2

. . .

[ pop r 6

pop r 7

]

DW_5

r t s

FuncEnd__mai n

St ackOf f set __mai n equ 0 ; At _mai n sp = 0 wor ds

St ackOf f set _DW_2 equ 2 ; At DW_2 sp = 2 wor ds

St ackOf f set _DW_5 equ 0 ; At DW_5 sp = 0 wor ds

Text End_hel l o

endsec

Val ue Si ze Bi ndi ng Type Sect i on Name

- - - - - - - - - - - - - - - - - - - - - - - - - - - - - - -

10120h 0 LOCAL NOTYPE . t ext Text St ar t _hel l o

0h 0 LOCAL NOTYPE ABS St ackOf f set __mai n

2h 0 LOCAL NOTYPE ABS St ackOf f set _DW_2

0h 0 LOCAL NOTYPE ABS St ackOf f set _DW_5

1012Ah 0 LOCAL NOTYPE . t ext DW_2

10136h 0 LOCAL NOTYPE . t ext DW_5

10138h 0 LOCAL NOTYPE . t ext FuncEnd_mai n

10138h 0 LOCAL NOTYPE . t ext Text End_hel l o

Specification Chapter 1

February 2007 Low-Level Binary Interface

Configuration Registers

Agere Systems - Proprietary 41

Configuration Registers

Field Types There are several types of fields in the configuration registers.

Field with defined state

Such a field has a defined value at function entry and function exit. The compiler is free to

change the field inside a function, but it must make sure that it restores the defined state

before calling another function or before returning from the function.

In addition a compiler implementation may provide options to assume a different state of a

field. But then no compatibility exists to modules, which are compiled with the default

state.

Destroyed field

A destroyed field has no defined value at function entry and exit, but the compiler is free

to modify the field in a function. This means that the compiler must assume that a the

content of such a field will change when calling a function. the field doesnt need to be

restored before a function returns.

Field under user control

The compiler does not assume any value for such a field. Nor it does change such a field

automatically. But A compiler may provide means for reading and writing such a field,

e.g. with intrinsics. So the user can explicitly access such a field.

Status field

A status field is like a destroyed field. In contrast to a destroyed field, status fields are not

set explicitly by the compiler, but implicitly by certain instructions.

Status Register (SR) SLF, LF3, LF2, LF1, LF0

These flags must be 0 on function entry. This means a function may use all four hardware

loops.

I, OVE, DI, EXP, PE

These fields are under user control.

VF3-VF0

These fields may be destroyed by a function.

SM2

The 16-bit arithmetic saturation mode must be enabled on function entry and exit, i.e. the

SM2 bit must be 1b.

S

The scaling bit is a status bit and has not a defined value on function entry and exit.

SCM

Scaling must be disabled on function entry and exit, i.e. the scaling mode must be 00b.

Chapter 1 Specification

Low-Level Binary Interface February 2007

Configuration Registers

42 Agere Systems - Proprietary

RM

The rounding mode must be set to to twos-complement rounding on function entry and

exit, i.e. the RM bit must be 1b.

SM

The 32-bit arithmetic saturation mode must be enabled on function entry and exit, i.e. the

SM bit must be 1b.

It is recommended that a compiler implementation provides an option so that no saturation

is assumed.

T, C

The true and carry bits are status bit and dont have a defined value on function entry and

exit.

Exception and Mode

Register (EMR)

All fields in the EMR register are status bits or under user control. Therefore they dont

have a defined value at function entry and exit.

General

Configuration

Register (GCR)

BAM[2]

The bit 2 of the BAM field indicates the shift direction of the DOALIGN instruction. In

little endian this field must be 0b (shift right), in big endian this field must be 1b (shift left)

at function entry and exit.

BAM[1...0]

The lower 2 bits of the BAM field may be destroyed by a function. They dont have a

defined value at function entry and exit. They can be set by the SETALIGN instruction,

which is usually done before the DOALIGN instruction is executed.

Modifier Control

(MCTL) Register

The MCTL register must be 0 at function entry and exit. This defines the memory address

calculation methods for R0R7 as linear.

Hardware loops From the definition of the loop fields in SR (SLF, LF3, LF2, LF1, LF0) follows that all

hardware loop resources are available for the compilers use. As it is assumed that no

nesting occurs when entering a function, a function may use all four nesting levels for its

own use.

Specification Chapter 1

February 2007 Low-Level Binary Interface

Static Programming Rules

Agere Systems - Proprietary 43

Static Programming Rules

Overview The programming rules are described in the core reference manuals (CRM). Many of

these rules require a certain execution distance, or separation, between two instructions.

There are two kinds of distances used in the definition of these rules:

VLES based

Cycle based

In some cases the code sequence to be checked includes a Change Of Flow (COF)

instruction, and the rule violation candidates involves an instruction pair that one belongs

to the execution flow before the COF and the other belongs to the flow after the COF.

A COF instruction, which are of interest for the ABI are J SR, BSR and RTS. This means

that the ABI defines how the rules have to be checked around function calls and returns.

Enforce at COF

Source

The default for most programming rules is that the rule is enforced at the COF source

(before a function call and before a function return).The compiler has to make sure that the

rules are not violated, regardless of what instruction is located at the COF target (at a

function begin and after a function return).

Following rules must be enforced at the COF source:

A.1

A.2

T.1

SR.2

Enforce at COF Target For performance reasons following rule must be enforced at the COF target (at a function

begin and after a function return):

SR.4

This means that at a COF target no MOVE like instruction may be located, which reads or

writes to EMR.

Loop Rules Rules, which affect the loop registers and loop modes are not part of the ABI, because the

code, which affects a loop may not be splitted across functions and there may not be a

function call inside a loop (except the compiler is under control of the called function).

Chapter 1 Specification

Low-Level Binary Interface February 2007

Memory Models

44 Agere Systems - Proprietary

Memory Models

Overview A compiler implementation may provide several memory models for code and data to

generate more compact instructions for addressing. There are several ways to specify the

memory model. For example, commnd line switches can specify the memory model for all

entities in a compilation module. It is also possible that a compiler provides pragmas to

specify the memory model of separate functions or variables.

The memory models allow the compiler to generate references to global and static data

and function calls without global knowledge as to the variables or functions final

allocation address in memory. For each model, the compiler will assume that references to

global and static data and functions fit within the corresponding size implied by the model.

The expectation is that the linker will generate errors whenever a symbolic reference is

resolved to not fit within the range defined by the memory model.

Object files, which are compiled with different memory models (or contain entities with

different memory models) may be linked together. But all constraints, which are imposed

by the memory models, must be satisfied. Otherwise the linker will issue an error.

Code Memory Models There are two memory models for code entities, i.e. functions:

small: The distance between a function call and the function entry must be within 20

bits, so that a 20-bit PC-relative BSR or J SR instruction may be generated.

huge: There is no restriction on the distance between the function call and the function

entry. Therefore the compiler must generate a 32-bit absolute call.

Example11. Code memory models

; Smal l memor y model

br s >_f unc ( 2 16- bi t wor ds)

; Huge memor y model

j sr _f unc ( 3 16- bi t wor ds)

Data Memory Models Following memory models are defined for data entities, i.e. global and static variables

small: Variables must be located in the lower 64 KB of memory. This allows the use of

a short addressing mode when accessing the variables.

large: There is no restriction on the placement of variables. Therefore the compiler

must generate a 32 bit addresssing mode to access the variables.

tiny: Variables must be located in the lower 32 KB of memory. This allows to use a

MOVE.W instruction for loading the address of the data into an R-register. This

memory model is optional

tiny for small variables: For non-array variables up to a size of 8 bytes, the tiny model

is used. For array variables and variables larger that 8 bytes, the default memory model

(usually big memory) is used. This memory model is optional.

Specification Chapter 1

February 2007 Low-Level Binary Interface

Memory Models

Agere Systems - Proprietary 45

Example12. Data memory models

; Smal l memor y model

move. l <_var , d0 ( 2 16- bi t wor ds)

moveu. l #_var , d0 ( 3 16- bi t wor ds)

; Bi g memor y model

move. l _var , d0 ( 3 16- bi t wor ds)

moveu. l #_var , d0 ( 3 16- bi t wor ds)

; Ti ny memor y model

move. l <_var , d0 ( 2 16- bi t wor ds)

move. w #_var , d0 ( 2 16- bi t wor ds)

; Ti ny f or smal l var i abl es memor y model ( wi t h bi g memor y as def aul t )

move. l <_smal l var , d0 ( 2 16- bi t wor ds)

move. w #_smal l var , d0 ( 2 16- bi t wor ds)

move. l _l ar gevar , d0 ( 3 16- bi t wor ds)

moveu. l #_l ar gevar , d0 ( 3 16- bi t wor ds)

Chapter 1 Specification

Low-Level Binary Interface February 2007

Memory Models

46 Agere Systems - Proprietary

Agere Systems - Proprietary 47

Chapter 2 High-Level Language Issues

Name Mapping

C Name Mapping Externally visible names in the C language are prefixed by an underscore (_ ) when

generating assembly language symbol names. For example, the following:

voi d t est f unc( ) {

. . .

}

generates following assembly name:

_t est f unc

C++ Name Mapping Externally visible C++language names are encoded using the rules from the generic C++

ABI, encoding known as name mangling. The external name of a C++symbol is formed

by prefixing an underscore character (_) to the mangled name of the symbol. For example,

the following:

i nt Cl ass: : member f unc( char , l ong) const {

. . .

}

generates following assembly name:

__ZNK5Cl ass10member f uncEcl

Chapter 2 Specification

High-Level Language Issues February 2007

C System Calls

48 Agere Systems - Proprietary

C System Calls

There are several typedefs specified in POSIX.1 which are required for system call

wrappers. These types are defined as follows for the StarCore architecture:

t ypedef unsi gned i nt mode_t ;

t ypedef l ong i nt of f _t ;

t ypedef unsi gned i nt si ze_t ;

t ypedef i nt ssi ze_t ;

t ypedef unsi gned l ong cl ock_t ;

t ypedef unsi gned l ong t i me_t ;

The following system calls must also be supported:

i nt open( const char *, i nt , . . . ) ; / / Thi r d ar g i s mode_t i f pr esent .