Beruflich Dokumente

Kultur Dokumente

Comp Logic System

Hochgeladen von

Dwaipayan Gupta0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

42 Ansichten33 SeitenThis document provides information about a 12-week certificate program in information systems with a focus on computer architecture and logic systems. It outlines the course content, assessment breakdown, attendance policy, fees, and contact schedule. The academic planner provides a weekly outline of topics to be covered, assigned readings, learning objectives, and preparation questions. Assessment includes an individual assignment, midterm exam, team project, and final exam. Attendance of at least 70% is required to sit for the final exam.

Originalbeschreibung:

logic

Originaltitel

Comp logic system

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenThis document provides information about a 12-week certificate program in information systems with a focus on computer architecture and logic systems. It outlines the course content, assessment breakdown, attendance policy, fees, and contact schedule. The academic planner provides a weekly outline of topics to be covered, assigned readings, learning objectives, and preparation questions. Assessment includes an individual assignment, midterm exam, team project, and final exam. Attendance of at least 70% is required to sit for the final exam.

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

42 Ansichten33 SeitenComp Logic System

Hochgeladen von

Dwaipayan GuptaThis document provides information about a 12-week certificate program in information systems with a focus on computer architecture and logic systems. It outlines the course content, assessment breakdown, attendance policy, fees, and contact schedule. The academic planner provides a weekly outline of topics to be covered, assigned readings, learning objectives, and preparation questions. Assessment includes an individual assignment, midterm exam, team project, and final exam. Attendance of at least 70% is required to sit for the final exam.

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 33

OLYMPIA BUSINESS SCHOOL

School of Computing & I nformation Science

CERTIFICATE IN INFORMATION SYSTEMS

FILO-TEXT

Computer Architecture & Logic Systems

May, 1999

12 weeks

RAFFLES EDUCATION GROUP

Kuala Lumpur w Petaling Jaya w Penang w Singapore w Jakarta w Bangkok w

Beijing w London w New-York

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 2 SCISCA & LD

TABLE OF CONTENTS

TABLE OF CONTENTS............................................................................................................................... 2

INTRODUCTION.......................................................................................................................................... 3

THE SUBJECT COMPUTER ARCHITECTURE & LOGIC SYSTEMS ...................................................................... 3

HOW TO USE THE FILO-TEXT?............................................................................................................... 4

ASSESSMENT............................................................................................................................................... 5

INDIVIDUAL ASSIGNMENT ............................................................................................................................ 5

MID-TERM EXAMINATION............................................................................................................................. 5

TEAM PROJECT............................................................................................................................................. 5

FINAL EXAMINATION.................................................................................................................................... 6

ATTENDANCE.............................................................................................................................................. 6

FEES............................................................................................................................................................... 6

CONTACT-TIME.......................................................................................................................................... 7

FULL-TIME................................................................................................................................................... 7

PART-TIME................................................................................................................................................... 7

THE ACADEMIC TEAM ............................................................................................................................. 8

THE ACADEMIC PLANNER....................................................................................................................... 9

WEEK 1 ....................................................................................................................................................... 10

WEEK 2 & 3 ................................................................................................................................................ 13

WEEK 4 ....................................................................................................................................................... 16

WEEK 5 ....................................................................................................................................................... 18

WEEK 6 ....................................................................................................................................................... 21

WEEK 7 ....................................................................................................................................................... 23

WEEK 8 ....................................................................................................................................................... 25

WEEK 9 ....................................................................................................................................................... 26

WEEK 10 ..................................................................................................................................................... 28

WEEK 11 ..................................................................................................................................................... 30

WEEK 12 ..................................................................................................................................................... 32

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 3 SCISCA & LD

INTRODUCTION

THE SUBJECT COMPUTER ARCHITECTURE & LOGIC SYSTEMS

Computer Architecture & Logic Systems will introduce to the students the basic and

advanced level in computer architecture.

This subject will emphasize on algorithms and design to impart to the students an

understanding of how and why computers function as they do. There will also be examples

and theories that the students have to adopt in order to understand the concepts of computer

logic and programming.

The objective of this subject will be to inject the basic understanding on how the

computer works and why.

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 4 SCISCA & LD

HOW TO USE THE FILO-TEXT?

The Filo-text is a tool providing you guidance for this subject. It provides you a general

information on the following:

Assessment

Attendance

Fees

Contact time

The academic team

The academic planner

For every week, it then provides you with the following information:

The topic

The objective(s) of the lecture

The textbook and the chapter(s) and page(s) related to the given topic

The other reference books available to you in the library

Additional reference material for your own research

The objective(s) of the tutorial

Questions to prepare for discussion during the tutorial

Questions for your personal research

Use the Filo-text to prepare yourself prior to the lecture, between the lecture and the

tutorial and after the tutorial.

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 5 SCISCA & LD

ASSESSMENT

Student assessment will be evaluated based on the following breakdown:

1) Individual Assignment 15 %

2) Mid-Term Examination 15 %

3) Team Project 20 %

4) Final Examination 50 %

Total 100 %

INDIVIDUAL ASSIGNMENT

An individual assignment will be given to the student on the first week and will have to

be returned no later than week 6. The marked assignment will be returned to the student by

no later than week 8.

The assignment will be related to the topics covered between week 1 and week 4

inclusive. It will comprise a written report of approximately 500 words.

Should the student fail to submit his/her assignment on week 6, the result will

automatically be nil.

MID-TERM EXAMINATION

A mid-term examination will be conducted during the lecture session of week 8. It will

assess the students knowledge and understanding of the topics covered up to week 6.

The results, together with the answer scripts, will be returned to the students no later then

week 10.

Should a student be absent without a valid apology, the result will automatically be nil.

TEAM PROJECT

A team project will be assigned to students during the first week. The team will comprise

of 4 to 6 students.

The report of the team project will have to be submitted to the subject lecturer by no later

than week 10 and will be presented on week 11. Late submission wont be entertained and

will automatically result in no marks being awarded.

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 6 SCISCA & LD

FINAL EXAMINATION

The final examination will be conducted on week 13 or week 14 and its duration will be 3

hours.

Registration for the examination is open from week 3 and is closing on week 6. Make

sure you register on time. No late registration will be entertained.

The format of the examination is as follows:

Section A - Multiple Choice Questions 20 * 1 Point

Section B - Short Answer Questions 5 * 4 Points

Section C - Essay-type Questions Any 3 out of 5 * 20 Points

Total 100 Points

ATTENDANCE

Attendance for both the lectures and the tutorials is compulsory. Any student not

attending a class should provide a medical certificate or a written justification (signed by a

parent or guardian in the case of a full-time student). Should a student fail to do so, he/she

will be considered truant.

Should a student attendance for a given subject be lower then 70 %, he/she will not be

allowed to sit for the final examination.

Punctuality is equally important. The lecturer is entitled to refuse entry into the

classroom to any student that would present him/herself late.

FEES

The registration fee is to be paid upon registration.

The course fee is paid either in full, per semester or by instalments. For payments made

in full, the payment is due before the first lecture. For payments made by semester, the

payment per semester is due on the first day of the semester. For monthly instalments, the

first payment is due on the first day of classes while the subsequent payments are due on the

first day of each subsequent month.

Should any student have difficulty to pay his/her fees on time, he/she must meet with the

(Deputy) Principal to arrange an alternative. Any student that would not have settled his/her

fees and would not have met with the (Deputy) Principal will not be allowed to attend classes

nor to sit for an examination.

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 7 SCISCA & LD

CONTACT-TIME

FULL-TIME

The duration of the classes is 12 weeks. Contact time consists of 1 1/2 hours of lecture

and 1 1/2 hours of tutorial per week.

PART-TIME

The duration of the classes is 12 weeks. Contact time consists of 1 hours of lecture per

week.

For each hour of contact, the student is expected to spend at least 2 hours of unsupervised

work, be individually or in group.

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 8 SCISCA & LD

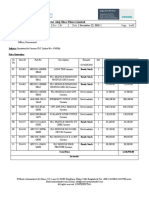

THE ACADEMIC TEAM

At the beginning of the first lecture, please fill-in the following:

Day Time Room

Starting Finishing

Lecture

Lecturer

Consultation

Tutorial

Tutor

Consultation

Class Lecturer

Consultation

Lecturer-in-Charge

Consultation

Principal

Consultation

Head of Department

Consultation

Subject Representative

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 9 SCISCA & LD

THE ACADEMIC PLANNER

Here is an outline of the topics you will cover, week after week.

Week Date Topic

1 Computer operation: assembly language

2 Boolean algebra and gate network

3 Boolean algebra and gate network

4 Map Simplification

5 Flipflops, Registers & Binary counters

6 The Arithmetic-Logic unit

7 The memory element

8 Mid-Term Examination

9 Input and output devices

10 Buses and interfaces

11 The control unit

12 Computer architecture

13 & 14 Final Examination

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 10 SCISCA & LD

WEEK 1

Lectures Subject: COMPUTER OPERATION: ASSEMBLY LANGUAGES

Lectures Objectives:

On completion of this lecture, the student will have acquired the following:

Knowledge of the decimal system.

Knowledge of bistable devices.

Counting in the binary system.

Knowledge of converting decimal numbers to binary, octal and hexadecimal.

Understanding of complements in other number systems.

How to compute addition and subtraction in the 1s and 2s complement system.

Textbook:

Chapter(s) Pages

Computer Architecture and Logic Design / Thomas Bartee 2 21 - 38

Reference Books:

Chapter(s) Pages

Computers and Information Systems / Fuori and Gioia

Computers and Information Systems / Hutchinson and

Sawyer

Data Structures, Algorithms, and Software Principles /

Thomas A. Standish

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 11 SCISCA & LD

Tutorials Subject: COMPUTER OPERATION: ASSEMBLY LANGUAGES

Tutorials Objectives:

On completion of this tutorial, the student will have acquired the following:

Transformed the knowledge acquired during the lecture into a sound

understanding of the topics covered.

Compared the concepts taught during the lecture with concepts presented in other

reference books.

Applied the concepts taught during the lecture to the real life environment.

Identified the relevance of the concepts taught during the lecture to the real needs

of todays professionals.

Questions to prepare for discussion during the tutorial:

1) Make up a hexadecimal addition table.

2) Show 2 decimal numbers that when converted to the IBM floating-point number system,

will have .0011 in bits 9, 10, 11 and 12.

3) For the 64-bit IBM floating-point number format, find the largest and smallest non-zero

number that can be represented.

4) A hexadecimal Odometer displays F34B, what is the next reading?

5) List some advantages and disadvantages of sign-magnitude and 2s complement

numbering system in representing the mantissas of floating-point number.

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 12 SCISCA & LD

Questions available for self-assessment:

1) Convert the following decimal numbers to equivalent binary numbers.

a) 43 b) 64 c) 2048.0625

2) Convert the following binary numbers to equivalent decimal numbers.

a) 1011 b) 100100 c) 10111010 d) 101.011

3) Perform the following multiplications and divisions in the binary number system.

a) 15 * 13 b) 7.75 * 2.5 c) 22.5 * 4.75

4) Convert the following binary numbers to both their 1s and 2s complements.

a) 1101 b) 1010 c) 1011

5) Perform the following subtractions using 9s and 10s complements.

a) 8 - 4 b) 27.6 - 23.4 c) 0.55 - 0.42

6) Perform the following subtractions of binary numbers using both their 1s and 2s

complements.

a) 1010 - 1011 b) 0.1111 - 0.101 c) 11.11 - 10.11

7) Write the first 12 numbers in the base 4 number system.

8) Convert the following hexadecimal numbers to binary system.

a) 9 b) AB c) 12B

9) How many different binary numbers can be stored in a register consisting of 4 switches?

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 13 SCISCA & LD

WEEK 2 & 3

Lectures Subject: BOOLEAN ALGEBRA AND GATE NETWORKS

Lectures Objectives:

On completion of this lecture, the student will have acquired the following:

Understanding of the fundamental concepts of boolean algebra.

The AND gates and OR gates.

Complementation and inverters.

Evaluation of logical expressions.

Knowledge of the basic laws of boolean algebra.

How to simplify Boolean expressions.

Understanding of DeMorgans theorem.

Textbook:

Chapter(s) Pages

Computer Architecture and Logic Design / Thomas Bartee 3 55 - 78

Reference Books:

Chapter(s) Pages

Computers and Information Systems / Fuori and Gioia

Computers and Information Systems / Hutchinson and

Sawyer

Data Structures, Algorithms, and Software Principles /

Thomas A. Standish

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 14 SCISCA & LD

Tutorials Subject: BOOLEAN ALGEBRA AND GATE NETWORKS

Tutorials Objectives:

On completion of this tutorial, the student will have acquired the following:

Transformed the knowledge acquired during the lecture into a sound

understanding of the topics covered.

Compared the concepts taught during the lecture with concepts presented in other

reference books.

Applied the concepts taught during the lecture to the real life environment.

Identified the relevance of the concepts taught during the lecture to the real needs

of todays professionals.

Questions to prepare for discussion during the tutorial:

1) Convert the following expressions to sum-of-products form:

(a) (A + B) (B + C)(A +C)

(b) (A + C)(A + B + C)(A + B)

2) Prove the following theorem:

(x + y)(x +y) = x

3) Draw a Karnaugh Map in X, Y, Z for :-

(a) M0 + M1 + M5 + M7

(b) M1 + M3 + M5

(c) M1 + M2 + M3 + M5

(d) M0 + M5 + M7

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 15 SCISCA & LD

Questions available for self-assessment:

1) Demonstrate by means of truth tables the validity of the following identities:

(a) DeMorgans theorem for three variables: (xyz) = x + y + z

(b) The second distributive law: x = y.z = ( x + y) (x + z)

1) Give the dual of the rule x + x.y = x + y

2) Prepare a truth table for the following Boolean expressions:

a) A.B + A.B b) A.C + AC

3) Describe the digital logic gates with graphic symbols and their truth tables.

4) Convert the following expressions to sum-of-products: (a + b) (c + b)

5) Define the duality theorem.

6) What are the digital logic gates? Identify their name, graphic symbols, switching

functions and truth-tables.

7) Prepare a truth table for the following boolean switching expression: x(y + z) + x.y

8) Show that the dual of the exclusive-OR is equal to its complement.

9) Find the complement of f = x + y.z; then show that f.f = 0 and f + f = 1.

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 16 SCISCA & LD

WEEK 4

Lectures Subject: MAP SIMPLIFICATION

Lectures Objectives:

On completion of this lecture, the student will have acquired the following:

How to simplify expressions by using Karnaugh map

Design methods using NAND and NOR gates.

Understanding of NAND-to-AND and NOR-to-OR gate networks.

Textbook:

Chapter(s) Pages

Computer Architecture and Logic Design / Thomas Bartee 3 78 81

91 - 103

Reference Books:

Chapter(s) Pages

Computers and Information Systems / Fuori and Gioia

Computers and Information Systems / Hutchinson and

Sawyer

Data Structures, Algorithms, and Software Principles /

Thomas A. Standish

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 17 SCISCA & LD

Tutorials Subject: MAP SIMPLIFICATION

Tutorials Objectives:

On completion of this tutorial, the student will have acquired the following:

Transformed the knowledge acquired during the lecture into a sound

understanding of the topics covered.

Compared the concepts taught during the lecture with concepts presented in other

reference books.

Applied the concepts taught during the lecture to the real life environment.

Identified the relevance of the concepts taught during the lecture to the real needs

of todays professionals.

Questions to prepare for discussion during the tutorial:

1) Using as few gates as possible, design a NAND-to-AND gate network that realizes the

following Boolean algebra expression.

A B C D + A B C D + A B C D + A B C D + A B C D

2) Prove the two basic De-Morgan Theorems, using the proof of perfect induction

3) Design an OR to AND gate combinational network for the Boolean algebra expression:

ABCD + ABCD + ABCD + (ABCD + ABCD)

Questions available for self-assessment:

1) Describe combinational circuits with an example.

2) Draw a logic diagram using only two-input NAND gates to implement the following

expression: (a.b + a.b) (c.d + c.d)

3) Simplify the Boolean function f(x, y, z) = (2, 3, 4, 5).

4) Given the following Boolean function: f = a.c + a.b + a.b.c + b.c

(a) Express it in sum of minterms;

(b) Find the minimal sum of products expression.

5) Simplify the following Boolean expression using four-variable maps:

w.z + x.z + x.y + w.x.z

6) Find the minterms of the following Boolean expression by first plotting each function in a

map: w.x.y + x.z + w.x.z

7) Draw Karnaugh map for the expression: xyz + xy.z + x y z

8) Simplify the following Boolean functions in product of sums:

F(a, b, c, d) = (1, 3, 5, 7, 13, 15)

9) Find eight different two-level gate circuits to implement f = xy.z + x y z + w

10) Prove the two basic DeMorgan theorems, using the proof by perfect induction.

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 18 SCISCA & LD

WEEK 5

Lectures Subject: FLIP FLOPS, REGISTERS & BINARY COUNTERS

Lectures Objectives:

On completion of this lecture, the student will have acquired the following:

Understanding of the RS Flip-Flop.

Understanding of transfer circuits.

Knowledge of the clock wave form.

Understanding of Flip-Flop Design (gated flip-flop, master-slave flip-flop).

Understanding of shift registers

Understanding of binary counters & JK flip flop

Understanding of BCD counters

Textbook:

Chapter(s) Pages

Computer Architecture and Logic Design / Thomas Bartee 4 132 - 152

Reference Books:

Chapter(s) Pages

Computers and Information Systems / Fuori and Gioia

Computers and Information Systems / Hutchinson and

Sawyer

Data Structures, Algorithms, and Software Principles /

Thomas A. Standish

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 19 SCISCA & LD

Tutorials Subject: FLIP FLOPS, REGISTERS & BINARY COUNTERS

Tutorials Objectives:

On completion of this tutorial, the student will have acquired the following:

Transformed the knowledge acquired during the lecture into a sound

understanding of the topics covered.

Compared the concepts taught during the lecture with concepts presented in other

reference books.

Applied the concepts taught during the lecture to the real life environment.

Identified the relevance of the concepts taught during the lecture to the real needs

of todays professionals.

Questions to prepare for discussion during the tutorial:

1) Explain the positive-going edge and negative-going edge.

2) Draw the circuit diagram for a transfer circuit.

3) Draw the RS flip-flop waveforms.

4) Design a Counter, using 3 JK flip-flops, X1,X2, X3 and whatever gates that you like to

count as follows:

X1 X2 X3

0 0 1

0 1 1

0 1 0

1 1 1

1 0 1

0 0 1

0 1 1

0 1 0

5) The rules of designing Counter using JK and RS Flip-Flop has been given. Derive the

rules for designing a counter using D flip-flop.

6) Design a JK flip-flop counter

7) Draw the diagram of input and output for a binary sequence detector.

8) Draw the diagram of gates and flip-flops for a sequence detector and its waveform.

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 20 SCISCA & LD

Questions available for self-assessment:

1) Draw a set of wave forms for S and R and X and X so that the flip flop will have the

signal 0011010 on the output line.

2) If the AND gate connected to the R input of X

1

in transfer circuit fails so that its output is

always 1, we will expect, after a few transfer, that X

1

will always be in what state? Why?

3) If the X output is a flip-flop is connected to an inverter, the inverters output will always

be the same as the X output of the flip-flop. True or false? Why?

4) Draw a set of wave forms for S and R so that the flip-flop will have the output signals

101110001 on the X output line.

5) Draw a set of wave forms for the flip-flop so that flip-flop will have the output signals

0010110 on its Y output line.

6) Draw the diagram of shift register with waveforms.

7) Draw the diagram of binary counter with waveforms.

8) Draw the circuit diagram of gated-clocked binary counter.

9) What is the binary number that represents 3 in 2s complements system, if we represent

the number by using a sign digit plus 4 magnitude digit.

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 21 SCISCA & LD

WEEK 6

Lectures Subject: THE ARITHMETIC-LOGIC UNIT

Lectures Objectives:

On completion of this lecture, the student will have acquired the following:

Integer representation

Binary half-adder and full-adder

Parallel Binary Adder

Addition and Subtraction in a Parallel Arithmetic element

Binary-coded-decimal Adder

Shift operation

Textbook:

Chapter(s) Pages

Computer Architecture and Logic Design / Thomas Bartee 5 190-205

209 - 211

Reference Books:

Chapter(s) Pages

Computers and Information Systems / Fuori and Gioia

Computers and Information Systems / Hutchinson and

Sawyer

Data Structures, Algorithms, and Software Principles /

Thomas A. Standish

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 22 SCISCA & LD

Tutorials Subject: THE ARITHMETIC-LOGIC UNIT

Tutorials Objectives:

On completion of this tutorial, the student will have acquired the following:

Transformed the knowledge acquired during the lecture into a sound

understanding of the topics covered.

Compared the concepts taught during the lecture with concepts presented in other

reference books.

Applied the concepts taught during the lecture to the real life environment.

Identified the relevance of the concepts taught during the lecture to the real needs

of todays professionals.

Questions to prepare for discussion during the tutorial:

1) What is an Adder? Explain?

2) Compare the different types of Adder. How do you combine half adders to obtain full

adder?

3) How does addition and subtraction in a parallel arithmetic element.

4) Design a half adder using only NAND gates.

5) Design a full-subtracter using only NOR gates.

Questions available for self-assessment:

1) Explain how the integer representation works. Try with some examples.

2) Draw the diagram of a half-adder.

3) Draw the diagram of a full-adder.

4) Draw the diagram of a parallel binary adder.

5) Explain how subtraction and addition work in a parallel arithmetic element.

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 23 SCISCA & LD

WEEK 7

Lectures Subject: THE MEMORY ELEMENT I

Lectures Objectives:

On completion of this lecture, the student will have acquired the following:

Introduction to RAM.

Understanding of Static RAM, Dynamic RAM

Understanding of ROM.

Understand virtual memory

Understand the cache memory and cache organization

Textbook:

Chapter(s) Pages

Computer Architecture and Logic Design / Thomas Bartee 6 245 247

263 275

293 - 305

Reference Books:

Chapter(s) Pages

Computers and Information Systems / Fuori and Gioia

Computers and Information Systems / Hutchinson and

Sawyer

Data Structures, Algorithms, and Software Principles /

Thomas A. Standish

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 24 SCISCA & LD

Tutorials Subject: THE MEMORY ELEMENT

Tutorials Objectives:

On completion of this tutorial, the student will have acquired the following:

Transformed the knowledge acquired during the lecture into a sound

understanding of the topics covered.

Compared the concepts taught during the lecture with concepts presented in other

reference books.

Applied the concepts taught during the lecture to the real life environment.

Identified the relevance of the concepts taught during the lecture to the real needs

of todays professionals.

Questions to prepare for discussion during the tutorial:

1. Explain DRAM.

2. Draw DRAM timing diagram.

3. Draw the circuit diagram of ROM.

4. Draw a Diode ROM that adds 3 to the each of the first six BCD numbers

5. Draw the flowchart for a virtual memory system with cache memory.

6. What are the main functions performed by a memory unit?

7. Give reasons why the page size in a paged virtual memory system should be neither

very small nor very large.

8. A Cache sweep is performed in some virtual memory system when a process finishes

and a new process takes its place .Discuss the effect of the strategy on tag bit and

cache design

9. Explain the concept of cache memory and why is it useful.

Questions available for self-assessment:

1) How do you understand read-write random-access memory?

2) Draw a diagram for basic memory cell.

3) Explain SRAM. Draw the SRAM memory timing diagram.

4) Fixed head disk memory reduces total access time by avoiding seek time or latency.

Which is avoided and why?

5) Discuss these memory technologies, relating cost per bit, access time and data transfer

rate

Dynamic IC RAMS

Static IC RAMS

CD-ROMS

6) What is virtual memory?

7) What are the two approaches to virtual memory organization?

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 25 SCISCA & LD

WEEK 8

MID-TERM EXAMINATION

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 26 SCISCA & LD

WEEK 9

Lectures Subject: INPUT AND OUTPUT DEVICES

Lectures Objectives:

On completion of this lecture, the student will have acquired the following:

Knowledge of different input/output media.

Error detecting and error correcting codes

ADC, shaft encoder, flash convertor

Textbook:

Chapter(s) Pages

Computer Architecture and Logic Design / Thomas Bartee 7 322 - 346

Reference Books:

Chapter(s) Pages

Computers and Information Systems / Fuori and Gioia

Computers and Information Systems / Hutchinson and

Sawyer

Data Structures, Algorithms, and Software Principles /

Thomas A. Standish

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 27 SCISCA & LD

Tutorials Subject: INPUT AND OUTPUT DEVICES

Tutorials Objectives:

On completion of this tutorial, the student will have acquired the following:

Transformed the knowledge acquired during the lecture into a sound

understanding of the topics covered.

Compared the concepts taught during the lecture with concepts presented in other

reference books.

Applied the concepts taught during the lecture to the real life environment.

Identified the relevance of the concepts taught during the lecture to the real needs

of todays professionals.

Questions to prepare for discussion during the tutorial:

1) Show how a flash converter works for a 3-bit system. Draw the gates from the comparator

outputs to the binary numbers.

2) Derive a rule for converting from Gray code to binary.

3) What is error correcting code?

4) What is error detecting code?

Questions available for self-assessment:

1) Draw the block diagram of ADC.

2) Write down the methods to convert from Gray to binary or from binary to Gray code.

3) Explain the flash converters.

4) Explain shaft encoder.

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 28 SCISCA & LD

WEEK 10

Lectures Subject: BUSES AND INTERFACES

Lectures Objectives:

On completion of this lecture, the student will have acquired the following:

Understanding of interconnecting system components.

Understanding of the functions IRQ and DMA.

Knowledge of the I/O addressing techniques.

Memory-mapped I/O.

Knowledge of the interrupts in Input / Output systems.

Textbook:

Chapter(s) Pages

Computer Architecture and Logic Design / Thomas Bartee 8 372 375

389 - 399

Reference Books:

Chapter(s) Pages

Computers and Information Systems / Fuori and Gioia

Computers and Information Systems / Hutchinson and

Sawyer

Data Structures, Algorithms, and Software Principles /

Thomas A. Standish

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 29 SCISCA & LD

Tutorials Subject: BUSES AND INTERFACES

Tutorials Objectives:

On completion of this tutorial, the student will have acquired the following:

Transformed the knowledge acquired during the lecture into a sound

understanding of the topics covered.

Compared the concepts taught during the lecture with concepts presented in other

reference books.

Applied the concepts taught during the lecture to the real life environment.

Identified the relevance of the concepts taught during the lecture to the real needs

of todays professionals.

Questions to prepare for discussion during the tutorial:

1) What is the basic advantage of the priority interrupt over a non-priority system?

2) What is the difference between a program controlled transfer and a DMA transfer?

3) Explain the function of interrupts?

4) What are the different types of interface addressing?.

Questions available for self-assessment:

1) Cite some advantages of memory-mapped I/O versus specific I/O versus specific I/O

instructions.

2) Cite some disadvantages of memory-mapped I/O versus specific I/O versus specific I/O

instructions.

3) Explain the meaning of direct memory access and why it is desirable in some cases.

4) Explain how peripheral devices interrupt a computer with a single-bus organisation?

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 30 SCISCA & LD

WEEK 11

Lectures Subject: THE CONTROL UNIT

Lectures Objectives:

On completion of this lecture, the student will have acquired the following:

Construction of an instruction word

Understanding of the instruction cycle and execution cycle organization.

Textbook:

Chapter(s) Pages

Computer Architecture and Logic Design / Thomas Bartee 9 417 - 424

Reference Books:

Chapter(s) Pages

Computers and Information Systems / Fuori and Gioia

Computers and Information Systems / Hutchinson and

Sawyer

Data Structures, Algorithms, and Software Principles /

Thomas A. Standish

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 31 SCISCA & LD

Tutorials Subject: THE CONTROL UNIT

Tutorials Objectives:

On completion of this tutorial, the student will be able to:

Transformed the knowledge acquired during the lecture into a sound

understanding of the topics covered.

Compared the concepts taught during the lecture with concepts presented in other

reference books.

Applied the concepts taught during the lecture to the real life environment.

Identified the relevance of the concepts taught during the lecture to the real needs

of todays professionals.

Questions to prepare for discussion during the tutorial:

1) Write a microprogram for the instruction ASL.

2) Write a microprogram for the instruction ASL. (arithmetic shift left).

3) What is a memory address register?

4) What is Op-code register?

Questions available for self-assessment:

1) What is the register transfer language?

2) What is an instruction cycle?

3) What is an execution cycle? Explain with diagram.

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 32 SCISCA & LD

WEEK 12

Lectures Subject: COMPUTER ARCHITECTURE

Lectures Objectives:

On completion of this lecture, the student will have understood the following:

Representation of instructions and data.

Direct, Immediate, Relative, Indirect, Indexed Addressing.

Subroutine calls & Interrupts.

Textbook:

Chapter(s) Pages

Computer Architecture and Logic Design / Thomas Bartee 10 453 - 476

Reference Books:

Chapter(s) Pages

Computers and Information Systems / Fuori and Gioia

Computers and Information Systems / Hutchinson and

Sawyer

Data Structures, Algorithms, and Software Principles /

Thomas A. Standish

School of Computing & Information Science Computer Architecture & Logic Systems

Olympia Business School Page 33 SCISCA & LD

Tutorials Subject: COMPUTER ARCHITECTURE

Tutorials Objectives:

On completion of this tutorial, the student will have acquired the following:

Transformed the knowledge acquired during the lecture into a sound

understanding of the topics covered.

Compared the concepts taught during the lecture with concepts presented in other

reference books.

Applied the concepts taught during the lecture to the real life environment.

Identified the relevance of the concepts taught during the lecture to the real needs

of todays professionals.

Questions to prepare for discussion during the tutorial:

1. What is direct addressing?

2. What is indirect addressing?

3. What is subroutine?

4. Explain stacks.

Questions available for self-assessment:

1. What is the difference between an immediate, a direct, and an indirect address instruction

word?

2. Give 3 examples of external interrupts and internal interrupts.

3. Discuss the advantages and disadvantages for the following addressing strategies in a

microcomputer :

(a) Paging

(b) Indirect addressing

(c) Index registers

Das könnte Ihnen auch gefallen

- Master the New York City Specialized High School Admissions TestVon EverandMaster the New York City Specialized High School Admissions TestNoch keine Bewertungen

- Motivating for STEM Success: A 50-step guide to motivating Middle and High School students for STEM success.Von EverandMotivating for STEM Success: A 50-step guide to motivating Middle and High School students for STEM success.Noch keine Bewertungen

- A D I S: Lympia Usiness ChoolDokument44 SeitenA D I S: Lympia Usiness Choolbhavana16686Noch keine Bewertungen

- Indus RelationDokument32 SeitenIndus RelationKhairy Azman100% (1)

- MGT ACC1Dokument41 SeitenMGT ACC1MsKhan00780% (3)

- MGT ACC3Dokument46 SeitenMGT ACC3MsKhan0078Noch keine Bewertungen

- Module 8 SyllabusDokument6 SeitenModule 8 Syllabusapi-265557783Noch keine Bewertungen

- New MA125 Course Syllabusrev12!15!1Dokument17 SeitenNew MA125 Course Syllabusrev12!15!1naos23Noch keine Bewertungen

- Eng102 9AMDokument7 SeitenEng102 9AMjeanninestankoNoch keine Bewertungen

- Eng102-Bc06 15fa StankoDokument7 SeitenEng102-Bc06 15fa StankojeanninestankoNoch keine Bewertungen

- 2013-14 AEUS Sem2 Student Info Handout 9janDokument9 Seiten2013-14 AEUS Sem2 Student Info Handout 9janBen WongNoch keine Bewertungen

- COM001 Kyungjae LeeDokument4 SeitenCOM001 Kyungjae LeeArnold MukaratiNoch keine Bewertungen

- Fall 2014 CHME 2010 SyllabusDokument6 SeitenFall 2014 CHME 2010 SyllabusSarah Al-mNoch keine Bewertungen

- Standard 4Dokument15 SeitenStandard 4hima67Noch keine Bewertungen

- ECO610-70 Syllabus H2 2020-2021Dokument8 SeitenECO610-70 Syllabus H2 2020-2021muzzamilNoch keine Bewertungen

- Eng101-Bc08 16sp StankoDokument12 SeitenEng101-Bc08 16sp StankojeanninestankoNoch keine Bewertungen

- Eng 100bc Syllabus Sp14Dokument7 SeitenEng 100bc Syllabus Sp14jeanninestankoNoch keine Bewertungen

- PGDSMA Brochure 2021Dokument22 SeitenPGDSMA Brochure 2021ABHISHEK KUMARNoch keine Bewertungen

- Lecture 01Dokument35 SeitenLecture 01Arju LubnaNoch keine Bewertungen

- AVI1O Student Course Outline PDFDokument3 SeitenAVI1O Student Course Outline PDFartwithmisschanNoch keine Bewertungen

- MAE501Syllabus PDFDokument5 SeitenMAE501Syllabus PDFlogan_prashantNoch keine Bewertungen

- PPPA CUJ Masters SyllabusDokument13 SeitenPPPA CUJ Masters SyllabusRodrigo Uribe BravoNoch keine Bewertungen

- 300-308-DW 40 W24 Jennifer SigouinDokument7 Seiten300-308-DW 40 W24 Jennifer SigouinEvelyne UkNoch keine Bewertungen

- Course Syllabus For ACC1002XDokument3 SeitenCourse Syllabus For ACC1002XethanchiaaNoch keine Bewertungen

- HWC Cis 142 SyllabusDokument7 SeitenHWC Cis 142 SyllabusyotnomukNoch keine Bewertungen

- MENG310 Beirut Syllabus Sec A Shaito Fall 2010Dokument6 SeitenMENG310 Beirut Syllabus Sec A Shaito Fall 2010Mouin SoukiNoch keine Bewertungen

- ASTRON 0085 Outlier Syllabus - Spring 2020 - Regular Term (14-Wk) - 12-2Dokument7 SeitenASTRON 0085 Outlier Syllabus - Spring 2020 - Regular Term (14-Wk) - 12-2VEDANT K. GUPTANoch keine Bewertungen

- AI: Introduction: Dept. of Computer Science Faculty of Science and TechnologyDokument36 SeitenAI: Introduction: Dept. of Computer Science Faculty of Science and TechnologyBishowjit DattaNoch keine Bewertungen

- Syllabus 11amDokument7 SeitenSyllabus 11amjeanninestankoNoch keine Bewertungen

- Spring 10Dokument4 SeitenSpring 10Theodore LiwonganNoch keine Bewertungen

- Financial Statements SyllabusFall2016Dokument6 SeitenFinancial Statements SyllabusFall2016MD PrasetyoNoch keine Bewertungen

- Syllabus - Math For Business - BBus - Nguyen Thi Thu Van PDFDokument7 SeitenSyllabus - Math For Business - BBus - Nguyen Thi Thu Van PDFMai TrầnNoch keine Bewertungen

- ECO 341K 33755 SyllabusDokument5 SeitenECO 341K 33755 SyllabusMack Coleman DowdallNoch keine Bewertungen

- Introduction To Information Technology: ITP 101 (4 Units)Dokument7 SeitenIntroduction To Information Technology: ITP 101 (4 Units)standalonembaNoch keine Bewertungen

- PHIL 110 Fall 2013 SyllabusDokument8 SeitenPHIL 110 Fall 2013 SyllabusbenjaminzenkNoch keine Bewertungen

- CIT 456 Syllabus Fall 2012 v2 8-24-2012Dokument6 SeitenCIT 456 Syllabus Fall 2012 v2 8-24-2012Salmi MatNoch keine Bewertungen

- English 11 SyllabusDokument2 SeitenEnglish 11 SyllabusKeith BuenaventuraNoch keine Bewertungen

- Course Intro Eng 101 2023-2024 FallDokument20 SeitenCourse Intro Eng 101 2023-2024 Fallahmed.adel.mazen2000Noch keine Bewertungen

- Course Information: Handbook For Additional InformationDokument10 SeitenCourse Information: Handbook For Additional InformationSean F-WNoch keine Bewertungen

- Syllabus BFIN2039 Fall 2023Dokument4 SeitenSyllabus BFIN2039 Fall 2023Diana CañasNoch keine Bewertungen

- Math101 202301 Syllabus-3Dokument3 SeitenMath101 202301 Syllabus-3otlacasNoch keine Bewertungen

- Bio SyllabusDokument3 SeitenBio SyllabusCBNoch keine Bewertungen

- C1500 Syllabus S20Dokument6 SeitenC1500 Syllabus S20Samiul Alim LesumNoch keine Bewertungen

- Guidelines For Online StudentsDokument5 SeitenGuidelines For Online StudentsMarisaNoch keine Bewertungen

- Marleneanu de Course OfferingsDokument8 SeitenMarleneanu de Course Offeringsapi-226161206Noch keine Bewertungen

- Business English Eng102: M Arket L Eader - Business LifeDokument4 SeitenBusiness English Eng102: M Arket L Eader - Business LifeAmine BensayahNoch keine Bewertungen

- Coward Fall 2020 21434A2 SyllabusDokument8 SeitenCoward Fall 2020 21434A2 Syllabusgabriella IrbyNoch keine Bewertungen

- 7th Grade Honors Course Syllabus 2016Dokument3 Seiten7th Grade Honors Course Syllabus 2016api-327918350Noch keine Bewertungen

- ENGR 230 Engineering Drawing Syllabus Fall 2016Dokument5 SeitenENGR 230 Engineering Drawing Syllabus Fall 2016احمدحاتمNoch keine Bewertungen

- ELC3421 Student Info Sheet (2016-17 Sem 1)Dokument6 SeitenELC3421 Student Info Sheet (2016-17 Sem 1)wingboscoNoch keine Bewertungen

- Introduction To Literature SyllabusDokument2 SeitenIntroduction To Literature SyllabusAomme JogthongNoch keine Bewertungen

- 105syl Y3Dokument7 Seiten105syl Y3api-196355369Noch keine Bewertungen

- Lesson 1-Course Orientation 1Dokument5 SeitenLesson 1-Course Orientation 1FMMNoch keine Bewertungen

- MGT 45: Managerial Accounting: TA: Laura LeeDokument4 SeitenMGT 45: Managerial Accounting: TA: Laura LeecalvinNoch keine Bewertungen

- Financial Accounting - B30000 Fall 2010: Course DescriptionDokument6 SeitenFinancial Accounting - B30000 Fall 2010: Course Descriptionmattb1409Noch keine Bewertungen

- LSPR Syllabus EAdvCommTheory p08Dokument14 SeitenLSPR Syllabus EAdvCommTheory p08elearninglspr100% (1)

- 3130 KwakDokument9 Seiten3130 KwakKelvin LeeNoch keine Bewertungen

- MGN-1 03DDokument3 SeitenMGN-1 03DJoseph Lee StanfieldNoch keine Bewertungen

- ECON 2113 SyllabusDokument6 SeitenECON 2113 SyllabusJason KristiantoNoch keine Bewertungen

- Microbiology Quiz: (A Handbook for Competitive Exam)Von EverandMicrobiology Quiz: (A Handbook for Competitive Exam)Bewertung: 3.5 von 5 Sternen3.5/5 (2)

- Exit Interview Questionnaire 3Dokument1 SeiteExit Interview Questionnaire 3Dwaipayan GuptaNoch keine Bewertungen

- Job Analysis and DesignDokument47 SeitenJob Analysis and DesignDwaipayan GuptaNoch keine Bewertungen

- Job Evaluation MethodsDokument45 SeitenJob Evaluation MethodsDwaipayan GuptaNoch keine Bewertungen

- Job Analysis FinalDokument38 SeitenJob Analysis FinaltanveerameenNoch keine Bewertungen

- Exit Interview Updated FormDokument2 SeitenExit Interview Updated FormDwaipayan GuptaNoch keine Bewertungen

- Exit Interview QuestionnaireDokument4 SeitenExit Interview QuestionnaireDwaipayan GuptaNoch keine Bewertungen

- Barin Bhoumiker Byaram by Satyajit RoyDokument17 SeitenBarin Bhoumiker Byaram by Satyajit RoyDwaipayan GuptaNoch keine Bewertungen

- Conjuring Movie ReviewDokument10 SeitenConjuring Movie ReviewDwaipayan GuptaNoch keine Bewertungen

- Exit Interview FormDokument2 SeitenExit Interview FormDwaipayan GuptaNoch keine Bewertungen

- Designing Pay Levels Mix and Pay StructuresDokument0 SeitenDesigning Pay Levels Mix and Pay StructuresMootoosamy Diany100% (1)

- Financial Statements SampleDokument7 SeitenFinancial Statements SamplesaintsandbarrelsNoch keine Bewertungen

- Food Price HikeDokument4 SeitenFood Price HikeDwaipayan GuptaNoch keine Bewertungen

- ClassDokument3 SeitenClassDwaipayan GuptaNoch keine Bewertungen

- Practical CreativityDokument2 SeitenPractical CreativityDwaipayan GuptaNoch keine Bewertungen

- Issue OF Food Inflation in India and The Effect of Food Security Bill On It: An AnalysisDokument12 SeitenIssue OF Food Inflation in India and The Effect of Food Security Bill On It: An AnalysisDwaipayan GuptaNoch keine Bewertungen

- Calculation For Urgent OrderDokument1 SeiteCalculation For Urgent OrderDwaipayan GuptaNoch keine Bewertungen

- Defining Comp en Sable FactorsDokument6 SeitenDefining Comp en Sable FactorsDwaipayan GuptaNoch keine Bewertungen

- What Is The Qualifying Exam For Admission Into Doms?Dokument5 SeitenWhat Is The Qualifying Exam For Admission Into Doms?viccky_116277Noch keine Bewertungen

- GD TopicsDokument2 SeitenGD TopicsDwaipayan GuptaNoch keine Bewertungen

- Applications of Wireless Sensor Networks: An Up-to-Date SurveyDokument24 SeitenApplications of Wireless Sensor Networks: An Up-to-Date SurveyFranco Di NataleNoch keine Bewertungen

- Cap1 - Engineering in TimeDokument12 SeitenCap1 - Engineering in TimeHair Lopez100% (1)

- Sprinkler Sizing en v1Dokument12 SeitenSprinkler Sizing en v1CristianDumitru0% (1)

- CSWIP-WP-19-08 Review of Welding Procedures 2nd Edition February 2017Dokument6 SeitenCSWIP-WP-19-08 Review of Welding Procedures 2nd Edition February 2017oberai100% (1)

- There Will Come Soft RainsDokument8 SeitenThere Will Come Soft RainsEng ProfNoch keine Bewertungen

- WWW Ranker Com List Best-Isekai-Manga-Recommendations Ranker-AnimeDokument8 SeitenWWW Ranker Com List Best-Isekai-Manga-Recommendations Ranker-AnimeDestiny EasonNoch keine Bewertungen

- Puma PypDokument20 SeitenPuma PypPrashanshaBahetiNoch keine Bewertungen

- Importance of Porosity - Permeability Relationship in Sandstone Petrophysical PropertiesDokument61 SeitenImportance of Porosity - Permeability Relationship in Sandstone Petrophysical PropertiesjrtnNoch keine Bewertungen

- Governance Operating Model: Structure Oversight Responsibilities Talent and Culture Infrastructu REDokument6 SeitenGovernance Operating Model: Structure Oversight Responsibilities Talent and Culture Infrastructu REBob SolísNoch keine Bewertungen

- English Test For Grade 7 (Term 2)Dokument6 SeitenEnglish Test For Grade 7 (Term 2)UyenPhuonggNoch keine Bewertungen

- 7 - Monte-Carlo-Simulation With XL STAT - English GuidelineDokument8 Seiten7 - Monte-Carlo-Simulation With XL STAT - English GuidelineGauravShelkeNoch keine Bewertungen

- "Organized Crime" and "Organized Crime": Indeterminate Problems of Definition. Hagan Frank E.Dokument12 Seiten"Organized Crime" and "Organized Crime": Indeterminate Problems of Definition. Hagan Frank E.Gaston AvilaNoch keine Bewertungen

- My BaboogDokument1 SeiteMy BaboogMaral Habeshian VieiraNoch keine Bewertungen

- Maximum and Minimum PDFDokument3 SeitenMaximum and Minimum PDFChai Usajai UsajaiNoch keine Bewertungen

- Engineering Ethics in Practice ShorterDokument79 SeitenEngineering Ethics in Practice ShorterPrashanta NaikNoch keine Bewertungen

- KK AggarwalDokument412 SeitenKK AggarwalEnrico Miguel AquinoNoch keine Bewertungen

- BECED S4 Motivational Techniques PDFDokument11 SeitenBECED S4 Motivational Techniques PDFAmeil OrindayNoch keine Bewertungen

- Installation Instructions INI Luma Gen2Dokument21 SeitenInstallation Instructions INI Luma Gen2John Kim CarandangNoch keine Bewertungen

- Banking Ombudsman 58Dokument4 SeitenBanking Ombudsman 58Sahil GauravNoch keine Bewertungen

- Raiders of SuluDokument1 SeiteRaiders of SuluBlexx LagrimasNoch keine Bewertungen

- Week 3 Lab Arado, Patrick James M.Dokument2 SeitenWeek 3 Lab Arado, Patrick James M.Jeffry AradoNoch keine Bewertungen

- Analisis Kebutuhan Bahan Ajar Berbasis EDokument9 SeitenAnalisis Kebutuhan Bahan Ajar Berbasis ENur Hanisah AiniNoch keine Bewertungen

- Job Satisfaction of Library Professionals in Maharashtra State, India Vs ASHA Job Satisfaction Scale: An Evaluative Study Dr. Suresh JangeDokument16 SeitenJob Satisfaction of Library Professionals in Maharashtra State, India Vs ASHA Job Satisfaction Scale: An Evaluative Study Dr. Suresh JangeNaveen KumarNoch keine Bewertungen

- Building Material Supplier in GurgaonDokument12 SeitenBuilding Material Supplier in GurgaonRodidustNoch keine Bewertungen

- LC For Akij Biax Films Limited: CO2012102 0 December 22, 2020Dokument2 SeitenLC For Akij Biax Films Limited: CO2012102 0 December 22, 2020Mahadi Hassan ShemulNoch keine Bewertungen

- KRAS QC12K-4X2500 Hydraulic Shearing Machine With E21S ControllerDokument3 SeitenKRAS QC12K-4X2500 Hydraulic Shearing Machine With E21S ControllerJohan Sneider100% (1)

- 4. Nguyễn Thị Minh Khai, Sóc TrăngDokument15 Seiten4. Nguyễn Thị Minh Khai, Sóc TrăngK60 TRẦN MINH QUANGNoch keine Bewertungen

- Sensitivity of Rapid Diagnostic Test and Microscopy in Malaria Diagnosis in Iva-Valley Suburb, EnuguDokument4 SeitenSensitivity of Rapid Diagnostic Test and Microscopy in Malaria Diagnosis in Iva-Valley Suburb, EnuguSMA N 1 TOROHNoch keine Bewertungen

- Group Case Study Rubric 3Dokument3 SeitenGroup Case Study Rubric 3Saraswathi Asirvatham67% (3)

- Polysep... Sized For Every Application: Psg-7 Psg-15 Psg-30 Psg-60 Psg-90Dokument1 SeitePolysep... Sized For Every Application: Psg-7 Psg-15 Psg-30 Psg-60 Psg-90Carlos JiménezNoch keine Bewertungen