Beruflich Dokumente

Kultur Dokumente

241 1163 1 PB

Hochgeladen von

Deepak SahuOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

241 1163 1 PB

Hochgeladen von

Deepak SahuCopyright:

Verfügbare Formate

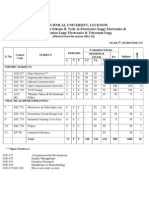

ETASR - Engineering, Technology & Applied Science Research Vol. 3, No.

6, 2013, 549-551

549

www.etasr.com Selvam: A Circuit for the Square Root of the Sum of Two Squared Voltages using an IC LM311

A Circuit for the Square Root of the Sum of Two

Squared Voltages using an IC LM311 Open Collector

Comparator

K. C. Selvam

Department of Electrical Engineering

Indian Institute of Technology, Madras -36, India

kcselvam@ee.iitm.ac.in

Abstract A circuit which accepts two input dc voltages V

1

and

V

2

and provides an output dc voltage V

O

equal to the square root

of the sum of the two squared voltages of V

1

and V

2

, using an

LM311 open collector comparator based single quadrant time

division multiplier is described in this paper.

Keywords- generator; comparator; integrator; square rooter;

adder

I. INTRODUCTION

A circuit for the square root of the sum of two squared

voltages is often needed in instrumentation and control

systems, particularly in phase sensitive detectors [1] which play

an important role in impedance measurements and power

measurements. This circuit is used in the construction of

signal-envelope circuits, diversity combiner circuits, radiometer

circuits and in other applications in which the powers of

separate waveforms have to be added. Stern and Lerner

described one circuit [2] in which they used a piecewise-linear

network employing resistors and diodes. A different approach

employing operational amplifiers, an LM 311 open collector

comparator and switches is described here. The principle of the

Time Division Multiplier [3-5] is used here in a simplified way.

II. CIRCUIT ANALYSIS

The proposed circuit diagram is shown in Figure 1. A

sawtooth wave, marked as Vs in Figure 1, of peak value Vt is

generated by the opamps OA1, OA2 and the switch S1. Let us

assume that at start, the charge and hence voltage at the output

terminal of opamp OA1 is zero. Since the inverting terminal of

the opamp OA1 is at virtual ground, the current through R1,

namely Vt/R1 Amps, would flow through and charge the

capacitor C1. During the capacitor being charged (till the

output of OA1 reaches a voltage level of Vt) the output of

opamp OA2, configured to work as a comparator, will be at the

LOW state and switch S1 is kept open (OFF). As soon as the

output of OA1 crosses the level of Vt, say after a time period T,

the output of comparator OA2 goes HIGH and the switch S1 is

closed (ON). The switch S1 would then short the capacitor C1

and hence Vs drops to zero volts. After a very short delay time

Td, required for the capacitor to discharge to zero volts, the

comparator output returns to LOW and switch S1 is opened,

thus allowing C1 to resume charging. This cycle, therefore,

repeats itself at a period (T+Td). The waveforms at cardinal

points in the circuit are shown in Figure 2.

The output of the integrator OA1 will be

1

( )

1 1 1 1

Vt

Vs t Vtdt t

R C R C

(1)

From the waveforms shown in Figure 2 and the fact that at t=T,

Vs(t) = Vt:

1 1

Vt

Vt T

R C

1 1 T R C (2)

The sawtooth wave Vs is compared with one input voltage

V1 using the LM311 Comparator COMP1. The LM311

comparator has the characteristic that if the ve input is greater

than +ve input voltage, its output goes to LOW (pin no 1 has to

be grounded). When the +ve input voltage is greater than the

ve input voltage, its output goes to the voltage at the other

end of its pull up resistor Rp connected at the output [6]. Hence

the output Vp1 of the comparator is a rectangular pulse

waveform with a maximum value of the input applied voltage

V1 as shown in Figure 2.

The ON time of the pulse waveforms vp1 is given by:

1

1

V

Ton T

Vt

(3)

The average value of Vp1 will be

1

1 Vw V dt

T

2

1 1

1

V V

Ton

T Vt

Similarly,

2

2 V

Vx

Vt

ETASR - Engineering, Technology & Applied Science Research Vol. 3, No. 6, 2013, 549-551

550

www.etasr.com Selvam: A Circuit for the Square Root of the Sum of Two Squared Voltages using an IC LM311

.

2

Vo

Vy

Vt

Vz Vx Vw

2 2

1 2 V V

Vz

Vt

If R3=R4=R and R5>>R and considering KCL for node J

in the circuit of Figure 1, we get:

1 2 I I , Vy Vz ,

2 2 2

1 2 Vo V V

Vt Vt

,

2 2 2

1 2 Vo V V

2 2

1 2 Vo V V (4)

Thus the output voltage is the square root of sum of two

(V1 and V2) squared voltages.

III. EXPERIMENTAL RESULTS

The circuit shown in Figure 1 was tested in our laboratory.

LM 324 IC was used for OA1-OA8. CD 4053 IC is used for

the switch S1. LM 311 ICs were used for COMP1-COMP3.

Rp=1.2 k, R1=1.2 M and C1 = 10 nF. A voltage of 7.5 V

was chosen for the power supply. The test results are shown in

Figures 3 and 4.

The accuracy of the circuit strongly depends upon the

sharpness and linearity of the sawtooth waveform. The offset

voltage of all the opamps used may cause a little error in the

output and hence it must be adjusted to zero. The small

variations in the voltage Vt will cause an error at the output,

hence a stable precision reference voltage must be used as Vt.

However, small variations in the power supply will not affect

the performance of the circuit at all.

-Vt

Vt

V1

V2

GND

GND

Vo

-Vz

GND

GND

GND

GND

C

R

C1

S1

R1

-

+

COMP2

-

+

COMP3

-

+

OA4

Vp2

Rp

-

+

OA6

-

+

OA3

Vp1

-

+

COMP1

Vs

R2 Vx

C

R

-

+

OA7

Vy R

C R3

I1

-

+

OA5

R2

R4

I2

J

Rp

-

+

OA8

-

+

OA2

Vp

R2 Vw

Rp

-

+

OA1

R5

Fig. 1. Circuit diagram for the square root of the sum of two squared voltages

ETASR - Engineering, Technology & Applied Science Research Vol. 3, No. 6, 2013, 549-551

551

www.etasr.com Selvam: A Circuit for the Square Root of the Sum of Two Squared Voltages using an IC LM311

TT

Td

T on1

T on2 T on2

Td

T on1

V1

Vt

Vs

Vp

Vp1

V1

V2

+Vcc

-Vcc

V2

Vp2

Output of

Integrator

OA1

Output of

Comparator

OA2

Output of

Comparator

COMP1

Output of

Comparator

COMP2

Fig. 2. Associated Waveforms of Figure 1

Fig. 3. Test results for Vt = 4V, V1 = 2.5V

Fig. 4. Test results for Vt = 4V, V2 = 2.5V

ACKNOWLEDGEMENT

The author is highly indebted to Prof. S. Srinivasan, Prof. Dr. Enakshi

Bhattacharya, Prof. Dr. V. Jagadeesh Kumar, Prof. Dr. Sridharan and Dr.

Bharath Bhikkaji, Department of Electrical Engineering, Indian Institute of

Technology, Madras, for their constant encouragement throughout the work.

He also thanks Mrs. Latha Selvam for circuit drawing and discussions.

REFERENCES

[1] H. O. Modi, V. J. Kumar, P. Sankaran, Feedback compensated

synchronous and multiplier type phase sensitive detectors, IEEE

Transactions on Instrumentation and Measurement, Vol. 40, No. 3, pp.

646-649, 1991

[2] T. E. Stern, R. M. Lerner,A circuit for the square root of the sum of the

squares, Proceedings of the IEEE, Vol. 51, No. 4, pp. 593-596, 1963

[3] M. Tomata, Y. Sugiyamma, K. Yamaguchi, An electronic multiplier for

accurate power measurements, IEEE Transactions on Instrumentation

and Measurement, Vol. 17, No. 4, pp. 245-251, 1968

[4] T. S. Rathore, B. B. Bhattacharyya, A new type of analog multiplier,

IEEE Trans on Industrial Electronics, Vol IE-31, No. 3, pp. 268-271,

1984.

[5] J. Greg Johnson, Analysis of the modified Tomata-Sugiyama-

Yamaguchi Multiplier, IEEE Transactions on Instrumentation and

Measurement, Vol. 33, No. 1, pp. 11-16, 1984

[6] National Semiconductor Corporation, CMOS Data Book, 1982

AUTHORS PROFILE

K.C. Selvam was born on 2

nd

April 1968 in

Krishnagiri District of Tamil Nadu State,

India. He graduated from the Institution of

Electronics and Telecommunication

Engineers, (IETE) New Delhi, India in

1994. He has published more than 15

research papers in various national and

international journals. He got the best paper

award by IETE in 1996. At present he is

working as Technical Staff in the

Department of Electrical Engineering,

Indian Institute of Technology, Madras,

India. His research interests focus on

measurements and instrumentation systems.

Das könnte Ihnen auch gefallen

- Electronic Devices (Ec-301)Dokument3 SeitenElectronic Devices (Ec-301)Deepak SahuNoch keine Bewertungen

- Communication Switching Techniques: Unit 4 Traffic EngineeringDokument30 SeitenCommunication Switching Techniques: Unit 4 Traffic EngineeringAlok RoyNoch keine Bewertungen

- EDC PUT Paper 2017-18Dokument3 SeitenEDC PUT Paper 2017-18Deepak SahuNoch keine Bewertungen

- Electronic Measurement & Instrumentation - AssignmentDokument3 SeitenElectronic Measurement & Instrumentation - AssignmentRohan Sharma100% (1)

- EDC - Old Question Papers For Unit I & IIDokument12 SeitenEDC - Old Question Papers For Unit I & IIDeepak SahuNoch keine Bewertungen

- EC 4 Year FinalDokument22 SeitenEC 4 Year FinalAmitNoch keine Bewertungen

- EC-401 Theory Exam QuestionsDokument19 SeitenEC-401 Theory Exam QuestionsDeepak SahuNoch keine Bewertungen

- EDC - Old Question Papers For Unit I & IIDokument12 SeitenEDC - Old Question Papers For Unit I & IIDeepak SahuNoch keine Bewertungen

- 2017 2 COLOSSAL Series CatalogueDokument20 Seiten2017 2 COLOSSAL Series CatalogueDeepak SahuNoch keine Bewertungen

- Gòej Øeosme Efme#Ekeâ Hee$Elee Hejer#Ee, (Keâ#Ee Lekeâ) Jùeekùeelcekeâ Nue Øemve-He$EDokument33 SeitenGòej Øeosme Efme#Ekeâ Hee$Elee Hejer#Ee, (Keâ#Ee Lekeâ) Jùeekùeelcekeâ Nue Øemve-He$EDeepak SahuNoch keine Bewertungen

- Mpeg4 Structured AudioDokument4 SeitenMpeg4 Structured AudioDeepak SahuNoch keine Bewertungen

- Programming in ANSI C - Balagurusamy (Solutions With Flowchart & Programs)Dokument227 SeitenProgramming in ANSI C - Balagurusamy (Solutions With Flowchart & Programs)michelrojar74% (39)

- Programming in ANSI C - Balagurusamy (Solutions With Flowchart & Programs)Dokument227 SeitenProgramming in ANSI C - Balagurusamy (Solutions With Flowchart & Programs)michelrojar74% (39)

- Programming in ANSI C - Balagurusamy (Solutions With Flowchart & Programs)Dokument227 SeitenProgramming in ANSI C - Balagurusamy (Solutions With Flowchart & Programs)michelrojar74% (39)

- Programming in ANSI C - Balagurusamy (Solutions With Flowchart & Programs)Dokument227 SeitenProgramming in ANSI C - Balagurusamy (Solutions With Flowchart & Programs)michelrojar74% (39)

- Programming in ANSI C - Balagurusamy (Solutions With Flowchart & Programs)Dokument227 SeitenProgramming in ANSI C - Balagurusamy (Solutions With Flowchart & Programs)michelrojar74% (39)

- Programming in ANSI C - Balagurusamy (Solutions With Flowchart & Programs)Dokument227 SeitenProgramming in ANSI C - Balagurusamy (Solutions With Flowchart & Programs)michelrojar74% (39)

- Electronics CommunicationDokument32 SeitenElectronics CommunicationSUPER_HERRERANoch keine Bewertungen

- BSNL Prepaid Mobile Special Tariff Vouchers (STVDokument1 SeiteBSNL Prepaid Mobile Special Tariff Vouchers (STVYunus KhanNoch keine Bewertungen

- EC 3 Year Time-Table - 2014-15 - IDokument1 SeiteEC 3 Year Time-Table - 2014-15 - IDeepak SahuNoch keine Bewertungen

- New Syllabus Iind Year EceDokument14 SeitenNew Syllabus Iind Year EceAnonymous eWMnRr70qNoch keine Bewertungen

- Circular ConvolutionDokument20 SeitenCircular ConvolutionDeepak SahuNoch keine Bewertungen

- 4th YrDokument20 Seiten4th YrKaran SharmaNoch keine Bewertungen

- EC 2 Year Time-Table - IDokument1 SeiteEC 2 Year Time-Table - IDeepak SahuNoch keine Bewertungen

- CSIR-UGC NET Physical Sciences Exam GuideDokument3 SeitenCSIR-UGC NET Physical Sciences Exam GuideMaruthiNoch keine Bewertungen

- EC 4th Year Time Table 2014-15 Devprayag Institute AllahabadDokument1 SeiteEC 4th Year Time Table 2014-15 Devprayag Institute AllahabadDeepak SahuNoch keine Bewertungen

- GATE SyllabusDokument2 SeitenGATE SyllabusVenkatesh KaulgudNoch keine Bewertungen

- Approved Annual Programme 2015Dokument1 SeiteApproved Annual Programme 2015Sharath HegdeNoch keine Bewertungen

- Csir-Ugc JRF - Net Exam2Dokument3 SeitenCsir-Ugc JRF - Net Exam2Deepak SahuNoch keine Bewertungen

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (894)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (73)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- b60Dokument34 Seitenb60srmanoharaNoch keine Bewertungen

- Antenna Used in IndiaDokument5 SeitenAntenna Used in IndiaShiv ChaudharyNoch keine Bewertungen

- TIKLOSDokument4 SeitenTIKLOSJanna Del MundoNoch keine Bewertungen

- Shostakovich Waltz No. 2 From Suite for Variety OrchestraDokument4 SeitenShostakovich Waltz No. 2 From Suite for Variety OrchestraAnonymous vrUXGCQnECNoch keine Bewertungen

- De Thi Tieng Anh Lop 6 Hoc Ki 1 Global Success So 2Dokument4 SeitenDe Thi Tieng Anh Lop 6 Hoc Ki 1 Global Success So 2Thăng VĩnhNoch keine Bewertungen

- Jazz Manouche Chords PDFDokument1 SeiteJazz Manouche Chords PDFnilNoch keine Bewertungen

- Bcrich Catalog 2012Dokument26 SeitenBcrich Catalog 2012escuipoNoch keine Bewertungen

- Survey Kebutuhan PLC SMART SDH (1-65)Dokument77 SeitenSurvey Kebutuhan PLC SMART SDH (1-65)ichbineinmusikantNoch keine Bewertungen

- Gavrilin - MarshDokument10 SeitenGavrilin - Marshpasundik100% (1)

- Multi Pulse Width Modulation Techniques (MPWM) : Experiment AimDokument4 SeitenMulti Pulse Width Modulation Techniques (MPWM) : Experiment AimAjay Ullal0% (1)

- Attenuator Convection Cooled DSDokument4 SeitenAttenuator Convection Cooled DShennrynsNoch keine Bewertungen

- Secure ATM Door Locking System Using RFIDDokument8 SeitenSecure ATM Door Locking System Using RFIDImranNoch keine Bewertungen

- 65° Panel Antenna: General SpecificationsDokument2 Seiten65° Panel Antenna: General SpecificationsMiroslav ZeljkovicNoch keine Bewertungen

- Billie EilishDokument21 SeitenBillie EilishchachasacNoch keine Bewertungen

- Presentation: Like/love + Noun or - Ing FormDokument2 SeitenPresentation: Like/love + Noun or - Ing FormKaren GimezNoch keine Bewertungen

- Interchange 2 CompressedDokument153 SeitenInterchange 2 CompressedVANYA GUADALUPE NIETO BLAZNoch keine Bewertungen

- Walk, Don't Run: A Rockin' and Rollin' MemoirDokument47 SeitenWalk, Don't Run: A Rockin' and Rollin' MemoirKallisti Publishing Inc - "The Books You Need to Succeed"Noch keine Bewertungen

- Mensural NotationDokument12 SeitenMensural NotationBrandon McguireNoch keine Bewertungen

- NDB System Setup GuideDokument48 SeitenNDB System Setup GuideFazz Yaakub100% (2)

- Savatage: Jezebel S Anaheim, California 26/08/90 Set ListDokument1 SeiteSavatage: Jezebel S Anaheim, California 26/08/90 Set ListSergio Arroyo CarrascoNoch keine Bewertungen

- Tanaka 2Dokument15 SeitenTanaka 2Firani Reza ByaNoch keine Bewertungen

- What Is A Time Signature?: About Those NumbersDokument10 SeitenWhat Is A Time Signature?: About Those NumbersNaluminoNoch keine Bewertungen

- Electrical Design Criteria - Rev.2Dokument13 SeitenElectrical Design Criteria - Rev.2civilISMAEELNoch keine Bewertungen

- Chapter 3 - The Physical Layer-Data Rate LimitsDokument32 SeitenChapter 3 - The Physical Layer-Data Rate Limitsrrs_198867% (3)

- Why Study MusicDokument11 SeitenWhy Study MusicVincent GalleyNoch keine Bewertungen

- Impressionist Music Era (1875-1925Dokument17 SeitenImpressionist Music Era (1875-1925DolfiParthaHutagalungNoch keine Bewertungen

- Em C Am B em C Am: You'Re So Gay-Katy PerryDokument12 SeitenEm C Am B em C Am: You'Re So Gay-Katy PerryBintang Estu AdiNoch keine Bewertungen

- 4.sat SubsystemsDokument66 Seiten4.sat Subsystemsrama krishnaNoch keine Bewertungen

- Datashee YS-1020Dokument3 SeitenDatashee YS-1020inyonggantengNoch keine Bewertungen

- Sailors Hornpipe Score and Parts PDFDokument12 SeitenSailors Hornpipe Score and Parts PDFhadiNoch keine Bewertungen