Beruflich Dokumente

Kultur Dokumente

Power Electronics Unit I

Hochgeladen von

Satya Sudhakar RasamsettiOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Power Electronics Unit I

Hochgeladen von

Satya Sudhakar RasamsettiCopyright:

Verfügbare Formate

POWER ELECTRONICS

UNIT I

Power electronics combine power, electronics and control. Power electronics

may be defined as the applications of solid state electronics for the control and

conversion of power. Power semiconductor devices can be operated as switches by

applying control signals to the gate terminal of thyristors and to the base of bipolar

transistors. The required output is obtained by varying the conduction time of these

switching devices.

CHARACTERISTICS AND MODELING POWER SEMICONDUCTOR

DIODES

Power semiconductor diodes play a significant role in power electronics

circuits.

A diode acts as a switch to perform various functions, such as switches in

rectifiers, free wheeling in switching regulators, charge reversal of capacitor

and energy transfer between components, voltage isolation, energy feed back

from the load to the power source, and trapped energy recovery.

Power diodes are similar to PN junction signal diodes but it has large power,

voltage and current handling capabilities. The frequency response or

switching speed is low compared to signal diodes.

A power diode is a two terminal PN junction device and a PN junction is

normally formed by alloying, diffusion and epitaxial growth. The modern

control techniques in diffusion and epitaxial processes permit the desired

device characteristics.

When the anode potential is positive with respect to the cathode, the diode is

said to be forward biased and the diode conducts. A conducting diode has a

relatively small forward voltage drop across it; and the magnitude of this drop

would depend on the manufacturing process and junction temperature.

When the cathode potential is positive with respect to the anode, the diode is

said to be reverse biased. Under reverse bias conditions, a small reverse

current also known as leakage current in the range of micro or milliampere

flows and this leakage current increase slowly in magnitude with the reverse

voltage until the avalanche or zener voltage are reached.

The fig shows the v-i characteristics of a diode. It can be expressed by an

equation known as schockly diode equation, and is given by

I

D

=I

S

(e

VD/nVT

-1)

Where I

D

= current through the diode,

V

D

=diode voltage with anode positive with respective to cathode,V

Is=leakage or reverse saturation current, typically in the range 10-6 to 10-15

A

N=empirical constant known as emission coefficicnt or ideality factor, whose

value varies from 1 to 2.

The emission coefficient n depends on the material and the physical

construction of the diode. For germanium diodes, n is considered to be 1.

For silicon diodes the predicted value of n is 2, but for most practical silicon

diodes, the value of n falls in the range 1.1 to 1.8.

V

T

in eqn(1) is a constant called thermal voltage and it is given by V

T

=k

T

/q

Where q= electron charge 1.602210

-19

T= absolute temperature in Kelvin (K=273+

0

C)

K= Boltzmann s constant: 1.380610

-23

J/K

At a specified temperature, the leakage current Is is a constant for a given diode .the

diode characteristics can be divided in to three regions.

DIODE REVERSE RECOVERY CHARACTERISTICS

After the forward diode current decays to zero, the diode continues to conduct

in the reverse direction because of the presence of stored charges in the two

layers.

The reverse current flows for a time called reverse recovery time t

rr

. The

diode regains its blocking capability until reverse recovery current decays to

zero.

The reverse recovery time t

rr

is defined as the time between the instant

forward diode current becomes zero and the instant reverse recovery current

decays to 25% of its reverse peak value I

RM

as shown in fig

The reverse recovery time is composed of two segments of time t

a

and t

b

i.e.

t

rr

= t

a

+t

b

. Time t

a

is the time between zero crossing of forward current and

peak reverse current I

RM

.

During the time t

a

, charge stored in depletion region is removed. Time t

b

is

measured from the instant of I

RM

to the instant where 0.25 I

RM

is reached.

During t

b

, charge from the two semiconductor layers is removed. The shaded

area represents the stored charge, or reverse recovery charge, Q

R

which must

be removed during the reverse recovery time t

rr

.

The ratio t

b

/t

a

is called the softness factor or S- factor. This factor is a

measure of the voltage transients occur during the time diode recovers. Its

usual value is unity and this indicates low oscillatory reverse recovery

process. In case s factor is small, diode has large oscillatory over voltages.

A diode with s factor equal to one is called soft recovery diode and a diode

with s factor less than one is called snappy recovery diode or fast recovery

diode. In fig is shown the waveform of forward voltage drop V

f

across the

diode.

The product of V

f

and if gives the power loss in a diode. Its variation is shown

in fig.2.c. The average value of V

f

I

f

gives the total power loss in a diode. Fig

2.c reveals that major power loss in a diode occurs during the period t

b

It is noticed from fig. that peak inverse current I

RM

can be expressed as

I

RM

= t

a

(di/dt)

Where di/dt is the rate of change of reverse current. The reverse recovery

characteristics of fig 2.a. can be taken to be triangular. Under this assumption,

storage charge Q

R

from fig2.a is given by

Q

R

= I

RM

t

rr

I

RM

=2Q

R

/t

rr

If trr= ta then from eqn

I

RM

= t

rr

di/dt

t

rr

di/dt= 2Q

R

/t

rr

or

t

rr

= [2Q

R

/ (di/dt)]

from eqn with ta=trr we get

I

RR

= t

rr

(di/dt) = [2Q

R

/ (di/dt)]

di/dt

I

RR

=[2Q

R

(di/dt)]

TYPES OF POWER DIODES

Diodes are classified according to their reverse recovery characteristics. The three

types of power diodes are as under:

(i) General purpose diodes

(ii) Fast recovery diodes

(iii) Schottky diodes.

These are now described briefly.

General-purpose Diodes

These diodes have relatively high reverse recovery time, of the order of about

25 is. Their current ratings vary from 1 A to several thousand amperes and

the range of voltage rating is from 50 V to about 5 kV.

Applications of power diodes of this type include battery charging, electric

traction, electroplating. welding and uninterruptible power supplies (UPS).

Fast-recovery Diodes

The diodes with low reverse recovery time, of about 5 jis or less, are

classified as fast-recovery diodes.

These are used in choppers, commutation circuits, switched mode power

supplies, induction heating etc. Their current ratings vary from about 1 A to

several thousand amperes and voltage ratings from 50 V to about 3 kV.

For voltage ratings below about 400 V, the epitaxial process is used for diode

fabrication. These diodes have fast recovery time, as low as 50 ns.

For voltage ratings above 400 V. diffusion technique is used for the

fabrication of diodes. In order to shorten the reverse-recovery time, platinum

or gold doping is carried out. But this doping may increase the forward

voltage drop in a diode.

Schottky Diodes

This class of diodes use metal-to-semiconductor junction for rectification

purposes instead of pn-junction. Schottky diodes are characterized by very

fast recovery time and low forward voltage drop.

Rectified current flow is by majority carriers only and this avoids the turn-off

delay accompanied with minority carrier recombination. Their reverse voltage

ratings are limited to about 100 V and forward current ratings vary from 1 A

to 300 A.

Applications of Schottky diodes include high-frequency instrumentation and

switching power supplies.

POWER MOSFET

A metal oxide semiconductor field effect transistor is a recent device

developed by combining the areas of field effect concept and MOS technology.

A power MOSFET has three terminals called drain, source and gate in place of

the corresponding three terminals collector, emitter and base for BJT. The

circuit symbol for power MOSFET is as shown below.

Here arrow indicates the direction of electron flow. A BJT is a current

controlled device whereas a power MOSFET is a voltage controlled device. As

its operation depends on the flow of minority carriers only, power MOSFET is

a unipolar device.

The control signal, or base current in BJT is much larger than the control

signal required in a MOSFET. This is because of the fact that the gate circuit

impedance in power MOSFET is extremely high.

This large impedance permits the power MOSFET gate to be driven directly

from the microelectronic circuits. BJT suffers from second breakdown voltage

whereas power MOSFET is free from this problem. Power MOSFETs are now

finding increasing applications in low power high frequency converters.

MOSFET OPERATION

An Understanding of the operation of MOSFETs can best be gleaned by the

first considering the lateral N-channel MOSFET shown in Figure 1.

With no electrical bias applied to the gate G, no current can flow in either

direction underneath the gate because there will always be a blocking PN

junction.

When the gate is forward biased with respect to the source S together with an

applied drain-source voltage, as shown in Figure 2, the free hole carriers in

the p-epitaxial layer are repelled away from the gate area creating a channel,

which allows electrons to flow from the source to the drain.

Note that since the holes have been repelled from the gate channel, the

electrons are the majority carriers by default. This mode of operation is

called enhancement but is easier to think of enhancement mode of

operation as the device being normally off, i.e., the switch blocks the

current until it receives a signal to turn on. The opposite is depletion mode,

which is normally on device.

D

G

S

The advantages of the lateral MOSFET are:

1. Low gate signal power requirement. No gate current can flow into the gate

after the small gate oxide capacitance has been charged.

2. Fast switching speeds because electrons can start to flow from drain to

source as soon as the channel opens. The channel depth is proportional to the gate

voltage and pinches closed as soon as the gate voltage is removed, so there is no

storage time effect as occurs in transistors.

The major disadvantages are:

1. High resistance channels. In normal operation, the source is electrically

connected to the substrate. With no gate bias, the depletion region extends out from

the N+ drain in a pseudo-hemispherical shape. The channel length L cannot be made

shorter than the minimum depletion width required to support the rated voltage of

the device.

2. Channel resistance may be decreased by creating wider channels but this is

costly since it uses up valuable silicon real estate. It also slows down the switching

speed of the device by increasing its gate capacitance.

CONTROLLING THE MOSFET

A major advantage of the Power MOSFET is its very fast switching speeds.

The drain current is strictly proportional to gate voltage so that the

theoretically perfect device could switch in 50ps - 200ps, the time it takes the

carriers to flow from source to drain.

Since the MOSFET is a majority carrier device, a second reason why it can

outperform the junction transistor is that its turn-off is not delayed by

minority carrier storage time in the base. A MOSFET begins to turn off as soon

as its gate voltage drops down to its threshold voltage.

SWITCHING BEHAVIOR

Figure 6 illustrates a simplified model for the parasitic capacitances of a

Power MOSFET and switching voltage waveforms with a resistive load. There are

several different phenomena occurring during turn-on. Referring to the same figure:

Time interval t1<t<t2:

The initial turn-on delay time t

d(ON)

is due to the length of time it takes V

GS

to

rise exponentially to the threshold voltage V

GS(TH)

. From Figure 6, the time constant

can be seen to be R

S

xC

GS

.

Typical turn-on delay approximation is:

t

d(ON)=

R

S

xC

GS

xln(1- (V

GS(TH)

)/V)

Note that since the signal source impedance appears in the td equation, it is

very important to pay attention to the test conditions used in measuring switching

times.

Time interval t

2

<t<t

3

:

Since V

GS

has now achieved the threshold value, the MOSFET begins to draw

increasing load current and V

DS

decreases. C

DG

must not only discharge but its

capacitance value also increases since it is inversely proportional to V

DS

, namely:

C

DG

= C

DG

(0)/V

DG

Unless the gate driver can quickly supply the current required to discharge C

DG

,

voltage fall will be slowed with increases in turn-on time.

Time interval t

3

<t<t

4

:

The MOSFET is now on so the gate voltage can rise to the overdrive level.

Turn-off interval t

4

<t<t

6

:

Turn-off occurs in reverse order. VGS must drop back close to the threshold value

before RDS(on) will start to increase. As VDS starts to rise, the Miller effect due to

CDG re-occurs and impedes the rise of VDS as CDG recharges to VCC. Specific gate

drive circuits for different applications are discussed and illustrated later in this

paper.

BIDIRECTIONAL TRIODE THYRISTOR

Two thyristors may be connected in inverse parallel, but at moderate power

levels the two antiparallel thyristors can be integrated into a single device

structure, as shown.

This device commonly known as Triac (triode a.c. switch) is represented by

the circuit symbol shown.

Triac is the word derived by combining the capital letters from the words

TRIode & a.c. As the Triac can conduct in both the directions, the terms

anode & cathode are not applicable to Triac.

Its three terminals are usually designated as main terminals, MT

1,

MT2 & gate

G, as in a thyristor.

The terminals MT

1

is the reference point for measurement of voltages &

currents at the gate terminal & at the terminal MT

2.

The gate is near to

terminal MT

1.

The V-I characteristics of a Triac is shown. This characteristic of the Triac are

based on the terminal MT

1

as the reference point.

The first quadrant is the region wherein MT

2

is positive with respect to MT

1

&

vice-versa for the third quadrant.

The peak voltage applied across the device in either direction must be less

than the break over voltage in order to retain control of the gate.

A gate current of specified amplitude of either polarity will trigger the Triac

into conduction in either quadrant, assuming that the device is in a blocking

condition initially before the gate signal is applied.

The characteristics of a Triac are similar to those of SCR, both in blocking &

conducting states, expect for the fact that SCR conducts only in the forward

direction, whereas the Triac conducts I both directions.

Depending upon the polarity of a gate pulse & biasing conditions, the main

four-layer structure that turns on by a regenerative process could be one of

P

1

N

1

P

2

N

2,

P

1

N

1

P

2

N

3,

or P

2

N

1

P

1

N

4,

TRIGGERING MODES OF TRIAC

Triggering can be obtained from d.c., rectified a.c., or pulse sources such as

unijunction transistors & switching diodes such as the Diac, silicon bilateral switch

(SBS) & asymmetrical trigger switch.

1. MT

2

positive, positive gate current (MODE 1)

When the gate current is positive with respect to MT

1

, gate current flows

normally from the gate lead to the terminal MT

1

through the P

2

N

2

junction as

shown. The device turns on in the conventional manner as in the case of an SCR.

However, in the case of a Triac, the gate current requirement is higher for turn on at

a particular voltage. Because of ohmic contacts of gate & MT

1

terminals on the P

2

-

layer, some more gate current flows from the gate lead G to the main terminal MT

1

through the semiconductor P

2

layer without passing through the P

2

N

2

junction. The

main structure which ultimately turns on through regenerative action is P

1

N

1

P

2

N

2.

The P

2

layer is flooded with electrons when the gate current flows across the P

2

N

2

junction. These electrons diffuse to the edge of the junction J

2

, are collected by N

1

layer. Therefore, the electrons build a space charge in the N

1

region & more holes

from P

1

diffuse into N

1

to neutralize the negative space charge. These holes arrive at

the junction J

2

. They produce a positive space charge in the P

2

region which results

in more electrons being injected from N

2

into P

2

. This results in positive regeneration

& ultimately the structure P

1

N

1

P

2

N

2

conducts the external current.

2. MT

2

positive, negative gate current (MODE 2)

A cross sectional view of the structure is shown. When the terminal MT

2

is

positive & gate terminal is negative with respect to terminal MT

1

, gate current flows

through P

2

-N

3

junction & this gate current I

G

forward biases the gate current P

2

-N

3

of

the auxiliary P

1

N

1

P

2

N

3

structure. As a result, Triac starts conducting through P

1

N

1

P

2

N

3

layers initially. With the conduction of P

1

N

1

P

2

N

3

, the voltage drop across it falls

but potential of layer between P

2

N

3

rises towards the anode potential of MT

2.

As the

right hand portion of P

2

is clamped at the cathode potential of MT

1,

a potential

gradient exists across layer P

2

from, its left hand region begin at higher potential

than its right hand region. A current is thus established in layer P

2

from left to right

which forward biased P

2

N

2

junction & finally the main structure P

1

N

1

P

2

N

2

, may be

considered as a pilot SCR, while the structure OP

1

N

1

P

2

N

2

may be regarded as the

main SCR, both begin built in one common structure. The anode current of the pilot

SCR serves as the gate current for the main SCR. As compared with turn on process,

the device with MT

2

positive but gate current negative is less sensitive & therefore

more gate current is required.

3. MT

2

negative, positive gate current (MODE 3)

When terminal MT

2

is negative & terminal MT

1

is positive, the device can be

turned on by applying a positive voltage between the gate & terminal MT

1

. In this

mode, the device operates in the third quadrant when it is triggered into conduction.

The turn on is initiated by remote gate control. The main structure that leads to turn

on is P

2

N

1

P

1

N

4

with N

2

acting as a remote gate as shown. The external gate current

I

G

forward biases P

2

N

2

TRIAC COMMUTATION EXPLAINED

A triac is an AC conduction device and may be thought of as two antiparallel

thyristors monolithically integrated onto the same silicon chip.

In phase-control circuits, the triac often has to be triggered into conduction

part way into each half cycle. This means that at the end of each half cycle,

the on-state current in one direction must drop to zero and not resume in the

other direction until the device is triggered again.

This commutation turn-off capability is at the heart of triac power control

applications. If the triac were truly two separate thyristors this requirement

would not present any problems.

However, the two are on the same piece of silicon. As one thyristor turns off,

there is a possibility that its reverse recovery current (due to unrecombined

charge carriers) may act as gate current triggering the other thyristor as the

voltage rises in the opposite direction.

This is described as a commutation failure and results in the triac continuing

to conduct in the opposite direction instead of blocking.

The probability of any device failing commutation is dependent on the rate of

rise of reverse voltage (dv/dt) and the rate of decrease of conduction current

(dI/dt).

The higher the dI/dt the more unrecombined charge carriers are left at the

instant of turn-off. The higher the dV/dt the more probable it is that some of

these carriers will act as gate current.

Thus the commutation capability of any device is usually specified in terms of

the turn-off dI/dt and the reapplied dV/dt it can withstand, at any particular

junction temperature.

If a triac has to be operated in an inductive load circuit with a combination of

dI/dt and dV/dt that exceeds its specification, an RC snubber network in

parallel with the device is needed to limit the dV/dt.

This is at a penalty of extra circuit complexity and dissipation in the snubber.

Hi-Com triacs are designed to have superior commutation capability, so that

even at a high rate of turn-off (dI/dt) and a high rate of re-applied dV/dt,

they can be used without the aid of a snubber network, thus greatly

simplifying the circuit.

INSULATED GATE BIPOLAR TRANSISTOR (IGBT)

IGBT is a new development in the area of power MOSFET technology. This

device combines into it the advantages of both MOSFET and BJT. So an IGBT

has high input impedance like a MOSFET and low-on-state power loss as in a

BJT.

Further, IGBT is free from second breakdown problem present in BJT. IGBT is

also known as metal- oxide insulated gate transistor (MOSFET), conductively-

modulated field effect transistor (COMFET) or gain modulated FET

(GEMFET).

It was also initially called insulated gate transistor (IGT). Its structure is a

combination of the two devices.

As shown in Fig. 1, the input has a MOS gate structure, and the output is a

wide base PNP transistor.

The base drive current for the PNP transistor is fed through the input channel.

Besides the PNP transistor, there is an NPN transistor, which is designed to be

inactivated by shorting the base and the emitter to the MOSFET source metal.

The 4 layers of PNPN, which comprises the PNP transistor and the NPN

transistor, form a thyristor structure, which causes the possibility of a latch-

up.

Unlike the power MOSFET, it does not have an integral reverse diode that

exists parasitically, and because of this it needs to be connected with the

appropriate fast recovery diode when needed.

Equivalent Circuit for the IGBT

When gate is positive with respect to emitter and with gate emitter voltage

more than the threshold voltage of IGBT, and n- channel is formed in the p

regions as in a power MOSFET, This n- channel short circuit the n- Region

with n+ emitter regions.

An electron movement in the n- channel, in turn, causes substantial hole

injection from p+ substrate layer into the epitaxial n_ layer.

Eventually, a forward current is established as shown in fig. The three layers

p+,n- and n+ layers constitute NPN transistor as shown in fig. Here n- serves

as base for PNP transistor and also as collector for NPN transistor. Further

serves as collector for PNP device and also as base for NPN transistor.

The two PNP and NPN transistors can, therefore, be connected as shown in

fig. to give the equivalent circuit of an IGBT. Fig. is the circuit symbol for

IGBT with gate (G), emitter (E) and collector as its three terminals. Fig.

illustrates the basic structure of an IGBT.

It is constructed virtually in the same manner as a power MOSFET. There is,

however; a major difference in the substrate.

The n+ layer substrate at the drain in a power MOSFET is now substituted in

the IGBT by a p+ layer substrate called collector. Like a power MOSFET, an

IGBT has also thousands of basic structure cells connected appropriately on a

single chip of silicon.

A Cross Section of the IGBT Structure (PT & N-Channel)

PT & NPT

An IGBT is called a PT (punch-through) or asymmetrical when there is an N+

buffer layer between the P+ substrate and N- drift region. Otherwise, it is

called an NPT (non-punch through) IGBT or symmetrical IGBT.

The N+ buffer layer improves turn-off speed by reducing the minority carrier

injection quantity and by raising the recombination rate during the switching

transition.

In addition, latch-up characteristics are also improved by reducing the current

gain of the PNP transistor.

The problem is that the on-state voltage drop increases. However, the

thickness of the N- drift region can be reduced with the same forward voltage

blocking capability because the N+ buffer layer improves the forward voltage

blocking capability.

As a result, on-state voltage drop can be lowered. Hence, the PT-IGBT has

superior trade-off characteristics as compared to the NPT-IGBT in switching

speed and forward voltage drop. Currently, most commercialized IGBTs

(Fairchild IGBTs) are PT-IGBTs.

About static blocking characteristics illustrates that IGBT forward and reverse

blocking capability are approximately equal because both are determined by

the same N- drift layer thickness and resistance.

The reverse-blocking voltage of PT-IGBTs that contain N+ buffer layer

between P+ substrate and N- drift region is lowered to tens of volts due to

the existence of a heavy doping region on both sides of J1.

OPERATION

TURN-ON

When the device is in the forward blocking mode, and if the positive gate bias

(threshold voltage), which is enough to invert the surface of P-base region

under the gate, is applied, then an n-type channel forms and current begins

to flow.

At this time the anode-cathode voltage must be above 0.7V (potential barrier)

so that it can forward bias the P+ substrate / N- drift junction (J1). The

electron current, which flows from the N+ emitter via the channel to the N-

drift region, is the base drive current of the vertical PNP transistor.

It induces the injection of hole current from the P+ region to the N- base

region. The conductivity modulation improves because of this high level

injection of the minority carrier (hole).

This increases the conductivity of the drift region by a factor varying from ten

to hundred. This conductivity modulation enables IGBTs to be used in high

voltage applications by significantly reducing the drift region resistance.

There are two kinds of currents flowing into the emitter electrode. One is the

electron current (MOS current) flowing through the channel, and the other is

the hole current (bipolar current) flowing through the P+ body / N- drift

junction (J2).

Turn-off

The gate must be shorted to the emitter or a negative bias must be applied to

the gate.

When the gate voltage falls below the threshold voltage, the inversion layer

cannot be maintained, and the supply of electrons into the N- drift region is

blocked, at which point, the turn-off process begins.

However, the turn-off cannot be quickly completed due to the high

concentration minority carrier injected into the N- drift region during forward

conduction.

First, the collector current rapidly decreases due to the termination of the

electron current through the channel, and then the collector current gradually

reduces, as the minority carrier density decays due to recombination.

IGBT CHARACTERISTICS

The circuit of Fig. shown the various parameters pertaining to IGBT

characteristics

Static V-I or output characteristics of an IGBT (n- channel type) show the plot

of collector current Ic versus collector-emitter voltage Vc

E

for various value of

gate- emitter voltages.

These characteristics are shown in Fig. In the forward direction, the shape of

the output characteristics is similar to that of BJT. But here the controlling

parameter is gate-emitter voltage V

GE

because IGBT is a voltage-controlled

device.

The transfer characteristics of an IGBT is a plot of collector current Ic versus

gate-emitter voltage V

GE

as shown in Fig. This characteristic is identical to that

of power MOSFET.

When V

GE

is less than the threshold voltage V

GET,

IGBT is in the off-satae.

When the device is off, junction j

2

blocks forward voltage and in case reverse

voltage appears across collector and emitter, junction j

1

blocks it.

SWITCHING CHARACTERISTICS

TURN-ON

When the device is in the forward blocking mode, and if the positive gate bias

(threshold voltage), which is enough to invert the surface of P base region

under the gate, is applied, then an n-type channel forms and the current

begins to flow.

At this time the anode-cathode voltage must be above 0.7V (potential

barrier), so that it can forward bias the P+ substrate / N- drift junction (J1).

The electron current flowing from the N+ emitter to the N- drift region

through the channel is the base drive current of the vertical PNP transistor,

and it induces a minority carrier (hole) injection from the P+ region to the N-

base region.

The current that flows to the emitter electrode are divided into the electron

current (MOS current) flowing through the channel and bipolar current flowing

through the P body / N- drift junction (J2).

When gate bias falls to near the threshold voltage at on-state, the inversion

layer conductivity is reduced, and significant voltage drop that arises from

electron current flow occurs across the region as in a MOSFET.

When the voltage drop is equal to the difference between the gate bias and

threshold voltage (VGE - Vth), then the channel is pinched off. At this point,

the electron current becomes saturated.

Since this limits the base drive current of the PNP transistor, the hole current

flowing through the PNP transistor is also limited. As a result, the device

operates with saturated current at the active region (gate controlled output

current).

TURN-OFF

The gate must be shorted to the emitter or a negative bias must be applied to

the gate.

When the gate voltage falls below the threshold voltage, the inversion layer

cannot be maintained, and the supply of electrons into the N- drift region is

blocked. At this point the turn-off process begins. As illustrated in Fig. 6, the

collector current (ICO) falls to zero in two stages.

As the electron current supplied through the MOSFET channel during the on-

state is stopped, collector current suffers an initial abrupt fall (ICD).

After that, the tail current (ICT) comes from the minority carrier (hole) that

was injected through the N- drift region from the P+ substrate during the on-

state.

The tail current of the IGBT lowers switching characteristics and increases

switching loss. Since N- drift region is the base of the PNP transistor, it cannot

be approached from outside, so it is not possible to control the tail current

from outside.

But it can be controlled with the amount of minority carrier (hole) injected

through the N- drift region and recombination rate when it is off.

In order to reduce the amount of injected minority carrier and increase the

recombination rate when it is off, the concentration and the thickness of the

N+ buffer layer between the P+ substrate and N- drift region must increase,

as well as the dose of electron irradiation (in FSC, electron irradiation is

applied to above 600V class except 400V) that takes place after device

fabrication.

However, improving the switching speed of the IGBT generally accompanies

reduced current handling capability.

As such, the trade-off between switching speed, which is related to switching

loss, and forward voltage drop, which in turn is related to conduction loss, is

important. The asymmetric structure is superior in such trade-offs as

compared to a symmetric structure, and it can be improved by increasing the

doping concentration in the buffer layer.

In terms of power loss, the power MOSFET is better suited for lower blocking

voltage and high operating frequency applications, while the IGBT is better

suited for higher blocking voltage and lower operating frequency.

Collector Current During Turn-off

The turn-on time is defined as the time between the instants of forward

blocking to forward on-state.

Turn-on time is composed of delay time t

dn

and rise time t

r,

i.e. t

on

= t

dn+

t

r.

The

delay time is defined as the time for collector-emitter voltage to fall from Vc

E

to 0.9 Vc

E .

Here Vc

E

is the initial collector-emitter voltage. Time t

dn

may also be defined

as the time for the collector current to rise from its initial leakage current Ic

E

to 0.1 Ic.

Here Ic is the final value of collector current. The rise time t

r

is the time

during which collector-emitter voltage falls from 0.9 Vc

E

to 0.1 Vc

E.

It is also

defined as the time for the collector current to rise from 0.1 Ic to its final

value Ic.

After time t

on,

the collector current is Ic and the collector-emitter voltage falls

to small value called conduction drop = Vc

ES

where subscript S denotes

saturated value.

The turn-off time is somewhat complex. It consists of three intervals: (i)

delay time, t

df (ii)

initial fall time, t

f1

and (iii) final fall time,t

f2

; i.e. t

off

= t

df

+

t

f1

+ t

f2

.

The delay time is the time during which gate voltage falls from V

GE

to

threshold voltage V

GET

. As V

GE

falls to V

GET

during t

df

, the collector current falls

from Ic to 0.9 Ic.

At the end of t

df,

collector-emitter voltage beings to rise. The first fall time t

f1

is defined as the time during which collector current falls from 90 to 20% of

its initial value Ic, or the time during which collector-emitter voltage rises

from Vc

ES

to 0.1 Vc

E.

The final fall time t

f2

is the time during which collector current falls from 20 to

10% of Ic or the time during which collector-emitter voltage rises from Vc

ES

to 0.1 Vc

E

to final value Vc

E

.

THYRISTOR

INTRODUCTION

The thyristor family of semiconductors consists of several very useful devices.

The most widely used of this family are silicon controlled rectifiers (SCRs),

triacs, and diacs.

There are many applications where these devices perform key functions and

are real assets in meeting environmental, speed, and reliability specifications

which their electro-mechanical counterparts cannot fulfill.

Since they are different from their electro-mechanical counterparts in many

ways, there are many characteristics, terms and parameters which must be

understood.

The purpose of this application note is to better acquaint users of SCRs,

triacs, and diacs to the basic fundamentals of these thyristors.

BASIC OPERATION OF AN SCR

The operation of a PNPN device can best be visualized as a specially coupled pair of

transistors as shown in Figure

The connections between the two transistors are such that regenerative

action can occur when a proper gate signal is applied to the base of the NPN

transistor.

Normal leakage current is so low that the combined h

FE

of the specially

coupled two-transistor feedback amplifier is less than unity, thus keeping the

circuit in an off-state condition.

A momentary positive pulse applied to the gate will bias the NPN transistor

into conduction which, in turn, biases the PNP transistor into conduction.

The effective h

FE

momentarily becomes greater than unity so that the

specially coupled transistors saturate. Once saturated, current through the

transistors is enough to keep the combined h

FE

greater than unity.

The circuit will remain on until it is turned off by reducing the anode-to-

cathode current (IT) such that the combined h

FE

is less than unity and

regeneration ceases; this threshold anode current is the holding current of the

SCR.

ELECTRICAL CHARACTERISTIC CURVES OF THYRISTORS

V-I Characteristics of SCR Device

Methods of Switching on Thyristors There are three general ways to switch thyristors

to on-state condition:

Application of Gate Signal

Static dv/dt Turn-On

Voltage Breakover Turn-On

Listed below is a brief description of each method.

Application Of Gate Signal

Must exceed IGT and VGT requirements of thyristor being used. For an SCR

(unilateral device), this signal must be positive with respect to the cathode

polarity.

A triac (bilateral device) can be turned on with gate signal of either polarity;

however, different polarities have different requirements of IGT and VGT

which must be satisfied.

Since a diac does not have a gate, this method of turn-on is not applicable to

diacs; in fact, the single major application of diacs is to switch-on triacs.

Static dv/dt Turn-On

Comes from a fast rising voltage applied across the anode and cathode

terminals of an SCR or the main terminals of a triac.

Due to the nature of thyristor construction, a small junction capacitor is

formed across each PN junction. Figure 14.14 shows how typical internal

capacitors are linked in gated thyristors. When voltage is impressed suddenly

across a PN junction, a charging current will flow which is equal to:

When c(dv/dt) becomes greater or equal to thyristor IGT, the

thyristor switches on.

Normally, this type of turn on does not damage or hurt the device providing

the surge current is limited.

Generally, thyristor application circuits are designed with static dv/dt snubber

networks if fast rising voltages are anticipated.

Voltage Breakover Turn-On

Is the method used to switch on diacs. However, exceeding voltage breakover

of SCRs and triacs is definitely not recommended as a turn-on method.

In the case of SCRs and triacs, the leakage current increases until it exceeds

the gate current required to turn-on these gated thyristors in a small localized

point.

When turn-on occurs by this method, there is localized heating in a small area

which may melt the silicon or damage the device if di/dt of the increasing

current is not sufficiently limited.

Diacs used in typical phase control circuits are basically protected against

excessive current at breakover as long as the firing capacitor is not

excessively large.

When diacs are used in a zener function, current limiting is necessary.

BIPOLAR JUNCTION TRANSISTORS

A bipolar transistor is a three-layer, two junction npn or pnp semiconductor device.

With one p-region sandwiched by two n-regions, Fig. 2.3 (a), npn transistor is

obtained. With two p-regions sandwicbing one n-region, Fig. 2.3 (b), pnp transistor

is obtained.

The term bipolar denotes that the current flow in the device is due to the movement

of both holes and electrons. A BJT has three terminals named collector, emitter and

base.

An emitter is indicated by an arrowhead indicating the direction of emitter current.

No arrow is associated with base or collector.

STEADY-STATE CHARACTERISTICS:

Out of the three possible circuit configurations for a transistor, common-emitter

arrangement is more common in switching applications. So, henceforth, npn

transistors will only be considered.

Input characteristics.

A graph between base current B and base-emitter voltage VBE gives input

characteristics. As the base-emitter junction of a transistor is like a diode, B versus

VBE graph resembles a diode curve. When collector-emitter voltage VCE is more

than VCE base current decreases as shown in Fig.

Output characteristics:

A graph between collector current I and collector-emitter voltage VCE gives

output characteristics of a transistor. For zero base current, i.e. for B = 0, as VCE is

increased, a small leakage (collector) current exists as shown in Fig. 2.4 (c). As the

base current is increased from B = 0 to Bi, B2 etc, collector current also rises as

shown in Fig. 2.4 (c).

Fig. 2.5 (a) shows two of the output characteristic curves, 1 for B = 0 and 2 for B 0.

The initial part of curve 2, characterized by low VCE is called the saturation region. in

this region, the transistor acts like a switch. The fault part of curve 2, indicated by

increasing V

CE

and almost constant I is the active region. In this region, transistor

acts like an amplifier. Almost vertically rising curve is the breakdown region which

must be avoided at all costs.

SAFE OPERATING AREA:

The safe operating area (SOA or SOAR) of a power transistor specifies the

safe operating limits of collector current I versus collector-emitter voltage V

CE

For reliable operation of the transistor, the collector current and voltage must

always lie within this area.

Actually, two types of safe operating areas are specified by the

manufacturers, FBSOA and RBSOA.

The forward-base safe operating area (FBSOA) pertains to the transistor

operation when base-emitter junction is forward biased to turn-on the

transistor.

For a power transistor, Fig. 2.7 shows typical FBSOA for its dc as well as

single-pulse operation. The scale for I and VCE are logarithmic.

Boundary AB is the maximum limit for dc and continuous current for VCE less

than about 80 V. For VCE for more than 80 V, collector current has to be

reduced to boundary BC so as to limit the junction temperature to safe

values.

For still higher VCE, current should further be reduced so as to avoid

secondary breakdown limit. Boundary CD defines this secondary breakdown

limit. Boundary DE gives the maximum voltage capability for this particular

transistor.

For pulsed operation, power transistor can dissipate more peak power so long

as average power loss is within safe limits of junction temperature.

It should be noted that FBSOA curves, as given by the manufacturers, are for

a case temperature of 25C and for dc and single-pulse operation.

In order to take into consideration the actual working temperature and

repetitive nature of the pulses, these curves must be modified with the help

of thermal impedance of the device.

During turn-off, a transistor is subjected to high current and high voltage with

base-emitter junction reverse biased. Safe operating area for transistor

during turn-off is specified as reverse blocking safe operating area (RBSOA).

GATE TURN OFF (G.T.O.) THYRISTOR

A gate turn-off thyristor, a pnpn device, can be turned on like an ordinary

thyristor by a pulse of positive gate current.

In inverter and chopper circuits, a thyristor can be turned off by forced

commutation. For such applications, a GTO is, however, a more versatile

device it can be easily turned off by a negative gate pulse of appropriate

amplitude.

GTOs were developed sometimes in the late 1960s but these could not find

commercial use because of certain performance problems.

Only recently, modern technology has helped in the improved performance of

GTOs and these are now being used in several commercial inverters.

As no forced commutation circuitry is required for GTOs, inverters using these

devices are compact and cost less.

The negative gate current required to turn off a GTO is quite a large

percentage (20 to 30%) of anode current prior to commutation.

Static V-I Characteristics of GTOs

Typical static V I characteristics for a GTO thyristor are shown in Fig. 4.50

(b).

It is seen from these characteristics that latching current for large power

GTOs is several amperes (here 2A) as compared to 100500 mA for

conventional thyristors of the same rating.

If gate current is not able to turn on the GTO, it behaves like a high voltage,

low gain transistor with considerable anode current. This leads to a noticeable

power loss under such conditions.

Switching Performance

A basic gate drive circuit for a GTO is shown in Fig. 4.51 (a). For turning-on a

GTO, first transistor TR1 is turned on, this in turn switches on TR2 to apply a

positive gate-current pulse to turn on GTO.

For turning off the GTO, the turn-off circuit should be capable outputting a

high peak current. Usually, a thyristor is used for this purpose.

In Fig. 451 turn-off process is initiated by gating thyristor Ti. When Ti is

turned on, a large negative gate current pulse turns off the GTO.

Gate turn-on. The turn-on process for a GTO is similar to that of a

conventional thyristor.

Gate turn-on time for GTO is made up of delay time, rise time and spread

time like a thyristor. Further, turn-on time in a GTO can be decreased by

increasing its forward gate current in a thyristor. Gate turn-off.

The turn-off characteristics of a GTO are different from those of an SCR,

Before the initiation of turn-off process, a GTO carries a steady current I Fig.

4.51 (h).

This figure shows a typical turn-off dynamic characteristic for a GTO. The total

turn off time tq subdivided into three different periods; namely the storage

period (t

s

), the fall period (t

f

) and the tail period (t

i

). In other words,

Initiation of turn-off process starts as soon as negative gate current begins to

flow after t = 0.

The rate of rise of this gate current depends upon the gate circuit inductance

and the gate voltage applied.

During the storage period, anode current Ia and anode voltage (equal to on-

state voltage drop) remain constant.

Termination of the storage period is indicated by a fall in I

a

and rise in V

a

During t

s

excess charges, i.e. holes, in p-base are removed by negative gate

current and the centre junction comes out of saturation.

In other words, during storage time t

s

the negative gate current rises to a

particular value and prepare the GTO for turning-off (or commutation) by

flushing out the stored carriers.

After t

s

anode current begins to fall rapidly and anode voltage starts rising. As

shown in Fig. 4.51 (b), the anode current falls to a certain value and then

abruptly changes its rate of fall.

This interval during which anode current falls rapidly is the fall time t

f

. The fall

period t

f

is measured from the instant gate current is maximum negative to

the instant anode current falls to its tail current.

At the time t = t

s

+ t

f

there is a spike in voltage due to abrupt current

change. After t

f

, anode current a and anode voltage V

a

keep moving towards

their turn-off values for a time t

f

called tail time.

After t

f

anode current reaches zero value and V

a

undergoes a transient

overshoot due to the presence of R C and then stabilizes to its off-state value

equal to the source voltage applied to the anode circuit.

Here R and Cs are the snubber circuit parameters. The turn-off process is

complete when tail current reaches zero.

The over shoot voltage and tail current can be decreased by increasing the

size of C but a compromise with snubber loss must be made. The duration of

t

f

depends upon the device characteristics

A GTO has the following disadvantages as compared to a conventional thyristor:

1. Magnitude of latching and holding currents is more in a GTO.

2. On state voltage drop and the associated loss is more in a GTO.

3. Due to the multicathode structure of GTO, triggering gate current is higher

than that required for a conventional SCR.

4. Gate drive circuit losses are more

5. Its reverse-voltage blocking capability is less than its forward-voltage

blocking capability. But this is no disadvantage so far as inverter circuits are

concerned.

In spite of all these demerits, GTO has the following advantages over an SCR

1. GTO has faster switching speed.

2. Its surge current capability is comparable with an SCR.

3. It has more di/dt rating at turn-on.

4. GTO circuit configuration has lower size and weight as compared to SCR

circuit unit.

5. GTO unit has higher efficiency because an increase in gate-drive power loss

and on-state loss is more than compensated by the elimination of forced

commutation losses.

6. GTO unit has reduced acoustical and electromagnetic noise due to elimination

of commutation chokes.

Breakover Point Any point on the principal voltage-current characteristic for

which the differential resistance is zero and where the principal voltage reaches a

maximum value.

Principal Current A generic term for the current through the collector junction.

Note: It is the current through main terminal 1 and main terminal 2 of a triac or

anode and cathode of an SCR.

Principal Voltage The voltage between the main terminals.

(1) In the case of reverse blocking thyristors, the principal voltage is called positive

when the anode potential is higher than the cathode potential, and called negative

when the anode potential is lower than the cathode potential.

(2) For bidirectional thyristors, the principal voltage is called positive when the

potential of main terminal 2 is higher than the potential of main terminal 1.

Average Gate Power Dissipation [P

G(AV)

] The value of gate power which may be

dissipated between the gate and main terminal 1 (or cathode) averaged over a full

cycle.

Breakover Current (I

BO

) The principal current at the breakover point.

Breakover Voltage (V

BO

) The principal voltage at the breakover point.

Circuit-Commutated Turn-Off Time (t

q

) The time interval between the instant

when the principal current has decreased to zero after external switching of the

principal voltage circuit, and the instant when the thyristor is capable of supporting a

specified principal voltage without turning on.

Critical Rate-of-Rise of Commutation Voltage of a Triac (Commutating

dv/dt)

The minimum value of the rate-of-rise of principal voltage which will cause switching

from the off-state to the on-state immediately following on-state current conduction

in the opposite quadrant.

Critical Rate-of-Rise of Off-State Voltage (Critical or Static dv/dt)

The minimum value of the rate-of-rise of principal voltage which will cause switching

from the off-state to the onstate.

Critical Rate-of-Rise of On-State Current (di/dt)

The maximum value of the rate-of-rise of on-state current which a thyristor can

withstand without deleterious effect.

Gate-Controlled Turn-On Time (t

gt

) The time interval between a specified point

at the beginning of the gate pulse and the instant when the principal voltage

(current) has dropped (risen) to a specified low (high) value during switching of a

thyristor from off-state to the on-state by a gate pulse.

Gate Trigger Current (I

GT

) The minimum gate current required to maintain the

thyristor in the on-state.

Gate Trigger Voltage (V

GT

) The gate voltage required to produce the gate trigger

current.

Holding Current (I

H

) The minimum principal current required to maintain the

thyristor in the on-state.

Latching Current (I

L

) The minimum principal current required to maintain the

thyristor in the on-state immediately after switching from the off-state to the on-

state has occurred and the triggering signal has been removed.

On-State Current (I

T

) The principal current when the thyristor is in the on state.

On-State Voltage (V

T

) The principal voltage when the thyristor is in the on-state.

Peak Gate Power Dissipation (PGM) The maximum power which may be

dissipated between the gate and main terminal 1 (or cathode) for a specified time

duration.

Repetitive Peak Off-State Current (I

DRM

) The maximum instantaneous value of

the off-state current that results from the application of repetitive peak off-state

voltage.

Repetitive Peak Off-State Voltage (V

DRM

) The maximum instantaneous value of

the off-state voltage which occurs across a thyristor, including all repetitive transient

voltages, but excluding all non-repetitive transient voltages.

Repetitive Peak Reverse Current of an SCR (I

RRM

) The maximum

instantaneous value of the reverse current that results from the application of

repetitive peak reverse voltage.

Repetitive Peak Reverse Voltage of an SCR (V

RRM

) The maximum

instantaneous value of the reverse voltage which occurs across the thyristor,

including all repetitive transient voltages, but excluding all non-repetitive transient

voltages.

Surge (Non-Repetitive) On-State Current (I

TSM

) An onstate current of short-

time duration and specified waveshape.

Thermal Resistance, Junction to Ambient (R

qJA

) The temperature difference

between the thyristor junction and ambient divided by the power dissipation causing

the temperature difference under conditions of thermal equilibrium.

Note: Ambient is defined as the point where temperature does not change as the

result of dissipation.

Thermal Resistance, Junction to Case (R

qJC

) The temperature difference

between the thyristor junction and the thyristor case divided by the power

dissipation causing the temperature difference under conditions of thermal

equilibrium.

POWER ELECTRONICS

Part A

1. What are the differences between Transistor & SCR?

2. Explain latching current and holding current of thyristor.

3. Define softness factor of power diode

4. What is reverse recovery time?

5. Draw the VI characteristics of SCR and mark the holding current and latching

current in the characteristics.

6. Define string efficiency of SCRs connected in series.

7. What are the advantages of GTO over BJT?

8. Define holding current and latching current of SCR

9. What is the purpose of di/dt and dv/dt protection?

10. What is an off state condition of thyristors?

Part B

1) (i) Draw the two transistor model of SCR and drive an expression for anode

current

(ii) Explain the characteristics of SCR. Describe the various methods of thyristor

turn on.

2) Explain the switching characteristics of MOSFET. How does the concept of

Saturation differs in MOSFET.

3) Explain various triggering methods and commutation of a TRIAC. Explain the

difference between TRIAC and SCR.

4) Discuss various gate drive circuits for a GTO. Give the merits and demerits of a

GTO as compared to a conventional SCR.

5) Explain the safe operating areas of an IGBT and briefly explain the gate drive

circuit for IGBT.

Das könnte Ihnen auch gefallen

- Half Wave Rectifier PDFDokument23 SeitenHalf Wave Rectifier PDFArjun SinghNoch keine Bewertungen

- Sony Sa-Wp1500 Ver1.0Dokument14 SeitenSony Sa-Wp1500 Ver1.0Crist MartinezNoch keine Bewertungen

- Power Electronics 2010-2011Dokument68 SeitenPower Electronics 2010-2011Adnan Younus100% (1)

- Chapter OneDokument105 SeitenChapter Oneadugna abdissaNoch keine Bewertungen

- Chapter - 1 Power Electronics ControlDokument0 SeitenChapter - 1 Power Electronics Controlwww.bhawesh.com.npNoch keine Bewertungen

- Sayas Wara GadaDokument18 SeitenSayas Wara GadaisseywarragadaaNoch keine Bewertungen

- Chapter One Semi Conductor DevicesDokument50 SeitenChapter One Semi Conductor DevicesbirhanuNoch keine Bewertungen

- Power ElectronicsDokument114 SeitenPower ElectronicsRoyal LakhemaruNoch keine Bewertungen

- NAME - Saurav Gupta Roll No - 19ME3FP14: ApparatusDokument26 SeitenNAME - Saurav Gupta Roll No - 19ME3FP14: Apparatussaurav guptaNoch keine Bewertungen

- AEC Module1 Clipping and ClampingDokument43 SeitenAEC Module1 Clipping and ClampingVinay kumar havinalNoch keine Bewertungen

- Power DiodesDokument5 SeitenPower DiodesJahan ZaibNoch keine Bewertungen

- Unit - 1 AspDokument52 SeitenUnit - 1 AspGaurav KumarNoch keine Bewertungen

- Introduction To Power ElectronicsDokument33 SeitenIntroduction To Power ElectronicsRama Murali KrishnaNoch keine Bewertungen

- Ree601 PDFDokument9 SeitenRee601 PDFJ JulietNoch keine Bewertungen

- Sem V Bee 502power ElectronicsDokument111 SeitenSem V Bee 502power ElectronicsnazibNoch keine Bewertungen

- EEE 2308 Lecture 1 - IntroductionDokument11 SeitenEEE 2308 Lecture 1 - IntroductionIAMMARKSNoch keine Bewertungen

- EEE T2 NotesDokument6 SeitenEEE T2 Notesjoshinihar19Noch keine Bewertungen

- EE4532 Part A Lecture - pdf0Dokument83 SeitenEE4532 Part A Lecture - pdf0Denise Isebella LeeNoch keine Bewertungen

- Edc 2 Marks QBDokument18 SeitenEdc 2 Marks QBAnonymous lt2LFZHNoch keine Bewertungen

- Samuel Caesar F. Talidro BSEE-4: 1. Shockley DiodeDokument10 SeitenSamuel Caesar F. Talidro BSEE-4: 1. Shockley DiodeSamuel Caesar TalidroNoch keine Bewertungen

- Lab 1Dokument4 SeitenLab 1Charles BentonNoch keine Bewertungen

- Lecture 4 Diode Circuits NewDokument76 SeitenLecture 4 Diode Circuits Newصدام حسینNoch keine Bewertungen

- 41-44 Lecture Microwave Solid State DevicesDokument61 Seiten41-44 Lecture Microwave Solid State Deviceskumarnpcc0% (3)

- EI2203 - Electronic Devices and Circuits - 2 Marks With AnswersDokument16 SeitenEI2203 - Electronic Devices and Circuits - 2 Marks With AnswersASPCN 2017Noch keine Bewertungen

- Unit - I Power Semi Conductor Devices Syllabus: Semiconductor Power Diodes, Thyristors - Silicon Controlled Rectifiers (SCR'S) - Triacs, GtosDokument33 SeitenUnit - I Power Semi Conductor Devices Syllabus: Semiconductor Power Diodes, Thyristors - Silicon Controlled Rectifiers (SCR'S) - Triacs, GtosRAJOLI GIRISAI MADHAVNoch keine Bewertungen

- Chap 6Dokument8 SeitenChap 6S M JOYNoch keine Bewertungen

- Chap 6Dokument8 SeitenChap 6S M JOYNoch keine Bewertungen

- Eee421: Power Electronics: Power Semiconductor Devices:DiodeDokument12 SeitenEee421: Power Electronics: Power Semiconductor Devices:DiodeRafat ShamsNoch keine Bewertungen

- Unit-1 NotesDokument61 SeitenUnit-1 NotesSaiBhavaniCNoch keine Bewertungen

- EDC Lab ManualDokument45 SeitenEDC Lab ManualChirag Sachdeva100% (2)

- Power Semiconductor DivcesDokument58 SeitenPower Semiconductor Divces김김Noch keine Bewertungen

- Eee421: Power Electronics: Power Semiconductor Devices: DiodeDokument12 SeitenEee421: Power Electronics: Power Semiconductor Devices: DiodeRafat ShamsNoch keine Bewertungen

- 2 Power Semiconductor Diodes & BJTDokument63 Seiten2 Power Semiconductor Diodes & BJTSayan DasNoch keine Bewertungen

- RACTIFIERDokument19 SeitenRACTIFIERDhananjay Aghara100% (1)

- Full WaveDokument17 SeitenFull WaveSandeep KumarNoch keine Bewertungen

- Electronics Devices & Circuit Lab ManualDokument53 SeitenElectronics Devices & Circuit Lab Manualbiswajit7sarkar100% (1)

- Chapter Two: Ac-Dc Conversion: Uncontroled RectificationsDokument53 SeitenChapter Two: Ac-Dc Conversion: Uncontroled Rectificationsfor life100% (3)

- Untitled DocumentDokument12 SeitenUntitled Documentaadietya11129Noch keine Bewertungen

- Pe FINALDokument131 SeitenPe FINALAnonymous R4WpNxNoch keine Bewertungen

- Unit 1 Lecture 2Dokument43 SeitenUnit 1 Lecture 2Shamil GadaNoch keine Bewertungen

- Emergency Lighting Fluorescent Lamp: AbstractDokument20 SeitenEmergency Lighting Fluorescent Lamp: AbstractAakash SheelvantNoch keine Bewertungen

- 3rd Semester Lab 201Dokument36 Seiten3rd Semester Lab 201Noor HussainNoch keine Bewertungen

- Power Semiconductor Diodes and CircuitsDokument20 SeitenPower Semiconductor Diodes and CircuitsHassan FrazNoch keine Bewertungen

- 02 - Power Devices - IDokument19 Seiten02 - Power Devices - IInaya ResthaNoch keine Bewertungen

- Ec6202-Electronic Devices and Circuits 2 Marks and 16 Marks (Q&A) Unit 1Dokument31 SeitenEc6202-Electronic Devices and Circuits 2 Marks and 16 Marks (Q&A) Unit 1SayiTisanShalomNoch keine Bewertungen

- One-Quadrant Switched-Mode Power Converters: R. PetrocelliDokument26 SeitenOne-Quadrant Switched-Mode Power Converters: R. PetrocelliClaudiu UdrescuNoch keine Bewertungen

- Power Semiconductor DevicesDokument62 SeitenPower Semiconductor DevicesMD. SADEKUL ISLAM RIMON 1502084Noch keine Bewertungen

- Triggering Circuit For Thyristors.: Project ProposalDokument9 SeitenTriggering Circuit For Thyristors.: Project Proposalmohsin AwanNoch keine Bewertungen

- 3Dokument48 Seiten3j4xzj8vx4Noch keine Bewertungen

- Analog Fault DerivationDokument89 SeitenAnalog Fault DerivationSachidananda SwarNoch keine Bewertungen

- Asymmetrical Full-Bridge ConverterDokument9 SeitenAsymmetrical Full-Bridge ConverterAthiesh KumarNoch keine Bewertungen

- Unit-3: REGULATORS:Half Wave Rectifier, Ripple FactorDokument12 SeitenUnit-3: REGULATORS:Half Wave Rectifier, Ripple FactorShinde SaikiranNoch keine Bewertungen

- Index: Web Space - Website Hosting - Business Hosting - Free Website Submission - Shopping Cart - PHP HostingDokument12 SeitenIndex: Web Space - Website Hosting - Business Hosting - Free Website Submission - Shopping Cart - PHP Hostingcelo81Noch keine Bewertungen

- Basic DC To DCDokument36 SeitenBasic DC To DCstrelectronicsNoch keine Bewertungen

- Ee 328 Lecture 1Dokument40 SeitenEe 328 Lecture 1Hasan Hatice IlcalıNoch keine Bewertungen

- EE6503-Power ElectronicsDokument41 SeitenEE6503-Power Electronicscwizard60Noch keine Bewertungen

- Electronics Lab 2019Dokument37 SeitenElectronics Lab 2019Noor HussainNoch keine Bewertungen

- Electronics: - Electronics Is A Branch of ScienceDokument43 SeitenElectronics: - Electronics Is A Branch of SciencemozammilNoch keine Bewertungen

- A Full Wave Rectifier: VoltsDokument7 SeitenA Full Wave Rectifier: Voltsanon_85099888Noch keine Bewertungen

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Von EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Noch keine Bewertungen

- Power ElectronicsDokument15 SeitenPower ElectronicsSatya Sudhakar RasamsettiNoch keine Bewertungen

- Unit 3 Ee336Dokument30 SeitenUnit 3 Ee336Satya Sudhakar RasamsettiNoch keine Bewertungen

- Unit 5 Ee336Dokument46 SeitenUnit 5 Ee336Satya Sudhakar RasamsettiNoch keine Bewertungen

- Unit 4 Ee336Dokument31 SeitenUnit 4 Ee336Satya Sudhakar RasamsettiNoch keine Bewertungen

- Design of Electrical Apparatus Unit-IDokument26 SeitenDesign of Electrical Apparatus Unit-ISatya Sudhakar RasamsettiNoch keine Bewertungen

- Design of DC Machines ConstructionDokument42 SeitenDesign of DC Machines ConstructionSatya Sudhakar RasamsettiNoch keine Bewertungen

- Unit 5 Ee336Dokument46 SeitenUnit 5 Ee336Satya Sudhakar RasamsettiNoch keine Bewertungen

- Unit 4 Ee336Dokument31 SeitenUnit 4 Ee336Satya Sudhakar RasamsettiNoch keine Bewertungen

- Design of DC Machines ConstructionDokument42 SeitenDesign of DC Machines ConstructionSatya Sudhakar RasamsettiNoch keine Bewertungen

- Unit 3 Ee336Dokument30 SeitenUnit 3 Ee336Satya Sudhakar RasamsettiNoch keine Bewertungen

- Design of Electrical Apparatus Unit-IDokument26 SeitenDesign of Electrical Apparatus Unit-ISatya Sudhakar RasamsettiNoch keine Bewertungen

- Armature WindingsDokument10 SeitenArmature WindingsSatya Sudhakar RasamsettiNoch keine Bewertungen

- Cummins Service Tool Bench Calibration 3377791 PDFDokument8 SeitenCummins Service Tool Bench Calibration 3377791 PDFDuy Kha100% (4)

- HP Pavillion dv2401 TUDokument3 SeitenHP Pavillion dv2401 TUapi-3772095Noch keine Bewertungen

- Product Data Sheet: Circuit Breaker Compact NSX160F, 36 KA at 415 VAC, TMD Trip Unit 160 A, 3 Poles 3dDokument3 SeitenProduct Data Sheet: Circuit Breaker Compact NSX160F, 36 KA at 415 VAC, TMD Trip Unit 160 A, 3 Poles 3dHenry Hasadiah Sanchez AguilarNoch keine Bewertungen

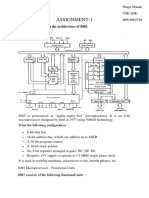

- MPMC Assignment-1Dokument7 SeitenMPMC Assignment-113Panya CSE2Noch keine Bewertungen

- Impedance Relay Timing Test Report: DobleDokument9 SeitenImpedance Relay Timing Test Report: DobleBarry79xNoch keine Bewertungen

- Smiths Connectors Medical BrochureDokument12 SeitenSmiths Connectors Medical BrochureSmiths ConnectorsNoch keine Bewertungen

- Datasheet Sensor UltrasonikDokument5 SeitenDatasheet Sensor UltrasonikHairul AminNoch keine Bewertungen

- EE602 - Statistical Signal Processing Lecture 2: Review of DSP Basics For SSPDokument26 SeitenEE602 - Statistical Signal Processing Lecture 2: Review of DSP Basics For SSPIshNoch keine Bewertungen

- Nortel Contact Centre 7.1Dokument205 SeitenNortel Contact Centre 7.1Gontse SitholeNoch keine Bewertungen

- KORG N264 N364 Service ManualDokument14 SeitenKORG N264 N364 Service Manualjfinnegan87Noch keine Bewertungen

- AM Diode ModulatorDokument3 SeitenAM Diode ModulatorAnonymous LsbuQJi2A9100% (2)

- Ax 3000Dokument12 SeitenAx 3000Colvin SergioNoch keine Bewertungen

- B. Write T On The Blank If The Statement Is True and F If The Statement Is FalseDokument1 SeiteB. Write T On The Blank If The Statement Is True and F If The Statement Is FalsePatricia Ann Dulce AmbataNoch keine Bewertungen

- Finlux Chassis Monoplus2 MP2 PDFDokument9 SeitenFinlux Chassis Monoplus2 MP2 PDFReiner BerbesiNoch keine Bewertungen

- Compensators - ControllersDokument22 SeitenCompensators - ControllersPrasanth Kumar0% (1)

- PL DV 2022 - LRDokument66 SeitenPL DV 2022 - LRKempip RahmanNoch keine Bewertungen

- Ic M802 UDokument79 SeitenIc M802 Uharis_fikriNoch keine Bewertungen

- Data Sheet: HEF4515B MSIDokument6 SeitenData Sheet: HEF4515B MSIGoodLookingPirateNoch keine Bewertungen

- 3G-Network Benchmarking Report Nairobi CityDokument57 Seiten3G-Network Benchmarking Report Nairobi CityAmit GurungNoch keine Bewertungen

- Bang Olufsen-3033 PDFDokument152 SeitenBang Olufsen-3033 PDFmrtuktukNoch keine Bewertungen

- Audio CompressionDokument9 SeitenAudio CompressionIshaan EvenidaNoch keine Bewertungen

- Transistor Circuit NotesDokument15 SeitenTransistor Circuit NotesKim KeatNoch keine Bewertungen

- Lab11b - SERVO TRAINER 4 Proportional Plus Integral Control of Servo Trainer SpeedDokument11 SeitenLab11b - SERVO TRAINER 4 Proportional Plus Integral Control of Servo Trainer Speedsairafi100% (3)

- RLFDokument5 SeitenRLFPritam ModakNoch keine Bewertungen

- HTAMDokument30 SeitenHTAMniteshtripathi_jobs100% (1)

- P Spice TutorialDokument9 SeitenP Spice TutorialPeiHanTseringNoch keine Bewertungen

- Zte Iptv: A Great IPTV Solution From China: System Architecture & ComponentsDokument2 SeitenZte Iptv: A Great IPTV Solution From China: System Architecture & ComponentsAdDit MokyuNoch keine Bewertungen

- Bank Box Go SpecificationDokument8 SeitenBank Box Go Specificationsafe upiNoch keine Bewertungen

- Fuses and FusingDokument3 SeitenFuses and FusingDiego García MedinaNoch keine Bewertungen