Beruflich Dokumente

Kultur Dokumente

Mosfets LOW High: (DGDT) For Power

Hochgeladen von

ΕπαμεινώνδαςΣκανδάληςOriginaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Mosfets LOW High: (DGDT) For Power

Hochgeladen von

ΕπαμεινώνδαςΣκανδάληςCopyright:

Verfügbare Formate

82 Proceedings 1997 IEEE International SO1 Conference, Oct.

1997

Double Gate Dynamic Threshold Voltage (DGDT) SO1 MOSFETs for LOW Power High

Performance Designs

Liqiong Wei, Zhanping Chen, Kaushik Roy

ECE department, Purdue University, West Lafayette, 47907- 1285

With the growing use of portable and wireless electronic systems, reduction in power consumption has become one of

the main concerns in todays VLSI circuit and system design. Lowering supply voltage along with scaling threshold

voltage is an effective way to achieve low power and high performance circuits. However, subthreshold leakage cur-

rent increases and leakage power is no longer negligible. Thin filmfully-depleted (FD) SO1 MOSFET has nearly

ideal subthreshold slope and small parasitic capacitance, which makes it attractive in low voltage high performance

applications. However, it is difficult to control the threshold voltage of FD SO1 MOSFETs. Dynamic threshold volt-

age MOSFET (DTMOS) can control threshold voltage dynamically by biasing the body [I], which requires ultra low

supply voltage (below 0.6V). Considering that the back gate can be used to control the front gate threshold voltage

[2][3] and reduce the sensitivity of threshold voltage to the thin silicon film [4], DTMOS can be achieved by double

gate FD SO1 devices. In this paper, double gate dynamic threshold voltage (DGDT) SO1 MOSFETs, which combine

the advantages of DTMOS and FDSO1 MOSFETs without the limitation of the supply voltage, are simulated using

SOI-SPICE4.4. The threshold voltages, leakage currents and drive currents for FD SO1 MOSFETs and DGDT SO1

MOSFETs are compared. DGDT SO1 MOSFET shows symmetric characteristics and the best Ion/& Excellent DC

inverter characteristics down to 0.15V and good full adder performance at 1V areshown. The propagation delay and

the average power consumption of the full adder are 0.62511s and 1 ISpW, respectively. It can be seen that DGDT SO1

MOSFET is a good candidate for low power high performance designs.

Figure 1 shows the structures of FDSOI MOSFET and DGDT SO1 MOSFET. Back gate oxide of DGDT SO1 MOS-

FET is thick enough to make the threshold voltage of the back gate larger than the supply voltage. Since the front gate

and back gate surface potentials are strongly coupled to each other, the front gate can be regarded as a conducting

gate while the back gate acts as a controlling gate for the front gate. Figure 2 shows the I-V characteristics of FD SO1

MOSFETs and DGDT SO1 MOSFETs. The design presumes 0.5pm channel lengths and dual polysilicon gates. The

front gate oxide thickness (bf), silicon layer thickness (Gi) and back gate oxide thickness (bb) are 7nm, 50nmand

20nm, respectively. The body doping densities of NMOSFETs and PMOSETs are 2.5E17~m-~ and 3.2E17cm,

respectively. For FD NMOSFET(PMOSFET), the threshold voltage can vary from 0.13V (-0.13V) to 0.35V (-0.36V)

as the back gate to source bias is changed from IV (-1V) to OV. DGDT SO1 MOSFETs show better subthreshold

characteristics than FD SO1 MOSFETs and the threshold voltage can be altered dynamically to suit the operating

state of the circuit. A high threshold voltage in the standby mode gives low leakage current (Ior), while a low thresh-

old allows for higher current drives (bn) in the active mode of operation. Figure 3 shows the variation in the range of

threshold voltage for different Gi and t&. The thinner the silicon layer thickness, the smaller is the threshold voltage.

This results in a higher drive current, but also larger leakage current. Thinning t,,b can improve the controllability of

the back gate to the front gate, which increases the threshold voltage variation range. Even though the back gate

capacitance will also be increased, it is much smaller than the front gate capacitance while interconnect capacitance

may be dominant for deep submicron VLSI. If the back gate oxide thickness is compatible with the front gate oxide

thickness, the back channel may conduct It can improve the drive current, but the leakage current and gate capaci-

tance will bestrongly increased. Table1 shows the comparison of I on/ I o~ for different FD SO1 MOSFETs and DGDT

SO1 MOSFETs. For typical FDSO1 PMOSFETs, the negative back-gate to source bias (Vg,,,,) lowers the threshold

voltage and makes the leakage current too high to beused in low voltage circuits. DGDT SO1 MOSFET shows sym-

metric characteristics and the best Ion/Iog.

Figure 4 shows the DGDT SO1 inverter voltage transfer characteristics (VTC) for different supply voltages. Good

noise margins can been seen even when the supply voltage is scaled down to 0.15V. A full adder (figure 5) is simu-

lated for DGDT SO1 and modified FDSOI (VgbspOV) structures with a supply voltage of 1V. The propagation

delays are 0.62%~and 0.7511s while the average power consumptions are 11.5pW and 10SpW for DGDT SO1 and

modified FDSOI full adders, respectively. Figure 6 shows the transient waveform.

Simulation results indicate that double gate dynamic threshold voltage (DGDT) SO1 MOSFETs are very attractive for

low power high performance designs.

Reference:[l] Fariborz Assaderaghi, et al., IEDM, p809, 1994 [2] Isabel Y. Yang, et al., IEDM, p877, 1995

[3] Jack P. Denton, et al., IEEE Elec. Dev. Lett.,No.ll, ~509,1996 [ 4] P.C. Yeh, et al., IEEE Int. SO1 Conf., p23, 1994

This research was supported in part by DARPA under contracts (F33615-95-C-1625 and DAAH04-96- 1-0222)

0-7803-3938-X 97CH36069

Proceedings 1997 IEEE International Si31 Conference, Oct. 1997 83

0.40

E

P

z

5 020

F 0.30

a) m

r

w r

c

0.10

TABLE 1. Comparison of Ion/ Io~ for different FDSOI MOSFETs and DGDT SO1 MOSFETs

-

-

.

-

I

Figure 1 The s&ctures of FD SO1 MOSFET (a) and

DGDTSOI MOSFET (b)

0.50

---

______--------

...... -- ........ .............................

....................................

-ml.s%nn

Duonm

1.)ldonm

- _

50.0 100.0 150.0 m.0

0.00

0.0

t& (nm)

Figure 3 Threshold voltage variation range for

different Gi and t(,b

Vdd

I

A

wk"

Figure 5 Schematic of a mirror full adder

10- I

io-.. t

J; , . y+ . ' <

. . .

. . .

-i .o -0.5 0.0 0.5 I .O

votr, 01)

l o-" f

Figure2 I-V characteristics of FD SO1 MOSFETs

and DGDT SO1 MOSFETs

0.8 O.* t

wp2w-

M. 5 "

Toh7nm

Tob3Onm

0.4 TSi -

w

0 2 0.4 0.6 0.8 1 .O

0.0

0.0

Vi M

Figure 4 VTC of DGDT SO1 inverter

I

-0.2 I

" , , . , . a t -

0 5e-09 le-08 15608 2848 2 . 5 e M

-0-

0 Se-OS 10-08 1.5048 2608 2.5e-013

1 [S)

Figure 6 Transient analysis of the full adder (Vdd,=IV)

Das könnte Ihnen auch gefallen

- Diode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesVon EverandDiode, Transistor & Fet Circuits Manual: Newnes Circuits Manual SeriesBewertung: 4.5 von 5 Sternen4.5/5 (7)

- High Voltage Junctionless FET With Improved DC Performance Compared To LDMOSDokument4 SeitenHigh Voltage Junctionless FET With Improved DC Performance Compared To LDMOSIJSTENoch keine Bewertungen

- Choosing Power Switching Devices For SMPS Designs: Mosfets or Igbts?Dokument6 SeitenChoosing Power Switching Devices For SMPS Designs: Mosfets or Igbts?RubenG200Noch keine Bewertungen

- Understanding Power MosfetsDokument5 SeitenUnderstanding Power MosfetsIskander XandrosNoch keine Bewertungen

- Mosfet: By: Mohamed Ahmed EL - Maghawry Mohamed Adel Yomna MohammedDokument16 SeitenMosfet: By: Mohamed Ahmed EL - Maghawry Mohamed Adel Yomna MohammedAhmed Mahmoud AhmedNoch keine Bewertungen

- Conduction Power Loss in MOSFET Synchronous Rectifier With Parallel-Connected Schottky Barrier DiodeDokument7 SeitenConduction Power Loss in MOSFET Synchronous Rectifier With Parallel-Connected Schottky Barrier DiodeMuhammad Saqib AliNoch keine Bewertungen

- Stacked High Voltage Switch Based S I C Vjfets: ISPSD 2003, April 14-17, UKDokument4 SeitenStacked High Voltage Switch Based S I C Vjfets: ISPSD 2003, April 14-17, UKМилан ЛукићNoch keine Bewertungen

- Practical Considerations When Comparing Sic and Gan in Power Applications White PaperDokument11 SeitenPractical Considerations When Comparing Sic and Gan in Power Applications White PaperIvan DumontNoch keine Bewertungen

- Design and Simulation of A Two Stage OPAMPDokument4 SeitenDesign and Simulation of A Two Stage OPAMPAbd TashNoch keine Bewertungen

- Application Note AN-983: IGBT CharacteristicsDokument16 SeitenApplication Note AN-983: IGBT Characteristicswizardgrt1Noch keine Bewertungen

- Ti - Mosfet Gate DriveDokument40 SeitenTi - Mosfet Gate Drivedownload_cruxNoch keine Bewertungen

- Comparative Study of SOI MOSFET for Low Power AppsDokument19 SeitenComparative Study of SOI MOSFET for Low Power AppsMohd AzlanNoch keine Bewertungen

- Mosfet To TfetDokument4 SeitenMosfet To TfetmuktikantaNoch keine Bewertungen

- Assignment FET 2Dokument3 SeitenAssignment FET 2shobanraj1995Noch keine Bewertungen

- SO1 and Nanoscale MOSFETsDokument2 SeitenSO1 and Nanoscale MOSFETsAnonymous OUnaZ1g9Noch keine Bewertungen

- 1999 - Fully-Depleted SOI CMOSDokument16 Seiten1999 - Fully-Depleted SOI CMOSrpaucar1979Noch keine Bewertungen

- Subthreshold Operation in Mosfets: Vidisha Verma, 2015189Dokument3 SeitenSubthreshold Operation in Mosfets: Vidisha Verma, 2015189Frank MartinNoch keine Bewertungen

- An Efficiency Primer For Switch-Mode, DC-DC Converter Power SuppliesDokument11 SeitenAn Efficiency Primer For Switch-Mode, DC-DC Converter Power SuppliesJonathan JaegerNoch keine Bewertungen

- EDN Design Ideas 2005Dokument134 SeitenEDN Design Ideas 2005chag1956100% (2)

- Silicon-on-Ferroelectric Insulator Field-Effect Transistor: Review ArticleDokument10 SeitenSilicon-on-Ferroelectric Insulator Field-Effect Transistor: Review ArticleBryanNoch keine Bewertungen

- User Manual For The Mosfet Irf 530 Power Amplifier Functional ModuleDokument14 SeitenUser Manual For The Mosfet Irf 530 Power Amplifier Functional ModuleemilianoNoch keine Bewertungen

- Power MOSFET Basics: Structure, Operation Limits & SwitchingDokument12 SeitenPower MOSFET Basics: Structure, Operation Limits & SwitchingBrightchip TechnologiesNoch keine Bewertungen

- IGBT or MOSFET: Choose Wisely: by Carl Blake and Chris Bull, International RectifierDokument5 SeitenIGBT or MOSFET: Choose Wisely: by Carl Blake and Chris Bull, International RectifiergubiliNoch keine Bewertungen

- GIDLDokument4 SeitenGIDLTnSharmaNoch keine Bewertungen

- History of Power Mosfets: ApplicationsDokument7 SeitenHistory of Power Mosfets: ApplicationsVaishali PatelNoch keine Bewertungen

- Project 1: Power Electronics IDokument10 SeitenProject 1: Power Electronics ISaratul AkmaNoch keine Bewertungen

- Power MOSFET: Basic StructureDokument10 SeitenPower MOSFET: Basic StructureDomagoj ProphectusNoch keine Bewertungen

- The Design of Integrated Switches and Phase Shifters: Liam DevlinDokument15 SeitenThe Design of Integrated Switches and Phase Shifters: Liam Devlinriccardo tarelliNoch keine Bewertungen

- Better ORing Diode PDFDokument5 SeitenBetter ORing Diode PDFYacine BàssotiNoch keine Bewertungen

- EI2403 - VLSI Design 2 Marks With AnswersDokument23 SeitenEI2403 - VLSI Design 2 Marks With AnswersAnand GvphNoch keine Bewertungen

- Analog Switches and Multiplexers BasicsDokument23 SeitenAnalog Switches and Multiplexers BasicsOfir CzNoch keine Bewertungen

- Anti-Parallel Diode PairDokument14 SeitenAnti-Parallel Diode PairSaid AdamNoch keine Bewertungen

- Full On-Chip CMOS Low-Dropout Voltage RegulatorDokument12 SeitenFull On-Chip CMOS Low-Dropout Voltage RegulatorashishmanyanNoch keine Bewertungen

- An Adaptive Reconfigurable Rectifier For Wireless Power TransmissionDokument3 SeitenAn Adaptive Reconfigurable Rectifier For Wireless Power Transmissionkavirasu1990Noch keine Bewertungen

- Two-Dimensional Analytical Threshold Voltage and Subthreshold Swing Models of Undoped Symmetric Double-Gate MosfetsDokument7 SeitenTwo-Dimensional Analytical Threshold Voltage and Subthreshold Swing Models of Undoped Symmetric Double-Gate Mosfetssurajkumar16Noch keine Bewertungen

- An 7506Dokument9 SeitenAn 7506MallickarjunaNoch keine Bewertungen

- MOSIC Amplifiers - Constant Current Source CircuitDokument18 SeitenMOSIC Amplifiers - Constant Current Source CircuitNoorullah ShariffNoch keine Bewertungen

- Mosfet CharacteristicsDokument12 SeitenMosfet CharacteristicsNavaneethaan NathamoorthyNoch keine Bewertungen

- WP HighPerfomanceZVSDokument10 SeitenWP HighPerfomanceZVSAdrian TanaseNoch keine Bewertungen

- AN-478A TextDokument12 SeitenAN-478A TextAl BenNoch keine Bewertungen

- Latest Technology PT Igbts vs. Power Mosfets: Application Note Apt0302 Rev. A April 4, 2003Dokument6 SeitenLatest Technology PT Igbts vs. Power Mosfets: Application Note Apt0302 Rev. A April 4, 2003Jyothsna VayyalaNoch keine Bewertungen

- Design of Cmos BufferDokument5 SeitenDesign of Cmos BufferVarunKaradesaiNoch keine Bewertungen

- Power MosfetsDokument17 SeitenPower MosfetsKyaw SoeNoch keine Bewertungen

- Power Loss in Switching MOSFETsDokument6 SeitenPower Loss in Switching MOSFETsManju RajagopalNoch keine Bewertungen

- D AND E MOSFETsDokument13 SeitenD AND E MOSFETsSRMEA SAN RAFAEL BULACANNoch keine Bewertungen

- AN521 Intoduction To IGBTDokument10 SeitenAN521 Intoduction To IGBTBuelnitaNoch keine Bewertungen

- Ch. 7 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsDokument43 SeitenCh. 7 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsChenming Hu100% (1)

- MOSFET Selection To Minimize Losses in Low Output Voltage DC DC ConvertersDokument23 SeitenMOSFET Selection To Minimize Losses in Low Output Voltage DC DC ConvertersTan Li KarNoch keine Bewertungen

- The Basics of Power Semiconductor Devices - Structures, Symbols, and Operations - Technical ArticlesDokument26 SeitenThe Basics of Power Semiconductor Devices - Structures, Symbols, and Operations - Technical ArticlesNanizeye Da GraçaNoch keine Bewertungen

- Nem Relay Based Low Power Design: 1. Literature ReviewDokument10 SeitenNem Relay Based Low Power Design: 1. Literature Reviewblessysara16Noch keine Bewertungen

- Pms Dei 062200Dokument4 SeitenPms Dei 062200Afrizal ALANANoch keine Bewertungen

- Mosfet Igbt BJT Difference and ApplicationDokument5 SeitenMosfet Igbt BJT Difference and ApplicationSangammeshwra AbNoch keine Bewertungen

- 3 s2.0 B9780444531537000080 MainDokument32 Seiten3 s2.0 B9780444531537000080 MainSanjay G RNoch keine Bewertungen

- Capacitor Less LdoDokument11 SeitenCapacitor Less LdoantharmukiNoch keine Bewertungen

- Jfet MosfetDokument25 SeitenJfet Mosfethrishabhraj710Noch keine Bewertungen

- Double Gate MosDokument21 SeitenDouble Gate MosdayaNoch keine Bewertungen

- Electronics Chapter 4Dokument16 SeitenElectronics Chapter 4YidnekachewNoch keine Bewertungen

- (DV-DT) MOSFET Basics-Fairchild (Am Citito)Dokument17 Seiten(DV-DT) MOSFET Basics-Fairchild (Am Citito)CataNoch keine Bewertungen

- Polysilazane - CuringDokument8 SeitenPolysilazane - CuringthuronNoch keine Bewertungen

- Vilano Cacao ECE Experiment2 PDFDokument22 SeitenVilano Cacao ECE Experiment2 PDFMonirachanthystNoch keine Bewertungen

- SBS VRLA Type Front Terminal Range Summary PDFDokument2 SeitenSBS VRLA Type Front Terminal Range Summary PDFehott23Noch keine Bewertungen

- Cargador Espress Exp - Unimax10-15Dokument2 SeitenCargador Espress Exp - Unimax10-15Kristian FonNoch keine Bewertungen

- Magnetic Flow MeterDokument3 SeitenMagnetic Flow Meterniazakhtar100% (1)

- Callate Gate 2: Parts List LayoutDokument1 SeiteCallate Gate 2: Parts List LayoutStefan HacknerNoch keine Bewertungen

- Ece Department - ANNA UNIVERSITY Important Question and Answers - Regulation 2013,2017 - STUDY MATERIAL, NotesDokument5 SeitenEce Department - ANNA UNIVERSITY Important Question and Answers - Regulation 2013,2017 - STUDY MATERIAL, NotesKali Thaash100% (2)

- LM35 Datasheet PDFDokument30 SeitenLM35 Datasheet PDFFrank ThoriqNoch keine Bewertungen

- Ferroelectric RamDokument20 SeitenFerroelectric RamRijy LoranceNoch keine Bewertungen

- Indelec pinoybixMCQDokument22 SeitenIndelec pinoybixMCQAndreana AmorNoch keine Bewertungen

- Electronic Measurements and Instrumentation QBDokument9 SeitenElectronic Measurements and Instrumentation QBSridhar Koneru VenkkatNoch keine Bewertungen

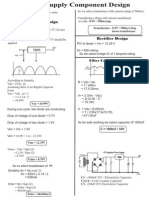

- Power Supply Design 2Dokument1 SeitePower Supply Design 2Kunal Khandelwal100% (2)

- Power Factor Controllers Prophi by Janitza Electronics GMBHDokument9 SeitenPower Factor Controllers Prophi by Janitza Electronics GMBHf.saglam77Noch keine Bewertungen

- Kvas 100Dokument98 SeitenKvas 100Vikash Kumar PrasadNoch keine Bewertungen

- Design and Implementation of FPGA Based Solar Power Saving System For Street Lighting and Automatic Traffic ControllerDokument2 SeitenDesign and Implementation of FPGA Based Solar Power Saving System For Street Lighting and Automatic Traffic ControllerKaran PatelNoch keine Bewertungen

- Small Signal Operation and Model: Assignment-3Dokument15 SeitenSmall Signal Operation and Model: Assignment-3Keshavamurthy LNoch keine Bewertungen

- Engg ProductsDokument304 SeitenEngg Productsjacky111Noch keine Bewertungen

- CTAB Modification of MCM-49 Zeolite Containing HMI and Its Acylation of AnisoleDokument11 SeitenCTAB Modification of MCM-49 Zeolite Containing HMI and Its Acylation of AnisoleFarida Nur AzizaNoch keine Bewertungen

- Digital Fire Alarm System Operating ManualDokument17 SeitenDigital Fire Alarm System Operating Manualmaithuong8567% (6)

- Lista Tonere Pentru CartuseDokument182 SeitenLista Tonere Pentru CartuseNelu NeluNoch keine Bewertungen

- Service Manual Zenith Eee Sms2049 TVDokument9 SeitenService Manual Zenith Eee Sms2049 TVDeyby GarciaNoch keine Bewertungen

- Heat Transfer Problems and SolutionsDokument2 SeitenHeat Transfer Problems and SolutionsPuneet MeenaNoch keine Bewertungen

- Chapter 8 Differential and Multistage Amplifiers Ee 3120 Microelectronics IIDokument22 SeitenChapter 8 Differential and Multistage Amplifiers Ee 3120 Microelectronics IIswagat656Noch keine Bewertungen

- Atmel 42365 SAM C21 DatasheetDokument1.194 SeitenAtmel 42365 SAM C21 Datasheetalex diazNoch keine Bewertungen

- BE 5 UnitDokument23 SeitenBE 5 Unit08sunnyjaganNoch keine Bewertungen

- Fundamentals of Electric Resistance WeldingDokument40 SeitenFundamentals of Electric Resistance WeldingRajkumar ArumugamNoch keine Bewertungen

- MC33030 DC Servo Motor Controller/Driver: Marking DiagramsDokument17 SeitenMC33030 DC Servo Motor Controller/Driver: Marking DiagramsAndrés ThompsonNoch keine Bewertungen

- Transmission Line 101Dokument6 SeitenTransmission Line 101George Ezar N. QuiriadoNoch keine Bewertungen

- Beng (Hons) Electrical and Electronic Engineering - E430: Modules CreditsDokument9 SeitenBeng (Hons) Electrical and Electronic Engineering - E430: Modules CreditsSalinee BookauramNoch keine Bewertungen

- Electronic CircuitsDokument3 SeitenElectronic CircuitsManoj KavediaNoch keine Bewertungen