Beruflich Dokumente

Kultur Dokumente

Acceso Directo A Memoria

Hochgeladen von

Henry Florián0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

31 Ansichten3 SeitenEl acceso directo a memoria (DMA) permite que dispositivos como tarjetas de sonido y discos duros accedan directamente a la memoria principal sin involucrar a la CPU. Esto evita sobrecargar a la CPU con interrupciones constantes. Sin embargo, la DMA puede causar problemas de coherencia en la memoria caché si no se gestiona correctamente. Los sistemas abordan esto implementando cachés coherentes con hardware o dejando la gestión al software a través del sistema operativo.

Originalbeschreibung:

Originaltitel

Acceso Directo a Memoria

Copyright

© © All Rights Reserved

Verfügbare Formate

DOCX, PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenEl acceso directo a memoria (DMA) permite que dispositivos como tarjetas de sonido y discos duros accedan directamente a la memoria principal sin involucrar a la CPU. Esto evita sobrecargar a la CPU con interrupciones constantes. Sin embargo, la DMA puede causar problemas de coherencia en la memoria caché si no se gestiona correctamente. Los sistemas abordan esto implementando cachés coherentes con hardware o dejando la gestión al software a través del sistema operativo.

Copyright:

© All Rights Reserved

Verfügbare Formate

Als DOCX, PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

31 Ansichten3 SeitenAcceso Directo A Memoria

Hochgeladen von

Henry FloriánEl acceso directo a memoria (DMA) permite que dispositivos como tarjetas de sonido y discos duros accedan directamente a la memoria principal sin involucrar a la CPU. Esto evita sobrecargar a la CPU con interrupciones constantes. Sin embargo, la DMA puede causar problemas de coherencia en la memoria caché si no se gestiona correctamente. Los sistemas abordan esto implementando cachés coherentes con hardware o dejando la gestión al software a través del sistema operativo.

Copyright:

© All Rights Reserved

Verfügbare Formate

Als DOCX, PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 3

ACCESO DIRECTO A MEMORIA

Permite a cierto tipo de componentes de una computadora

acceder a la memoria del sistema para leer o escribir

independientemente de la unidad central de procesamiento

(CPU) principal. Muchos sistemas hardware utilizan DMA,

incluyendo controladores de unidades de disco, tarjetas

grficas y tarjetas de sonido. DMA es una caracterstica esencial

en todos los ordenadores modernos, ya que permite a

dispositivos de diferentes velocidades comunicarse sin someter a

la CPU a una carga masiva de interrupciones.

PROBLEMAS DE COHERENCIA EN LA MEMORIA CACH

La DMA puede llevar a problemas de coherencia de cach.

Imagine una CPU equipada con una memoria cach y una

memoria externa que se pueda acceder directamente por los

dispositivos que utilizan DMA. Cuando la CPU accede a X lugar

en la memoria, el valor actual se almacena en la cach. Si se

realizan operaciones posteriores en X, se actualizar la copia en

cach de X, pero no la versin de memoria externa de X. Si la

cach no se vaca en la memoria antes de que otro dispositivo

intente acceder a X, el dispositivo recibir un valor caducado

de X.

Del mismo modo, si la copia en cach de X no es invalidada

cuando un dispositivo escribe un nuevo valor en la memoria,

entonces la CPU funcionar con un valor caducado de X.

Este problema puede ser abordado en el diseo del sistema de

las siguientes dos formas:

Los sistemas de cach coherente implementan un mtodo

en el hardware externo mediante el cual se escribe una seal

en el controlador de cach, la cual realiza una invalidacin

de la cach para escritura de DMA o cach de descarga

para lectura de DMA.

Los sistemas no-coherente dejan este software, donde el

sistema operativo debe asegurarse de que las lneas de

cach se vacan antes de que una transferencia de salida de

DMA sea iniciada y anulada antes de que una parte de la

memoria sea afectada por una transferencia entrante de

DMA que se haya requerido. El sistema operativo debe

asegurarse de que esa parte de memoria no es accedida

por cualquier subproceso que se ejecute en ese instante. Este

ltimo enfoque introduce cierta sobrecarga a la operacin

de DMA, ya que la mayora de hardware requiere un bucle

para invalidar cada lnea de cach de forma individual.

Los hbridos tambin existen, donde en la cach secundaria L2

es coherente, mientras que en la cach L1 (generalmente la

CPU) es gestionado por el software.

SECUENCIA DE EVENTOS

Una operacin de E/S por DMA se establece ejecutando una

corta rutina de inicializacin. Consiste en varias instrucciones de

salida para asignar valores iniciales a:

AR: Direccin de memoria de la regin de datos de E/S IOBUF

(buffer de entrada/salida).

WC: Nmero N de palabras de datos a transferir.

Una vez inicializado, el DMA procede a transferir datos entre

IOBUF y el dispositivo de E/S. Se realiza una transferencia cuando

el dispositivo de E/S solicite una operacin de DMA a travs de

la lnea de peticin del DMAC.

Despus de cada transferencia, se decrementa el valor de WC

y se incrementa el de AR.

La operacin termina cuando WC=0, entonces el DMAC (o el

perifrico) indica la conclusin de la operacin enviando al

procesador una peticin de interrupcin.

Alumno: Henry Estuardo Florin Njera

Carnet: 0905 09 7568

Universidad Mariano Glvez de Guatemala

Campus Jutiapa

Catedra: Arquitectura de Computadoras

Catedrtico: Ing. Cesar Lzaro

Jutiapa 30 de agosto de 2014

Das könnte Ihnen auch gefallen

- Tema Acceso Directo A Memoria (Dma)Dokument4 SeitenTema Acceso Directo A Memoria (Dma)Jeremy FuentesNoch keine Bewertungen

- Que Es Dma en IngenieriaDokument7 SeitenQue Es Dma en Ingenieriaandrea melgarNoch keine Bewertungen

- Acceso directo a memoria (DMA) permite a dispositivos acceder memoria de forma independiente a CPUDokument6 SeitenAcceso directo a memoria (DMA) permite a dispositivos acceder memoria de forma independiente a CPUEnrique Cabrera QuirozNoch keine Bewertungen

- Acceso directo a memoria (DMA) permite a dispositivos acceder memoria de forma independiente a CPUDokument10 SeitenAcceso directo a memoria (DMA) permite a dispositivos acceder memoria de forma independiente a CPUlezti_chanNoch keine Bewertungen

- DMA y formato de instruccionesDokument6 SeitenDMA y formato de instruccionesEmmanuel QuiñonesNoch keine Bewertungen

- Acceso Directo A La MemoriaDokument5 SeitenAcceso Directo A La MemoriaGalindo Molle CarlosNoch keine Bewertungen

- Acceso Directo A Memoria DMA. Sistemas Operativos, Características Básicas.Dokument18 SeitenAcceso Directo A Memoria DMA. Sistemas Operativos, Características Básicas.Alexander Barboza AnayaNoch keine Bewertungen

- Acceso Directo A MemoriaDokument21 SeitenAcceso Directo A MemoriaJosé ManuelNoch keine Bewertungen

- DmaDokument10 SeitenDmaJosemaría VilledaNoch keine Bewertungen

- Acceso A Memoria DirectoDokument11 SeitenAcceso A Memoria DirectoRaaùl PeerèzNoch keine Bewertungen

- Capas Del Software de eDokument4 SeitenCapas Del Software de eYenifer Boscan100% (1)

- Acceso Directo A Memoria ExpoDokument13 SeitenAcceso Directo A Memoria ExpoAdry RodriguezNoch keine Bewertungen

- Direct Memory Access o DMADokument7 SeitenDirect Memory Access o DMAGeorge AlexisNoch keine Bewertungen

- www.oposinet.comDokument24 Seitenwww.oposinet.comelio ramirezNoch keine Bewertungen

- Interrupciones de HardwareDokument7 SeitenInterrupciones de HardwareJuan Leonardo Medina SanchezNoch keine Bewertungen

- Entrada SalidaDokument43 SeitenEntrada SalidaJulián AgustínNoch keine Bewertungen

- Manejo de La EntradaDokument20 SeitenManejo de La Entradaluis hernandezNoch keine Bewertungen

- Modulo E-SDokument4 SeitenModulo E-SNovedades MLNoch keine Bewertungen

- Sistemas OperativosDokument5 SeitenSistemas OperativosfedericomqsNoch keine Bewertungen

- Sistemas OperativosDokument5 SeitenSistemas OperativosfedericomqsNoch keine Bewertungen

- Sistemas OperativosDokument5 SeitenSistemas OperativosfedericomqsNoch keine Bewertungen

- DmaDokument5 SeitenDmaIsai AlejandroNoch keine Bewertungen

- Gestión E/S y planificación discoDokument20 SeitenGestión E/S y planificación discoJuan Carlos MarínNoch keine Bewertungen

- SO Stallings - Capítulos I-XVDokument56 SeitenSO Stallings - Capítulos I-XVtendoucurienNoch keine Bewertungen

- Gestion de Dispositivos de EntradaDokument8 SeitenGestion de Dispositivos de EntradaAlejandra RochaNoch keine Bewertungen

- Documento 5Dokument8 SeitenDocumento 5almenteroelaineNoch keine Bewertungen

- Resumen de La Máquina de Von NeumannDokument3 SeitenResumen de La Máquina de Von NeumannMel JergiNoch keine Bewertungen

- Qué Es Una InterrupciónDokument7 SeitenQué Es Una InterrupciónCaro BrouchyNoch keine Bewertungen

- Gestión Del Sistema de Entrada y Salida de Los Sistemas Operativos.Dokument5 SeitenGestión Del Sistema de Entrada y Salida de Los Sistemas Operativos.wtnNoch keine Bewertungen

- Universidad Nacional "Pedro Ruíz Gallo": Facultad de Ciencias Físicas Y MatemáticasDokument25 SeitenUniversidad Nacional "Pedro Ruíz Gallo": Facultad de Ciencias Físicas Y MatemáticasYianmarco ChavezNoch keine Bewertungen

- Clase 16-12Dokument28 SeitenClase 16-12llopisfbarrioNoch keine Bewertungen

- Entrada y SalidaDokument6 SeitenEntrada y SalidaManuel RodriguezNoch keine Bewertungen

- Examen Final Arquitectura de Computadoras Semipresencial 2019-IDokument3 SeitenExamen Final Arquitectura de Computadoras Semipresencial 2019-Iroger vegaNoch keine Bewertungen

- Arquitectura de ComputadorasDokument7 SeitenArquitectura de ComputadorasCarlos MendozaNoch keine Bewertungen

- Manejo de DispositivosDokument8 SeitenManejo de DispositivosEmmanuel Jimenez PerezNoch keine Bewertungen

- Ud3.4 Estructura Del So III E-S ArchivosDokument28 SeitenUd3.4 Estructura Del So III E-S ArchivosMarcos MountainsNoch keine Bewertungen

- IntroducciónDokument9 SeitenIntroducciónCARLOS ALBERTO PAREDES ROJASNoch keine Bewertungen

- Arquitectura Von NeumannDokument4 SeitenArquitectura Von NeumannwilkinsNoch keine Bewertungen

- Power Line Communication - PPTX (Repaired)Dokument11 SeitenPower Line Communication - PPTX (Repaired)miguel gallegosNoch keine Bewertungen

- Trabajo Sobre Los Controladores DMADokument5 SeitenTrabajo Sobre Los Controladores DMAVictor ManuelNoch keine Bewertungen

- 2021 08 26 Definicion de Sistema OperativoDokument68 Seiten2021 08 26 Definicion de Sistema OperativoCARLOS ALFREDO MAMANI POMANoch keine Bewertungen

- Sistemas OperativosDokument6 SeitenSistemas OperativosMiguel kunfupandaNoch keine Bewertungen

- Tarea 2 Tema 4 Antonia-1Dokument6 SeitenTarea 2 Tema 4 Antonia-1ELIA GUADALUPE MORALES CABRERANoch keine Bewertungen

- Las Técnicas de Entrada y SalidadDokument5 SeitenLas Técnicas de Entrada y SalidadRodrigo HernandezNoch keine Bewertungen

- Interrupción de HardwareDokument6 SeitenInterrupción de HardwareCindy Lizbeth LinaresNoch keine Bewertungen

- Objetivos del software de entrada y salidaDokument13 SeitenObjetivos del software de entrada y salidaLuz Stefany Verano AlzateNoch keine Bewertungen

- ExposicionDokument13 SeitenExposicionAnton JWNoch keine Bewertungen

- 2 - M1 C1 Arquitecturas de Un Sistema MicroinformáticoDokument12 Seiten2 - M1 C1 Arquitecturas de Un Sistema MicroinformáticodilisnaNoch keine Bewertungen

- Acceso Directo A Memoria DMADokument2 SeitenAcceso Directo A Memoria DMAPablo SolanoNoch keine Bewertungen

- Exposicion ARQUITECTURA DE VON NEUMANNDokument9 SeitenExposicion ARQUITECTURA DE VON NEUMANNYimabel TumbacoNoch keine Bewertungen

- Gestión de Entrada y SalidaDokument6 SeitenGestión de Entrada y SalidajavierjeNoch keine Bewertungen

- Revisión Del Hardware de ComputadoraDokument21 SeitenRevisión Del Hardware de ComputadoraAnonymous U1yUg3Noch keine Bewertungen

- AIM y ADMDokument1 SeiteAIM y ADMJavi_v88Noch keine Bewertungen

- Introducción a la Arquitectura de ComputadoresDokument4 SeitenIntroducción a la Arquitectura de ComputadoresJuan RodriguezNoch keine Bewertungen

- Algoritmos de Programacion Del Brazo Del Disco 2Dokument16 SeitenAlgoritmos de Programacion Del Brazo Del Disco 2Christian Pastor UrquiagaNoch keine Bewertungen

- T2 Arquitectura de Un ComputadorDokument7 SeitenT2 Arquitectura de Un ComputadorSamuelNoch keine Bewertungen

- Interrupciones & DMADokument16 SeitenInterrupciones & DMAYasmin Zülley VeGaNoch keine Bewertungen

- S01 S1-MaterialDokument37 SeitenS01 S1-MaterialIvan LeonardoNoch keine Bewertungen

- UF0852 - Instalación y actualización de sistemas operativosVon EverandUF0852 - Instalación y actualización de sistemas operativosBewertung: 5 von 5 Sternen5/5 (1)

- Desarrollo de componentes software para el manejo de dispositivos. IFCT0609Von EverandDesarrollo de componentes software para el manejo de dispositivos. IFCT0609Noch keine Bewertungen

- Power BiDokument4 SeitenPower BiHenry FloriánNoch keine Bewertungen

- CeibaDokument5 SeitenCeibaHenry FloriánNoch keine Bewertungen

- ElectrónicaDokument9 SeitenElectrónicaHenry FloriánNoch keine Bewertungen

- Charla de AuditoríaDokument2 SeitenCharla de AuditoríaHenry FloriánNoch keine Bewertungen

- CeibaDokument5 SeitenCeibaHenry FloriánNoch keine Bewertungen

- ImparableDokument3 SeitenImparableHenry FloriánNoch keine Bewertungen

- Ejercicios de nueves y triángulo de PascalDokument2 SeitenEjercicios de nueves y triángulo de PascalHenry Florián100% (1)

- Internet Del TodoDokument6 SeitenInternet Del TodoHenry FloriánNoch keine Bewertungen

- 9 Maneras Como Satanás AtacaDokument1 Seite9 Maneras Como Satanás AtacaHenry FloriánNoch keine Bewertungen

- Perfiles de ProfesionalDokument2 SeitenPerfiles de ProfesionalHenry FloriánNoch keine Bewertungen

- Dispositivos de SeguridadDokument16 SeitenDispositivos de SeguridadHenry FloriánNoch keine Bewertungen

- 20 Poemas de Amor Románticos para EnamorarDokument29 Seiten20 Poemas de Amor Románticos para EnamorarFrancisco Polo MariñosNoch keine Bewertungen

- Cableado EstructuradoDokument1 SeiteCableado EstructuradoHenry FloriánNoch keine Bewertungen

- Ficha de ProgramaciónDokument1 SeiteFicha de ProgramaciónHenry FloriánNoch keine Bewertungen

- Diagrama de Data CenterDokument2 SeitenDiagrama de Data CenterHenry FloriánNoch keine Bewertungen

- Ciudadana FelizDokument9 SeitenCiudadana FelizHenry FloriánNoch keine Bewertungen

- PoemaDokument1 SeitePoemaHenry FloriánNoch keine Bewertungen

- El Caerle Bien A La Gente Esta Íntimamente Es Aquel Que Va Tomado de La Mano de DiosDokument1 SeiteEl Caerle Bien A La Gente Esta Íntimamente Es Aquel Que Va Tomado de La Mano de DiosHenry FloriánNoch keine Bewertungen

- Reto 365Dokument5 SeitenReto 365Henry FloriánNoch keine Bewertungen

- TiedCOMM BCM: software para gestión de expedientes y controles administrativosDokument5 SeitenTiedCOMM BCM: software para gestión de expedientes y controles administrativosHenry FloriánNoch keine Bewertungen

- La OraciónDokument1 SeiteLa OraciónHenry FloriánNoch keine Bewertungen

- PERDÓNDokument4 SeitenPERDÓNHenry FloriánNoch keine Bewertungen

- Chapín de CorazónDokument1 SeiteChapín de CorazónHenry Florián67% (3)

- Textos CampDokument3 SeitenTextos CampHenry FloriánNoch keine Bewertungen

- FacturaciónDokument3 SeitenFacturaciónHenry FloriánNoch keine Bewertungen

- Aspectos A CalificarDokument1 SeiteAspectos A CalificarHenry FloriánNoch keine Bewertungen

- LibertadDokument15 SeitenLibertadHenry FloriánNoch keine Bewertungen

- Carta LaboralDokument1 SeiteCarta LaboralHenry FloriánNoch keine Bewertungen

- Frases de La SaludDokument4 SeitenFrases de La SaludHenry FloriánNoch keine Bewertungen

- Quién InventóDokument8 SeitenQuién InventóHenry FloriánNoch keine Bewertungen

- Variables y ConstantesDokument19 SeitenVariables y ConstantesRomi KatNoch keine Bewertungen

- Diagrama ER HospitalDokument9 SeitenDiagrama ER HospitalVictor FraideNoch keine Bewertungen

- PIC16F877 Con MikroCDokument160 SeitenPIC16F877 Con MikroCErick Zepeda CamposNoch keine Bewertungen

- Guia 1 - ASP UdbDokument20 SeitenGuia 1 - ASP UdbManuelNoch keine Bewertungen

- Linux ExamenesDokument40 SeitenLinux ExamenesJuanDiaz71% (45)

- Ejemplo VFP Accesando SQLite Con ODBCDokument6 SeitenEjemplo VFP Accesando SQLite Con ODBCJesúsHernánCanoMartínezNoch keine Bewertungen

- ¡Lista de Códigos Secretos Más Completa de Samsung Galaxy!Dokument13 Seiten¡Lista de Códigos Secretos Más Completa de Samsung Galaxy!Geo Morales100% (1)

- Alfabeto en Código BinarioDokument2 SeitenAlfabeto en Código BinarioEricks SuarezNoch keine Bewertungen

- Acceso A Discos en Lenguaje EnsambladorDokument6 SeitenAcceso A Discos en Lenguaje EnsambladorJuanScNoch keine Bewertungen

- Gestión centralizada alarmas MM8000Dokument15 SeitenGestión centralizada alarmas MM8000Leon JuanNoch keine Bewertungen

- 1.3 Diseño de Interfases Visuales LISTODokument9 Seiten1.3 Diseño de Interfases Visuales LISTOluisNoch keine Bewertungen

- Sistemas Operativos PrivativosDokument12 SeitenSistemas Operativos PrivativosFredy Lopez DextreNoch keine Bewertungen

- PL PGSQLDokument15 SeitenPL PGSQLGuillermoAlmanzaNoch keine Bewertungen

- Unidad 6 Base de DatosDokument28 SeitenUnidad 6 Base de DatosRully Pech FigueroaNoch keine Bewertungen

- Automatas Unidad 2Dokument28 SeitenAutomatas Unidad 2Luis CadenasNoch keine Bewertungen

- Prueba de Computación C-1Dokument4 SeitenPrueba de Computación C-1Rodrigo Vargas Pérez100% (3)

- Universidad Nacional Abierta Vicerrectorado Académico Área IngenieríaDokument5 SeitenUniversidad Nacional Abierta Vicerrectorado Académico Área IngenieríaJoseph LainoNoch keine Bewertungen

- Curso de SQLDokument87 SeitenCurso de SQLChristian VargasNoch keine Bewertungen

- MODBUSDokument1 SeiteMODBUSRichard Rojas LduNoch keine Bewertungen

- Mindmeister PDFDokument8 SeitenMindmeister PDFAntonio Ayala RamosNoch keine Bewertungen

- ASCII_caracter_enteroDokument7 SeitenASCII_caracter_enteroGabriel WardNoch keine Bewertungen

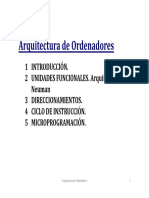

- Arquitectura de OrdenadoresDokument18 SeitenArquitectura de Ordenadoresjuanchopro 00100% (1)

- TOLVA VIBRATORIA PARA CAPILAR TodoDokument9 SeitenTOLVA VIBRATORIA PARA CAPILAR TodoRicardo Tomas Muskus MuskusNoch keine Bewertungen

- Aplicativo móvil UnipanamericanaDokument2 SeitenAplicativo móvil UnipanamericanaGamilo CubillosNoch keine Bewertungen

- App EmpresaDokument14 SeitenApp EmpresaRamon Carrasquel50% (2)

- Hypermedia HG1600 H323 configuraciónDokument12 SeitenHypermedia HG1600 H323 configuracióncastilloneyra.carlosNoch keine Bewertungen

- Piano 1Dokument28 SeitenPiano 1luipmejiaNoch keine Bewertungen

- AprendiendoOOoBasic 2Dokument640 SeitenAprendiendoOOoBasic 2ffergomNoch keine Bewertungen

- Colección de Problemas de POODokument56 SeitenColección de Problemas de POOBigfish781 Rafael PLNoch keine Bewertungen

- Inf143 PDFDokument2 SeitenInf143 PDFMarcelo SalasNoch keine Bewertungen