Beruflich Dokumente

Kultur Dokumente

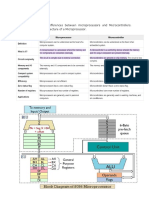

Convert fixed-point expression to CSD and draw RTL diagram

Hochgeladen von

mtkhusro92Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Convert fixed-point expression to CSD and draw RTL diagram

Hochgeladen von

mtkhusro92Copyright:

Verfügbare Formate

Exercise 6.

1

Convert the following expression into its equivalent 8 bit xed point representation:

[] = 0.231[] +0.396[ 1] +0.1111[ 5]

Further convert the xed point constants into their respective CSD representations. Consider

x[n] is an 8-bit input in Q1.7 format. Draw an RTL diagram to represent your design. Each

multiplication should be implemented as a CSD multiplier. Consider only the four most

signicant non zero bits in your CSD representation.

Exercise 6.6

Compute the dot product of two vectors A and x, where A is a vector of constants and x is a

vector of variable data with 4 bit elements. The coefcients of A are:

0

= 13,

1

= 11,

2

= 11,

3

= 13

Use symmetry of the coefcients to optimize the DA based architecture. Test the design for

the following:

= [ 3 13 11 3 ]

Exercise 7.3

Retime the D FG of Figure 7 .39. Move the two se t of registers at the input to break the

critical path of the digital logic. Each computational node also depicts the combinational

time delay of the node in the logic.

Exercise 7.4

Identify all the loops in the DFG of Figure 7.40, and compute the critical path delay assuming

the combinational delays of the adder and the multiplier are 4 and 8 tu, respectively. Compute

the IPB of the graph. Apply the node transfer theorem to move the algorithmic registers for

reducing the critical path and achieving the IPB.

Exercise 8.4

Unfold the second order IIR lter in the TDF structure of Figure 8.5, by a factor of 3. Identify

loops in the unfolded structures and compute their IPBs assuming multiplication and addition

take 3 and 2 time units, respectively.

Exercise 8.7

Fold the architecture of Figure 8.20 by a factor of 4. Find an appropriate folding set. Draw

the folded architecture and write RTL Verilog code of the original and unfolded designs.

Exercise 10.7

Design a micro program state machine that supports the following instruction set:

&

&

&

&

&

&

== )

(

> )

R1 to R5 are 8-bit registers. A branch address or subroutine address can be written in R5 using

a load instruction. As given in the instruction set, jump and subroutine instructions are

developed to use the contents of R 5 as address of the next instruction. The conditions are

based on the content of R4. Draw the RTL diagram of the datapath and micro programmed

state machine. Show all the control signals. Specify the instruction format and size.

Das könnte Ihnen auch gefallen

- Architecture-Aware Optimization Strategies in Real-time Image ProcessingVon EverandArchitecture-Aware Optimization Strategies in Real-time Image ProcessingNoch keine Bewertungen

- DCD QB Dec 2023 StudentDokument7 SeitenDCD QB Dec 2023 StudentPranav VasudevNoch keine Bewertungen

- Data Transfer and Arithmetic InstructionsDokument6 SeitenData Transfer and Arithmetic InstructionsAkshaya ThirumalairajNoch keine Bewertungen

- DLD GTU Question Bank: Chapter-1 Binary SystemDokument129 SeitenDLD GTU Question Bank: Chapter-1 Binary Systemnirav34Noch keine Bewertungen

- Exercises Lg1 Lg6Dokument4 SeitenExercises Lg1 Lg6Helga PravinNoch keine Bewertungen

- DLD GTU Question Bank: Chapter-1 Binary SystemDokument5 SeitenDLD GTU Question Bank: Chapter-1 Binary Systemnirav34Noch keine Bewertungen

- Caassgnsem 1Dokument12 SeitenCaassgnsem 1Sunil GawaskerNoch keine Bewertungen

- A Parallel IEEE P754 Decimal Floating-Point MultiplierDokument8 SeitenA Parallel IEEE P754 Decimal Floating-Point MultiplierMd RasheedNoch keine Bewertungen

- CA Classes-111-115Dokument5 SeitenCA Classes-111-115SrinivasaRaoNoch keine Bewertungen

- Ecl202 - Digital Circuits: Exercise No.4Dokument2 SeitenEcl202 - Digital Circuits: Exercise No.4Shubham ChomalNoch keine Bewertungen

- SP Question BankDokument6 SeitenSP Question BankVinaySharmaNoch keine Bewertungen

- Improved Design of High-Performance Parallel Decimal MultipliersDokument15 SeitenImproved Design of High-Performance Parallel Decimal MultipliersMathew GeorgeNoch keine Bewertungen

- Exp 8 - Array - Multiplier - CADDLABDokument7 SeitenExp 8 - Array - Multiplier - CADDLABSushant R NaikNoch keine Bewertungen

- Experiment-10 4-Digit Multiplexed Seven Segment Display: BjectiveDokument2 SeitenExperiment-10 4-Digit Multiplexed Seven Segment Display: BjectiveUmair HameedNoch keine Bewertungen

- DLDM Question BankDokument8 SeitenDLDM Question BankMayur PatilNoch keine Bewertungen

- Co ImpDokument7 SeitenCo ImpG09Deviprasad N shettyNoch keine Bewertungen

- AE2406 Lab ManualDokument73 SeitenAE2406 Lab ManualSathya NarayananNoch keine Bewertungen

- QB - 22ADS35 (Python For Data Science)Dokument6 SeitenQB - 22ADS35 (Python For Data Science)Arvind ASNoch keine Bewertungen

- Manage-Implementation of Floating - Bhagyashree HardiyaDokument6 SeitenManage-Implementation of Floating - Bhagyashree HardiyaBESTJournalsNoch keine Bewertungen

- Assignment 1 - CSE211 RGDokument4 SeitenAssignment 1 - CSE211 RGSurya TyagiNoch keine Bewertungen

- Question Bank: Ec6302 Digital ElectronicsDokument14 SeitenQuestion Bank: Ec6302 Digital ElectronicsBarry SmithNoch keine Bewertungen

- Floating Point ArithDokument8 SeitenFloating Point ArithVishnupriya Akinapelli100% (1)

- COA Question BankDokument7 SeitenCOA Question BankAnkit NandyNoch keine Bewertungen

- EE 2174 Lab 9 NewDokument6 SeitenEE 2174 Lab 9 NewnotdrphilNoch keine Bewertungen

- HW/SW Co-Design For Soc With Vivado HLS: Example 6-1 Serial AdditionDokument9 SeitenHW/SW Co-Design For Soc With Vivado HLS: Example 6-1 Serial AdditionHamdan AbdellatefNoch keine Bewertungen

- VLSI Implementation of RSA Encryption System Using AncientDokument5 SeitenVLSI Implementation of RSA Encryption System Using AncientAbhishek GuptaNoch keine Bewertungen

- AE2406 Lab ManualDokument73 SeitenAE2406 Lab ManualPrabha Karan100% (1)

- DSP Unit 1 To 5 QBDokument12 SeitenDSP Unit 1 To 5 QBSamuel WhiteNoch keine Bewertungen

- CSE 211 Online Assignment 1 SolutionsDokument4 SeitenCSE 211 Online Assignment 1 SolutionsDeepak VishwakarmaNoch keine Bewertungen

- e-PG Pathshala: Logical Operators, Data Conversion and Serialization in Embedded CDokument9 Seitene-PG Pathshala: Logical Operators, Data Conversion and Serialization in Embedded C2019-EE-35 Hafiz NoumanNoch keine Bewertungen

- Unit IIDokument1 SeiteUnit IIRajkumar ArunachalamNoch keine Bewertungen

- Questions Combinational CircuitDokument2 SeitenQuestions Combinational CircuitVigneswaran VigneshNoch keine Bewertungen

- JNTUK Computer Organization Nov 2015 Question PaperDokument4 SeitenJNTUK Computer Organization Nov 2015 Question PaperTSRKNoch keine Bewertungen

- COA Question Bank-2Dokument2 SeitenCOA Question Bank-2itzzsandeshNoch keine Bewertungen

- CS1203 - SYSTEM SOFTWARE UNIT IDokument17 SeitenCS1203 - SYSTEM SOFTWARE UNIT IGeetha ParthibanNoch keine Bewertungen

- Department of EceDokument8 SeitenDepartment of Ecerajendr_46Noch keine Bewertungen

- University Solved Answers Unit 1 SS (System Software Notes)Dokument12 SeitenUniversity Solved Answers Unit 1 SS (System Software Notes)Vaishnavi Rave100% (1)

- FinalprojectDokument12 SeitenFinalprojectapi-490672851Noch keine Bewertungen

- Annauniv 5thsem Sytsemsoftware Students CornersDokument21 SeitenAnnauniv 5thsem Sytsemsoftware Students CornersstudentscornersNoch keine Bewertungen

- FAQs - CS1202 Digital Principles and System DesignDokument13 SeitenFAQs - CS1202 Digital Principles and System DesignsridharanchandranNoch keine Bewertungen

- Model MCDokument2 SeitenModel MCAkilen MahalingamNoch keine Bewertungen

- 4-Input Decimal Adder Using 90 NM CMOS Technology: Meena Aggarwal, Aastha Agarwal, MR - Rajesh MehraDokument4 Seiten4-Input Decimal Adder Using 90 NM CMOS Technology: Meena Aggarwal, Aastha Agarwal, MR - Rajesh MehraIOSRJEN : hard copy, certificates, Call for Papers 2013, publishing of journalNoch keine Bewertungen

- Lab AssignmentDokument1 SeiteLab AssignmentParas BhardwajNoch keine Bewertungen

- Laboratory Exercise 10: An Enhanced ProcessorDokument4 SeitenLaboratory Exercise 10: An Enhanced ProcessorKhánh ConNoch keine Bewertungen

- Co QBDokument6 SeitenCo QBHarris ChikunyaNoch keine Bewertungen

- (SS) System Software Viva Question and AnswersDokument15 Seiten(SS) System Software Viva Question and AnswersVenkatesh NaiduNoch keine Bewertungen

- Updates on university exams, courses and admissionsDokument2 SeitenUpdates on university exams, courses and admissionssameeksha chiguruNoch keine Bewertungen

- Microprocessor & Its Interfacing - Ic-403Dokument3 SeitenMicroprocessor & Its Interfacing - Ic-403Shreemaye DasNoch keine Bewertungen

- CS1203-SYSTEM SOFTWAREDokument31 SeitenCS1203-SYSTEM SOFTWAREMohammed HashimNoch keine Bewertungen

- Week5Dokument4 SeitenWeek5Hoàng Huy NguyễnNoch keine Bewertungen

- Rajalakshmi Engineering College: CS2308 - SS Lab VVQ Unit I-IntroductionDokument17 SeitenRajalakshmi Engineering College: CS2308 - SS Lab VVQ Unit I-IntroductionssarvinthNoch keine Bewertungen

- PDF 1Dokument17 SeitenPDF 1Nivedita Acharyya 2035Noch keine Bewertungen

- Antilogarithmic ConverterDokument13 SeitenAntilogarithmic ConverterJohn LeonsNoch keine Bewertungen

- cs2304 System Software 2 Marks and 16 Marks With AnswerDokument18 Seitencs2304 System Software 2 Marks and 16 Marks With Answermanojkumar024Noch keine Bewertungen

- CaseDokument25 SeitenCaseDeepanshu Midha5140Noch keine Bewertungen

- Lab6 VerilogDokument6 SeitenLab6 VerilogVận MặcNoch keine Bewertungen

- Economic and Financial Modelling with EViews: A Guide for Students and ProfessionalsVon EverandEconomic and Financial Modelling with EViews: A Guide for Students and ProfessionalsNoch keine Bewertungen

- Linear Programming and Resource Allocation ModelingVon EverandLinear Programming and Resource Allocation ModelingNoch keine Bewertungen

- Dm4000series Spec SheetDokument4 SeitenDm4000series Spec Sheetmtkhusro92Noch keine Bewertungen

- PBXDokument4 SeitenPBXmtkhusro92Noch keine Bewertungen

- Muhammad Rafay Abdullah Roll# 038: Lab# 5 Submitted To: Sir FaheemDokument7 SeitenMuhammad Rafay Abdullah Roll# 038: Lab# 5 Submitted To: Sir Faheemmtkhusro92Noch keine Bewertungen

- Sample Paper For DSDDokument2 SeitenSample Paper For DSDmtkhusro92Noch keine Bewertungen

- Python Based Quality Assurance Software ToolDokument16 SeitenPython Based Quality Assurance Software Toolmtkhusro92Noch keine Bewertungen

- Communication Systems Lec 1Dokument30 SeitenCommunication Systems Lec 1mtkhusro92Noch keine Bewertungen

- Engineering Drawing SolutionsDokument20 SeitenEngineering Drawing Solutionsmtkhusro92Noch keine Bewertungen

- Arthur C. Clarke - Childhood's EndDokument4 SeitenArthur C. Clarke - Childhood's EndMantuanBard67% (3)

- Network Programming Lecture 1 IntroductionDokument11 SeitenNetwork Programming Lecture 1 Introductionmtkhusro92Noch keine Bewertungen

- DSD Practice ExamDokument1 SeiteDSD Practice Exammtkhusro92Noch keine Bewertungen

- Mini Presentation SwotDokument20 SeitenMini Presentation Swotmtkhusro92Noch keine Bewertungen

- IP Data NetworkingDokument144 SeitenIP Data Networkingmtkhusro92Noch keine Bewertungen

- Mustanad Roohani NuskhayDokument145 SeitenMustanad Roohani Nuskhaynkarpak88% (8)

- Role of Media NewDokument4 SeitenRole of Media Newmtkhusro92Noch keine Bewertungen

- Hayat e QadirDokument137 SeitenHayat e Qadirmtkhusro92Noch keine Bewertungen

- Revelation of MysteryDokument487 SeitenRevelation of MysteryEnkidu_100% (2)

- Masha'Ikh of ChishtDokument140 SeitenMasha'Ikh of Chishtibwaheemi100% (2)

- The 14 Harms of Casting Evil GlancesDokument23 SeitenThe 14 Harms of Casting Evil Glancesjunaidiqbal100% (3)

- Life and Works of Allamah Anwar Shah Kashmiri by Shaykh Yunoos OsmanDokument176 SeitenLife and Works of Allamah Anwar Shah Kashmiri by Shaykh Yunoos Osmanmtkhusro92Noch keine Bewertungen

- Dinar & Dirham - Islam and The Future of Money - Shaikh Dr. Imran N. HoseinDokument49 SeitenDinar & Dirham - Islam and The Future of Money - Shaikh Dr. Imran N. Hoseinm.suh100% (4)

- 40 Hadith Islamic PersonalityDokument21 Seiten40 Hadith Islamic PersonalityISLAMICULTURE100% (1)

- Artificial Intelligence Learning Roadmap - Step-By-Step Guide 2023Dokument9 SeitenArtificial Intelligence Learning Roadmap - Step-By-Step Guide 2023Vincent O. AbuNoch keine Bewertungen

- Gvahim Assembly BookDokument318 SeitenGvahim Assembly Bookאראל נחוםNoch keine Bewertungen

- AWT Event Handling ExplainedDokument8 SeitenAWT Event Handling ExplainedrutchelinesaritaNoch keine Bewertungen

- Transportation Problem 2Dokument11 SeitenTransportation Problem 2Chasity WrightNoch keine Bewertungen

- Opentbs Demo: Merge Data With A ChartDokument4 SeitenOpentbs Demo: Merge Data With A ChartApepIndraSaputraNoch keine Bewertungen

- Module 5Dokument16 SeitenModule 5SANGRAM SINGH 1CD20IS093Noch keine Bewertungen

- This Study Resource Was: Database Programming With PL/SQL 9-3: Practice ActivitiesDokument2 SeitenThis Study Resource Was: Database Programming With PL/SQL 9-3: Practice Activitiesimhereforanswers2Noch keine Bewertungen

- Embedded SystemDokument9 SeitenEmbedded SystemKathir RajNoch keine Bewertungen

- Lotus Domino and Visual Basic PDFDokument164 SeitenLotus Domino and Visual Basic PDFmarcin823100% (1)

- Activemq Broker Camel Connector Jms Client 5.15.8 5.15.9 5.15.10 5.15.12Dokument4 SeitenActivemq Broker Camel Connector Jms Client 5.15.8 5.15.9 5.15.10 5.15.12MassiNoch keine Bewertungen

- BCS304-DSA Notes M-3Dokument61 SeitenBCS304-DSA Notes M-3sagar2024kNoch keine Bewertungen

- Addmrpt 1 36557 36558Dokument5 SeitenAddmrpt 1 36557 36558Anonymous ZGcs7MwsLNoch keine Bewertungen

- Become A Reliable Web Programmer: Menjadi Programmer Handal Era KekinianDokument48 SeitenBecome A Reliable Web Programmer: Menjadi Programmer Handal Era KekinianGie ZwskyNoch keine Bewertungen

- Automation: Project EngineeringDokument13 SeitenAutomation: Project EngineeringMilan SjausNoch keine Bewertungen

- KPR Institute of Engineering and Technology: COIMBATORE - 641 407Dokument56 SeitenKPR Institute of Engineering and Technology: COIMBATORE - 641 407Karthic SundaramNoch keine Bewertungen

- Sorting Arrays in VBADokument2 SeitenSorting Arrays in VBAvaskoreNoch keine Bewertungen

- Verilator and Systemperl: Wilson SnyderDokument14 SeitenVerilator and Systemperl: Wilson Snydershanu kumarNoch keine Bewertungen

- Data Engineering With Databricks DaDokument232 SeitenData Engineering With Databricks Davitlesh.sfNoch keine Bewertungen

- ARM Instruction Set OverviewDokument60 SeitenARM Instruction Set OverviewDevid gakharNoch keine Bewertungen

- Sub Queries Group 2Dokument21 SeitenSub Queries Group 2bingbongsxdNoch keine Bewertungen

- Bash Programming GuideDokument69 SeitenBash Programming Guidekalligadu_143Noch keine Bewertungen

- CodeDokument5 SeitenCodeapi-637679575Noch keine Bewertungen

- Laravel Development Using Phpstorm: Prerequisites (Plugin Installation and Configuration)Dokument18 SeitenLaravel Development Using Phpstorm: Prerequisites (Plugin Installation and Configuration)Mashe1985Noch keine Bewertungen

- Userguidev6 US R 2018 12Dokument122 SeitenUserguidev6 US R 2018 12Achraf SalimNoch keine Bewertungen

- Creating An Action With A BADI Schedule ConditionDokument6 SeitenCreating An Action With A BADI Schedule ConditionlyquocnguyenNoch keine Bewertungen

- Python Optimization Modeling Objects (Pyomo)Dokument17 SeitenPython Optimization Modeling Objects (Pyomo)arteepu4Noch keine Bewertungen

- A Schemer's Introduction to Monads in Accumulator-Passing StyleDokument5 SeitenA Schemer's Introduction to Monads in Accumulator-Passing StyleDavid IrelandNoch keine Bewertungen

- Komal - Final Project ReportDokument20 SeitenKomal - Final Project ReportKomal DeswalNoch keine Bewertungen

- Common Syllabus For Bachelor in Computer Applications (Bca) PreambleDokument42 SeitenCommon Syllabus For Bachelor in Computer Applications (Bca) PreambleTiktok IndiaNoch keine Bewertungen

- Sequential Function ChartDokument26 SeitenSequential Function ChartOswaldo Rojas GoveaNoch keine Bewertungen