Beruflich Dokumente

Kultur Dokumente

05 HW

Hochgeladen von

SandipChowdhury0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

17 Ansichten3 Seitenca

Originaltitel

05_HW

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenca

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

17 Ansichten3 Seiten05 HW

Hochgeladen von

SandipChowdhuryca

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 3

CSE 30321 Computer Architecture I Fall 2011

Homework 05 Datapath Design 65 points

Assigned: September 27, 2011 Due: October 4, 2011

Problem 1: (10 points)

Background:

Here, youll need to augment the MIPS datapath discussed in class to support a new instruction. When

you decide to add or support a new instruction, this will most often require changes to datapath

hardware, as well as to the finite state machine (FSM) / control logic that controls the datapath

components in a given clock cycle. Ideally, youd like an instruction to (i) improve execution time (by

lowering CPI, improving clock rate, or reducing instruction count), (ii) improve functionality with respect

to the baseline datapath, etc. with as little additional hardware (multiplexors, wires, etc.) and control

signal overhead as possible.

In this problem, we want to augment the existing, multi-cycle MIPS datapath and FSM that we have

discussed in class (see link on course website) to support a load upper immediate (lui) instruction.

For lui, the immediate value is shifted left 16 bits and stored in a register. The lower 16 bits are 0s.

- The instruction syntax is: lui $t, imm

- Thus, $t ! (imm << 16)

- The instruction encoding is:

Bits 31-26 Bits 25-21 Bits 20-16 Bits 15-0

Opcode Unused Destination Immediate value

001111 XXXXX TTTTT iiii iiii iiii iiii

This instruction is not currently supported by the single cycle or multi-cycle MIPS datapath that was

derived and discussed in class which instead focused on a subset of commonly used instructions. In

actuality, the MIPS datapath would contain hardware to facilitate the execution of 100s of instructions.

The lui instruction allows you to place constant values that are greater than 16 bits into a register.

For example, assume that you want to load the number shown below into $4:

o 0000 1000 0000 0000 0000 0000 0000 0001 (binary)

o 134,217,729

10

(base 10)

In this instance, you could NOT do something like:

o addi, $4, $0, 134,217,729

10

o (as seen above, 134,217,729

10

cannot be represented with just 16 bits)

However, this could be accomplished with the following sequence of instructions:

lui $4, 2048

10

# 2048 is the decimal representation of 0000 1000 0000 0000

# Thus, $4 = 0000 1000 0000 0000 0000 0000 0000 0000

ori $4, $4, 1

10

# The or-immediate instruction will be used to set the lower order bits

Question:

For the MIPS multi-cycle datapath, discuss/show the necessary modifications to the datapath

and finite state machine to perform a lui in 3 clock cycles

Note that for your answer, you do not have to update all other states in the finite state machine

if you add new control signals

Your answer should be supported by augmented FSM and datapath diagrams (available online)

Problem 2: (10 points)

Background:

In lecture, we did an in-class example where you were asked to implement a branch-if-less-than

instruction e.g. blt $s1, $s2, Label. There is no explicit branch-if-less-than or branch-if-greater than

instruction in MIPS, and two separate instructions were needed to implement branch-if-less-than

functionality.

The solution presented in class was to use the set-on-less-than instruction:

slt $t0, $s1, $s2 # $t0 ! 0 if $s1 ! $s2

# $t0 ! 1 if $s1 < $s2

Then, branch-if-less-than functionality could be implemented as follows:

slt $1, $s1, $s2

bne $1, $0, label

Question:

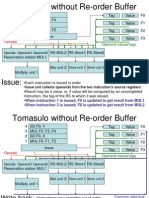

In this question, you are asked to explain how the MIPS multi-cycle datapath and finite state machine

would need to be modified in order to implement an explicit blt (or bgt) instruction. Whether or not the

data in one register is less than or greater than the data in another will be determined by examining the

most significant bit of the ALUOut register after a comparison calculation is performed. (Thus, if the

most significant bit of ALUOut is a 1, the result of the comparison is negative. If the bit is a 0, the result

of the comparison is positive.)

Note explicit modifications of the datapath and finite state machine diagrams are not required for this

problem (although you can use them if you would like). However, please explain why you made the

design decisions that you made and your rationale for making them.

Remember that a branch address is calculated in clock cycle #2 per Lecture 11!

Problem 3: (10 points)

Background:

The purpose of this question is to quantify performance improvements to the MIPS multi-cycle datapath

to determine what design improvement makes the most sense from the standpoint of execution time.

Question:

2 important parameters control the performance of a processor: cycle time and cycles per instruction.

1. Some designers prefer to increase the processor frequency at the expense of larger CPIs.

2. Other designers follow a different school of thought and try to reduce CPI at the expense of

lower clock frequencies.

Qualitatively, explain how the processor datapaths for Options 1 and 2 might differ assuming the same

ISA i.e. both datapaths would execute the same ADD instruction, the ADD instruction would have the

same 32-bit encoding given each datapath, etc.

Problem 4: (35 points)

Part A: (25 points)

Below, Ive included representative instruction counts to do an MP3 encoding and decoding. (Data was

obtained from the SimpleScalar tool used in Lab 01.) You will use this data to investigate possible

changes to the MIPS datapath that may or may not improve benchmark performance. (Note that while

this data was taken from simulations using an ARM core, we will assume that the instruction mixes

would be relatively similar for the MIPS datapath too especially as both the MIPS and ARM ISAs are

RISC-like.)

MAD:

LAME:

The following design options are possible:

D1: The multicycle MIPS datapath that we have worked with in class (see handout) with a 4 GHz

clock.

D2: A machine with a multicycle datapath like D1, except that register updates are done in the same

clock cycle as a memory read or ALU operation. (Thus, in the FSM of Problem 1, states 6 and 7

and states 3 and 4 are combined.) This machine has a 3.1 GHz clock, as the register update

increases the length of the critical path.

D3: A machine like D3 except that effective address calculations are done in the same clock cycle

as a memory access. Thus, states 2, 3 and 4 can be combined, as can 2 and 5, as well as 6

and 7. This machine has a 2.8 GHz clock because of the long cycle created by combining the

address calculation and memory access.

- What design is best if you only want to decode MP3s?

- What design is best if you only want to encode MP3s?

- What design is best if you want to do both (most likely)? Why do you think this is?

Part B: (10 points)

For Designs 1, 2, and 3, what is the maximum amount of time that you have to do the logic associated

with a given clock cycle before the data is latched? (This question reviews the concept of a clock

cycle.)

Instruction Type Instruction Count Base CPI

ALU 1,809,493,063 4

Store 177,074,647 4

Load 505,117,744 5

Branch 89,895,551 3

Instruction Type Instruction Count Base CPI

ALU 1,074,420,032 4

Store 214,038,157 4

Load 631,988,109 5

Branch 47,775,211 3

Das könnte Ihnen auch gefallen

- HW 05Dokument6 SeitenHW 05samadNoch keine Bewertungen

- Assignment1 4Dokument5 SeitenAssignment1 4Munim DheemanNoch keine Bewertungen

- Instructions: Csce 212: Final Exam Spring 2009Dokument5 SeitenInstructions: Csce 212: Final Exam Spring 2009NapsterNoch keine Bewertungen

- CENG400 Midterm Fall 2015Dokument10 SeitenCENG400 Midterm Fall 2015Mohamad IssaNoch keine Bewertungen

- Cse3666 MT1S F12Dokument5 SeitenCse3666 MT1S F12dimpal_3221Noch keine Bewertungen

- COMPUTER ORGANISATION (LONG ANSWERS 2 PM)Dokument5 SeitenCOMPUTER ORGANISATION (LONG ANSWERS 2 PM)spacekiller98Noch keine Bewertungen

- Practice Final ExamDokument3 SeitenPractice Final ExamThành ThảoNoch keine Bewertungen

- CS122: Computer Architecture & Organization: Semester I, 2011Dokument27 SeitenCS122: Computer Architecture & Organization: Semester I, 2011Tarunbir BangaNoch keine Bewertungen

- BaiTap Chuong123Dokument19 SeitenBaiTap Chuong123Nguyễn Ngọc TúNoch keine Bewertungen

- PracticeProblems COA8eDokument40 SeitenPracticeProblems COA8eAnousith PhompidaNoch keine Bewertungen

- Computer Architecture Lecture Notes Spring 2005 Dr. Michael P. Frank Competency Area 3: Programming and Coding MethodsDokument68 SeitenComputer Architecture Lecture Notes Spring 2005 Dr. Michael P. Frank Competency Area 3: Programming and Coding MethodsNapsterNoch keine Bewertungen

- On How To Improve The Initial Load by Row Id ApproachDokument12 SeitenOn How To Improve The Initial Load by Row Id ApproachSyed AliNoch keine Bewertungen

- Your Name:: Final ExamDokument9 SeitenYour Name:: Final ExamDaniel EcheverriaNoch keine Bewertungen

- Assignment: - 4Dokument7 SeitenAssignment: - 4nikita_gupta3Noch keine Bewertungen

- Speed of Computer SystemsDokument4 SeitenSpeed of Computer SystemsVíctor DávilaNoch keine Bewertungen

- EE380 Spring 2004 Sample Final Exam: Direct Connection (Aka, Fully Connected) Networ Ks Offer Ver y Good Latency andDokument7 SeitenEE380 Spring 2004 Sample Final Exam: Direct Connection (Aka, Fully Connected) Networ Ks Offer Ver y Good Latency andJaxzen42Noch keine Bewertungen

- Problem Project 1Dokument4 SeitenProblem Project 1Nandeesh GowdaNoch keine Bewertungen

- Cyan 2800398239029h09fn0ivj0vcjb0Dokument16 SeitenCyan 2800398239029h09fn0ivj0vcjb0Anonymous zWBss8LKNoch keine Bewertungen

- Computer Organization & Design The Hardware/Software Interface, 2nd Edition Patterson & HennessyDokument118 SeitenComputer Organization & Design The Hardware/Software Interface, 2nd Edition Patterson & HennessyMr.Puppy80% (5)

- Updated Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. LipastiDokument8 SeitenUpdated Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. LipastitargetiesNoch keine Bewertungen

- Full Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipasti PDFDokument18 SeitenFull Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipasti PDFtargetiesNoch keine Bewertungen

- Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. LipastiDokument11 SeitenSolution Manual For Modern Processor Design by John Paul Shen and Mikko H. LipastitargetiesNoch keine Bewertungen

- Full Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. LipastiDokument27 SeitenFull Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipastitargeties50% (2)

- Minimizing Power Consumption of Embedded System Processors Through Instruction-Set CompressionDokument4 SeitenMinimizing Power Consumption of Embedded System Processors Through Instruction-Set CompressionMohamed HacamNoch keine Bewertungen

- hw1 11 12 13 16 31 12 33 PDFDokument7 Seitenhw1 11 12 13 16 31 12 33 PDFNguyễn Thành HiệpNoch keine Bewertungen

- hw1 11 12 13 16 31 12 33 PDFDokument7 Seitenhw1 11 12 13 16 31 12 33 PDFKavya suresh pcNoch keine Bewertungen

- Model Answers Hw1 - Chapter 2 & 3Dokument7 SeitenModel Answers Hw1 - Chapter 2 & 3Kavya suresh pc0% (1)

- Midtermarch 2Dokument9 SeitenMidtermarch 2Ghina BaassiriNoch keine Bewertungen

- Lab Manual 02 Implementation of 8086 Based Data Movement and Arithmetic Instructions Such As ADD, SUB, MOV Using EMU8086Dokument5 SeitenLab Manual 02 Implementation of 8086 Based Data Movement and Arithmetic Instructions Such As ADD, SUB, MOV Using EMU8086Muhammad FaizanNoch keine Bewertungen

- Ovn MainDokument54 SeitenOvn MainAvenir BajraktariNoch keine Bewertungen

- Illinois Exam2 Practice Solfa08Dokument4 SeitenIllinois Exam2 Practice Solfa08bittronicNoch keine Bewertungen

- Computer ArchitectDokument194 SeitenComputer Architectksu2006Noch keine Bewertungen

- Cse-Vii-Advanced Computer Architectures (10cs74) - SolutionDokument111 SeitenCse-Vii-Advanced Computer Architectures (10cs74) - SolutionShinu100% (1)

- Design of 32-Bit Risc Cpu Based On Mips: Journal of Global Research in Computer ScienceDokument5 SeitenDesign of 32-Bit Risc Cpu Based On Mips: Journal of Global Research in Computer ScienceAkanksha Dixit ManodhyaNoch keine Bewertungen

- Ia Iii - QPDokument12 SeitenIa Iii - QPkeerthi3214Noch keine Bewertungen

- Inroduction and Performance AnalysisDokument29 SeitenInroduction and Performance AnalysisUmang AggarwalNoch keine Bewertungen

- HPCA Assignment 1& 2 For Improvement & BacklogDokument3 SeitenHPCA Assignment 1& 2 For Improvement & Backlogdebjeet.mailmeNoch keine Bewertungen

- Project - Behavioral Model: Homework 2 - April 24, 2005Dokument2 SeitenProject - Behavioral Model: Homework 2 - April 24, 2005Shawn SagarNoch keine Bewertungen

- Performance Tips For Large Datasets - Knowledge BaseDokument8 SeitenPerformance Tips For Large Datasets - Knowledge BaserajisgoodNoch keine Bewertungen

- Question Bank For Computer ArchitectureDokument23 SeitenQuestion Bank For Computer ArchitecturesuryaNoch keine Bewertungen

- Assignment Nov 19Dokument7 SeitenAssignment Nov 19CSE ANoch keine Bewertungen

- SAS Programming Guidelines Interview Questions You'll Most Likely Be AskedVon EverandSAS Programming Guidelines Interview Questions You'll Most Likely Be AskedNoch keine Bewertungen

- Performance Chap4Dokument20 SeitenPerformance Chap4Rajesh TiwaryNoch keine Bewertungen

- CSC 424 AssignmentDokument8 SeitenCSC 424 AssignmentBalsesbiz Consults100% (1)

- Tutorial Module 4Dokument9 SeitenTutorial Module 4Neupane Er KrishnaNoch keine Bewertungen

- Assignment: - 4: Part - ADokument9 SeitenAssignment: - 4: Part - Anikita_gupta3Noch keine Bewertungen

- Input Unit: Five Basic Components of Computer SystemDokument9 SeitenInput Unit: Five Basic Components of Computer SystemJefin PaulNoch keine Bewertungen

- 16 Marks Question Bank NewDokument16 Seiten16 Marks Question Bank Newsakthivijayan80Noch keine Bewertungen

- Embedded System Design-NPTEL-NOTESDokument38 SeitenEmbedded System Design-NPTEL-NOTESGulshan Upreti100% (1)

- Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipasti PDFDokument5 SeitenSolution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipasti PDFtargeties0% (1)

- DSP-8 (DSP Processors)Dokument8 SeitenDSP-8 (DSP Processors)Sathish BalaNoch keine Bewertungen

- CSO Cache Memory NumericalsDokument12 SeitenCSO Cache Memory NumericalsHimanshu GuptaNoch keine Bewertungen

- SPRING 2015 CDA 3101 Homework 3: Date-Assigned: Mar 27th, 2015 Due Dates: 11:55pm, April 7th, 2015Dokument5 SeitenSPRING 2015 CDA 3101 Homework 3: Date-Assigned: Mar 27th, 2015 Due Dates: 11:55pm, April 7th, 2015ayylmao kekNoch keine Bewertungen

- C6713 DSP Lab Mannual 2Dokument40 SeitenC6713 DSP Lab Mannual 2dangvuduongNoch keine Bewertungen

- Designing and Tuning High Speed Data Loading - Thomas KejserDokument41 SeitenDesigning and Tuning High Speed Data Loading - Thomas KejserWasis PrionggoNoch keine Bewertungen

- SAS Interview Questions You'll Most Likely Be AskedVon EverandSAS Interview Questions You'll Most Likely Be AskedNoch keine Bewertungen

- GameCube Architecture: Architecture of Consoles: A Practical Analysis, #10Von EverandGameCube Architecture: Architecture of Consoles: A Practical Analysis, #10Noch keine Bewertungen

- Foundation Course for Advanced Computer StudiesVon EverandFoundation Course for Advanced Computer StudiesNoch keine Bewertungen

- 04 PPT 1up PDFDokument30 Seiten04 PPT 1up PDFSandipChowdhuryNoch keine Bewertungen

- MIPS FSM Diagram!: Cycle 1!Dokument1 SeiteMIPS FSM Diagram!: Cycle 1!SandipChowdhuryNoch keine Bewertungen

- MIPS Datapath (With Exception Handling) !Dokument1 SeiteMIPS Datapath (With Exception Handling) !SandipChowdhuryNoch keine Bewertungen

- 05 BoardDokument4 Seiten05 BoardSandipChowdhuryNoch keine Bewertungen

- 03 HWDokument3 Seiten03 HWSandipChowdhuryNoch keine Bewertungen

- 04 PPT 4upDokument8 Seiten04 PPT 4upSandipChowdhuryNoch keine Bewertungen

- 04 BoardDokument10 Seiten04 BoardSandipChowdhuryNoch keine Bewertungen

- 02 HWDokument6 Seiten02 HWSandipChowdhuryNoch keine Bewertungen

- 1 LabDokument10 Seiten1 LabSandipChowdhuryNoch keine Bewertungen

- Lectures 02, 03 Introduction To Stored Programs": Suggested Reading:" HP Chapters 1.1-1.3"Dokument30 SeitenLectures 02, 03 Introduction To Stored Programs": Suggested Reading:" HP Chapters 1.1-1.3"SandipChowdhuryNoch keine Bewertungen

- 02 LabDokument7 Seiten02 LabSandipChowdhuryNoch keine Bewertungen

- 03 LabDokument8 Seiten03 LabSandipChowdhuryNoch keine Bewertungen

- Lectures 02, 03 Introduction To Stored Programs": Suggested Reading:" HP Chapters 1.1-1.3"Dokument30 SeitenLectures 02, 03 Introduction To Stored Programs": Suggested Reading:" HP Chapters 1.1-1.3"SandipChowdhuryNoch keine Bewertungen

- CSE 30321: Computer Architecture I: LogisticsDokument3 SeitenCSE 30321: Computer Architecture I: LogisticsSandipChowdhuryNoch keine Bewertungen

- CSE 30321 - Lecture 02-03 - in Class Example Handout: Discussion - Overview of Stored ProgramsDokument8 SeitenCSE 30321 - Lecture 02-03 - in Class Example Handout: Discussion - Overview of Stored ProgramsSandipChowdhuryNoch keine Bewertungen

- 1Dokument12 Seiten1SandipChowdhuryNoch keine Bewertungen

- Control Unit and Datapath For 3-Instruction Processor!Dokument1 SeiteControl Unit and Datapath For 3-Instruction Processor!SandipChowdhuryNoch keine Bewertungen

- From: Subject: Date: To: Reply-ToDokument1 SeiteFrom: Subject: Date: To: Reply-ToSandipChowdhuryNoch keine Bewertungen

- 1HDokument8 Seiten1HSandipChowdhuryNoch keine Bewertungen

- Comparator PDFDokument24 SeitenComparator PDFBá Anh ĐàoNoch keine Bewertungen

- 8051 At89s52Dokument18 Seiten8051 At89s52Sanjana SinghNoch keine Bewertungen

- This Specification Covers A Range of 2K Bit Serial EEPROM Products, The ST93C56, 56C Specified at 5V 10% and The ST93C57C Specified at 3V To 5.5V. in The Text, Products Are Referred To As ST93C56.Dokument13 SeitenThis Specification Covers A Range of 2K Bit Serial EEPROM Products, The ST93C56, 56C Specified at 5V 10% and The ST93C57C Specified at 3V To 5.5V. in The Text, Products Are Referred To As ST93C56.bylly122001Noch keine Bewertungen

- Embeddedsystem Lecture1Dokument25 SeitenEmbeddedsystem Lecture1Ankita SinghNoch keine Bewertungen

- Tomasulo With Re-Order Buffer-V3Dokument10 SeitenTomasulo With Re-Order Buffer-V3prakash_shrNoch keine Bewertungen

- Design and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolDokument10 SeitenDesign and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolRakeshconclaveNoch keine Bewertungen

- Mcu - r8c27 - Renesas r8c26 r8c27 - Software Manual Rej09b0001 - r8csmDokument298 SeitenMcu - r8c27 - Renesas r8c26 r8c27 - Software Manual Rej09b0001 - r8csmLudwig SchmidtNoch keine Bewertungen

- Book. 2010. Introduction To Embedded Systems Using Ansi C and The Arduino Development EnvironmentDokument275 SeitenBook. 2010. Introduction To Embedded Systems Using Ansi C and The Arduino Development Environmentfrsalazar100% (1)

- Question Paper Computer System Architecture (MC121) - January 2005Dokument14 SeitenQuestion Paper Computer System Architecture (MC121) - January 2005amitukumarNoch keine Bewertungen

- Microprocessor For Bca Bit BeDokument0 SeitenMicroprocessor For Bca Bit Bewww.bhawesh.com.npNoch keine Bewertungen

- Computer GenerationsDokument4 SeitenComputer GenerationsJason YipNoch keine Bewertungen

- The Chip: An Electronic Brain Olawore JeliliDokument8 SeitenThe Chip: An Electronic Brain Olawore JeliliOyeniyi Samuel KehindeNoch keine Bewertungen

- CC Viva QuestionsDokument5 SeitenCC Viva QuestionsSaraah Ghori0% (1)

- Micro PillsDokument33 SeitenMicro PillsAmshala SrikanthNoch keine Bewertungen

- Spacecraft Computer Systems: Colonel John E. KeeseeDokument34 SeitenSpacecraft Computer Systems: Colonel John E. KeeseeErickGarciaNoch keine Bewertungen

- 8085 Microprocessor: Assignment OnDokument45 Seiten8085 Microprocessor: Assignment OntusharbhatiNoch keine Bewertungen

- s7 1500 Compare Table en MnemoDokument71 Seitens7 1500 Compare Table en MnemoVICTORSJNoch keine Bewertungen

- Chapter 6 - Introduction To An Embedded System and ITs Design - Microcontrollers & Embedded SystemsDokument16 SeitenChapter 6 - Introduction To An Embedded System and ITs Design - Microcontrollers & Embedded SystemsAmish VermaNoch keine Bewertungen

- Design and Implementation of Simple As Possible Computer (SAP-1)Dokument51 SeitenDesign and Implementation of Simple As Possible Computer (SAP-1)Miguel San AntonioNoch keine Bewertungen

- Module 5 - Cisc Vs RiscDokument3 SeitenModule 5 - Cisc Vs RiscStefania PopescuNoch keine Bewertungen

- VivA QuestionS MPDokument9 SeitenVivA QuestionS MPG yugandhar srinivasNoch keine Bewertungen

- Computer System Overview (Review) : Operating SystemsDokument50 SeitenComputer System Overview (Review) : Operating SystemsLộc Khang PhúcNoch keine Bewertungen

- 16 Kbit and 8 Kbit Serial SPI Bus EEPROM With High Speed ClockDokument45 Seiten16 Kbit and 8 Kbit Serial SPI Bus EEPROM With High Speed ClockRick CastilloNoch keine Bewertungen

- Lab Manual SPCCDokument62 SeitenLab Manual SPCCenggeng7Noch keine Bewertungen

- Computer FundamentalsDokument29 SeitenComputer FundamentalsJimmy OrajayNoch keine Bewertungen

- An Overview of Virtualization Techniques: Online Simulations and MoreDokument19 SeitenAn Overview of Virtualization Techniques: Online Simulations and MoretqmquocNoch keine Bewertungen

- Pascal/ASM Sec. 1.3Dokument15 SeitenPascal/ASM Sec. 1.3Glenn MerrittNoch keine Bewertungen

- Central Processing Unit (CPU) : TopicDokument6 SeitenCentral Processing Unit (CPU) : TopicGaurav KulkarniNoch keine Bewertungen

- MIPS AssemblyInstruction FormatsDokument5 SeitenMIPS AssemblyInstruction Formatsfeezy1100% (1)

- LPC2138Dokument39 SeitenLPC2138yuvaraja_703Noch keine Bewertungen

- Syslib Rm018 en e (P AInAdv)Dokument56 SeitenSyslib Rm018 en e (P AInAdv)carbono980Noch keine Bewertungen