Beruflich Dokumente

Kultur Dokumente

CS6303

Hochgeladen von

Pushpavalli Mohan0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

26 Ansichten3 Seitenimportant questions

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenimportant questions

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

26 Ansichten3 SeitenCS6303

Hochgeladen von

Pushpavalli Mohanimportant questions

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 3

ST.

JOSEPH COLLEGE OF ENGINEERING

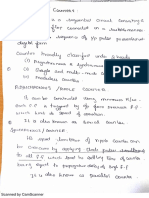

COMPUTER ARCHITECTURE- CS6303

QUESTION BANK

UNIT-3

2 MARKS

1) State the advantages of multiple levels of decoding.

2) Give instruction formats for R type, load or store and branch instructions.

3) State the functions of following control lines.

a)PC Src b)ALU Src c)RegDst d)Mem R

4) Draw the format of jump instruction.

5) State the reasons for not using single cycle implementation.

6) What is the ideal speed-up expected in a pipelined architecture with n stages? Justify

your answer.

7) Define pipelining?

8) Define data hazard?

9) Define control hazard?

10) List the conditions to overcome data hazard?

11) Distinguish between static and dynamic branch prediction approaches?

12) What is meant by hazard in pipelining?

13) Draw the structure of two stage instruction pipeline?

14) What would be the effect, if we increase the number of pipelining stages?

15) What do you mean by out-of order execution?

16) Why is branch prediction algorithm needed?

17) What is meant by speculative execution?

18) What is the role of cache in pipelining?

19) What is imprecise and precise exception?

20) Define data path?

16 MARKS

1) Draw and explain the functional block diagram with control signals for basic

implementation of MIPS subset.

2) Explain the control implementation scheme

i) The ALU Control ii)Designing the main control unit

3) Explain the operation of the data path for an R-type, Load Word, branch, control,

jump instructions in detail.

4) (i)Explain the function of a six segment pipeline and draw a space diagram for a six

segment pipeline showing the time it takes to process eight tasks.

(ii)Discuss the basic concepts of pipelining?

5) (i)Explain pipeline performance in detail

(ii)Explain branch prediction in detail.

6) Explain the concept of pipelined data path and control in detail.

7) What is a data hazard? How do you overcome it? And discuss its side effects.

8) What is instruction hazard? Explain the methods for dealing with the instruction

hazards?

9) Draw and explain the data path to implement fetch and PC increment operations,

arithmetic-logic instructions.

10) Draw and explain the data path segment for load word and store word instructions,

computation of branch target address.

UNIT-4

2MARKS

1) Define parallel processing?

2) Define multiprocessors.

3) Define task-level or process level parallelism.

4) State the basic ways to achieve parallelism.

5) What do you mean by CMPs?

6) What are the limitations to increase clock frequency or processor speed?

7) State the Amdahls law?

8) List four major groups of computers defined by Michael J.Flynn?

9) What is SISD?

10) What is SIMD?

11) What is MISD?

12) What is MIMD?

13) What is data-level parallelism?

14) What is hardware multithreading?

15) Give the comparison between process switch and thread switch?

16) What do you mean by implicit and explicit multithreading?

17) Define interleaved or fine-grained multithreading?

18) Define blocked or coarse-grained multithreading?

19) What do you mean by shared-address multiprocessor?

20) What is UMA and NUMA multiprocessor?

16 MARKS

1. Explain instruction level parallelism in detail?

2. Explain parallel processing challenges in detail?

3. Explain briefly the Flynns classification?

4. What is hardware multithreading? Explain the various approaches in detail?

5. Explain multicore processors in detail?

6. Compare SISD, SIMD, MISD, and MIMD in detail?

7. Explain the following:

i) Implicit and Explicit multithreading.

ii) Interleaved, Blocked and Simultaneous multithreading.

8. What are multicore processors? Explain the common configurations that support

multiprocessing?

.

Das könnte Ihnen auch gefallen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (895)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (74)

- ARM Processors Interview QuestionsDokument2 SeitenARM Processors Interview Questionsjosephgopu100% (2)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- STD V 21.10.2020 EVS & Language PDFDokument14 SeitenSTD V 21.10.2020 EVS & Language PDFPushpavalli MohanNoch keine Bewertungen

- STD Ii 03.12.2021 English Tamil AsgmtDokument15 SeitenSTD Ii 03.12.2021 English Tamil AsgmtPushpavalli MohanNoch keine Bewertungen

- Unit 1,2 & 3 QB For FoccDokument25 SeitenUnit 1,2 & 3 QB For FoccPushpavalli MohanNoch keine Bewertungen

- Ooad Question BankDokument23 SeitenOoad Question BankPushpavalli MohanNoch keine Bewertungen

- STD V 16.09.2020 Tamil & EVS W.SHDokument18 SeitenSTD V 16.09.2020 Tamil & EVS W.SHPushpavalli MohanNoch keine Bewertungen

- CP5191Dokument2 SeitenCP5191Pushpavalli MohanNoch keine Bewertungen

- ProjectPhase 1 EvaluationDokument3 SeitenProjectPhase 1 EvaluationPushpavalli MohanNoch keine Bewertungen

- Organizational Behaviour Week5Dokument2 SeitenOrganizational Behaviour Week5Pushpavalli MohanNoch keine Bewertungen

- Elective Paper V &vi - Ug UpdatedDokument19 SeitenElective Paper V &vi - Ug UpdatedPushpavalli MohanNoch keine Bewertungen

- 9 School Block InformationDokument1.047 Seiten9 School Block InformationPushpavalli MohanNoch keine Bewertungen

- Stuart Hansen University of Wisconsin - ParksideDokument14 SeitenStuart Hansen University of Wisconsin - ParksidePushpavalli MohanNoch keine Bewertungen

- 8sem - Soa - 2013 - It - Dec 2016 PDFDokument2 Seiten8sem - Soa - 2013 - It - Dec 2016 PDFPushpavalli MohanNoch keine Bewertungen

- NIST Cloud Computing Reference ArchitectureDokument21 SeitenNIST Cloud Computing Reference ArchitecturePushpavalli MohanNoch keine Bewertungen

- Cloud SyllabusDokument1 SeiteCloud SyllabusPushpavalli MohanNoch keine Bewertungen

- Step1: Install Python From Below LinkDokument6 SeitenStep1: Install Python From Below LinkPushpavalli MohanNoch keine Bewertungen

- TelecardiologyDokument20 SeitenTelecardiologyPushpavalli Mohan100% (1)

- Embedded SQL - PPT PDFDokument32 SeitenEmbedded SQL - PPT PDFPushpavalli MohanNoch keine Bewertungen

- HITT 1211 Chapter 4 Lecture Notes TelemedicineDokument2 SeitenHITT 1211 Chapter 4 Lecture Notes TelemedicinePushpavalli MohanNoch keine Bewertungen

- Ge6757 TQM Int 2 Q OnlyDokument3 SeitenGe6757 TQM Int 2 Q OnlyPushpavalli MohanNoch keine Bewertungen

- Design and Analysis of AlgorithmDokument210 SeitenDesign and Analysis of AlgorithmPushpavalli Mohan100% (2)

- List of Experiments: Exp. No. Name of The Experiments Page NoDokument76 SeitenList of Experiments: Exp. No. Name of The Experiments Page NoPushpavalli MohanNoch keine Bewertungen

- CountersDokument8 SeitenCountersPushpavalli MohanNoch keine Bewertungen

- Features and Modes of 8086Dokument11 SeitenFeatures and Modes of 8086ABHishekNoch keine Bewertungen

- Sesi II 2021 Topicd Lect3Dokument29 SeitenSesi II 2021 Topicd Lect3mbagavan 0712Noch keine Bewertungen

- Microcontroller Lecture Notes Module IIIDokument88 SeitenMicrocontroller Lecture Notes Module IIIMuhammet MintaşNoch keine Bewertungen

- List Harga Laptop NewDokument5 SeitenList Harga Laptop NewHepi ParianiNoch keine Bewertungen

- Rog Rampage Vi Extreme Omega Dram QVLDokument36 SeitenRog Rampage Vi Extreme Omega Dram QVLmasoodkamaliNoch keine Bewertungen

- Main Memory DesignDokument28 SeitenMain Memory DesignDev Rishi ThakurNoch keine Bewertungen

- Dadoria2018 Article PerformanceEvaluationOfDominoLDokument8 SeitenDadoria2018 Article PerformanceEvaluationOfDominoLKavyashreeMNoch keine Bewertungen

- 8086 Addressing ModesDokument2 Seiten8086 Addressing Modesbt21me011Noch keine Bewertungen

- MX25L1006E, 3V, 1Mb, v1.4 PDFDokument51 SeitenMX25L1006E, 3V, 1Mb, v1.4 PDFpanjoelsNoch keine Bewertungen

- Evolution of Microprocessor - Types and ApplicationsDokument9 SeitenEvolution of Microprocessor - Types and ApplicationsAnonymous U8awvgZ3pDNoch keine Bewertungen

- GNUSim8085 Is A Graphical SimulatorDokument18 SeitenGNUSim8085 Is A Graphical SimulatorAl AidenNoch keine Bewertungen

- Gujarat Technological UniversityDokument1 SeiteGujarat Technological UniversityRenieNoch keine Bewertungen

- Arria 10 Fpga SlideDokument10 SeitenArria 10 Fpga SlideDushyant KaushikNoch keine Bewertungen

- Intel Core Processor FamilyDokument11 SeitenIntel Core Processor FamilyCJApalinNoch keine Bewertungen

- CHAPTER 1 Introduction To The Microprocessor and ComputerDokument154 SeitenCHAPTER 1 Introduction To The Microprocessor and ComputerMira AlvarezNoch keine Bewertungen

- 8086 in Minimum Mode Part 9Dokument6 Seiten8086 in Minimum Mode Part 9vikas chawlaNoch keine Bewertungen

- LPC9221 NXPDokument8 SeitenLPC9221 NXPRicardo FantiniNoch keine Bewertungen

- Homework #3 Solutions: Spring 2013Dokument2 SeitenHomework #3 Solutions: Spring 2013Adip ChyNoch keine Bewertungen

- MAIN Electrical Parts List: Parts Code Design Loc DescriptionDokument17 SeitenMAIN Electrical Parts List: Parts Code Design Loc DescriptionManuel BonillaNoch keine Bewertungen

- Atmel 4099 Flash Microcontrollers Product Portfolio BrochureDokument48 SeitenAtmel 4099 Flash Microcontrollers Product Portfolio BrochureJogender SainiNoch keine Bewertungen

- 486-PVT (Rev. B2)Dokument14 Seiten486-PVT (Rev. B2)Samuel MarquezNoch keine Bewertungen

- Crusoe ProcessorDokument28 SeitenCrusoe Processorvichu0481Noch keine Bewertungen

- Chapter 3Dokument283 SeitenChapter 3Biruk DawitNoch keine Bewertungen

- Daftar Honorer Kab. Kolaka UtaraDokument174 SeitenDaftar Honorer Kab. Kolaka UtaraevisuviatiNoch keine Bewertungen

- MicroStar (MSI) MS6507 Motherboard SchematicsDokument36 SeitenMicroStar (MSI) MS6507 Motherboard SchematicsChoccyDodgerNoch keine Bewertungen

- Intel Processadores Mais TopsDokument3 SeitenIntel Processadores Mais TopsCesar PereiraNoch keine Bewertungen

- Msi MS-7680 Rev 3.2Dokument34 SeitenMsi MS-7680 Rev 3.2Петро ДуманськийNoch keine Bewertungen

- Ece5023 Memory-Design-And-testing TH 1.1 47 Ece5023Dokument2 SeitenEce5023 Memory-Design-And-testing TH 1.1 47 Ece5023Bhargavi PatilNoch keine Bewertungen