Beruflich Dokumente

Kultur Dokumente

WWW - Montgomerycollege.edu - Kyee - EE244 - Course Handouts - Lecture Notes - Lecture Notes 07

Hochgeladen von

T F0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

45 Ansichten8 SeitenQuestion sample

Originaltitel

www.montgomerycollege.edu_~kyee_EE244_Course handouts_Lecture notes_Lecture notes 07

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenQuestion sample

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

45 Ansichten8 SeitenWWW - Montgomerycollege.edu - Kyee - EE244 - Course Handouts - Lecture Notes - Lecture Notes 07

Hochgeladen von

T FQuestion sample

Copyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 8

EE244 Digital Logic Design Spring 2014 Lecture Notes Set #7

Dr. Kam F. Yee Mar 25, 2014

Page 1 of 8

4.2: Binary Decoders (or simply, Decoders)

Converts n bits input to m bits unique outputs (typically, m = 2

n

)

n-to-2

n

decoder:

- n inputs

- 2

n

outputs; each output corresponds to a minterm of the n inputs

Commonly available decoders:

- 1-to-2 decoder - 2-to-4 decoder

- 3-to-8 decoder - 4-to-16 decoder

3-to-8 Decoder

- 3 inputs: x, y, z (or S

2

, S

1

, S

0

. Order does matter!)

- 8 outputs: Y

0

to Y

7

, each corresponding to a minterm

Y

0

= m

0

= xyz (or S

2

S

1

S

0

)

Y

1

= m

1

= xyz (or S

2

S

1

S

0

)

Y

7

= m

7

= x y z (or S

2

S

1

S

0

)

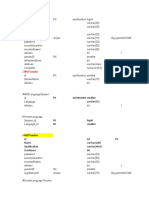

Truth Table

S

n-1

.

.

.

S

1

S

0

Y

0

Y

1

Y

2

Y

Y

.

.

n inputs

2

n

outputs

2

n

-2

2

n

-1

EE244 Digital Logic Design Spring 2014 Lecture Notes Set #7

Dr. Kam F. Yee Mar 25, 2014

Page 2 of 8

Logic Circuit Diagram

Decoder with Enable

Enable input: EN = 0, normal decoder

EN = 1, all outputs are 0

3-to-8 Decoder

(Done by adding one

more input EN to each

one of the AND gates)

Inside of a 3-to-8 Decoder

x

y

z

Y

0

Y

1

Y

2

Y

6

Y

7

Y

4

Y

5

Y

3

EN

EE244 Digital Logic Design Spring 2014 Lecture Notes Set #7

Dr. Kam F. Yee Mar 25, 2014

Page 3 of 8

Implementing Boolean functions using Decoders.

To implement a n-variable Boolean function using a decoder:

1) Find minterm list

2) Use a decoder large enough to generate all minterms

3) Use an OR gate to form the logical sum of all minterms

Ex 1. Implement the following functions using a single 3-to-8 decoder with

enable, an additional OR gates as needed:

F

1

(A, B, C) = AB + AC + BC; F

2

(A, B, C) = m(1, 2, 4, 7)

F

3

(A, B, C) = M(1-4)

x(MSB)

y

z

Y

0

Y

1

Y

2

Y

6

Y

7

Y

4

Y

5

Y

3

EN

EE244 Digital Logic Design Spring 2014 Lecture Notes Set #7

Dr. Kam F. Yee Mar 25, 2014

Page 4 of 8

Ex 2. What does the following circuit do? (Complete circuit in class)

Ex 3. Make a 3-to-8 decoder from smaller 2-to-4 decoders. Use additional

logic gates as needed.

x(MSB)

y

z

Y

0

Y

1

Y

2

Y

6

Y

7

Y

4

Y

5

Y

3

EN

EE244 Digital Logic Design Spring 2014 Lecture Notes Set #7

Dr. Kam F. Yee Mar 25, 2014

Page 5 of 8

4.4: Multiplexers (or muxes)

Combinational logic circuit that selects one of many input lines to connect to

output line, controlled by the selection lines.

Commonly available multiplexers:

- 2-to-1 mux - 4-to-1 mux

- 8-to-1 mux - 16-to-1 mux

Two-way multiplexer, also known as 2-to-1 Mux

- Total of 3 inputs: Data inputs: I

0

, I

1

; Selection input: S

- Always 1 output: Out

Truth table has 8 combinations. It can be condensed in a function table.

Output equation: Out = (S) I

0

+ (S) I

1

n selection lines

I

0

I

1

I

2

Out

1 output

2

n

input lines

S

n-1

S

0

.

.

.

S Out

0 I

0

1 I

1

If S = 0 Out = I

0

If S = 1 Out = I

1

Out

Out

I

2

n

-1

EE244 Digital Logic Design Spring 2014 Lecture Notes Set #7

Dr. Kam F. Yee Mar 25, 2014

Page 6 of 8

Four-way multiplexer, also known as 4-to-1 Mux

- Total of 6 inputs: Data inputs: I

0

, I

1

, I

2

, I

3

; Selection inputs: S

1

, S

0

- Always 1 output: Out

Truth table has 64 combinations. It can be condensed in a function table.

Output equation: Out = (S

1

S

0

) I

0

+ (S

1

S

0

) I

1

+ (S

1

S

0

) I

2

+ (S

1

S

0

) I

3

Circuit Diagram Logic Symbol

S

1

S

0

Out

0 0 I

0

0 1 I

1

1 0 I

2

1 1 I

3

If S

1

S

0

= 00 Out= I

0

If S

1

S

0

= 01 Out = I

1

If S

1

S

0

= 10 Out = I

2

If S

1

S

0

= 11 Out = I

3

I

0

I

1

I

2

Out

S

1

S

0

I

3

EE244 Digital Logic Design Spring 2014 Lecture Notes Set #7

Dr. Kam F. Yee Mar 25, 2014

Page 7 of 8

Implementing Boolean functions using Muxes.

To implement a n-variable Boolean function using a mux:

Choose a mux with n selection lines (if possible)

1) Assign Boolean function inputs to mux selection lines

2) Determine required value of data input lines (use a truth table)

3) Output of the mux is the output of the Boolean function

Or, choose a mux with n-1 selection lines (if possible)

1) Assign n-1 Boolean function inputs to mux selection lines

2) Determine required value of data input lines (use a condensed table)

3) Output of the mux is the output of the Boolean function

Ex 1. Implement F(x, y, z) = m(1, 2, 6, 7) using a 8-to-1 mux.

x y z F

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Ex 2. Implement the above function F(x, y, z) using a 4-to-1 mux.

x y z F

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

I

0

I

1

I

2

Out

S

1

S

0

I

3

x y F

0 0

0 1

1 0

1 1

Condense the truth table

so that number of rows

matches with number of

inputs.

I

0

I

1

I

2

Out

S

2

S

1

S

0

I

3

I

4

I

5

I

6

I

7

EE244 Digital Logic Design Spring 2014 Lecture Notes Set #7

Dr. Kam F. Yee Mar 25, 2014

Page 8 of 8

Ex 3. Implement F(w, x, y, z) = m(1, 3, 4, 11-15) using a 8-to-1 mux.

w x y z F

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

Mux with Enable

Enable input: EN = 0, normal mux

EN = 1, output is constant 0

Out = (S

1

S

0

) I

0

EN + (S

1

S

0

) I

1

EN + (S

1

S

0

) I

2

EN + (S

1

S

0

) I

3

EN

For example, consider a 4-to-1 mux with enable input:

(Done by adding one

more input EN to each

one of the AND gates)

Condense the truth table

so that number of rows

matches with number of

inputs.

w x y F

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

I

0

I

1

I

2

Out

S

2

S

1

S

0

I

3

I

4

I

5

I

6

I

7

I

0

I

1

I

2

Out

S

1

S

0

I

3

EN

1

0

1

0

y z

F(x,y,z)

x

x y z F

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Das könnte Ihnen auch gefallen

- Cellular NetworksDokument60 SeitenCellular NetworksT FNoch keine Bewertungen

- Integrated Services Digital Network (Isdn) : Mcgraw-Hill ©the Mcgraw-Hill Companies, Inc., 2001Dokument29 SeitenIntegrated Services Digital Network (Isdn) : Mcgraw-Hill ©the Mcgraw-Hill Companies, Inc., 2001T FNoch keine Bewertungen

- Syllabus - Introduction To Telecommunication Networks CourseDokument2 SeitenSyllabus - Introduction To Telecommunication Networks CourseT FNoch keine Bewertungen

- OSI Physical LayerDokument30 SeitenOSI Physical LayerT FNoch keine Bewertungen

- Ece 374 Course Notes Telecom Networks 2012-2013Dokument80 SeitenEce 374 Course Notes Telecom Networks 2012-2013Saptarshi ChatterjeeNoch keine Bewertungen

- Faraday - Ee.emu - Edu.tr Eeng211 Exam F 09 10 Final SolutionsDokument12 SeitenFaraday - Ee.emu - Edu.tr Eeng211 Exam F 09 10 Final SolutionsT FNoch keine Bewertungen

- Voice Communication Concepts and Technology: 1 Modified by Masud-ul-Hasan and Ahmad Al-YamaniDokument80 SeitenVoice Communication Concepts and Technology: 1 Modified by Masud-ul-Hasan and Ahmad Al-YamaniT FNoch keine Bewertungen

- Acom Lab ManualDokument58 SeitenAcom Lab ManualRavi ShankarNoch keine Bewertungen

- Sign MagnitudeDokument25 SeitenSign MagnitudeT FNoch keine Bewertungen

- You Did What! by Nonjon-Harry Potter Fan FictionDokument317 SeitenYou Did What! by Nonjon-Harry Potter Fan FictionT FNoch keine Bewertungen

- Half Adders and Full AddersDokument12 SeitenHalf Adders and Full AddersmonzuracNoch keine Bewertungen

- Ece 374 Course Notes Telecom Networks 2012-2013Dokument80 SeitenEce 374 Course Notes Telecom Networks 2012-2013Saptarshi ChatterjeeNoch keine Bewertungen

- Harlequin 2Dokument5 SeitenHarlequin 2T FNoch keine Bewertungen

- Mistaken Love by MzKISSEShereDokument78 SeitenMistaken Love by MzKISSEShereT FNoch keine Bewertungen

- 2 Miricles To Be SaintDokument13 Seiten2 Miricles To Be SaintT FNoch keine Bewertungen

- 5 Hours 27 Minutes and 12 Seconds by Draco - Lover202Dokument23 Seiten5 Hours 27 Minutes and 12 Seconds by Draco - Lover202T FNoch keine Bewertungen

- Heart To Stone by Phoenix - Flames - 1Dokument6 SeitenHeart To Stone by Phoenix - Flames - 1T FNoch keine Bewertungen

- 5 Hours 27 Minutes and 8 Seconds by Draco - Lover202Dokument3 Seiten5 Hours 27 Minutes and 8 Seconds by Draco - Lover202T FNoch keine Bewertungen

- Physics EquationsDokument5 SeitenPhysics Equationsanon-992211100% (64)

- New Microsoft Office Word DocumentDokument42 SeitenNew Microsoft Office Word DocumentT FNoch keine Bewertungen

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeVon EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeBewertung: 4 von 5 Sternen4/5 (5782)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceVon EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceBewertung: 4 von 5 Sternen4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)Von EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Bewertung: 4 von 5 Sternen4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureVon EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureBewertung: 4.5 von 5 Sternen4.5/5 (474)

- Shoe Dog: A Memoir by the Creator of NikeVon EverandShoe Dog: A Memoir by the Creator of NikeBewertung: 4.5 von 5 Sternen4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaVon EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaBewertung: 4.5 von 5 Sternen4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingVon EverandThe Little Book of Hygge: Danish Secrets to Happy LivingBewertung: 3.5 von 5 Sternen3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItVon EverandNever Split the Difference: Negotiating As If Your Life Depended On ItBewertung: 4.5 von 5 Sternen4.5/5 (838)

- Grit: The Power of Passion and PerseveranceVon EverandGrit: The Power of Passion and PerseveranceBewertung: 4 von 5 Sternen4/5 (587)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryVon EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryBewertung: 3.5 von 5 Sternen3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerVon EverandThe Emperor of All Maladies: A Biography of CancerBewertung: 4.5 von 5 Sternen4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnVon EverandTeam of Rivals: The Political Genius of Abraham LincolnBewertung: 4.5 von 5 Sternen4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealVon EverandOn Fire: The (Burning) Case for a Green New DealBewertung: 4 von 5 Sternen4/5 (72)

- The Unwinding: An Inner History of the New AmericaVon EverandThe Unwinding: An Inner History of the New AmericaBewertung: 4 von 5 Sternen4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersVon EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersBewertung: 4.5 von 5 Sternen4.5/5 (344)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyVon EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyBewertung: 3.5 von 5 Sternen3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreVon EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreBewertung: 4 von 5 Sternen4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Von EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Bewertung: 4.5 von 5 Sternen4.5/5 (119)

- Her Body and Other Parties: StoriesVon EverandHer Body and Other Parties: StoriesBewertung: 4 von 5 Sternen4/5 (821)

- Therigatha Pali EnglishDokument191 SeitenTherigatha Pali EnglishAtma DevaNoch keine Bewertungen

- Cambridge IGCSE™: Computer Science 0478/11 May/June 2020Dokument11 SeitenCambridge IGCSE™: Computer Science 0478/11 May/June 2020Miguel Oubiña SánchezNoch keine Bewertungen

- Niruktaślokavārttika by Kōndayūr Nīlaka A - A StudyDokument4 SeitenNiruktaślokavārttika by Kōndayūr Nīlaka A - A StudySaranya KNoch keine Bewertungen

- Much Ado QuotesDokument4 SeitenMuch Ado QuotesDaniela LlorensNoch keine Bewertungen

- Grammar and Vocabulary Starter UnitDokument2 SeitenGrammar and Vocabulary Starter UnitBelén NMNoch keine Bewertungen

- API DokumentationDokument277 SeitenAPI DokumentationOleksiy OsiychukNoch keine Bewertungen

- Virtual Class ManagementDokument10 SeitenVirtual Class ManagementGaurang MakwanaNoch keine Bewertungen

- Lesson Plan in Writing To WritingDokument5 SeitenLesson Plan in Writing To WritingKi KoNoch keine Bewertungen

- Pipelining TutorialDokument14 SeitenPipelining Tutorialrktiwary256034Noch keine Bewertungen

- Difference Between Oracle Apps 11i and R12Dokument5 SeitenDifference Between Oracle Apps 11i and R12Srinivasa Rao AsuruNoch keine Bewertungen

- Book Review - Toward A Structural Psychology of CinemaDokument3 SeitenBook Review - Toward A Structural Psychology of Cinema3xpositionalNoch keine Bewertungen

- How To Write Minutes (Taken From OCR Level 3 Book)Dokument3 SeitenHow To Write Minutes (Taken From OCR Level 3 Book)kr004k5356Noch keine Bewertungen

- Edagogy of Anguages: VerviewDokument54 SeitenEdagogy of Anguages: VerviewMukesh MalviyaNoch keine Bewertungen

- m2500 Modbus Memory Map Uk PDFDokument7 Seitenm2500 Modbus Memory Map Uk PDFJandfor Tansfg ErrottNoch keine Bewertungen

- Read The Following Passage and Choose The Correct AnswersDokument2 SeitenRead The Following Passage and Choose The Correct AnswersRHTi BDNoch keine Bewertungen

- Installations OMSI 2Dokument3 SeitenInstallations OMSI 2KapputNoch keine Bewertungen

- Sentence Starters Debate Notes and Discussion CardsDokument12 SeitenSentence Starters Debate Notes and Discussion Cardsapi-293029174100% (2)

- Forming Comparative and Superlative AdjectivesDokument8 SeitenForming Comparative and Superlative AdjectivesLeonel GasparNoch keine Bewertungen

- Learning Restaurant ExpressionsDokument3 SeitenLearning Restaurant Expressionslaura mejiaNoch keine Bewertungen

- Skylar Chaput Resume 2021Dokument2 SeitenSkylar Chaput Resume 2021api-678836671Noch keine Bewertungen

- Learners With Difficulty Remembering and FocusingDokument33 SeitenLearners With Difficulty Remembering and FocusingKyla Katrinne Asenjo100% (2)

- Educ 6 M4-FinalDokument10 SeitenEduc 6 M4-FinalRachelle LemosioneroNoch keine Bewertungen

- How to install MXRoad V8i SELECTseries 4Dokument8 SeitenHow to install MXRoad V8i SELECTseries 4Marieo ParillaNoch keine Bewertungen

- Bersifat Ingin Tahu Kelestarian Alam Sekitar Mengaplikasi Audio 1,2 Dan3 (Lagu Salam Sejahtera) Buku Teks: Ms 4Dokument7 SeitenBersifat Ingin Tahu Kelestarian Alam Sekitar Mengaplikasi Audio 1,2 Dan3 (Lagu Salam Sejahtera) Buku Teks: Ms 4farahNoch keine Bewertungen

- Lesson 4 - Introduction-To-Adobe-Illustrator-CcDokument30 SeitenLesson 4 - Introduction-To-Adobe-Illustrator-CcJoserie MirabelesNoch keine Bewertungen

- Translation Evaluation - A State of The Art Survey: Alina Secară Leeds UniversityDokument20 SeitenTranslation Evaluation - A State of The Art Survey: Alina Secară Leeds UniversityVinoth Ur FriendNoch keine Bewertungen

- SAX Parsing With PythonDokument3 SeitenSAX Parsing With Pythonmarquimf2008Noch keine Bewertungen

- Document 123Dokument2 SeitenDocument 123Mustakim MalikNoch keine Bewertungen

- What Is Art? Philippine Art As FilipinoDokument2 SeitenWhat Is Art? Philippine Art As FilipinoKelly Jane ChuaNoch keine Bewertungen