Beruflich Dokumente

Kultur Dokumente

ReconfArqsBasseConsommation PDF

Hochgeladen von

Jessica Thompson0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

14 Ansichten9 SeitenOriginaltitel

ReconfArqsBasseConsommation.pdf

Copyright

© © All Rights Reserved

Verfügbare Formate

PDF, TXT oder online auf Scribd lesen

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

0 Bewertungen0% fanden dieses Dokument nützlich (0 Abstimmungen)

14 Ansichten9 SeitenReconfArqsBasseConsommation PDF

Hochgeladen von

Jessica ThompsonCopyright:

© All Rights Reserved

Verfügbare Formate

Als PDF, TXT herunterladen oder online auf Scribd lesen

Sie sind auf Seite 1von 9

Architectures recongurables : opportunits pour la faible consommation

Sbastien Pillement, Raphal David, Olivier Sentieys

quipe R2D2 - Universit de Rennes I/IRISA

6 rue de Kerampont, BP 447, 22305 Lannion, France

Ml : pillemen@univ-rennes1.fr

http://www.irisa.fr/

Abstract

Les architectures recongurables reprsentent un nou-

veau choix dans le processus de conception et dim-

plmentation dapplications complexes. Ces architec-

tures, de part leur exibilit, offrent des opportuni-

ts pour la prise en compte de la consommation dans

le cycle de conception. Bien que rcente dans le do-

maine du recongurable, cette contrainte est intgre

dans les nouvelles recherches tout les niveaux de la

conception (optimisations architecturales, logiques et

technologiques). Nous prsentons dans cet article les

opportunits et les premiers rsultats, du point de vue

de la consommation, quoffrent les architectures re-

congurables.

1 Introduction

Depuis quelques annes, les progrs technologiques

raliss ont permis lmergence dun nouveau type

darchitectures : les architectures recongurables.

Lide de base de ces architectures est doffrir aux

concepteurs la exibilit dune architecture program-

mable et les performances temporelles dun circuit d-

di. Ces architectures ont donc t trs largement uti-

lises dans des domaines trs volatiles, o les normes

font dfauts et o les performances dun microproces-

seur seul ne sont pas sufsantes. Elles offraient ce-

pendant de trs faibles capacits dintgration et nof-

fraient pas des performances de calcul trs leves.

Les recherches dans ce domaine se sont donc intres-

ses lamlioration de ces problmes dlaissant to-

talement les aspects consommation. Elles se sont tra-

duites par lintroduction de nouvelles architectures [1]

supportant les contraintes temporelles dapplications

complexes et offrant de nouveaux paradigmes de cal-

cul.

Dans le mme temps, de nouvelles applications ont

merges telles que les ordinateurs personnels ou por-

tables, les tlcommunications sans l, les assistants

de personnes (PDA), le multimdia ou les rseaux

adhoc. Ces applications intgrent des fonctionnalits

complexes qui demandent des calculs performants.

En outre, du point de vue architectural, les systmes de

prochaines gnrations auront successivement trai-

ter des applications trs diffrentes en terme de grain

de calcul (du niveau bit au niveau arithmtique), de

motif de calcul ou daccs aux donnes. Lorsque par

ailleurs, le systme doit consommer trs peu dnergie

(systmes embarqus ou problme de refroidissement)

et rester exible, le problme de sa conception devient

insoluble si lon se limite aux architectures classiques.

On peut prendre pour exemple les futures gnrations

de tlcommunications mobiles. En effet, au trs haut

niveau de performance (estim 12 GOPS) rsultant

de lassociation de capacits multimdia et de tech-

niques daccs volues telles que le W-CDMA que

devront supporter ces systmes, sajoute la ncessit

de supporter lensemble des algorithmes intgrs aux

normes de gnrations actuelles ainsi que leurs vo-

lutions. Ces systmes tant souvent embarqus leurs

consommations devra tre matrise.

De part les contraintes associes aux nouvelles appli-

cations, les solutions totalement matrielles (ASIC) ou

totalement logicielles (P, DSP) ne sont plus adap-

tes. Ds lors, lalternative propose via les architec-

tures recongurables est de plus en plus considre.

De nombreux travaux ont dmarr dans le but dasso-

cier les trois principales contraintes inhrentes aux ap-

plications de prochaine gnration que sont les hautes

performances, la faible consommation et la exibilit.

Dans cet article, aprs un rappel des contraintes et

des spcicits des architectures recongurables nous

aborderons la problmatique de la consommation pour

cette cible technologique. Les opportunits de concep-

tion faible consommation au niveau physique, au ni-

veau porte et au niveau architectural feront lobjet des

sections suivantes.

2 Architectures recongurables : dnitions

et exemples

Il est facile dassocier architectures recongurables et

FPGA

1

, cependant ceci rduit considrablement les-

pace de conception de ces architectures. Ltude s-

mantique du mot recongurable en donne une dni-

tion plus prcise. En effet, conguration

2

, signie

lorigine faonner la ressemblance de et a pris le sens

de disposition relative dlments.

Une architecture est constitue dune disposition rela-

tive dlments organiss selon un certain schma. La

reconguration, en permettant un choix des lments

dune part, et de leur disposition relative dautre part,

autorise une variabilit des schmas et donc des archi-

tectures. Cette dnition recouvre alors un large en-

semble darchitectures dont les FPGAs font partis.

Lavantage de ces systmes vient de la possibilit

daugmenter les performances de traitement en crant

un chemin de donnes matriel adapt, tout en main-

tenant un niveau de exibilit dvolu habituellement

aux solutions logicielles. Cette exibilit est obtenue

par la mise en place de ressources redondantes of-

frant diffrentes possibilits de routage ou de calcul.

Les architectures sont en gnral organises selon un

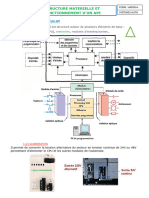

tableau rgulier dlments de calcul (g. 1) d-

nis diffrent niveau de granularit. Ces ressources

de calcul sont interconnectes par un rseau plus ou

moins exible et plus ou moins performant [2]. Les

connexions sont ralises par des matrices dintercon-

nexions construites autour de portes de transmission

permettant de crer des connexions entre les segments

arrivant sur la matrice.

Blocs de

calculs

Structure

d'interconnexion

Blocs d'E/S

FIG. 1. Architecture recongurable gnrique

La reconguration consiste donc spcier les op-

rations et les interconnexions de cet ensemble de res-

1

Field Programmable Gate Array

2

Le Robert, dictionnaire historique de la langue franaise sous

la direction dAlain Rey

sources, que lon nomme couche opratoire. Cette re-

conguration est effectue dans une couche suprieure

(dite couche de reconguration) construite autour de

points de mmorisation statique.

2.1 Granularit de reconguration

Dans [3], Jan Rabaey dnit quatre niveaux de recon-

guration. Le niveau porte qui correspond aux FPGA,

le niveau oprateur, le niveau fonctionnel et le ni-

veau systme. Ce dernier niveau correspond en fait

aux processeurs programmables. Les considrations

de consommation pour ce niveau de reconguration

sont connues et tudies par ailleurs [4, 5, 6]. La

classication propose nous semble ambigu et dif-

cile raliser, dans le sens o la distinction fonction-

nel/oprateur nest pas claire. Nous regrouperons donc

ces deux niveaux de reconguration. Nous qualierons

de grain n les architectures de type FPGA qui per-

mettent une optimisation au bit prs. Les architectures

de grain plus pais (de niveau fonctionnel ou opra-

teur) seront appeles processeurs recongurables.

Nous prsentons ici les principales caractristiques des

architectures grain n et des processeurs recongu-

rables.

2.1.1 Reconguration au niveau porte

La reconguration au niveau porte est celle qui est ra-

lise sur les composants FPGA ou CPLD

3

[7]. Les ar-

chitectures supportant ce type de reconguration sont

qualies de grain n en raison de la faible largeur des

chemins de donnes.

Dans le cas (le plus rpandu) des FPGAs, la recon-

guration opre au niveau logique sur des LUTs (Look-

Up Table) et sur leurs interconnexions. tant donne

la quantit de LUTs ncessaire la dnition de fonc-

tions volues

4

, et un rseau dinterconnexions tota-

lement connect, ces architectures ncessitent un trs

grand nombre de donnes de conguration. Pour ces

architectures la couche de conguration est une m-

moire de type SRAM.

En recongurant une architecture au niveau logique,

on a la possibilit de dnir nimporte quel type de

chemin de donnes en synthtisant les oprateurs re-

quis par lapplication. Cette caractristique est trs in-

tressante pour les traitements logiques pour lesquels

chaque bit est susceptible dtre trait indpendam-

ment. Mais si cette exibilit facilite la "customisa-

3

Complex Programmable Logic Device

4

La complexit des quations boolennes implantes dans ces

LUTs est limite par le nombre dentres de ces quations et non

par un nombre de portes logiques : typiquement 3/4 entres.

tion" des chemins de donnes disposant dun fort pa-

ralllisme au niveau bit, elle est par contre dfavorable

aux traitements arithmtiques.

2.1.2 Reconguration au niveau fonctionnel et

oprateur

Linadquation des FPGAs avec certaines applications

a amen les concepteurs proposer dautres types

darchitectures. Dans ces architectures les intercon-

nexions et les oprateurs sont congurables mais tra-

vaillent au niveau arithmtique (par exemple 8 ou 16

bits). Ceci a pour effet damliorer les performances

sur les traitements arithmtiques, au dtriment des op-

timisations au niveau bit. Cette approche, provient du

fait que les applications sont constitues de curs de

boucles trs rguliers [8]. Ces architectures rduisent

par ailleurs la taille des congurations, permettant

denvisager des stratgies de recongurations dyna-

miques.

La plupart de ces architectures utilise un rseau din-

terconnexion [2] deux dimensions, ventuellement

hirarchique. On peut citer, par exemple, les architec-

tures DReAM [9], Morphosys [10], FPFA [11], RaPiD

[12] ou le KressArray [13]. Cependant certaines archi-

tectures prsente une topologie linaire comme le Pi-

perench [14].

La taille des recongurations tant limite, des mca-

nismes volus peuvent ainsi tre mis en uvre pour

distribuer les informations de conguration et rduire

le cot (en consommation) du contrle de ces architec-

tures. Ces considrations ont t mises en uvre dans

les architectures Pleiades [15] et DART [16], spci-

quement conues pour la faible consommation.

3 Rpartition dnergie dans les architec-

tures recongurables

Les solutions ddies (ASIC) peuvent tres consid-

res comme optimales du point de vue de la consom-

mation. Dans ces circuits les oprateurs sont optimaux

en terme de largeur de donnes et de sophistication car

ils sont conus pour une application. Il ny a donc pas

de exibilit et aucune ressource supplmentaire nest

ncessaire. Lexcution de lapplication est dtermi-

niste et souvent gre par une simple machine dtats.

Le paralllisme (de donne, dinstruction ou de tches)

peut par ailleurs tre compltement exploit. En choi-

sissant le bon niveau de paralllisme, il est alors pos-

sible de rduire la frquence de fonctionnement. De

ce fait, la tension dalimentation peut tre optimise.

Dans ces circuits la frquence et la surface tant opti-

males, larbre de distribution de lhorloge peut tre r-

duit et optimis. Les pnalits de distribution de lhor-

loge peuvent galement tre minimises en utilisant

des communications globalement asynchrone - loca-

lement synchrone [17].

Finalement, le fait de construire compltement larchi-

tecture permet doptimiser les changes de donnes.

La hirarchie mmoire (trs consommatrice dnergie)

peut donc tre optimise et les accs aux donnes sont

matriss [18].

Clairement, les ASICs reprsentent la limite basse at-

teindre pour la consommation, cependant ces circuits

noffrent aucune exibilit. Cette problmatique pos-

sde des impacts sur le cot des circuits (car il y a trs

peu de rutilisation) et sur les nouvelles applications,

qui ncessitent toutes de la exibilit. Cette constata-

tion a des chos dans le monde industriel puisque ST-

Microelectronics, Inneon, Motorola et Texas Instru-

ments annoncent lutilisation darchitectures recon-

gurables dans leurs futurs systmes pour linfrastruc-

ture des tlcommunications mobiles.

3.1 Distribution de lnergie dans les architec-

tures recongurables grain n

Les FPGAs offrent une reconguration au niveau bit

et utilisent gnralement un rseau dinterconnexion

de type mesh (maillage). De nombreux travaux ont d-

montr le potentiel de ces architectures du point de vue

de la performance [19], cependant ces architectures in-

troduisent des lments faisant augmenter la consom-

mation dnergie.

En fait, construire des oprateurs arithmtique im-

plique lutilisation dun grand nombre de cellules sur

un bit qui doivent tre interconnectes. Le rseau tant

trs exible, les signaux doivent alors traverser un

grand nombre de matrices dinterconnexions (switch

box) qui induisent un gaspillage dnergie non ngli-

geable.

Les tudes menes pour estimer la consommation

dnergie des FPGAs [20, 21, 22, 23] montrent toutes

que 60 70% de lnergie consomme est due lin-

terconnexion, 20% est due larbre dhorloge et que le

reste se rpartit entre les blocs de calcul et les entres-

sorties. Cette distribution inhabituelle de la consom-

mation vient du fait que sur des oprations arithm-

tiques il nest pas ncessaire de contrler les bits indi-

viduellement [15], le paralllisme de niveau bit tant

trs limit.

Un autre inconvnient de ces architectures provient du

volume de donnes de conguration ncessaire. Cette

conguration (qui concerne les oprateurs au niveau

bit et les interconnexions) est charge en srie dans une

mmoire de type SRAM. Lorsque ces congurations

atteignent le million de bits [24, 25], lnergie de la

reconguration doit tre pris en compte. Il nexiste ce-

pendant, pour linstant, aucune estimation (sinon celle

applique aux mmoires) sur le cot de la recongura-

tion dun FPGA.

3.2 Distributiondnergie dans les processeurs re-

congurables

La distribution dnergie de ces architectures peut tre

rapproches de celle des processeurs programmables,

dans lesquelles lajout de ressources et laugmentation

de la frquence pour augmenter les performances en

conservant la exibilit se paye par une forte consom-

mation dnergie (distribution du contrle, accs de

large bancs mmoires, frquence leve, . . .).

Cependant la mthode de reconguration des pro-

cesseurs recongurables, permet la rduction de la

consommation dnergie. En limitant la taille de la

conguration et en tenant compte de la rgle du 80/20

[26] ces recongurations arrivent trs occasionnelle-

ment et rduisent ainsi la consommation due la dis-

tribution du contrle de larchitecture.

Un autre avantage de ces architectures vient de la pos-

sibilit de prendre en compte le paralllisme de lappli-

cation. Il est alors possible de rduire la frquence de

fonctionnement et la tension dalimentation en adap-

tant le paralllisme de larchitecture celui de lappli-

cation.

3.3 Conclusions

La problmatique de la faible consommation dans

les architectures recongurables doit donc prendre en

compte ces spcicits. Cette contrainte doit tre opti-

mise tous les niveaux de la conception dun systme

base darchitectures recongurables.

La table 1 rsume les avantages et inconvnients des

diffrentes classes darchitecture et montre lincidence

du mode de reconguration sur lefcacit nerg-

tique obtenue. La premire colonne donne une esti-

mation du nombre de donnes de reconguration n-

cessaires. La deuxime colonne prsente alors la fr-

quence de reconguration envisageable et spcie si

la reconguration doit tre effectue chaque cycle,

chaque appel de fonction (ou excution dune boucle)

ou lorsquune nouvelle tche (application) arrive. La

troisime colonne rsume les deux premires en ap-

proximant lefcacit nergtique caractrise par le

nombre de MOPS

5

pour chaque mW consomm. Le

critre de exibilit est nalement prsent dans la co-

lonne de droite.

Nous allons dans la suite du document prsenter les

optimisations possibles et les axes de recherche pour

rduire la consommation des architectures recongu-

rables.

4 Optimisations au niveau technologique

Au niveau transistor les initiatives doptimisations

pour les architectures grain n sont faibles, le mar-

ch tant couvert par les deux principaux fabricants de

FPGA (Xilinx et Altera). Cette situation laisse donc

peux de place pour les innovations ce niveau. Ce-

pendant Xilinx offre maintenant des architectures sp-

ciques pour la faible consommation avec son ar-

chitecture CoolRunner

TM

[27]. Cette architecture de

CPLD possde un mode standby et supporte diff-

rents domaines dhorloge et un fonctionnement asyn-

chrone. Cette architecture supporte des frquences de

333 MHz et consomme 14 A en mode standby. Le

mode standby de cette architecture a par ailleurs t

repris dans dautres architectures de Xilinx, comme le

Spartan et le XC4000 (serie XL).

Les fabricants intgrent dsormais des mcanismes

permettant de rduire la consommation. Ces blocs

spciques concernent essentiellement la distribution

de lhorloge [28]. Les FPGAs actuels intgrent plu-

sieurs DLL (Delay Locked Loop) ou PLL (Phase Lo-

cked Loop) permettant de dnir plusieurs domaines

dhorloge indpendant [29, 25] et proposent des m-

canismes de re-synchronisation.

Des recherches ont nanmoins t menes ce niveau

pour proposer notamment de nouvelles architectures

de portes de transmission [23]. Les auteurs ont mon-

trs quavec leur architecture la tension dalimentation

peut tre ramene 2xV

T

. Ce type de structure permet

dutiliser des tensions dalimentation de lordre de 1,5

V pour les nouvelles technologies de FPGAs.

Une architecture grain n et faible consommation a

t propose par V. George [30]. Cette architecture im-

plmente une interconnexion de type low-swing et ap-

porte une attention particulire aux matrices dinter-

connexions par lextraction de la taille optimale des

transistors constituant les portes de transmission. Le

problme principal provenant des connexions non ac-

tives introduisant de fortes capacits de charge, un r-

seau dinterconnexions hirarchique permettant la r-

duction de la consommation a t tudi. Enn, la mo-

dication de la hirarchie de calcul a t revue pour

5

Millions of Operations Per Seconds

Type dArchitecture Taille de la conguration Frquence de conguration Efcacit nergtique Flexibilit

ASIC 0 bit 0 100 MOPS/mW - -

FPGA 1 M bits Tche 1 MOPS/mW +/-

niveau oprateur 10 k bits Fonction 1 MOPS/mW +

niveau fonction 100 bits Fonction 10 MOPS/mW +

Processeur 10 bits Cycle 1 MOPS/mW ++

TAB. 1. Efcacit nergtique des diffrentes classes darchitecture

obtenir une consommation plus faible tout en mainte-

nant un niveau de exibilit acceptable.

Une autre approche se retrouve dans les architectures

FPOP [31] ou le RNS Recongurable Processor [32].

Lide est ici de tirer partie des proprits des codes re-

dondants ou de larithmtique des rsidus (RNS), an

de rduire la surface des oprateurs arithmtiques. Le

passage dans une reprsentation autre que le binaire

naturel permet de rduire la consommation de ces ar-

chitectures en simpliant certaines oprations.

Dune manire gnrale, en ce qui concerne les pro-

cesseurs recongurables les techniques de conception

dASIC pour la faible consommation doivent tres ap-

pliques.

5 Optimisations au niveau porte

Lobjectif prioritaire est ici de rduire au maximum les

interconnexions et le taux dactivit des signaux.

La premire optimisation vient de la dcomposition

logique des circuits. Cette optimisation concerne es-

sentiellement les architectures grain n, les proces-

seurs recongurables travaillant au niveau arithm-

tique. En effet, dans un FPGA, la logique est impl-

mente sous forme de LUT gnralement de 4 entres.

Ces LUT, pouvant tre assimiles de la mmoire

SRAM, sont souvent sous-utilises gaspillant alors de

la logique et des interconnexions. Ce problme NP-

complet nest pas beaucoup abord dans la littrature

(du point de vue de la consommation), les architec-

tures tant extrmement protges par leur construc-

teur. Cependant des optimisations peuvent tres appor-

tes partir dune solution initiale [33], en remaniant

le mapping technologique an de rduire ( fonction

constante) le taux dactivit des signaux internes dune

fonction complexe. Les rsultats obtenus amnent une

amlioration de lordre de 10 % sur la consomma-

tion globale du circuit. Il est possible ici, tant donne

la exibilit des architectures, denvisager des tech-

niques dencodage de bus ou de machines dtats [34]

permettant encore une fois de rduire le taux dactivit.

Le deuxime aspect de ce niveau vient du placement

des blocs de logiques dans la couche opratoire. Ce

placement a un impact fort sur le routage. Les al-

gorithmes de placement/routage minimisent le temps

dexcution ou la surface. Pour une conception ef-

cace en consommation le placement/routage doit sou-

vent tre effectu la main.

Les architectures recongurables intgrent aujour-

dhui beaucoup de fonctionnalits [29, 35]. Le choix

du bloc appropri a alors un impact majeur sur les

performances en consommation. Par exemple, dans le

VIRTEX II, limplmentation de ressources de sto-

ckage peut se faire de trois manires : par lutilisa-

tion de registres, lutilisation de mmoire locale qui

est un premier niveau de hirarchie mmoire ou par

lutilisation du deuxime niveau de hirarchie que sont

les BRAM. Le choix dun de ces lments dpend du

nombre de donnes stocker, si ce nombre excde 48

le choix des BRAM est alors le meilleur. Un autre

exemple vient de lutilisation efcace des blocs in-

tgrs ddis. Par exemple, les multiplieurs des nou-

velles gnrations de FPGAs sont plus efcaces en

terme dnergie et de performances, quune implmen-

tation sous forme de LUT. Dans les processeurs recon-

gurables ce choix est primordial, les oprateurs tant

optimiss pour certains types doprations.

Finalement le mcanisme dhorloge garde (clock ga-

ting), qui est une technique trs largement utilise,

peut tre appliqu aux architectures recongurables.

En utilisant les ressources de gestion dhorloge int-

gres, il est possible de grer dynamiquement larbre

dhorloge an de ne faire commuter que les parties

utiles du circuit [28]. Une autre possibilit est de r-

duire dynamiquement la frquence de certaines par-

ties du circuit. Ces techniques sont aussi employes

dans des processeurs recongurables comme DART

par exemple [16].

Le dernier point consiste utiliser des arithmtiques

diffrentes sadaptant au mieux aux architectures re-

congurables "classiques". Larithmtique RNS per-

met denvisager des rsultats intressant [36]. Cette

arithmtique permet de reprsenter les systmes sous

la forme de petit datapath indpendant, permettant

doptimiser lutilisation des ressources de routage. Le

paralllisme des architectures grain n est particuli-

rement bien adapte ce type dapproche.

6 Optimisations au niveau architectural

Les techniques doptimisation au niveau architectural

visent principalement rduire le cot de laccs aux

donnes et de la reconguration tout en autorisant une

exploitation optimale du paralllisme de lapplication.

La rduction du cot de laccs aux donnes implique

la minimisation de deux critres : le cot dun accs

mmoire et le nombre daccs mmoire. Bien que les

architectures recongurables disposent de ressources

de stockage dont le nombre et la taille sont gs, il

est toutefois concevable de construire des hirarchies

mmoire efcaces. titre dexemple, le FPGA Vir-

texII dispose de trois types de ressources de mmo-

risation : des registres, des mmoires locales (Selec-

tRAM) de 128 bits et des blocs de mmoire (BRAM :

Bloc SelectRAM) de 18 kbits. Ds lors, il est possible

de concevoir une hirarchie mmoire approprie, limi-

tant le cot nergtique moyen des accs aux donnes.

Bien que les tudes portant sur la conception de hirar-

chies mmoires sur les composants ddis soient au-

jourdhui en passe darriver maturit [37, 18], elles

tardent cependant samorcer sur les composants re-

congurables.

De part leur structure, les architectures recongu-

rables autorisent par ailleurs une rduction sensible

du nombre daccs aux donnes. Lexploitation de la

localit spatiale des donnes est notamment facilite

par les connexions de type "un vers tous" pouvant tre

mises en uvre dans ces architectures. Il est ainsi no-

tamment possible dapprovisionner plusieurs units de

calcul par le biais dun unique accs mmoire. La loca-

lit temporelle des donnes passe quant elle par luti-

lisation des plus bas niveaux de la hirarchie mmoire.

Lexploitation des registres internes aux chemins de

donnes pour crer des chanes de retard permet ce

titre dconomiser de prcieux accs mmoires.

Loptimisation architecturale dun composant recon-

gurable passe galement par lexploitation du parall-

lisme de lapplication. Cette exploitation se traduisant

par un accroissement de la puissance de calcul, les fr-

quences de fonctionnement et les tensions dalimen-

tation peuvent alors tre rduites. Lefcacit nerg-

tique de larchitecture est donc fortement inuence

par la qualit de lexploration logicielle. De part leur

exibilit, les architectures recongurables offrent aux

ingnieurs systmes la possibilit dutiliser tout type

de paralllisme.

Loptimisation au niveau architectural des architec-

tures recongurables passe nalement par la rduction

du cot de la distribution du contrle au travers du

composant. Cette thmatique de recherche a rcem-

ment fait lobjet de nombreuses tudes, ciblant prin-

cipalement les processeurs recongurables. En parti-

culier, la distinction des donnes servant spcier la

structure matrielle du chemin de donnes (e.g. inter-

connexion doprateur) et de celles servant la contr-

ler (e.g. mise zros des accumulateurs), a rendu pos-

sible la mise en uvre de techniques de recongura-

tion offrant un niveau de exibilit comparable celui

des processeurs tout en minimisant la complexit de

cette opration de contrle [16, 38]. Outre ces tech-

niques ddies aux architectures grain pais, des tra-

vaux ont galement t mens dans le but de limiter la

quantit de donnes devant tre transfres pour recon-

gurer le circuit. Elles se sont notamment traduites par

lintroduction de techniques de reconguration par-

tielle et par le partage dinformations de conguration

entre plusieurs sous-ensembles du circuit.

7 Optimisations au niveau systme

Les optimisations ce niveau sont trs classiques dans

la conception en vue de la faible consommation. Ce-

pendant la exibilit et les ressources intgres dans

une architecture recongurable permettent de tirer par-

tie de ces optimisations pour diffrentes classes dap-

plications, au lieu dune.

Dans [39], les auteurs montrent une rduction de la

consommation dnergie de lordre de 33% par luti-

lisation dun pipeline "en vague" (Wave Pipeline). Ce

pipeline ne dcoupe pas le circuit en fonctionnalit,

mais cre des chemins de longueur gale. Tirant par-

tie de la topologie des architectures recongurables,

il permet de ne pas limiter la frquence de fonctionne-

ment par des chemins critiques trop longs et disparates.

Les auteurs ont aussi dmontr un gain de 45% par un

partitionnement judicieux de lapplication. Cette tech-

nique de pipeline augmente la puissance dissipe mais

peut permettre la diminution de lnergie. Cette tech-

nique de pipeline est utilise aussi dans Piperench. Les

auteurs utilisent la reconguration pour dnir la no-

tion de pipeline virtuel [40] permettant limplmenta-

tion dune application dont le nombre dtages de pi-

peline est suprieur celui que peut supporter larchi-

tecture.

La slection des algorithmes et des architectures

les implmentant est un facteur de rduction de la

consommation. Dans [41], les auteurs obtiennent des

gains de consommation de lordre de 70% par rapport

une implmentation classique sur un Xilinx VIR-

TEX II et un DSP Texas Instruments TMS320C6415.

Ces gains sont obtenus par un choix judicieux des al-

gorithmes, par exemple une multiplication de matrice

consommera moins si elle est considre comme tant

un tableau 1D, car elle ncessitera moins dintercon-

nexion et par lexploitation du paralllisme de lappli-

cation.

Le choix de larchitecture joue un rle trs impor-

tant sur la consommation en dterminant le nombre de

ressources dinterconnexion et de calcul ncessaires

lapplication [42]. Si toutes les optimisations des ar-

chitectures grain n peuvent tres transposes pour les

processeurs recongurables, sur ce point ces dernires

amnent des optimisations radicales par rapport au ni-

veau bit.

Une approche spcique vient des possibilits de re-

conguration partielle et dynamique des nouvelles ar-

chitectures. Dans [43, 44], les auteurs utilisent la re-

conguration partielle pour rduire la taille du circuit

utilis, un circuit plus petit consommant moins dner-

gie. Lobjectif principal et dviter davoir des res-

sources non utilises. Ils ont appliqu cette mthode

au traitement des images et sadaptent aux besoins en

monitorant les entres du systme. Des blocs fonction-

nels sont alors rpliqus ou supprims en utilisant la

reconguration partielle.

La dernire optimisation au niveau systme spcique

aux processeurs recongurables vient de la rduction

de la taille de reconguration, amenant une rduction

de la mmoire de stockage ncessaire. De plus ces ar-

chitectures offrent (dans la majorit des cas) plusieurs

niveaux de paralllisme, permettant alors de sadapter

lapplication courante.

8 Conclusions

Il nexiste pas lheure actuelle darchitecture recon-

gurable au niveau bit, associant des considrations

de faible-consommation et une forte densit dintgra-

tion. Des initiatives existent cependant des niveaux

de reconguration suprieurs. Larchitecture Pliades

[45] est une architecture recongurable htrogne d-

nie pour la faible consommation. Lintgration de

blocs de calcul ddis et la dnition dun rseau

dinterconnexions hirarchique lui permettent dobte-

nir une efcacit nergtique de 30 MOPS/mW. Lar-

chitecture DART [16] est quant elle une architec-

ture recongurable au niveau fonctionnel. La prise

en compte, lors de sa conception, de la contrainte de

faible consommation permet dobtenir une efcacit

nergtique de 40 MOPS/mW.

La consommation des circuits recongurables devient

une contrainte de conception importante. Hormis des

effets de bord dus aux spcicits de ces architectures

permettant dobtenir de la exibilit, toutes les tech-

niques classiques de conception en vue de la faible

consommation peuvent tres utilises. Les fabricants

de circuits recongurables apportent par ailleurs un in-

trt de plus en plus grand ces questions et offrent des

possibilits doptimisation de la consommation dans

leurs architectures.

Cependant de nombreux verrous reste lever. En

effet les architectures recongurables faible grain

souffrent dune sous-utilisation de leurs ressources de

calcul amenant un gaspillage dnergie. De plus, les

modles de consommation entre architectures recon-

gurables et ddis sont diffrents. La puissance tant

gnralement due lhorloge dans les ASIC, alors

que ce sont les interconnexions qui sont dominantes

dans les architectures recongurables. Cette pression

sur linterconnexion risque de saccentuer avec lav-

nement des technologies submicroniques profondes.

Enn, les mthodologies de conception ncessitent des

estimations prcises et de haut niveau an de guider la

synthse des applications. Si lestimation de consom-

mation du plan opratoire commence tre matrise,

il en est autrement de la consommation du plan de

conguration pour lequel aucun travail nest men

ce jour. Ces estimations deviendront prpondrantes si

lon souhaite tirer partie des possibilits de recongu-

ration partielle des futures architectures.

Les architectures recongurables offrent des opportu-

nits pour la conception faible-consommation. Si des

progrs sont encore faire pour les architectures faible

grain, les processeurs recongurables offrent des opti-

misations et des rsultats trs encourageants.

Rfrences

[1] R. Hartenstein. A Decade of Recongurable

Computing : A Visionary retrospective. In De-

sign Automation and Test in Europe, Munich,

Germany, March 2001.

[2] H. Zhang, M. WAN, V. George, and J. Rabaey.

Interconnect Architecture Exploration for Low-

Energy Recongurable Single-Chip DSPs. In

IEEE Workshop on VLSI, April 1999.

[3] J. M. Rabaey. Recongurable Processing :

The solution to Low-Power Programmable DSP.

In IEEE International Conference on Acoustics,

Speech, and Signal Processing, April 1997.

[4] J. Fridman. Sub-Word Parallelism in Digital Si-

gnal Processing. IEEE Signal Processing Maga-

zine, 17(2) :2735, March 2000.

[5] P. Faraboshi, G. Desoli, and J. A. Fisher. The

Latest Word in Digital and Media Processing.

IEEE Signal Processing Magazine, pages 59

85, March 1998.

[6] V. S. Krishnan. Speculative Multithreading Ar-

chitectures. PhD thesis, University of Illinois,

1998.

[7] C. Tavernier. Circuits logiques programmables.

Microcontrleur et environnement. Dunod, 1996.

[8] N. Zhang and R.W. Brodersen. Architectural

Evaluation of Flexible Digital Signal Processing

for Wireless Receiver. In Asilomar Conference,

October 2000.

[9] J. Becker, T. Pionteck, and M. Glesner. DReAM :

A Dynamically Recongurable Architecture for

Future Mobile Communication Applications. In

International Workshop on Field Programmable

Logic and Applications, pages 312321, Villach,

Austria, August 2000. Lecture notes in Computer

Science 1896.

[10] H. Singh, G. Lu, M. Lee, E. Filho, and

R. Maestre. MorphoSys : Case study of a Re-

congurable Computing System targeting Multi-

media Applications. In International Design Au-

tomation Conference, pages 573578, Los An-

geles, California, June 2000.

[11] G. Smit, P. Havinga, L. Smit, P. Heysters, and

M. Rosien. Dynamic Reconguration in Mobile

Systems. In International Conference on Field

Programmable Logic and Applications, pages

171181, Montpellier, France, September 2002.

Lecture Notes in Computer Sciences 2438.

[12] D. C. Cronquist, P. Franklin, C. Fisher, M. Fi-

gueroa, and C. Ebeling. Architecture Design of

Recongurable Pipelined Datapath. In Advance

Research in VLSI, pages 2340, Atlanta, USA,

March 1999.

[13] R. Hartenstein and R. Kress. A Datapath Syn-

thesis System for the Recongurable Computing.

In Asia and South Pacic Design Automation

Conference, Chiba, Japan, 1995.

[14] S. Goldstein, H. Schmit, M. Moe, M. Budiu, and

S. Cadambi. PipeRench : A Coprocessor for

Streaming Media Acceleration. In International

Symposium on Computer Architecture, Atlanta,

USA, May 1999.

[15] A. Abnous. Low Power Domain Specic Proces-

sors for Digital Signal Processing. PhD thesis,

University of California, Berkeley, 2001.

[16] R. David, D. Chillet, S. Pillement, and O. Sen-

tieys. VLSI-SOC 2001 Post Conference Book,

chapter ADynamically Recongurable Architec-

ture for Low-Power Multimedia Terminals. Klu-

wer Academic Publishers, 2002.

[17] W.S. VanScheik and R.F. Tinder. High Speed

Externally Asynchronous/ Internally Clocked

Systems. IEEE Transaction on Computers,

46(7) :824829, July 1997.

[18] S. Wuytack, J.Ph. Diguet, F. Catthoor, and H. De

Man. Formalized methodology for data reuse

exploration for low-power hierarchical memory

mappings. IEEE Transactions on VLSI Systems,

6(4) :529537, December 1998.

[19] G.R. Goslin. A Guide to Using Field Program-

mable Gate Arrays (FPGAs) for Application-

Specic Digital Signal Processing Performance.

In High- Speed computing, Digital Signal Pro-

cessing and Filtering Using recongurable Lo-

gic, pages 321331. SPIE, 1995.

[20] A. D. Garcia. Etude sur lestimation et lopti-

misation de la consommation de puissance des

circuits logiques programmables du type FPGA.

PhD thesis, Ecole Nationale Suprieure des T-

lcommunications, Paris, 2000.

[21] K. K. W. Poon. Power Estimation For Field Pro-

grammable Gate Arrays. Masters thesis, Univer-

sity of British Columbia, 2002.

[22] L. Shang, A. S. Kaviani, and K. Bathala. Dy-

namic power consumption in Virtex-II FPGA

family. In International Symposium on Field-

Programmable Gate Arrays, pages 157164,

2002.

[23] E. Kusse. Analysis and Circuit Design for Low

Power Programmable Logic Modules. Masters

thesis, University of California, Berkeley, 1997.

[24] Xilinx Inc. FPGA Conguration Guidelines,

XAPP090, November 1997.

[25] Altera. Conguring APEX20k, Flex10k and

Flex6000 Devices, A.N. 116, May 2000.

[26] J. Villarreal, D. Suresh, G. Stitt, F. Vahid, and

W. Najjar. Improving Software performance with

Congurable Logic. Design Automation for Em-

bedded Systems, 7(4) :325339, November 2002.

[27] Xilinx Inc. CoolRunner-II CPLD Family, March

2003.

[28] I. Brynjolfson and Z. Zilic. FPGA clock manage-

ment for lowpower applications. In International

Symposium on Field programmable gate arrays,

page 219, 2000.

[29] Xilinx Inc. VIRTEX2 1.5V Series Field Program-

mable Gate Arrays, July 2001.

[30] V. George. Low Energy Field-Programmable

Gate Array. PhD thesis, University of Califor-

nia, Berkeley, 2000.

[31] A. Tisserand, P. Marchal, and C. Piguet. An

on-line arithmetic based FPGA for low-power

custom computing. In International Work-

shop on Field Programmable Logic and Applica-

tions, pages 264273. Lecture notes in Computer

Science 1673, August/September 1999.

[32] G. C. Cardarilli, A. Del Re, A. Nannarelli, and

M. Re. Residue Number System Recongurable

Datapath. In International Symposium on Cir-

cuits and Systems, pages 756759, May 2002.

[33] C.-S. Chen, T. Hwang, and C. L. Liu. Low po-

wer FPGA design : A re-engineering approach.

In Conference on Design Automation (DAC-97),

pages 656661, NY, USA, June 913 1997.

[34] G. Sutter, E. Todorovich, S. Lopez-Buedo, and

E. Boemo. Low-power FSMs in FPGA : En-

coding alternatives. Lecture Notes in Computer

Science, 2451 :363370, 2002.

[35] Altera. Stratix FPGA Family, December 2002.

[36] U. Meyer-Baese, J. Ramrez, and A. Garca. Low

power high speed algebraic integer frequency

sampling lters using FPLDs. In International

Workshop on Field Programmable Logic and Ap-

plications, pages 897904, Montpellier, France,

September 2002. Lecture Notes in Computer

Science 2348.

[37] D. Chillet, D. Saille, and O. Sentieys. Conception

de hirachies mmoires faible consommation. In

Confrence FTFC, 2003.

[38] Carl Ebeling, Darren C. Cronquist, and Paul

Franklin. RaPiD - Recongurable Pipelined Da-

tapath. In International Workshop on Field Pro-

grammable Logic and Applications, pages 126

135, Darmstadt, September 1996. Lecture notes

in Computer Science 1142.

[39] E. I. Boemo, S. Lpez-Buedo, and J. M. Me-

neses. Some Experiments About Wave Pipeli-

ning on FPGAs. IEEE Trans on Very Large Scale

Integration Systems, 6(2) :232237, June 1998.

[40] S. C. Goldstein, H. Schmit, M. Budiu, S. Ca-

dambi, M. Moe, and R. R. Taylor. PipeRench :

A Recongurable Architecture and Compiler.

IEEE Computer, 33(4), April 2000.

[41] S. Choi, R. Scrofano, V. Prasanna, and J.W. Jang.

Energy-Efcient Signal Processing Using FP-

GAs. In International Symposium on Field Pro-

grammable Gate Arrays, pages 225234, Monte-

rey, USA, February 2003.

[42] P. Bertin, D. Roncin, and J. Vuillemein. Introduc-

tion to programmable active memories. In Sys-

tolic Array Processor, pages 301309. Prentice

Hall, 1989.

[43] S. Park and W. Burleson. Reconguration for po-

wer saving in real-time motion estimation. In In-

ternational Conference on Acoustics, Speech and

Signal Processing, pages 30373040, May 1997.

[44] S. Park and W. Burleson. Conguration cloning :

Exploiting regularity in dynamic DSP architec-

tures. In International Symposium on Field Pro-

grammable Gate Arrays, pages 8189, February

1999.

[45] A. Abnous and J. Rabaey. Ultra low-power spe-

cic multimedia processors. 459468, VLSI Si-

gnal Processing IX, November 1996.

Das könnte Ihnen auch gefallen

- Activite 2ndDokument31 SeitenActivite 2ndJérôme KadjaNoch keine Bewertungen

- CPST 146Dokument25 SeitenCPST 146sirovic90Noch keine Bewertungen

- Manuel D'utilisation RDSDokument17 SeitenManuel D'utilisation RDSAndreiNoch keine Bewertungen

- Instrumentation Et Acquisition de Données MétéorologiquesDokument0 SeitenInstrumentation Et Acquisition de Données MétéorologiquesjboncoinNoch keine Bewertungen

- CHAPITRE I-VpdfDokument12 SeitenCHAPITRE I-VpdfIkhlas MeddahNoch keine Bewertungen

- SYSTEME - FicheDokument2 SeitenSYSTEME - Fichekenza boufamaNoch keine Bewertungen

- StallingsChap4Cache NASRO@Dokument36 SeitenStallingsChap4Cache NASRO@api-3746044Noch keine Bewertungen

- TD 2Dokument8 SeitenTD 2MH INA KAHIYEHNoch keine Bewertungen

- Sfo Chap I - 2021-1Dokument99 SeitenSfo Chap I - 2021-122bw023Noch keine Bewertungen

- Information D'un Post de TravailDokument8 SeitenInformation D'un Post de TravailAbdellah ChadidNoch keine Bewertungen

- Rapport de LDokument11 SeitenRapport de Lchaimae aznagueNoch keine Bewertungen

- Ch7 MemoiresDokument52 SeitenCh7 MemoiressinchicovichNoch keine Bewertungen

- 5385c78f1a756 PDFDokument18 Seiten5385c78f1a756 PDFRihab HrmNoch keine Bewertungen

- C Bascules DDokument5 SeitenC Bascules DA.HoussainNoch keine Bewertungen

- 32 Step 7blocsDokument29 Seiten32 Step 7blocsامة الرحمانNoch keine Bewertungen

- Concours de PassageDokument4 SeitenConcours de PassageDépart info IAHFNoch keine Bewertungen

- 16-Structure Materielle Et Fonctionnement D'un APIDokument7 Seiten16-Structure Materielle Et Fonctionnement D'un APIDan EkraNoch keine Bewertungen

- Chapitre 3 (N)Dokument12 SeitenChapitre 3 (N)lewis kingNoch keine Bewertungen

- Chap 4 - BasculesDokument14 SeitenChap 4 - BasculesAdam Ait FarsNoch keine Bewertungen

- Correction TP Gestion Des DisquesDokument9 SeitenCorrection TP Gestion Des Disquesmohamedaziz.theiriNoch keine Bewertungen

- TP1 StorageDokument2 SeitenTP1 StorageMohamed AnnaniNoch keine Bewertungen

- Yosra Zaghden 6Dokument19 SeitenYosra Zaghden 6Yosra ZaghdeneNoch keine Bewertungen

- Architecture Dun Micro OrdinateurDokument5 SeitenArchitecture Dun Micro OrdinateurmaherhamdiNoch keine Bewertungen

- Fiches de Progression Gso EsfDokument31 SeitenFiches de Progression Gso EsfSali MadiNoch keine Bewertungen

- Chapitre - 5 - Gestion de Mémoire PDFDokument34 SeitenChapitre - 5 - Gestion de Mémoire PDFImad EL IDRISSINoch keine Bewertungen

- OrdStrApp2010 Chap1Dokument79 SeitenOrdStrApp2010 Chap1Hind BAHRINoch keine Bewertungen

- Chapitre2 Système A MicroprocesseurDokument11 SeitenChapitre2 Système A MicroprocesseurÑar ĎjesNoch keine Bewertungen

- S5S7 FDokument148 SeitenS5S7 Felj_medNoch keine Bewertungen

- SystemeDokument6 SeitenSystemeyassNoch keine Bewertungen

- Les Elements de La Performance D'un OrdinateurDokument7 SeitenLes Elements de La Performance D'un Ordinateurits.nathanNoch keine Bewertungen