Beruflich Dokumente

Kultur Dokumente

HW 1

Hochgeladen von

peeyush_tapadiyaCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

HW 1

Hochgeladen von

peeyush_tapadiyaCopyright:

Verfügbare Formate

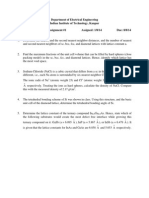

EE 212 FALL 09-010

HOMEWORK ASSIGNMENT #1

ASSIGNED: THURSDAY SEPT. 24

DUE: THURSDAY OCT. 1

ANSWER SHEET

Reading Assignment: Chapters 1 and 2 in the text.

#1. Spend 30 min or so scanning the information in the 2007 ITRS Executive Summary

(on the class website or at the website given in the class notes). You dont need to

turn anything in for this HW problem.

The next two problems are meant to review some basic concepts of semiconductor

materials. This material was not covered in class but is in Chapter 1 in the text. We

will use these basic concepts throughout the quarter.

#2. A silicon wafer is contaminated with gold atoms to a density of 10

15

cm

-3

. Au

atoms in silicon can act as either donors or acceptors. E

D

and E

A

levels exist for the

Au and are both close to the middle of the silicon bandgap. Two regions on the wafer

are also doped respectively with:

i) 1x10

18

cm

-3

Boron atoms

ii) 5x10

17

cm

-3

Arsenic atoms

B As

Au

a) Determine the resistivity of each region at 300 K. You can use Fig. 1.18 in the text.

Explain how the Au behaves in the N and P regions as part of your answer. Does it

act as a donor or an acceptor? (5 points)

b) Calculate the equilibrium electron and hole concentrations of each region at 300 K. (5

points).

Answer:

a) In N type material, the Fermi level will be in the upper half of the bandgap as shown

in the band diagram below. Allowed energy levels below E

F

will in general be

occupied by electrons. Thus the E

D

and E

A

levels will have electrons filling them.

This means the donor level will not have donated its electron whereas the acceptor

level will have accepted an electron. Thus the Au atoms will act as acceptors in N

type material.

Free

Electrons

Holes

E

F

E

D

E

A

E

C

E

V

In P type material, the Fermi level will be in the lower half of the bandgap. Allowed

energy levels above E

F

will in general not be occupied by electrons. Thus the E

D

and

E

A

levels will not have electrons filling them. This means the donor level will have

donated its electron whereas the acceptor level will have not accepted an electron.

Thus the Au atoms will act as donors in P type material.

However, the Au concentration is only 10

15

cm

-3

, which is much less than either the

As or B concentrations. Thus we can neglect the Au in calculating the resistivity.

Using Figure 1.18, we have:

P region: 1x10

18

cm

-3

P type doping so that resistivity 5 x 10

-2

ohm cm.

N region: 5x10

17

cm

-3

N type doping so that resistivity 3 x 10

-2

ohm cm.

b) In the P type region we have:

p = N

A

=1x10

18

cm

3

, n = n

i

2

/ p =

2.1x10

20

cm

6

1x10

18

cm

3

= 210cm

3

and in the N type region we have:

n = N

D

= 5x10

17

cm

3

, p = n

i

2

/ n =

2.1x10

20

cm

6

5x10

17

cm

3

= 420cm

3

#3. a). 1.9 in the text. A silicon diode has doping concentrations on the N and P sides

of N

D

= 1 x 10

19

cm

-3

and of N

A

= 1 x 10

15

cm

-3

. Calculate the process temperature

at which each of the two sides of the diode become intrinsic. (Intrinsic is defined

as n

i

= N

D

or N

A

.) (Note that in Eqn. 1.4, 3.1 should be 3.9 - see corrections to the

book on the class website.) (5 points)

b). Repeat Problem 1.9 for Ge. You can use Figure 1.16 in the text. If you wanted

to have the diode in Problem 1.9 operate in a high temperature environment (say

150 C) would you choose Si or Ge as the material? Why? (5 points)

Answer:

a). Each side of the diode will become intrinsic at the temperature at which n

I

= N

D

or

N

A

. We can estimate these temperatures by looking at the graph in Fig. 1-16. From

the graph, the N side of the diode will become intrinsic around 1400K or 1125C.

The P side will become intrinsic at a lower temperature since N

A

is smaller than N

D

.

From the figure, the P side becomes intrinsic at about 500K or 225C.

More accurately, we solve Eqn. 1.4 to find the exact temperature. Thus

n

i

= 3.9x10

16

T

3/ 2

exp

0.605eV

kT

Setting n

I

= 10

19

cm

-3

and 10

15

cm

-3

respectively, and solving by iteration, we find

that the N side becomes intrinsic at about 1335K = 1062C and the P side becomes

intrinsic at about 535K = 262C.

b). For Ge, the n

I

values are much higher at any given temperature because the

material bandgap is smaller than it is in silicon. From Fig. 1.16, n

I

in Ge is roughly 1

x 10

15

cm

-3

at 400K or 125C and n

I

in Ge is roughly 1 x 10

19

cm

-3

at 900K or

625C. For operation of the diode at high temperature, Si would be a better choice

because Ge becomes intrinsic at a lower T. Once the material becomes intrinsic, the

doping does not matter and the electrical properties will change significantly with T.

#4. Problem 2.2 in the text. During the 1970s, the dominant logic technology was

NMOS as described briefly in Chapter 1. A cross-sectional view of this

technology is shown below (see also Figure 1-33). The depletion mode device is

identical to the enhancement mode device except that a separate channel

implant is done to create a negative threshold voltage. Design a plausible

process flow to fabricate such a structure, following the ideas of the CMOS

process flow in this chapter. You do not have to include any quantitative

process parameters (times, temperatures, doses etc.) Your answer should be

given in terms of a series of sketches of the structure after each major process

step, like the figures in Chapter 2. Briefly explain your reasoning for each step

and the order you choose to do things.

P P

N

+

N

+

N

+

P

P

N

N

+

Depletion Transistor Enhancement Transistor

Answer:

We can follow many of the process steps used in the CMOS process flow in

Chapter 2. The major differences are that only NMOS devices are required (2

different threshold voltages however), and there is a buried contact connecting the

poly gate of the depletion device to the source region of that device.

P

-

SiO

2

Si

3

N

4

Photoresist

P

+

Following initial cleaning, an SiO

2

layer is thermally grown on the silicon substrate.

A Si

3

N

4

layer is then deposited by LPCVD. Photoresist is spun on the wafer to

prepare for the first masking operation.

P

Mask #1 patterns the photoresist. The Si

3

N

4

layer is removed where it is not

protected by the photoresist by dry etching.

P

P Implant

Boron Boron

A boron implant prior to LOCOS oxidation increases the substrate doping locally

under the field oxide to minimize field inversion problems.

P

P P

During the LOCOS oxidation, the boron implanted regions diffuse ahead of the

growing oxide producing the P doped regions under the field oxide. The Si

3

N

4

is

stripped after the LOCOS process.

P

P P

As or Phos

N

Mask #2 is used for the the threshold shifting implant for the depletion transistors.

An N type dopant is implanted.

P

P P

B

P N

Mask #3 is used to mask the threshold shifting implant for the enhancement

transistors. A P type dopant is implanted.

P

P P

P N

After etching back the thin oxide to bare silicon, the gate oxide is grown for the

MOS transistors.

P

P P

P N

Mask #4 is used to provide the buried contact. The gate oxide is etched where the

poly needs to contact the silicon.

P

P P

P N

A layer of polysilicon is deposited. Ion implantation of an N type dopant follows

the deposition to heavily dope the poly.

P

P P

P N

Photoresist is applied and mask #5 is used to define the regions where MOS gates

are located. The polysilicon layer is then etched using plasma etching.

P

P P N

+

Implant

Arsenic

P N

Arsenic is implanted to form the source and drain regions. Note that this can be

unmasked because there are only NMOS transistors on the chip.

P

P P

N

+

N

+

N

+ P N

N

+

A final high temperature drive-in activates all the implanted dopants and diffuses

junctions to their final depth. The N doping in the poly outdiffuses to provide the

buried contact.

P

P P

N

+

N

+

N

+

P

N

N

+

A conformal SiO

2

layer is deposited by LPCVD.

P

P P

N

+

N

+

N

+

P

N N

+

Mask #6 is used to define the contact holes.

P

P P

N

+

N

+

N

+

P N N

+

Aluminum is deposited on the wafer.

P P

N

+

N

+

N

+

P

P

N

N

+

Mask #7 is used to pattern the aluminum. After stripping the resist, the structure is

finished to the point shown in the cross-section we started with. In actual practice

an additional deposition of a final passivation layer and an additional mask (#8)

would be needed to open up the regions over the bonding pads.

Das könnte Ihnen auch gefallen

- Cswip 3.2.2 Questions and AnswersDokument8 SeitenCswip 3.2.2 Questions and AnswersZakirUllah0% (1)

- AS 404 – STEEL AND TIMBER DESIGN CODEDokument4 SeitenAS 404 – STEEL AND TIMBER DESIGN CODEJoshua VicenteNoch keine Bewertungen

- PFA Coating PFA Film - Teflon ™ PFADokument7 SeitenPFA Coating PFA Film - Teflon ™ PFAmladen lakicNoch keine Bewertungen

- MOS Integrated Circuit DesignVon EverandMOS Integrated Circuit DesignE. WolfendaleNoch keine Bewertungen

- Abstract AlgebraDokument438 SeitenAbstract AlgebraThomas HNoch keine Bewertungen

- Solns 4Dokument14 SeitenSolns 4ramprakash_rampelliNoch keine Bewertungen

- Assignment 3Dokument1 SeiteAssignment 3vatsaljain0709Noch keine Bewertungen

- Introduction To Cmos Circuits: Unit IiDokument48 SeitenIntroduction To Cmos Circuits: Unit Iiarun14089Noch keine Bewertungen

- Semiconductor Physics Problems 2015: A B C D E FDokument15 SeitenSemiconductor Physics Problems 2015: A B C D E Fsan san moeNoch keine Bewertungen

- Construction of A Monolithic Bipolar TransistorDokument6 SeitenConstruction of A Monolithic Bipolar TransistorsampNoch keine Bewertungen

- HW4Dokument2 SeitenHW4Saied Aly SalamahNoch keine Bewertungen

- SC Part2Dokument18 SeitenSC Part2Istiaq Ahmed AnikNoch keine Bewertungen

- Mse630 f10 Hw1 SolDokument4 SeitenMse630 f10 Hw1 SolLava Kumar BNoch keine Bewertungen

- Week 3 HWDokument3 SeitenWeek 3 HWMoazh TawabNoch keine Bewertungen

- Chapter 2: CMOS Technology: Instructor: Dr. Po-Wen Chiu (EE/NTHU)Dokument35 SeitenChapter 2: CMOS Technology: Instructor: Dr. Po-Wen Chiu (EE/NTHU)王靖堯Noch keine Bewertungen

- Jomo Kenyatta University EEE Revision QuestionsDokument9 SeitenJomo Kenyatta University EEE Revision QuestionsIAMMARKSNoch keine Bewertungen

- 143f2010 04 PDFDokument3 Seiten143f2010 04 PDFBabasrinivas GuduruNoch keine Bewertungen

- Advanced PV Technologies Assignment 1Dokument3 SeitenAdvanced PV Technologies Assignment 1Chairil ChairilNoch keine Bewertungen

- Eem212 Analog Electronics Questions 1Dokument4 SeitenEem212 Analog Electronics Questions 1AweNerviumNoch keine Bewertungen

- Lecture - 3 (ECE 4201)Dokument35 SeitenLecture - 3 (ECE 4201)imposter 29Noch keine Bewertungen

- ECE482 Homework 1 SolDokument4 SeitenECE482 Homework 1 SolsuhaaasNoch keine Bewertungen

- EEE210 (Physical Electronic)Dokument57 SeitenEEE210 (Physical Electronic)ozNoch keine Bewertungen

- Bec010 Vlsi - NotesDokument109 SeitenBec010 Vlsi - NotesFarukh ZafarNoch keine Bewertungen

- PMMD Model Questions Semiconductor PhysicsDokument4 SeitenPMMD Model Questions Semiconductor PhysicslavishNoch keine Bewertungen

- EE 105: Microelectronic Devices and Circuits: University of California at BerkeleyDokument12 SeitenEE 105: Microelectronic Devices and Circuits: University of California at BerkeleynandhakumarmeNoch keine Bewertungen

- Principles and Applications of Electrical Engineering 5th Edition Rizzoni Solutions ManualDokument39 SeitenPrinciples and Applications of Electrical Engineering 5th Edition Rizzoni Solutions Manualousleyrva9100% (16)

- EEE210 (Physical Electronic)Dokument57 SeitenEEE210 (Physical Electronic)Yavuz KaplanNoch keine Bewertungen

- Etc - Ei-Ii Final Exam Paper - 2020 - 21Dokument3 SeitenEtc - Ei-Ii Final Exam Paper - 2020 - 21ARYA RAJPUTNoch keine Bewertungen

- Physics of VLSI Devices (ECE-5018) Digital Assignment - II: M S G M S GDokument6 SeitenPhysics of VLSI Devices (ECE-5018) Digital Assignment - II: M S G M S GShreyas RaoNoch keine Bewertungen

- Lec 7,8 Modern CMOS TechnologyDokument43 SeitenLec 7,8 Modern CMOS TechnologyVikram MeenaNoch keine Bewertungen

- Tutorial 3Dokument1 SeiteTutorial 3Ma SeenivasanNoch keine Bewertungen

- Solved Problems AustraliaDokument12 SeitenSolved Problems AustraliaIsidoro VaquilaNoch keine Bewertungen

- Sheet2 DevicesDokument5 SeitenSheet2 DevicesYoussefMohamedNoch keine Bewertungen

- Mtech Vlsi TutDokument4 SeitenMtech Vlsi Tuttanuj_sharma1991Noch keine Bewertungen

- Question PaperDokument1 SeiteQuestion PaperAnkit MehtaNoch keine Bewertungen

- IIT Delhi Physics Dept tutorial on semiconductorsDokument2 SeitenIIT Delhi Physics Dept tutorial on semiconductorsSachin KhareNoch keine Bewertungen

- Electronic Devices and Circuits Part 2Dokument9 SeitenElectronic Devices and Circuits Part 2Renz Benhar Ocon BobadillaNoch keine Bewertungen

- EE3402 Linear Integrated Circuits Reg 2021 Notes (Unit I)Dokument20 SeitenEE3402 Linear Integrated Circuits Reg 2021 Notes (Unit I)Monika GNoch keine Bewertungen

- CH 1-Ch 7Dokument13 SeitenCH 1-Ch 7Eligius MartinezNoch keine Bewertungen

- Semiconductor Physics ExamDokument2 SeitenSemiconductor Physics ExamBee PNoch keine Bewertungen

- Design of BJT TransistorsDokument17 SeitenDesign of BJT TransistorsSomnium AlnuaimiNoch keine Bewertungen

- ReportDokument8 SeitenReportROMANCE FantasNoch keine Bewertungen

- Exam4 S16Dokument7 SeitenExam4 S16Alejandro PuceiroNoch keine Bewertungen

- Analog Digital Bicmos RealizationDokument63 SeitenAnalog Digital Bicmos RealizationSravana JyothiNoch keine Bewertungen

- Physics of VLSI Devices (ECE5018) - CAT-2 Solutions: Dr. Rajan Pandey Associate Professor, SENSEDokument16 SeitenPhysics of VLSI Devices (ECE5018) - CAT-2 Solutions: Dr. Rajan Pandey Associate Professor, SENSEVibha M VNoch keine Bewertungen

- Problem 4 PN JN Solar CellDokument4 SeitenProblem 4 PN JN Solar CellsagarNoch keine Bewertungen

- Assignments 1 FundamentalsofSemiconductor - 2023fallDokument3 SeitenAssignments 1 FundamentalsofSemiconductor - 2023falldjw2982274252Noch keine Bewertungen

- HW 2Dokument2 SeitenHW 2b98154Noch keine Bewertungen

- Vlsi NotesDokument11 SeitenVlsi NotesShowcase MarathiNoch keine Bewertungen

- Mock 20Xx Examinations: Paper Code NO. EN4630/ENT630Dokument14 SeitenMock 20Xx Examinations: Paper Code NO. EN4630/ENT630mohamedyahaiNoch keine Bewertungen

- MAE 536 Micro/Nano Electromechanical Systems: Yong Zhu Lecture 10 - Surface MicromachiningDokument48 SeitenMAE 536 Micro/Nano Electromechanical Systems: Yong Zhu Lecture 10 - Surface MicromachiningAnonymous 8kdwhwUNoch keine Bewertungen

- Junction Phy Tuts 2014Dokument8 SeitenJunction Phy Tuts 2014ESAU0% (1)

- NDokument5 SeitenNVyne NguyenNoch keine Bewertungen

- EE143 Lecture 18 Self-Aligned IC Process Integration TechniquesDokument35 SeitenEE143 Lecture 18 Self-Aligned IC Process Integration TechniquesNhật HoàngNoch keine Bewertungen

- Fowler Nordheim Tunneling in Thin SiO2 FilmsDokument7 SeitenFowler Nordheim Tunneling in Thin SiO2 FilmskobelkNoch keine Bewertungen

- Ass1 SolutionDokument2 SeitenAss1 SolutionJon LegaspiNoch keine Bewertungen

- EECS 130 Midterm I examDokument8 SeitenEECS 130 Midterm I examRyan GittensNoch keine Bewertungen

- P Side N SideDokument3 SeitenP Side N SideAahan JainNoch keine Bewertungen

- Homework05 SolutionsDokument2 SeitenHomework05 SolutionsAamir ZahoorNoch keine Bewertungen

- Bsapl97 REf No 2Dokument3 SeitenBsapl97 REf No 2Bukinakere SatyanarayanaNoch keine Bewertungen

- MOS Transistor DesignDokument52 SeitenMOS Transistor DesignPrakashKumarRoutNoch keine Bewertungen

- CMOS VLSI MOS Transistor CharacteristicsDokument26 SeitenCMOS VLSI MOS Transistor CharacteristicsvuaphuNoch keine Bewertungen

- Silicon Integrated Circuits: Advances in Materials and Device ResearchVon EverandSilicon Integrated Circuits: Advances in Materials and Device ResearchDawon KahngNoch keine Bewertungen

- Expt 5Dokument2 SeitenExpt 5peeyush_tapadiyaNoch keine Bewertungen

- Ass SpectraDokument4 SeitenAss Spectrapeeyush_tapadiyaNoch keine Bewertungen

- Simulate a simple resistor in Silvaco 2D for EE 698I assignmentDokument1 SeiteSimulate a simple resistor in Silvaco 2D for EE 698I assignmentpeeyush_tapadiyaNoch keine Bewertungen

- EE-611 Lab Report Fabrication and Characterization of Organic Solar CellDokument6 SeitenEE-611 Lab Report Fabrication and Characterization of Organic Solar Cellpeeyush_tapadiyaNoch keine Bewertungen

- Department of Electrical Engineering Indian Institute of Technology, Kanpur EE 618 Home Assignment #1 Assigned: 1/8/14 Due: 8/8/14Dokument1 SeiteDepartment of Electrical Engineering Indian Institute of Technology, Kanpur EE 618 Home Assignment #1 Assigned: 1/8/14 Due: 8/8/14peeyush_tapadiyaNoch keine Bewertungen

- CDMADokument32 SeitenCDMApeeyush_tapadiyaNoch keine Bewertungen

- 2007 World Final Problem Set 11Dokument20 Seiten2007 World Final Problem Set 11Yousef AburawiNoch keine Bewertungen

- Semiconductor Device Current Density and Potential ProfilesDokument4 SeitenSemiconductor Device Current Density and Potential Profilespeeyush_tapadiyaNoch keine Bewertungen

- Linux vs. Windows Server: A Cost & Security ComparisonDokument10 SeitenLinux vs. Windows Server: A Cost & Security Comparisonpeeyush_tapadiyaNoch keine Bewertungen

- Session July-Nov 2012: Academic Calender For Ii, Iii, Iv Be./B.Pharm./B.E. (PTDC) Ii, Iii Mca & PGDokument2 SeitenSession July-Nov 2012: Academic Calender For Ii, Iii, Iv Be./B.Pharm./B.E. (PTDC) Ii, Iii Mca & PGpeeyush_tapadiyaNoch keine Bewertungen

- BE Scheme & SyllbsDokument52 SeitenBE Scheme & Syllbspeeyush_tapadiyaNoch keine Bewertungen

- Signal and SystemDokument6 SeitenSignal and Systempeeyush_tapadiyaNoch keine Bewertungen

- IES Emt PaperDokument5 SeitenIES Emt Paperpeeyush_tapadiyaNoch keine Bewertungen

- Linkin Park-Live in TexasDokument19 SeitenLinkin Park-Live in Texaspeeyush_tapadiyaNoch keine Bewertungen

- Agarwal A., Lang J. - Foundations of Analog and Digital Electronic Circuits - Supplemental Sections and Examples - 2005Dokument136 SeitenAgarwal A., Lang J. - Foundations of Analog and Digital Electronic Circuits - Supplemental Sections and Examples - 2005შაქრო ტრუბეცკოიNoch keine Bewertungen

- 7400 SeriesDokument16 Seiten7400 Seriespeeyush_tapadiyaNoch keine Bewertungen

- Touch Screen TechnologyDokument33 SeitenTouch Screen Technologypeeyush_tapadiyaNoch keine Bewertungen

- Ec 2006Dokument11 SeitenEc 2006Supriyo GangulyNoch keine Bewertungen

- STEEL BEAM WEB STIFFENER ANALYSISDokument7 SeitenSTEEL BEAM WEB STIFFENER ANALYSISNEONoch keine Bewertungen

- SS 40 Phy 14Dokument11 SeitenSS 40 Phy 14Atul VermaNoch keine Bewertungen

- Nanotechnology in Food Production - A Potential Risk or A Risky PotentialDokument27 SeitenNanotechnology in Food Production - A Potential Risk or A Risky PotentialMarcos LoredoNoch keine Bewertungen

- 10 1016@j Matchemphys 2019 05 033Dokument13 Seiten10 1016@j Matchemphys 2019 05 033Deghboudj SamirNoch keine Bewertungen

- CRIT JOURNAL Comparing finite element techniques for predicting rutting of asphaltDokument3 SeitenCRIT JOURNAL Comparing finite element techniques for predicting rutting of asphaltKristian MalauNoch keine Bewertungen

- Gibbs Thomson EquationDokument5 SeitenGibbs Thomson EquationDebasis HembramNoch keine Bewertungen

- Astm A320 PDFDokument9 SeitenAstm A320 PDFFerri AguswanNoch keine Bewertungen

- Fluid Phase Equilibria: Alena Randov A, Lidmila Bartovsk ADokument11 SeitenFluid Phase Equilibria: Alena Randov A, Lidmila Bartovsk Aanon_837143581Noch keine Bewertungen

- A Generalized Description of The Elastic Properties of NanowiresDokument6 SeitenA Generalized Description of The Elastic Properties of NanowiresHugo LivasNoch keine Bewertungen

- Introduction To Turbulence1Dokument28 SeitenIntroduction To Turbulence1Mustafa YılmazNoch keine Bewertungen

- Pe Product Finder Na EnpdfDokument6 SeitenPe Product Finder Na Enpdfshubhendra mishraaNoch keine Bewertungen

- 1 Stress Strain SMDokument39 Seiten1 Stress Strain SMsameerajuvathNoch keine Bewertungen

- Plastic Analysis Notes PDFDokument14 SeitenPlastic Analysis Notes PDFVineetha KrishnanNoch keine Bewertungen

- Polyflow Extrusion WS08 Immiscible Fluids by SpeciesDokument24 SeitenPolyflow Extrusion WS08 Immiscible Fluids by Specieswoongs73Noch keine Bewertungen

- Properties of Spider SilkDokument9 SeitenProperties of Spider SilkArifah PujiatiNoch keine Bewertungen

- Buildings Ductile For Good Seismic PerformanceDokument2 SeitenBuildings Ductile For Good Seismic PerformanceWaqas AhmedNoch keine Bewertungen

- Tutorial No.5 DMEDokument1 SeiteTutorial No.5 DMEOnkarNoch keine Bewertungen

- Corporation 100 CTC Drive Johnstown, PA 15904Dokument7 SeitenCorporation 100 CTC Drive Johnstown, PA 15904Milan JoshiNoch keine Bewertungen

- Betini 2019Dokument13 SeitenBetini 2019Jose G. Cueva CardeñaNoch keine Bewertungen

- Ultrasonic Wave Behavior at InterfacesDokument15 SeitenUltrasonic Wave Behavior at InterfaceskingstonNoch keine Bewertungen

- CH 6503 Cet IiDokument66 SeitenCH 6503 Cet IiDrVishwanatha HNNoch keine Bewertungen

- Aluminum Defects After AnodizingDokument41 SeitenAluminum Defects After AnodizingSONNoch keine Bewertungen

- Assign Chap 8Dokument3 SeitenAssign Chap 8nishedhNoch keine Bewertungen

- Slope Stability: Disiapkan Oleh T.IlyasDokument45 SeitenSlope Stability: Disiapkan Oleh T.Ilyasimmanuel evaldoNoch keine Bewertungen

- 07 Handout 1Dokument2 Seiten07 Handout 1odrhey hernandezNoch keine Bewertungen

- NE 335 Macromolecular Science 2: Reactivity RatiosDokument17 SeitenNE 335 Macromolecular Science 2: Reactivity RatiosMoeen Khan RisaldarNoch keine Bewertungen

- Sandvik SteelDokument16 SeitenSandvik Steeljohn9999_502754Noch keine Bewertungen