Beruflich Dokumente

Kultur Dokumente

Sistemas Digitais

Hochgeladen von

Rafael SousaCopyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Sistemas Digitais

Hochgeladen von

Rafael SousaCopyright:

Verfügbare Formate

UNIVERSIDADE FEDERAL DE SO CARLOS CCET

___________________________________________________________________________

UNIVERSIDADE FEDERAL DE SO CARLOS

Sistemas Digitais I ENGENHARIA ELTRICA

4o PERODO (2o SEM / 2014)

Prof. Dr.Giuseppe Antonio Cirino

RELATRIO NR. 3

PORTAS LGICAS e LGEBRA DE BOOLE

(REALIZADA EM 24 / 09 / 2014)

INTEGRANTES DO GRUPO:

NOME

RA

Luciano Nogueira

609870

Rafael Antonio de Sousa

609773

Vinicius Cunha

610712

RELATRIO ENTREGUE EM: 01 / 10 / 2014

ASSINATURA

UNIVERSIDADE FEDERAL DE SO CARLOS CCET

___________________________________________________________________________

Introduo

Circuitos Digitais so circuitos eletrnicos que funcionam como base na

lgica binria, em que toda a informao guardada e processada como zero

e um. Esses circuitos operam com tenses que se encontram em faixas

determinadas que representam o binrio, no importando o valor da tenso.

So constitudos por associaes de blocos lgicos.

O Mapa de Karnaugh um mtodo de simplificao grfico para

encontrar a equao de sada de um circuito logico na forma mais simplificada.

Esse mtodo considerado mais eficaz que a lgebra booleana, visto que

simplifica a equao visando o menor erro possvel.

UNIVERSIDADE FEDERAL DE SO CARLOS CCET

___________________________________________________________________________

Objetivos

O experimento tem como objetivo simular o funcionamento de um

elevador e controlar as funes atravs de circuitos lgicos e testar a

funcionalidade do mapa Veitch-Karnough para o circuito ABRIR e o circuito

ALARME.

UNIVERSIDADE FEDERAL DE SO CARLOS CCET

___________________________________________________________________________

Procedimentos experimentais

Este experimento consistiu em projetar o circuito de um elevador atravs

de um circuito lgico. Para desenvolvimento do circuito, criou-se quatro

entradas e duas sadas. As entradas formadas foram FT, F1, F2 e M que

representam respectivamente o trreo, primeiro andar, segundo andar e M

representa o movimento do elevador. Quando o circuito apresenta nvel lgico

1, significa que o elevador est em um respectivo andar naquele momento.

Quando o circuito apresenta nvel lgico 0, significa que o elevador est

parado. Para M = 1, o elevador esta em movimento e para M = 0, o elevador

esta parado. A partir do circuito lgico, montou-se uma tabela-verdade. Com a

tabela-verdade foi possvel reduzir as expresses de sada por meio do mapa

V-K e as expresses encontradas foram montadas na protoboard para

comparar com os valores tericos com o prtico. Os resultados encontrados

sero discutidos posteriormente.

UNIVERSIDADE FEDERAL DE SO CARLOS CCET

___________________________________________________________________________

Resultados e Discusso

Montamos um circuito lgico para controlar as funes do elevador. Ao

projetar esse circuito lgico, chegou-se a concluso que o mesmo possui

quatro entradas e duas sadas.

Circuito Lgico ABRIR.

Note que as entradas so M, FT, F1 e F2 na qual esto respectivamente

na ordem de deslocamento do elevador, trreo, primeiro e segundo andar. A

partir deste sistema, foi obtido uma tabela-verdade, que esta representada

abaixo.

UNIVERSIDADE FEDERAL DE SO CARLOS CCET

___________________________________________________________________________

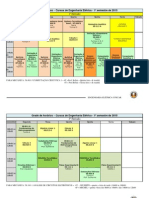

Tabela verdade Abrir.

Na sada abrir, obteve-se alguns valores X, isso significa que uma

situao que teoricamente pode acontecer, mas na situao real do elevador

ela considerada impossvel, no entanto, o elevador pode estar em dois

lugares ao mesmo tempo e quando isso ocorre, o alarme dispara

representando um nvel lgico 1.

Os Mapas de Karnaugh esto representados abaixo tanto para valores

tericos quanto para medidos.

Mapa de Karnaugh da sada ABRIRTEO

UNIVERSIDADE FEDERAL DE SO CARLOS CCET

___________________________________________________________________________

Mapa de Karnaugh da sada ALTEO

Mapa de Karnaugh da sada ABRIRMED

UNIVERSIDADE FEDERAL DE SO CARLOS CCET

___________________________________________________________________________

Mapa de Karnaugh da sada ALMED

O circuito referente ao alarme esta representado abaixo, juntamente com

a tabela verdade do alarme.

Circuito logico ALARME

UNIVERSIDADE FEDERAL DE SO CARLOS CCET

___________________________________________________________________________

Tabela verdade Alarme

UNIVERSIDADE FEDERAL DE SO CARLOS CCET

___________________________________________________________________________

Concluso

O experimento realizado na pratica 3 foi satisfatrio. Podemos concluir

que tanto a sada ABRIR quanto a sada AL estavam operando de maneira

correta, no entanto o valor encontrado para a sada do alarme simulado foi um

pouco diferente do encontrado para os valores tericos. Os Componentes

utilizados

na

prtica

funcionaram

como

favorecendo os resultados no experimento.

seus

respectivos

datasheet,

Das könnte Ihnen auch gefallen

- Regimento Cursos Graduacao ConsUniDokument115 SeitenRegimento Cursos Graduacao ConsUniRafael SousaNoch keine Bewertungen

- Lista de Exercícios 06 - Junção P-N e Dispositivos SemicondutoresDokument2 SeitenLista de Exercícios 06 - Junção P-N e Dispositivos SemicondutoresRafael SousaNoch keine Bewertungen

- Mapa Mercado de Trabalho EstagiÁrea Segredos Dos Processos Seletivos PDFDokument9 SeitenMapa Mercado de Trabalho EstagiÁrea Segredos Dos Processos Seletivos PDFRafael SousaNoch keine Bewertungen

- Aula 07 - TeoriaDokument41 SeitenAula 07 - TeoriaRafael SousaNoch keine Bewertungen

- Lista de Exercícios 06 - Junção P-N e Dispositivos SemicondutoresDokument2 SeitenLista de Exercícios 06 - Junção P-N e Dispositivos SemicondutoresRafael SousaNoch keine Bewertungen

- Aula 08 - TeoriaDokument19 SeitenAula 08 - TeoriaRafael SousaNoch keine Bewertungen

- Aula 02 - TeoriaDokument46 SeitenAula 02 - TeoriaRafael SousaNoch keine Bewertungen

- Lista2 PDFDokument4 SeitenLista2 PDFRafael SousaNoch keine Bewertungen

- 2017 A1 To Grad ApresentacaoDokument27 Seiten2017 A1 To Grad ApresentacaoRafael SousaNoch keine Bewertungen

- Lista 1Dokument5 SeitenLista 1Rafael SousaNoch keine Bewertungen

- Aula 5 - Transistores de Efeito de Campo Resposta em FrequenciaDokument20 SeitenAula 5 - Transistores de Efeito de Campo Resposta em FrequenciaRafael SousaNoch keine Bewertungen

- 2017 A1 To Grad ApresentacaoDokument27 Seiten2017 A1 To Grad ApresentacaoRafael SousaNoch keine Bewertungen

- SistCont1 Aula8 2Dokument1 SeiteSistCont1 Aula8 2Rafael SousaNoch keine Bewertungen

- Lista ProvaDokument9 SeitenLista ProvaRafael SousaNoch keine Bewertungen

- Notas Inst. Elétricas - 2014 (Incompleto)Dokument2 SeitenNotas Inst. Elétricas - 2014 (Incompleto)Rafael SousaNoch keine Bewertungen

- Horario 1º Semestre de 2015 - V8Dokument5 SeitenHorario 1º Semestre de 2015 - V8Rafael SousaNoch keine Bewertungen

- Aula 1 - Transistores de Efeito de Campo JFET PDFDokument40 SeitenAula 1 - Transistores de Efeito de Campo JFET PDFRafael SousaNoch keine Bewertungen

- U1S2 - Atividade Diagnóstica PDFDokument2 SeitenU1S2 - Atividade Diagnóstica PDFPedro Curty0% (1)

- Rt765e-2 Om Ctrl513-02 Brazilian PortugueseDokument180 SeitenRt765e-2 Om Ctrl513-02 Brazilian PortugueseKelly RibeiroNoch keine Bewertungen

- Modulo de Experiencias de OOODokument25 SeitenModulo de Experiencias de OOOFelix Pessa MuaniuaNoch keine Bewertungen

- Correção Teste 7Dokument3 SeitenCorreção Teste 7Raquel GasparNoch keine Bewertungen

- Exames EF de Anos Anteriores e Sua Resolução PDFDokument179 SeitenExames EF de Anos Anteriores e Sua Resolução PDFFlávia SilvaNoch keine Bewertungen

- AOB508-G21 Controlador Temperatura ReléDokument8 SeitenAOB508-G21 Controlador Temperatura ReléCaio CesarNoch keine Bewertungen

- Lista de Livros Recomendados Por Mortimer J. AdlerDokument24 SeitenLista de Livros Recomendados Por Mortimer J. AdlerAnderson Claiton Koberstein100% (1)

- O Hexagrama SLIDESDokument117 SeitenO Hexagrama SLIDESgayNoch keine Bewertungen

- 2-APOSTILA - Módulo - Tendências Pedagógicas - 40hDokument60 Seiten2-APOSTILA - Módulo - Tendências Pedagógicas - 40hAntonio José AlvesNoch keine Bewertungen

- SA2 Template IEP ALUNODokument5 SeitenSA2 Template IEP ALUNOneville trindade da silvaNoch keine Bewertungen

- Aula EletroquimicaDokument65 SeitenAula EletroquimicaCarol LimaNoch keine Bewertungen

- Bimestral de FísicaDokument2 SeitenBimestral de FísicawagnerNoch keine Bewertungen

- Impermeabilização Com Membrana PoliureiaDokument9 SeitenImpermeabilização Com Membrana PoliureiaLéo RomeroNoch keine Bewertungen

- Apostila EstatisticaDokument161 SeitenApostila EstatisticaGabriela CasagrandeNoch keine Bewertungen

- Analise Do Reator Tipo Tanque Agitado CSTRDokument6 SeitenAnalise Do Reator Tipo Tanque Agitado CSTRIsaias QueirozNoch keine Bewertungen

- Relatividade RestritaDokument15 SeitenRelatividade RestritaRanderson VictorNoch keine Bewertungen

- Alimentos Brasileiros e Suas PorçõesDokument19 SeitenAlimentos Brasileiros e Suas PorçõesLisiane PerinNoch keine Bewertungen

- A2742 8p 8Dokument16 SeitenA2742 8p 8Eleu Eduardo Mehret Scorsin Filho100% (2)

- Trabalho de GADokument4 SeitenTrabalho de GAninho12345Noch keine Bewertungen

- CruzadaDokument1 SeiteCruzadaCarol MonksNoch keine Bewertungen

- Dia 1 UFRGSDokument27 SeitenDia 1 UFRGSGui S SchoenardieNoch keine Bewertungen

- Processo Geométrico de PonceletDokument7 SeitenProcesso Geométrico de PonceletPatrick QueirozNoch keine Bewertungen

- Cabo - Mondego - BiolgiaDokument18 SeitenCabo - Mondego - BiolgiaJoão Paulo NunesNoch keine Bewertungen

- Trabalho Pós VEH - José Martinho - Modulo Segurança - Adriel Maia Do AmaralDokument33 SeitenTrabalho Pós VEH - José Martinho - Modulo Segurança - Adriel Maia Do AmaralAdrielNoch keine Bewertungen

- Informativa-Movimento Placas LitosféricasDokument2 SeitenInformativa-Movimento Placas LitosféricasAna Rita Rainho100% (13)

- Os 15 Mandamentos Da Direção de Arte - Design - Alumni ESPMDokument8 SeitenOs 15 Mandamentos Da Direção de Arte - Design - Alumni ESPMLeandro CavalheiroNoch keine Bewertungen

- Informações de Auxilio Da Tomador de Amostra Sonda ObliquaDokument3 SeitenInformações de Auxilio Da Tomador de Amostra Sonda ObliquaAndré MariaNoch keine Bewertungen

- TCC BerneDokument15 SeitenTCC BerneRudan Paraizo GarciaNoch keine Bewertungen

- DistanciaDokument4 SeitenDistanciaLuciene SilvaNoch keine Bewertungen

- Princípio de BernoulliDokument14 SeitenPrincípio de BernoulliFernandoSilvaNoch keine Bewertungen