Beruflich Dokumente

Kultur Dokumente

Codificador 16 A 4

Hochgeladen von

Camilo A. InfanteOriginalbeschreibung:

Originaltitel

Copyright

Verfügbare Formate

Dieses Dokument teilen

Dokument teilen oder einbetten

Stufen Sie dieses Dokument als nützlich ein?

Sind diese Inhalte unangemessen?

Dieses Dokument meldenCopyright:

Verfügbare Formate

Codificador 16 A 4

Hochgeladen von

Camilo A. InfanteCopyright:

Verfügbare Formate

Dpto.

de Sistemas Electrnicos y de Control

TEMA 3

CIRCUITOS

COMBINACIONALES

Dpto. de Sistemas Electrnicos y de Control

CIRCUITOS COMBINACIONALES

Objetivos:

Conocer las principales caractersticas de un

sistema combinacional y los convenios utilizados

para representar seales de entrada/salida y

control.

Comprender la funcin lgica y algunas de las

aplicaciones bsicas de los siguientes circuitos

combinacionales:multiplexores,codificadores,

decodificadores,demultiplexores,

generadorescomprobadores de paridad,sumadores y restadores.

Manejar los CIs combinacionales que proporcionan

los fabricantes haciendo uso de la descripcin, tabla

de verdad y cronogramas facilitados.

Aplicar la metodologa de anlisis

diagramas de bloques funcionales.

utilizando

Adquirir destreza en el montaje de aplicaciones con

circuitos combinacionales.

Entender la informacin que se facilita en los

catlogos de los diferente circuitos combinacionales

integrados.

III-0

Dpto. de Sistemas Electrnicos y de Control

CIRCUITOS COMBINACIONALES

Contenidos:

Multiplexores.

Codificadores.

Decodificadores y Demultiplexores.

Decodificadores excitadores.

Generadores-comprobadores de paridad.

Comparadores binarios.

Circuitos sumadores.

Circuitos restadores.

Bibliografa:

Fundamentos de Sistemas Digitales (7 edicin).

Captulo 6.

Thomas L. Floyd.

Edit: Prentice Hall.

III-1

Dpto. de Sistemas Electrnicos y de Control

SISTEMAS COMBINACIONALES

CONVENIOS PARA SALIDAS Y ENTRADAS

DE CONTROL

A

B

C

E

F

Activas a Nivel Bajo (cero lgico)

Activas a Nivel Alto (uno lgico)

REPRESENTACION

0

1

2

3

4

5

6

7

A0

A1

A2

EO

ENABLE: HABILITA EL FUNCIONAMIENTO

CUANDO ES ACTIVO

DISABLE: DESHABILITA EL FUNCIONAMIENTO

CUANDO ES ACTIVO

III-2

Dpto. de Sistemas Electrnicos y de Control

SISTEMAS COMBINACIONALES

LINEAS

DE

ENTRADA

SISTEMA

COMBINACIONAL

LINEAS

DE

SALIDA

ENABLE

LINEAS DE CONTROL

DEFINICION:

Tabla de Verdad

Cronograma

E3 E2 E1 E0

S1 S0

1 X X

0 1 1

0 X 0

0 X 1

0 X 0

Z

1

0

1

1

X

0

0

0

1

Z

0

1

1

1

L5

t

L

t

L3

t

L

t

L0

t

Ecuacin Lgica Salidas:

S1 = E3 E 2 + E 0 E1

S0 = ( E 2 + E 0 ) ( E1 + E 0 )

III-3

Dpto. de Sistemas Electrnicos y de Control

MULTIPLEXORES

N

ENTRADA DE

MULTIPLEXOR

DATOS

ENTRADA DE

ENTRADAS DE

ENABLE

SELECCION

N = 2P

SALIDA

ENTRADAS DE

SELECCION

III-4

SALIDA

Dpto. de Sistemas Electrnicos y de Control

MULTIPLEXOR CON ENTRADA DE VALIDACION

SELECCION VALIDACION

ENTRADAS

S1

S0

E

I0

I1

I2

I3

X

X

L

X

X

X

X

SALIDA

Z

L

I0

I0

I1

I1

I2

I2

I3

I3

Z = E(S1S0I0+ S1S0I1 + S1S0I2 + S1S0I3)

E

I0

I1

I2

I3

S1 S0

III-5

Dpto. de Sistemas Electrnicos y de Control

74153.- DOBLE MULTIPLEXOR 4:1

FUNCTION TABLE

INPUTS

SELECT

DATA

STROBE

G

OUTPUT

Y

C0

C1

C2

C3

X

X

X

H

H

L

H

X

X

X

X

H

X

X

L

L

L

H

L

Select inputs A and B are common to both sections.

1G

1C0

1C1

1

6

5

7

Data 1

1C2

1C3

B

1Y

3

2

Select

A

2C0

2C1

Data 2

2C2

2C3

2G

14

10

11

9

12

13

15

III-6

2Y

Dpto. de Sistemas Electrnicos y de Control

EXTENSION DE LA CAPACIDAD

DE UN MULTIPLEXOR

MULTIPLEXOR DE 32 ENTRADAS:

SE NECESITAN 5 ENTRADAS DE DIRECCIONAMIENTO

4 MULTIPLEXORES DE 8 ENTRADAS

1 MULTIPLEXOR DE 4 ENTRADAS

ENTRADAS

1

8:1

8

8:1

16

4:1

17

8:1

24

25

8:1

32

S2 S1S0S4S3

III-7

SALIDA

Dpto. de Sistemas Electrnicos y de Control

EJEMPLO DE MULTIPLEXORES:

SE PRETENDE MULTIPLEXAR 4

FUENTES DE DATOS DE 4 BITS CADA

UNA, HACIA UN RECEPTOR. REALIZAR

EL CIRCUITO EMPLEANDO EL C.I. 74153.

CUANTOS MULTIPLEXORES

SERAN NECESARIOS ?

CUANTAS ENTRADAS SE USARAN

DE DICHOS MULTIPLEXORES ?

III-8

Dpto. de Sistemas Electrnicos y de Control

CODIFICADORES

EXCITANDO UNA ENTRADA SE GENERA UN

CODIGO DE N BITS EN LAS SALIDAS

M

ENTRADAS

CODIFICADOR

ENABLE

M2N

III-9

N

SALIDAS

Dpto. de Sistemas Electrnicos y de Control

CODIFICADOR CON PRIORIDAD

74148 (8 LINEAS A 3 LINEAS CON PRIORIDAD)

FUNCTION TABLE

INPUTS

EI

OUTPUTS

A2

A1

A0

GS

EO

H

10

15

14

1

11

EI

A0

13

7

5

GS

12

EO

A1

4

6

III-10

A2

Dpto. de Sistemas Electrnicos y de Control

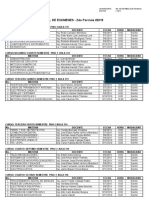

AMPLIACION: CODIFICADOR 16:4

16-Line Data (active low)

0 1 23

4 5 67

8 9 10 11 12 13 14 15

0 1 23

4 5 67

EI

0 1 23

'148

EO A0

A1

4 5 67

Enable

(active low)

EI

'148

A2 GS

EO

A0

A1

A2

GS

'08

01

Priority Flag

(active low)

Encoded Data (active low)

16-Line Data (active low)

0 1 23

4 5 67

8 9 10 11 12 13 14 15

0 1 23

4 5 67

EI

0 1 23

'148

EO A0

A1

4 5 67

Enable

(active low)

EI

'148

A2 GS

EO

A0

A1

A2

GS

'00

01

Priority Flag

(active high)

Encoded Data (active high)

III-11

Dpto. de Sistemas Electrnicos y de Control

DECODIFICADOR

Ejemplo de un decodificador de dos entradas y cuatro salidas

I0

DECODIFICADOR

I1

A0

A1

A2

A3

Diagrama lgico:

A0

E

A1

A2

I0

A3

I1

Tabla de funcionamiento:

E

1

0

0

0

0

I1

X

0

0

1

1

I0

X

0

1

0

1

A0 A1 A2 A3

1

1

1

1

0

1

1

1

1

0

1

1

1

1

0

1

1

1

1

0

III-12

Dpto. de Sistemas Electrnicos y de Control

DEMULTIPLEXOR

Ejemplo de un demultiplexor de cuatro salidas:

Salidas

Entrada

DEMULTIPLEXOR

DE 4 CANALES

Diagrama lgico:

I1

A0

A1

A2

A3

I0

Entradas de control

A0

E

A1

A2

I0

A3

I1

Tabla de funcionamiento:

E

1

0

0

0

0

I1

X

0

0

1

1

I0

X

0

1

0

1

A0 A1 A2 A3

1

1

1

1

0

1

1

1

1

0

1

1

1

1

0

1

1

1

1

0

III-13

Dpto. de Sistemas Electrnicos y de Control

74LS139. DUAL 1-OF-4 DECODER/DEMULTIPLEXER

FUNCTION TABLE

INPUTS

OUTPUTS

SELECT

ENABLE

G

Y0

Y1

Y2

Y3

logic diagram

4

Enable 1G

6

1A

Select

Inputs

1B

1Y0

1

1Y1

1Y2

2

7

1Y3

Data

Outputs

12

Enable 2G

11

10

2A

Select

Inputs

2B

2Y0

15

2Y1

2Y2

14

9

13

III-14

2Y3

Dpto. de Sistemas Electrnicos y de Control

Ejercicio Decodificador:

Para una aplicacin se requiere decodificar un nmero en

binario de cinco bits. Usando el C.I. 74154 (decodificador4:16)

implementar el circuito.

El nmero binario de entrada est representado en el formato:

A4A3A2A1A0

74154

1

2

4

8

A0

A

1

A

2

A3

A

4

EN

74154

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

1

2

4

8

A

4

III-15

EN

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Dpto. de Sistemas Electrnicos y de Control

DECODIFICADORES BCD - 7 SEGMENTOS

A diferencia de los Decodificadores pueden

activar varias salidas al mismo tiempo.

Son capaces de proporcionar corriente (salidas

activas a nivel alto, para displays de ctodo

comn) o absorberla (salidas activas a nivel bajo,

para displays de nodo comn).

CDIGO

DECODIFICADOR

EXCITADOR

DECODIFICADOR

TRANSCODIFICADOR

CDIGO

DECODIFICADOR

CODIFICADOR

15

III-16

Dpto. de Sistemas Electrnicos y de Control

DECODIFICADORES BCD - 7 SEGMENTOS

DISPLAY DE 7 SEGMENTOS

NOMENCLATURA

a

f

b

g

c

d

CONFIGURACIN Y CONEXIONES DE LOS LEDs:

GND

g

CTODO COMN

NODO COMN

III-17

VCC

Dpto. de Sistemas Electrnicos y de Control

54/7446- 54/7447A- 54LS/74.S47- 74246-74247 (NODO COMN)

54/7448 -74248 (CTODO COMN)

DECODIFICADORES/DRIVERS DE BCD A 7 SEGMENTOS

A, B, C, D: Dato BCD.

LTN : Entrada para encender todos los leds.

BIN: Entrada para apagar todos los leds.

RBIN-RBON: Encadenamiento para apagar

los dgitos no significativos.

OA.....OG: Segmentos del Display

III-18

Dpto. de Sistemas Electrnicos y de Control

Estructura interna

10

11

12

13

14 15

Representaciones numricas

III-19

Dpto. de Sistemas Electrnicos y de Control

Aplicacin: representacin de un nmero de cuatro cifras en BCD

a)Nmero entero

0

0000

8 4 2 1

RBI LT

8 4 2 1

RBI LT

7447

g f e d c b a

0000

g f e d c b a

1001

8 4 2 1

RBI LT

7447

BI/RBO

0011

7447

BI/RBO

g f e d c b a

8 4 2 1

RBI LT

7447

BI/RBO

g f e d c b a

BI/RBO

Blanked

Blanked

b)Nmero fraccionario

0111

0101

RBI LT

8 4 2 1

RBI LT

7447

g f e d c b a

8 4 2 1

g f e d c b a

8 4 2 1

RBI LT

7447

BI/RBO

BI/RBO

g f e d c b a

8 4 2 1

RBI LT

7447

dp

0000

0000

7447

BI/RBO

g f e d c b a

Blanked

III-20

BI/RBO

Blanked

Dpto. de Sistemas Electrnicos y de Control

GENERADORES/DETECTORES DE PARIDAD

En la transmisin de datos (sobre todo en la

serie), se pueden producir errores.

Las soluciones son :

- Aadir bit de paridad.

- Usar cdigos especiales (CRC,GRAY..).

Perturbaciones

TRANSMISOR

Dato

entrada

RECEPTOR

Mensaje con paridad

(dato de entrada + bit

de paridad)

Dato

salida

PARIDAD: Se aade un bit (bit de paridad) ms a

la informacin (Dato entrada), para que el nmero

de unos en el mensaje con paridad sea par

(CRITERIO DE PARIDAD PAR) o impar

(CRITERIO DE PARIDAD IMPAR).

III-21

Dpto. de Sistemas Electrnicos y de Control

GENERADORES DE PARIDAD

CASO DE 2 BITS

B1

B0

EP

OP

EP: PARIDAD PAR

OP: PARIDAD IMPAR

EP = B1.B0 + B1.B0 = B1 B0

OP = EP

III-22

Dpto. de Sistemas Electrnicos y de Control

54/74180 - 180b-280- 280b : GENERADOR/DETECTOR DE PARIDAD

A, B, C, D, E, F, G, H: Dato entrada.

EVNI, ODDI : Entradas para

seleccionar el tipo de paridad y permitr

conectar varios en cascada.

EVNS, ODDS: Salidas que

contienen el bit de paridad par y el

impar.

III-23

Dpto. de Sistemas Electrnicos y de Control

54/74180 - 180b-280- 280b : GENERADOR/DETECTOR DE PARIDAD

ESTRUCTURA INTERNA:

PUEDE USARSE COMO:

-COMPROBADOR DE PARIDAD (PAR O IMPAR)

SOBRE 9 BITS DE ENTRADA (8 DE DATOS Y UNO DE PARIDAD)

-GENERADOR DE BIT DE PARIDAD, PARA FORMAR UN CDIGO

DE 9BITS.

III-24

Dpto. de Sistemas Electrnicos y de Control

COMPARADORES BINARIOS

CASO DE 2 BITS

A

L

A, B: Entradas

G: Salida que indica A > B

L: Salida que indica A < B

G = A.B

E: Salida de igualdad (A = B)

L = A.B

E=G+L

III-25

Dpto. de Sistemas Electrnicos y de Control

54/7485 : COMPARADOR (BINARIO O BCD) DE 4 BITS

Entradas:

A0..A3: Dato de entrada A.

B0..B3: Dato de entrada B.

A < B: Entrada que indica que en la

comparacin de nivel anterior A ha sido

menor que B (conexin en cascada).

A = B: Entrada que indica que en la

comparacin de nivel anterior A=B.

A > B: Entrada que indica que en la

comparacin de nivel anterior A>B.

Salidas

A<B, A=B, A>B: Salidas que indican el

resultado de la comparacin.

III-26

Dpto. de Sistemas Electrnicos y de Control

54/7485 : COMPARADOR (BINARIO O BCD) DE 4 BITS

EXPANSIN PARA REALIZAR LA COMPARACIN DE DOS BYTES :

III-27

Dpto. de Sistemas Electrnicos y de Control

SUMA: Circuitos Sumadores

En Binario:

0

0

0

0

1

1

1

0

1

+

1

1

1

0

Acarreo

Circuito Semisumador:

A

0

0

1

1

B

0

1

0

1

S C

0 0

1 0

1 0

0 1

S = AB + A B = A B

C = AB

A

B

III-28

Dpto. de Sistemas Electrnicos y de Control

SUMA: Circuitos Sumadores

En general las magnitudes a sumar

sern PALABRAS de N bits y para

poder sumarlas habr que considerar el

ACARREO PREVIO

CIRCUITO SUMADOR COMPLETO:

Realizacin con Circuitos Semisumadores

An

Sn

SEMISUMADOR

SEMISUMADOR

Bn

Cn

Cn-1

III-29

Dpto. de Sistemas Electrnicos y de Control

SUMA: Circuitos Sumadores

Circuito Sumador Completo:

TABLA DE VERDAD

An

0

0

0

0

1

1

1

1

Bn

0

0

1

1

0

0

1

1

Cn-1

0

1

0

1

0

1

0

1

Sn

0

1

1

0

1

0

0

1

S n = An Bn Cn 1

Cn

0

0

0

1

0

1

1

1

Cn = Cn 1 ( An Bn ) + An Bn

III-30

Dpto. de Sistemas Electrnicos y de Control

Realizacin con puertas lgicas:

An

Bn

Sn

Cn

Cn

CIRCUITOS SUMADORES DE N BITS:

A) Suma Paralelo, Acarreo Serie

An

Bn

Cn

A1

Cn-1

Sn

B1

C1

A0

B0

C0

S1

C-1

S0

F Introduce el retardo de la propagacin

serie del acarreo a travs de todas las etapas

III-31

Dpto. de Sistemas Electrnicos y de Control

Suma Paralelo - Acarreo Serie

Tiempo de Propagacin

1 1

1 0

1 0

1 0

A B Cin

A B Cin

A B Cin

A B Cin

Cout

Cout

Cout

Cout

MSB

8ns

8ns

8ns

32ns

III-32

LSB

8ns

Dpto. de Sistemas Electrnicos y de Control

B) Suma Paralelo, Acarreo Paralelo

(Carry Look-Ahead)

Estudio del acarreo:

An

0

0

0

0

1

1

1

1

Bn

0

0

1

1

0

0

1

1

Cn-1

0

1

0

1

0

1

0

1

PROPAGACIN:

Cn

0

0

0

1

0

1

1

1

No se genera

Se propaga

Se genera

Cn = Cn 1

Pn = An Bn

GENERACIN:

Cn = 1

Gn = An Bn

El acarreo puede expresarse como:

Cn = An Bn + ( An Bn )Cn 1 =

= Gn + Pn Cn 1

III-33

Dpto. de Sistemas Electrnicos y de Control

Dando valores a n:

C0 = G0 + P0C1

C1 = G1 + P1C0 = G1 + P1G0 + P1 P0C1

C2 = G2 + P2C1 = G2 + P2G1 + P2 P1G0 + P2 P1 P0C1

....

Cn = Gn + PnGn 1 + Pn Pn 1Gn 2 + ... + Pn Pn 1...P1G0 +

+ Pn Pn 1...P1 P0C1

La complejidad circuital aumenta con el nmero de bits

EJEMPLO:

A3

B3

Para n=3

P3

G3

A2

B2

P2

G2

A1

B1

P1

C3

G1

A0

B0

P0

G0

C-1

III-34

Dpto. de Sistemas Electrnicos y de Control

C) Circuito Sumador Mixto

B7 B6 B5 B4

A7 A6 A5 A4

B3 B2 B1 B0

A3 A2 A1 A0

B3 B2 B1 B0

B3 B2 B1 B0

SUMADOR TOTAL

C3

4 BIT

A3 A2 A1 A0

SUMADOR TOTAL

C-1

C3

4 BIT

C-1

ACARREO SERIE

ACARREO SERIE

S3S2 S1 S0

S3S2 S1 S0

S7S6 S5 S4

C7

A3 A2 A1 A0

C-1

S3S2 S1 S0

B7 B6 B5 B4

A7 A6 A5 A4

B3 B2 B1 B0

A3 A2 A1 A0

B3 B2 B1 B0

A3 A2 A1 A0

B3 B2 B1 B0

A3 A2 A1 A0

GENERADOR

C3

GENERADOR

C3

C3

PROPAGADOR C-1

PROPAGADOR C-1

DEL ACARREO

DEL ACARREO

III-35

Dpto. de Sistemas Electrnicos y de Control

74LS283

Patillaje

Smbolo

Esquema

III-36

Dpto. de Sistemas Electrnicos y de Control

EJEMPLO DE APLICACIN

- Sistema de votacin utilizando sumadores

completos y sumadores de 4 bits en paralelo.

Vcc

SI

NO

SI

A

B

Cin

NO

SI

Cout

A

B

Cin

1

2

A

3

4

1

2

B

3

4

1

2

3

4

BCD

to

7 seg

decod.

SI

Cout

NO

SI

NO

A

B

Cin

SI

NO

Cout

A

B

Cin

1

2

A

3

4

1

2

B

3

4

Cout

SI

NO

III-37

NO

1

2

3

4

BCD

to

7 seg

decod.

Dpto. de Sistemas Electrnicos y de Control

CIRCUITOS RESTADORES

REALIZACIN DE LA RESTA COMO UNA SUMA:

A-B=A+(-B)

Para poder utilizar nmeros negativos se usar:

@ Complemento a dos.

OPERACIN A-B:

COMPLEMENTO A DOS:

A + C2 (B) = A + 2p B=2p + A - B

1) A>B : resultado positivo en p-1 bits.

2) A<B :

resultado negativo en complemento a 2.

III-38

Dpto. de Sistemas Electrnicos y de Control

CIRCUITO COMPLEMENTADOR

Datos

Entradas

Control

Salidas

Ai

EI

Yi

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

1

1

0

0

0

1

1

0

A0

A1

Y0

M

0

0

1

1

A2

Y1

EI

0

1

0

1

A3

Y2

III-39

SALIDA

Dato negado

Puesta a 1

Dato

Puesta a 0

EI

Y3

Dpto. de Sistemas Electrnicos y de Control

CIRCUITO RESTADOR

EN COMPLEMENTO A2

OPERANDO A

OPERANDO B

A3 .A2 A1 A0

CIRCUITO

COMPLEMENTADOR

Y3 Y2 Y1 Y0

B3 .B2 B1 B0

0

M=0 Resta

M=1 Suma

A3 .A2 A1 A0

C0

C-1

S3 S2 S1 S0

SUMA / RESTA

III-40

Das könnte Ihnen auch gefallen

- SD GR12 Cueva Prieto Informe 8Dokument5 SeitenSD GR12 Cueva Prieto Informe 8Jose CuevaNoch keine Bewertungen

- Preparatorio 6Dokument14 SeitenPreparatorio 6Luis LoayzaNoch keine Bewertungen

- Operaciones Aritmeticas BinariasDokument8 SeitenOperaciones Aritmeticas BinariasAndres Vega100% (1)

- Ejercicios de Cod - Dec - Mux - DemuxDokument4 SeitenEjercicios de Cod - Dec - Mux - DemuxGuillermo Nuñez Bances50% (2)

- 3.TRANSISTORES OPTOELECTRÓNICOS PrepaDokument2 Seiten3.TRANSISTORES OPTOELECTRÓNICOS PrepaDavidCaloNoch keine Bewertungen

- Lab 3 N2 Sistemas DigitalesDokument18 SeitenLab 3 N2 Sistemas DigitalesChristian Huapaya ContrerasNoch keine Bewertungen

- Convertidores CD-CDDokument37 SeitenConvertidores CD-CDVictor Quevedo MaldonadoNoch keine Bewertungen

- Diseñe e Implemente Un Circuito SumadorDokument4 SeitenDiseñe e Implemente Un Circuito SumadorJuan Luis Mamani SirpaNoch keine Bewertungen

- Sistemas ProgramablesDokument4 SeitenSistemas ProgramablesivantwrsNoch keine Bewertungen

- Amplificador Polarizado Por Divisor de VoltajeDokument6 SeitenAmplificador Polarizado Por Divisor de Voltajeemze_franz100% (3)

- Funcionamiento Del Convertidor Analógico Digital ADC0809Dokument5 SeitenFuncionamiento Del Convertidor Analógico Digital ADC0809Jorge CaballeroNoch keine Bewertungen

- Chicaiza Intriago Práctica#7 InformeDokument7 SeitenChicaiza Intriago Práctica#7 InformeAlejandro Sebastian Chicaiza Tipan100% (1)

- 6 Polarizacion de Los FETDokument34 Seiten6 Polarizacion de Los FETYesica DeysiNoch keine Bewertungen

- Contadors AsincronosDokument10 SeitenContadors AsincronosDiego Alejandro Gorritti Villarroel100% (1)

- Filtros Segundo OrdenDokument4 SeitenFiltros Segundo OrdenlfernandaceNoch keine Bewertungen

- Preparatorio 3 de Dispositivos ElectrónicosDokument3 SeitenPreparatorio 3 de Dispositivos ElectrónicosJose CuevaNoch keine Bewertungen

- Lab Oratorio Multiplex OresDokument7 SeitenLab Oratorio Multiplex OresChristian Barba Yañiquez33% (3)

- Aplicación de Ecuaciones Diferenciales en Circuitos EléctricosDokument10 SeitenAplicación de Ecuaciones Diferenciales en Circuitos EléctricosElizabeth JuanNoch keine Bewertungen

- Diagramas P&id PDFDokument22 SeitenDiagramas P&id PDFhugoNoch keine Bewertungen

- Solucionario Del Examen Parcial II de Electronic A DigitalDokument5 SeitenSolucionario Del Examen Parcial II de Electronic A Digitalsuperminded50% (2)

- PRINCIPALES POLARIZACIONES DE LOS FET (Parte 1)Dokument8 SeitenPRINCIPALES POLARIZACIONES DE LOS FET (Parte 1)Brayan CastroNoch keine Bewertungen

- Práctica 1 Comparador de VentanaDokument37 SeitenPráctica 1 Comparador de VentanaMaryle Nuñez67% (3)

- Problemas Corte 1Dokument20 SeitenProblemas Corte 1juan ferreiraNoch keine Bewertungen

- Preparatorio 6Dokument7 SeitenPreparatorio 6Luis Edison TocaNoch keine Bewertungen

- Ejemplo #1. Ejemplo #1.: Análisis Del Lugar Geométrico de Las Raíces (LGR) Ó Método de EvansDokument42 SeitenEjemplo #1. Ejemplo #1.: Análisis Del Lugar Geométrico de Las Raíces (LGR) Ó Método de EvansBrayan100% (1)

- Proyecto Lógica Digital: Contador de 4 BitsDokument5 SeitenProyecto Lógica Digital: Contador de 4 BitsJosue Rendón88% (8)

- Ejercicion1-22 Amplificadores de Potencia PDFDokument11 SeitenEjercicion1-22 Amplificadores de Potencia PDFBrayanGarcíaNoch keine Bewertungen

- Solucionario DigitalDokument2 SeitenSolucionario DigitalAlvaNoch keine Bewertungen

- Multiplicador or Decodificador Codificador MultiplexorDokument10 SeitenMultiplicador or Decodificador Codificador MultiplexorJCesar Cusi AlvaradoNoch keine Bewertungen

- Amplificadores RealimentadosDokument16 SeitenAmplificadores RealimentadosRolando Choque CahuanaNoch keine Bewertungen

- PREPARATORIO - PRACTICA No 2Dokument5 SeitenPREPARATORIO - PRACTICA No 2Luis SuquilloNoch keine Bewertungen

- Diseño de Un Disparador de SchmittDokument38 SeitenDiseño de Un Disparador de Schmittrealbanil92Noch keine Bewertungen

- Convertidor Analógico Digital de 8 BitsDokument2 SeitenConvertidor Analógico Digital de 8 Bits'Osmayritthoo GLenn'Noch keine Bewertungen

- Labo6 DSDDokument7 SeitenLabo6 DSDMijhael JanckoNoch keine Bewertungen

- Informe Labo 7Dokument11 SeitenInforme Labo 7Fati EspindolaNoch keine Bewertungen

- CODIFICACION BINARIA (Paper Teoria)Dokument6 SeitenCODIFICACION BINARIA (Paper Teoria)Joseph Muje RamosNoch keine Bewertungen

- Informe #2 Sistemas Digitales 1Dokument5 SeitenInforme #2 Sistemas Digitales 1Juan Sebastian Chicangana MontoyaNoch keine Bewertungen

- Preparatorio Lab DigitalesDokument9 SeitenPreparatorio Lab DigitalesLaura VizcaínoNoch keine Bewertungen

- Preparatorio 1Dokument10 SeitenPreparatorio 1BolivarNoch keine Bewertungen

- Prueba ElectronicaDokument14 SeitenPrueba ElectronicaMax Alvarez50% (2)

- Informe Cerradura Digital de 4 BitsDokument5 SeitenInforme Cerradura Digital de 4 BitsRichert Jesus BompartNoch keine Bewertungen

- Rectificadores de Precisión Con Amplificadores Operacionales de MEDIA ONDA Y ONDA COMPLETADokument41 SeitenRectificadores de Precisión Con Amplificadores Operacionales de MEDIA ONDA Y ONDA COMPLETACarlos Bautista67% (3)

- CPST Preparatorio5 ZambranoJ PDFDokument8 SeitenCPST Preparatorio5 ZambranoJ PDFJuan Diego Zambrano TorresNoch keine Bewertungen

- De Pol de FetDokument17 SeitenDe Pol de FetChewy Santana100% (1)

- Circuitos de Espejo de CorrienteDokument2 SeitenCircuitos de Espejo de CorrienteRicardo Sanjines FloresNoch keine Bewertungen

- Sumador Restador 8 BitsDokument9 SeitenSumador Restador 8 BitsMaria Alejandra Cardozo Guzman0% (1)

- Diseño de Contadores FLOYDDokument10 SeitenDiseño de Contadores FLOYDSergio RomeroNoch keine Bewertungen

- Control de Velocidad de Un Motor DC Con DacDokument10 SeitenControl de Velocidad de Un Motor DC Con DacJosé Manuel Ulloa RamírezNoch keine Bewertungen

- Dispositivos Electrónicos - Novillo Carlos - Capítulo 6Dokument43 SeitenDispositivos Electrónicos - Novillo Carlos - Capítulo 6Jhonny Villota100% (1)

- Practica 5 Multiplexor y DemultiplexorDokument8 SeitenPractica 5 Multiplexor y DemultiplexorNicolas Garcia Aranda De MartinezNoch keine Bewertungen

- Sumador Completo de Dos Bits en VHDLDokument4 SeitenSumador Completo de Dos Bits en VHDLVictor Alejandro100% (1)

- ObservacionCONCLUSIONES DE INFORMEes y Conclusiones DacDokument1 SeiteObservacionCONCLUSIONES DE INFORMEes y Conclusiones DacRoy GutierrezNoch keine Bewertungen

- Informe de Laboratorio 6 Circuitos Adc 0808Dokument7 SeitenInforme de Laboratorio 6 Circuitos Adc 0808David Ajhuacho IncaNoch keine Bewertungen

- Preparatorio 6 DigitalesDokument8 SeitenPreparatorio 6 DigitalesMauricio Fernando TwisterNoch keine Bewertungen

- Proyecto Sumador y Restador BCDDokument13 SeitenProyecto Sumador y Restador BCDLiz Shermelyn Barrientos ValderramaNoch keine Bewertungen

- Logic A ModularDokument57 SeitenLogic A ModularEsteban Jose Hontoria ArlandizNoch keine Bewertungen

- Laboratorio Circuitos CombinatoriosDokument11 SeitenLaboratorio Circuitos CombinatoriosHeyner Marmol VerbelNoch keine Bewertungen

- Previo 7 Digitales LabDokument10 SeitenPrevio 7 Digitales LabHarold Cruz SalasNoch keine Bewertungen

- Sumador de 8bitsDokument22 SeitenSumador de 8bitsposkonono12591100% (8)

- Conclusiones Labo 3Dokument21 SeitenConclusiones Labo 3Jean PierreNoch keine Bewertungen

- Data Logger MSR255 Ficha TecnicaDokument2 SeitenData Logger MSR255 Ficha TecnicaCamilo A. InfanteNoch keine Bewertungen

- Clase - 4 MAPAS DE KARNAUGH PDFDokument6 SeitenClase - 4 MAPAS DE KARNAUGH PDFCamilo A. InfanteNoch keine Bewertungen

- Receptor FM 7Dokument3 SeitenReceptor FM 7Camilo A. InfanteNoch keine Bewertungen

- Modulador Balanceado PDFDokument4 SeitenModulador Balanceado PDFCamilo A. InfanteNoch keine Bewertungen

- PLLDokument4 SeitenPLLCamilo A. InfanteNoch keine Bewertungen

- Guia Lab 2 Oscilaciones. Sistema Masa-ResorteDokument4 SeitenGuia Lab 2 Oscilaciones. Sistema Masa-ResorteCamilo A. InfanteNoch keine Bewertungen

- Momentos de InerciaDokument12 SeitenMomentos de InerciaCamilo A. Infante100% (1)

- Resumen de HidrostaticaDokument1 SeiteResumen de HidrostaticaCamilo A. Infante0% (1)

- Colegio ParticularDokument11 SeitenColegio ParticularWilmer OscoNoch keine Bewertungen

- GuiasDokument2 SeitenGuiasCristy Valentina Bedoya GalvisNoch keine Bewertungen

- Compendio de Practicas Sensores 2005Dokument50 SeitenCompendio de Practicas Sensores 2005zhefyroNoch keine Bewertungen

- Manual Marca Smart TVDokument29 SeitenManual Marca Smart TVRonald Santiago0% (1)

- Tesis Estudio, Análisis y Simulación Del Beamforming en Antenas Inteligentes para Un Entorno de Telefonía Celular CDMADokument130 SeitenTesis Estudio, Análisis y Simulación Del Beamforming en Antenas Inteligentes para Un Entorno de Telefonía Celular CDMASylvère MugemanyiNoch keine Bewertungen

- FICHA DE PRACTICA 1 Tableros HECHODokument3 SeitenFICHA DE PRACTICA 1 Tableros HECHOJonatan Aaron ANDRADE CAMPOSNoch keine Bewertungen

- Reguladores Reductores y ElevadoresDokument5 SeitenReguladores Reductores y ElevadoresAdrian Reyes GalavizNoch keine Bewertungen

- JU-SSO-STD-005.F02 Check List Insp Paneles ElectricosDokument2 SeitenJU-SSO-STD-005.F02 Check List Insp Paneles ElectricosCristian Omar Ojeda CamaNoch keine Bewertungen

- Historia de Los MicrocontroladoresDokument6 SeitenHistoria de Los MicrocontroladoresServando De JesúsNoch keine Bewertungen

- Organizacion y Arquitectura de ComputadoresDokument7 SeitenOrganizacion y Arquitectura de ComputadoresdmartinezolivaresNoch keine Bewertungen

- Irig PreampDokument5 SeitenIrig PreampJorman ManriqueNoch keine Bewertungen

- Comercial PhanehauseDokument105 SeitenComercial Phanehausemegane1772Noch keine Bewertungen

- Diseño de Instrucciones Del UsuarioDokument41 SeitenDiseño de Instrucciones Del UsuarioJuan ThompsonNoch keine Bewertungen

- Diagrama de Redes AtmDokument11 SeitenDiagrama de Redes AtmMi Angel FabrizioNoch keine Bewertungen

- Instructivo Mantenimiento de Variadores de FrecuenciaDokument8 SeitenInstructivo Mantenimiento de Variadores de FrecuenciaFabian Ariza ArizaNoch keine Bewertungen

- 7.1.2.8 Lab - Research Docking Stations and Port ReplicatorsDokument2 Seiten7.1.2.8 Lab - Research Docking Stations and Port Replicatorsstiven rufinoNoch keine Bewertungen

- Comandos Básicos de BitDokument14 SeitenComandos Básicos de BitJontan FloresNoch keine Bewertungen

- Trabajo de PCDokument57 SeitenTrabajo de PCWilliam castillo100% (1)

- Tecnología de La InformaciónDokument3 SeitenTecnología de La InformaciónNelson MataNoch keine Bewertungen

- Características Del MultimetroDokument1 SeiteCaracterísticas Del MultimetroOscar Jhoan Chan Gonzalez80% (5)

- Arbol SolarDokument8 SeitenArbol SolarRonaldo Dueñas Bautista100% (1)

- Silabo - Electronica II - AUTODokument9 SeitenSilabo - Electronica II - AUTORicardo BarrionuevoNoch keine Bewertungen

- Actividad 7 RoboticaDokument3 SeitenActividad 7 RoboticaITZEL REBECA CORTEZ ROBLEDONoch keine Bewertungen

- 13.2 Amplificadores Operacionales Sumador, Restador y en CascadaDokument23 Seiten13.2 Amplificadores Operacionales Sumador, Restador y en CascadaSara Mendieta100% (1)

- Tyc Pospago 5 0 Nueva OfertaDokument6 SeitenTyc Pospago 5 0 Nueva OfertaAndersonNoch keine Bewertungen

- Instalacion OxoDokument129 SeitenInstalacion OxoSamuel Mares PalafoxNoch keine Bewertungen

- Formato General Silabo-Sunedu ArquitecturaDokument5 SeitenFormato General Silabo-Sunedu ArquitecturaJuan Perez ArizavalNoch keine Bewertungen

- Redes Opticas ActivasDokument5 SeitenRedes Opticas ActivasKarina AngamarcaNoch keine Bewertungen

- AIR-USB150GNH Datasheet PDFDokument2 SeitenAIR-USB150GNH Datasheet PDFElvis Gustavo ColcaNoch keine Bewertungen

- Proyecto Final OptomecatronicaDokument13 SeitenProyecto Final OptomecatronicaCon Vel'zNoch keine Bewertungen